Изобретение относится к области измерительной техники и может быть использовано для спектрального анализа детерминированных и случайных сигналов в реальном масштабе времени о

Известен цифровой анализатор спектра, содержащий блок согласования, генератор вспомогательного сигнала, два компаратора, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, генератор счетных импульсов, ключ, два реверсивных счетчика, Фильтр, генератор меандровых сигналов и два блока умножения зна. ков (А.С.СССР № 12690 6, G01 R23/00).

Недостатком данного анализатора спектра является его невысокое быстродействие

Известен также адаптивный анализатор спектра, содержащий дискре- тизатор, аналого-цифровой преобразователь, блок памяти, два перемножителя, накапливающий сумматор, блок памяти весовых коэффициентов, преобразователь частотных характеристик, синхронизатор, генератор некоррелированных выборок и два сумматора (А„С0СССР f 12571Й7,G 01 R 23/16) .

Основным его недостатком является ограниченное быстродействие ,

С С

о

Наиболее близким по технической сущности к предлагаемому изобретению и принятым за прототип следует считать анализатор комплексного спектра „ периодических напряжении, содержащий

входной блок, выход которого соединен с входом усилителяs а вход - с входной шиной, синхронный детектор, выход которого соединен с входом ин- дикатора, формирователь опорного напряжения, первый выход которого соединен с первым входом синхронного детектора, а вход - с шиной опорного напряжения, а также цифроаналоговый преобразователь, программируемый постоянный запоминающий блок и формирователь адресов, причем сигнальные вход и выход цифроаналогового преобразователя подключены соответ- ственно к выходу усилителя и к второму входу синхронного детектора, а управляющие входы цифроаналогового преобразователя соединены с кодовыми выходами программируемого по- стоянного запоминающего блокаs адресные входы которого подключены к кодовым выходам формирователя адресов, вход которого соединен со вторым входом формирователя опорного напряже- ния (А«С0СССР № 116600, G 01R23/00)

Существенным недостатком указанного анализатора является его низкое быстродействие, обусловленное необ- ходимостью изменения частоты опорного напряжения в процессе спектрального анализа с целью последующего вычисления амплитудных и фазовых спектрово

Целью изобретения является повышение быстродействия анализатора спектра.,

Эта цель достигается тем, что в анализатор спектра, содержащий вход- ной блок, выход которого соединен с входом усилителя, а вход - с входной шиной, а также формирователь адреса и блок перепрограммируемых постоянных запоминающих устройств, адресные вхо- ды которого подключены к кодовым выходам формирователя адресов, дополнительно введены аналого-цифровой преобразователь (АЦП), два блока перемножителеи, каждый из которых содерг жит N перемножителей, два блока накопительных сумматоров, каждый из которых содержит N сумматоров, два блока квадраторов, каждый из которых со

5 0

g 0

5 g

5

держит N квадраторов, блок вычисли - телей модуля, содержащий N вычислителей, блок функциональных преобразователей, содержащий N преобразователей, устройство синхронизации и второй блок перепрограммируемых постоянных запоминающих устройств (ППЗУ), причем первый и второй блок ППЗУ содержит N запоминающих устройств каждый, адресные входы которых объединены и подключены к выходу формирователя адресов, вход которого соединен с первым выходом устройства синхронизации и первым входом АЦП, второй вход которого подключен к выходу усилителя, а выход - к первому входу каждого из N перемножителей первого и второго блоков перемножителей, второй вход каждого из N перемножителей первого блока перемножителей соединен с выходом соответствующего запоминающего устройства первого блока ППЗУ, второй вход каждого из N перемножителей второго блока перемножителей соединен с выходом соответствующего запоминающего устройства второго блока ППЗУ, третьи входы каждого из N перемножителей,первого и второго блоков перемножителей объединены и подключены рому выходу устройства синхронизации, первый вход каждого из N сумматоров первого блока накопительных сумматоров соединен с выходом соответствующего перемножителя первого блока перемножителей, а выход каждого из N сумматоров - с первым входом соответствующего квадратора первого блока квадраторов и первым входом соответствующего преобразователя блока функциональных преобразователей, первый вход каждого из N сумматоров второго блока накопительных сумматоров соединен с выходом соответствующего перемножителя второго блока перемножителей, а выход каждого из N сумматоров - с первым входом соответствующего квадратора второго блока квадраторов и вторым входом соответствующего преобразователя блока функциональных преобразователей,вторые входы каждого из N квадраторов первого и второго блоков квадраторов подключены к рому выходу устройства синхронизации; выход каждого из N квадраторов первого блока квадраторов соединен с

5

перв ымПзходом соответствующего вычислителя блока вычислителей модуля, второй вход каждого из N вычислителей блока вычислителей модуля подключен к выходу соответствующего квадратора второго блока квадраторов, вторые входы каждого из N сумматоров первого и второго блока накопительных сумматоров соединены с третьим выходом устройства синхронизации, при этом выходы блока вычислителей модуля являются первой выходной шиной анализатора спектра, а выходы блока функциональных преобразователей - его второй выходной шиной.

Введение в анализатор спектра новых элементов и связей позволило реализовать рекуррентный алгоритм вычисления коэффициентов Фурье с- параллельным выполнением операций и тем самым значительно повысить его быстродействие.

Решение с такой совокупностью признаков, как у заявляемого, среди решений, известных в науке и технике на данный момент, авторами не обнаружено.

Именно введение новой совокупности ранее перечисленных элементов и связей позволило повысить быстродействие цифрового динамического анализатора спектров.

Таким образом, заявляемое техническое решение соответствует крите- рию существенные отличия.

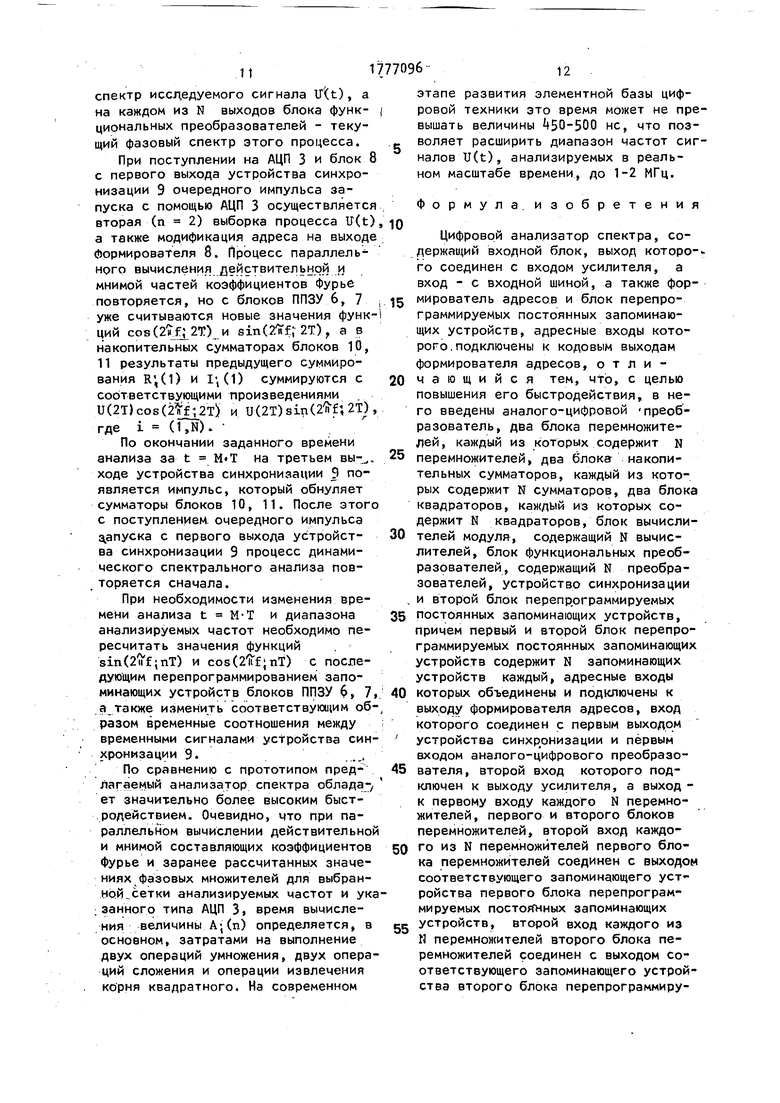

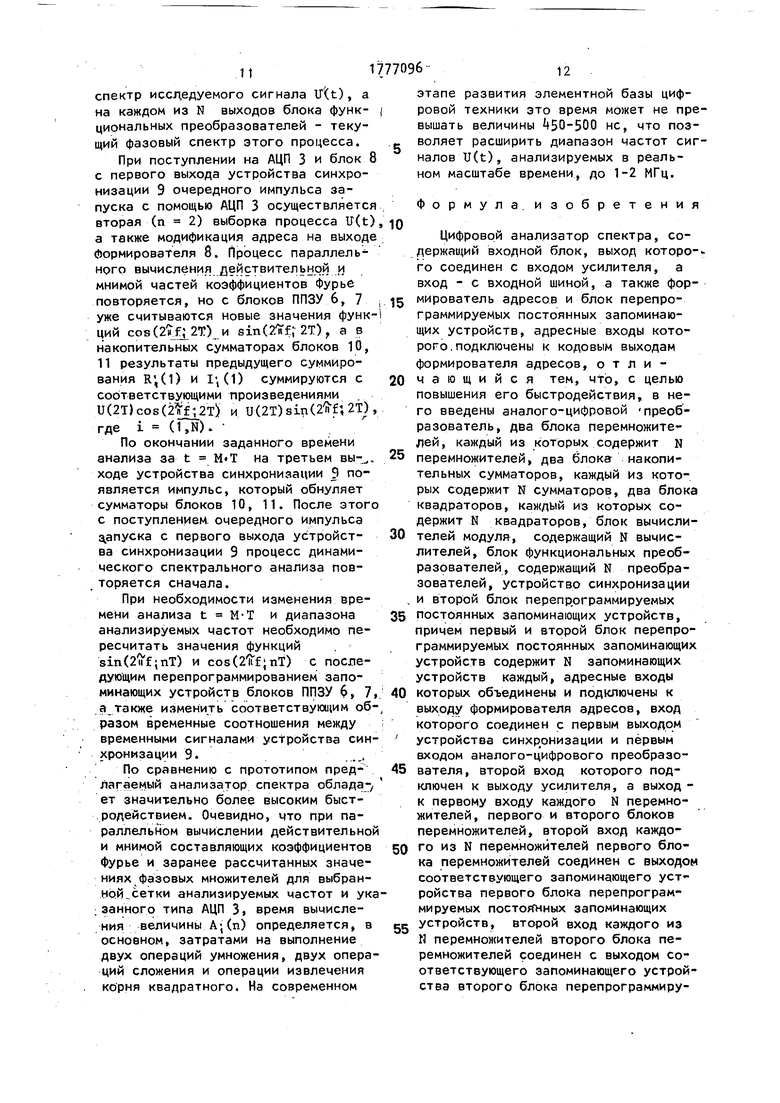

Структурная схема цифрового динамического анализатора спектров представлена на чертеже.

Анализатор спектра включает в себя последовательно соединенные вход- ьой блок 1, усилитель 2, АЦП 3, выход которого подключен к первым входам каждого из N перемножителей первого блока перемножителей k и второго блока перемножителей 5. К вторым входам каждого из N перемножителей блока 4 подключены выходы соответствующих запоминающих устройств первого блока ППЗУ 6. К вторым входам каждого из N перемножителей блока 5 подключены выходы соответствующих запоминающих устройств второго блока ППЗУ 7. Адресные входы блоков ППЗУ 6, 7 объединены и подключены к выходу формирователя- адресов 8, вход которого соединен с первым входом устройства, синхронизации 9 и входом

77096 б

управления АЦП 3. Третьи входы каждого из N перемножителей блоков , 5 . соединены с вторым входом устройства синхронизации 9. Первый блок накопительных сумматоров 10 и второй блок накопительных сумматоров 11 содержат по N сумматоров каждый. Первый вход каждого из N сумматоров Ю блока 10 соединен с входом соответствующего перемножителя блока А, а выход - с первым входом соответствующего квадратора первого блока квадраторов 12 и первым входом со- 15 ответствующего преобразователя блока функциональных преобразователей 13. Первый вход каждого из N сумматоров блока 11 соединен с выходом соответствующего перемножителя блока 20 5, а выход - с вторым входом соответствующего преобразователя блока функциональных преобразователей 13. Вторые входы каждого из N квадраторов блока 12 и блока k объединены 25 и подключены ко второму выходу устройства синхронизации 9, третий выход которого соединен с вторым входом каждого из N сумматоров блока 10 и блока 11. Выход каждого из N 30 квадраторов блока 12 соединен с первым входом соответствующего вычислителя блока вычислителей модуля 15. Второй вход каждого из N вычислителей блока 15 подключен к выходу со- 35 ответствующего квадратора второго блока квадраторов И. Выходы каждого из N вычислителей блока 15 представляют собой первую выходную шину анализатора спектра, а N выходов бло- 40 ка функциональных преобразователей 13 - его вторую выходную шину.

Для практической -реализации предлагаемого анализатора спектра могут быть рекомендованы следующие 45 известные съемные решения и элементная база.

Входной блок может быть выполнен, например, в виде приемного СВЧ модуля, построенного по супергетеродин- 50 ной схеме с однократным преобразованием частоты {Радиоприемные устройства: Учебное пособие для радиотехнических специальностей вузов/ /Давыдов Ю.Т., Данич Ю.С., Жуков- 55 ский А.П. и др.- М.: Высшая школа, 1989.- с.111, 119).

Усилитель 2 может быть реализован по известной схеме широкополосного усилителя (Хоровиц П., Хилл У, Искусство схемотехники.- М.: Мир, 1983 - т.2, с.325).

АЦП 3 легко реализуется на ИМС серий К1107, К57 |, КЙО. Рекомендуе- мый вариант схемного включения быстродействующего АЦП типа К1Ю7ПВ1 описан в литературе (федорков Б.Г.,1 Телец В.А., Дегтяренко В.П. Микро - электронные цифроаналоговые и аналого цифровые преобразователи,- М.: Радио и связь, . - c.8l).

Цифровые перемножители сигналов в квадраторы, входящие в состав блоков 4, 5, 12 и 1А, легко реализуются на базе секционного умножителя типа КР1802ВР2 (Хвощ С.Т. и др. Микропроцессоры и микроЭВМ в системах автоматического управления: Справочник.- Л.: Машиностроение, 1987.- с.335-339)

Запоминающие устройства первого и второго блоков ППЗУ могут быть реализованы, например, на ИМС типа К572РФ2, К572РФ6 и т.п.

Формирователи адресов 8 легко реализуются в виде счетчика и буферных каскадов,повышающих его нагрузочную способность, например, на ИМС серий К155, К555.

Для реализации устройства синхроизации 9 может быть рекомендована звестная схема синхронизатора. (Цифовые анализаторы спектра. Плотников В.Н., Белинский А.В., Суханов В.А, Жигулевцев Ю.Н.- М.: Раио и связь, 1990, с.133).

Сумматоры, входящие в состав блоков накопительных сумматоров 10, 11 могут быть реализованы по известной схеме (Файзулаев Б.Н. Применение интегральных микросхем в электронной вычислительной технике.-М.: Радио и связь, 1987, с.1Й).

Для реализации вычислителей модуля, входящих в состав блока 15, могут быть рекомендованы цифровые сумматоры серии К155 и известное устройство для извлечения квадратного корня (Плотников В.Н., Белинский А.В., Суханов В.А., Жигулевцев Ю.Н. Цифровые анализаторы спектра.- М.: Радио и связь, 1990.- с.89).

Преобразователи, входящие в состав блока функциональных преобразователей 13 и обеспечивающие вычисления фнукции arctg J/R табличным способом, проще всего реализовать

на ИМС ППЗУ серии К572 и логических элементах серии К155.

Работа предлагаемого анализатора спектра основана на реализации преобразования Фурье исследуемого сигнала U(t) с помощью аналого-цифровой техники по следующим рекурент- ным формулам:

Q

5 0

5

0

5

0

5

R;(n) Rj(n-l) + + U(nT)cos(2 flf;nT)

l7(n) I;(n-1) н- + U(nT)sin(2lTf;nT),

где Rj(n), I;(n)

(1)

(2)

действительная и мнимая составляющие коэф- . фициентов Фурье соответственно для n-й выборки временного процесса U(t) на i-й частоте

n 1,2...М - номер временной выборки ,

i 1,2...N - номер анализируемой частоты,

М - число, соответствующее размеру временной выборки,

N - число,4 соответствующее интервалу анализируемых частот;

Т - период дискретизации временного процесса U(t).

Очевидно, что для реализации дискретного преобразования Фурье с помощью формул (1) и (2) необходимо:

-осуществить дискретизацию по времени .и квантование по уровню временного процесса U(t)1,

-определить значение функций sin и cos.для всех частот f;(i 1,N) и выборок n (n 1,м),

-для каждой выборки n 1,м по всем частотам вычислить произведение

0 функций sin2 nf nT и cos27f;nT с величиной U(nT)

-по формулам (1) и (2) вычислить значения R|(n) и 1{(п), с помощью которых определить для i-й частоты

5 модуль и фазу коэффициента Фурье по формулам:

А;(п)

1

) +

1(п

«ftOO-Tctglj В исходном состоянии сумматоры первого блока накопительных сумматоров 10 и второго блока накопительных сумматоров 11 обнулены. В N запоминающих устройствах первого блока ППЗУ, имеющих глубину адресации М, записаны заранее рассчитанные для всех анализируемых частот fj ( V 1,N) и всех выборок п 1 ,М

U(nT) значения

N запоминающих устройствах второго блока ППЗУ 7, также имеющих глубину адресации М, записаны заранее рассчитанные Для всех анализируемых частот f; (i 1,ГТ) и всех выборок n t,M

значевременного процесса функции cosUftf; nT). В

временного процесса U(nT) ния функции sinUfif; nT).

Анализатор спектра работает следующим образом.

Исследуемый сигнал U(t) через входной блок 1 и усилитель 2 поступает на информационный вход АЦП 3. Одновремено с этим на управляющий вход АЦП 3 поступает импульс запуска, вырабатываемый устройством синхронизации 9 и снимаемый с его первого выхода. По импульсу запуска начинается преобразование в АЦП 3 аналогового сигнала u(t) в цифровой двоичный код, а также устанавливается на выходе формирователя 8 код адреса, соответствующий первой (п 1) временной выборке процесса U(t). По указанному адресу с N запоминающих устройств блока 7 осуществляется считывание цифровых кодов, соответствующих значениям функций cos (2frf; Т) и sin(2TTf; Т) для всех анализируемых частот fJ (i 1,N). Выходные коды блоков ППЗУ 6,7 поступают соответственно на вторые входы блоков перемножителей Ь и 5, на первые входы которых подается выходной код АЦП 3, соответствующий величине и(Т). В каждом из N перемножителей блока k одновременно осуществляется умножение величины и(Т) на соответствующий фазовый множитель cos(2trf ;T), а в каждом из N перемножителей блока 5 - умножение величины U(Т) на соответствующий фазовый множитель sinCZfrf; Т), где i 1,N. С выходов N перемножителей блока цифровые коды поступают на N накопительных сумматоров бпока 10, в

10

15

20

30

77709610

котором происходит сложение результата предыдущего суммирования R;(n-1) с текущим произведением U(T)cos(2 «f ;T), для всех анализируемых частот f.;. В К накопительных сумматорах блока 11 происходит сложение результата предыдущего суммирования I (n-1) с текущим произведением U(T)sin(2 Ј Т), для всех анализируемых частот f;. В результате суммирования на выходе каждого из N сумматоров блока 10 формируется новое значение R;(n) действительной части коэффициентов Фурье,- а на выходе каждого из N сумматоопв блока 11 - новое значение I; (п) мнимой части коэффициентов Фурье,

Поскольку в исходном состоянии все N сумматоров блока 10 и блока 11 обнулены, значения величин R{.(0) и для i 1,N - нулевые.

Для получения текущего фазового

1;(0)

спектра на частотах f| (i 1,N) ве- 25 личины Rj(n) и l;(n) подаются на соответствующие входы функциональных преобразователей блока 13, в каждом из которых для соответствующей частоты fj вычисляется значеТ (п

ние функции (п) arctg ™4-у-

Для вычисления текущего амплитудного спектра полученные в блоке 10 действительные части R(n) коэффи35 циентов Фурье к вадраторах блокл 12 возводятся в квадрат, после чего поступают на вход соответствующего вычислителя модуля блока 15- На вторые входы каждого из N вычислителей мо40 дуля блока 15 с соответствующих выходов блока 1А поступают коды, определяющие квадрат мнимой части 1(п) коэффициентов Фурье. При этом синхронизация работы квадраторов блоков 12,

45 1 и перемножителей блоков 4, 5 осуществляется импульсами, снимаемыми со второго выхода устройства синхронизации 9.

В каждом из N вычислителей блока

50 соответствующей частоты f; (i 1.N) выполняются операции суммирования величин R2(n) и 1(п) с последующим извлечением корня квадратного из полученной суммы для оп55 ределения модуля коэффициента Фурье А (п). Тем самым на каждом из N вы-i ходов блока 15 до окончания интерва-| ла времени, равного Т, формируется мгновенный (текущий) амплитудный

спектр иссдедуемого сигнала lT(t), a на каждом из N выходов блока функ- ционалыных преобразователей - текущий фазовый спектр этого процесса.

При поступлении на АЦП 3 и блок 8 с первого выхода устройства синхронизации 9 очередного импульса запуска с помощью АЦП 3 осуществляется вторая (п 2) выборка процесса U(t) а также модификация адреса на выходе формирователя 8. Процесс параллельного вычисления действительной и мнимой частей коэффициентов Фурье повторяется, но с блоков ППЗУ 6, 7 уже считываются новые значения функций cos() и ainCZTTf; 2T), а в накопительных сумматорах блоков Ю, 11 результаты предыдущего суммирования R;(1) и г,(1) суммируются с

соответствующими произведениями U(2T)cos(2fa;2T) и U(2T)sin(2ftf;2T), где i (1,N).

По окончании заданного времени анализа за t М«Т на третьем вы-. ходе устройства синхронизации 9 появляется импульс, который обнуляет сумматоры блоков 10, 11. После этого с поступлением очередного импульса запуска с первого выхода устройства синхронизации 9 процесс динамического спектрального анализа повторяется сначала.

При необходимости изменения времени анализа t М-Т и диапазона анализируемых частот необходимо пересчитать значения функций sin(2li f;nT) и cos(2 li f;nT) с последующим перепрограммированием запоминающих устройств блоков ППЗУ 6, 7, а также изменить соответствующим образом временные соотношения между временными сигналами устройства синхронизации 9.

По сравнению с прототипом предлагаемый анализатор спектра облада-х ет значительно более высоким быстродействием. Очевидно, что при параллельном вычислении действительной и мнимой составляющих коэффициентов Фурье и заранее рассчитанных значениях фазовых множителей для выбранной, сетки анализируемых частот и ука , занного типа АЦП 3 время вычисления величины А;(п) определяется, в основном, затратами на выполнение двух операций умножения, двух операций сложения и операции извлечения корня квадратного. На современном

.

5

0

5

этапе развития элементной базы цифровой техники это время может не превышать величины 50-500 не, что позволяет расширить диапазон частот сигналов U(t), анализируемых в реальном масштабе времени, до 1-2 МГц.

Формула изобретения

Цифровой анализатор спектра, содержащий входной блок, выход которо-- го соединен с входом усилителя, а вход - с входной шиной, а также формирователь адресов и блок перепрограммируемых постоянных запоминающих устройств, адресные входы которого подключены к кодовым выходам формирователя адресов, отличающийся тем, что, с целью повышения его быстродействия, в него введены аналого-цифровой -преобразователь, два блока перемножителей, каждый из которых содержит N перемножителей, два блока накопительных сумматоров, каждый из которых содержит N сумматоров, два блока квадраторов, каждый из которых содержит N квадраторов, блок вычислителей модуля, содержащий N вычислителей, блок функциональных преобразователей, содержащий N преобразователей, устройство синхронизации и второй блок перепррграммируемых 5 постоянных запоминающих устройств, причем первый и второй блок перепрограммируемых постоянных запоминающих устройств содержит N запоминающих устройств каждый, адресные входы которых объединены и подключены к выходу формирователя адресов, вход которого соединен с первым выходом устройства синхронизации и первым входом аналого-цифрового преобразователя, второй вход которого подключен к выходу усилителя, а выход - к первому входу каждого N перемножителей, первого и второго блоков перемножителей, второй вход каждого из N перемножйтелей первого блока перемножителей соединен с выходом соответствующего запоминающего устройства первого блока перепрограммируемых постоянных запоминающих устройств, второй вход каждого из И перемножителей второго блока перемножителей соединен с выходом соответствующего запоминающего устройства второго блока перепрограммиру0

0

5

0

5

емых постоянных запоминающих устройств, третьи входы каждого из N перемножителей первого и второго блоков перемножителей объединены и подключены к второму выходу устройства синхронизации, первый вход каждого из N сумматоров первого блока накопительных сумматоров соединен с выходом соответствующего перемножи- теля первого блока перемножителей, а выход каждого из N сумматоров - с первым входом соответствующего квадратора первого блока квадраторов и первым входом соответствующего преобразователя блока функциональных преобразователей, первый вход каждого из сумматоров второго блока накопительных сумматоров соединен с выходом соответствующего перемножи- теля второго блока перемножителей, а выход каждого из N сумматоров - с первым входом соответствующего квадратора второго блока квадраторов и вторым входом соответствующего пре

образователя блока функциональных преобразователей, вторые входы каждого из N квадраторов первого и второго блоков квадраторов подключены к второму выходу устройства синхронизации, выход каждого из N квадраторов первого блока квадраторов соединен с первым входом соответствующего вычислителя блока вычислителей модуля, второй вход каждого из N вычислителей блока вычислителей модуля подключен к выходу соответствующего квадратора второго блока квадратора, вторые входы каждого из N суммататоров первого и второго блока накопительных сумматоров соединены с третьим выходом устройства синхронизации, при этом выходы блока вычислителей модуля являются первой выходной шиной анализатора спектра, а выходы блока функциональных преобразователей - его второй выходной шиной.

хмп/яонпт

вънрохпд t/Dgdai/ монрохмд vodowg

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ спектрального анализа с линейным предсказанием | 1988 |

|

SU1691770A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Способ анализа спектра сигналов и устройство для его осуществления | 1988 |

|

SU1573432A1 |

| ДЕМОДУЛЯТОР СИСТЕМЫ СВЯЗИ С ДВУХКРАТНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2009 |

|

RU2427969C1 |

| Устройство для выделения признаков при распознавании случайных сигналов | 1990 |

|

SU1797134A1 |

| Цифровой панорамный измеритель частоты | 1985 |

|

SU1296955A1 |

| РАДИОМОДЕМ | 2010 |

|

RU2460215C1 |

| Устройство для предварительной обработки электроразведочных сигналов | 1986 |

|

SU1539708A1 |

| Анализатор спектра с линейным предсказанием | 1985 |

|

SU1275315A1 |

| Устройство контроля аналого-цифровых преобразователей | 1988 |

|

SU1711327A1 |

Использование: в области измерительной техники и для спектрального анализа детерминированных и случайных сигналов а реальном масштабе времени. Сущность изобретения; со-, держит входной блок 1, усилитель 2, формирователь адресов 8, АЦП 3, два блока перемножителей k, 5, каждый из которых содержит N перемножителей, два блока накопительных сумматоров 10, П, каждый из которых содержит N сумматоров, два блока 12, 1 квадраторов, каждый из которых содержит N квадраторов,блок 15 вычислителей модуля, содержащий N вычислителей, блок 13 функциональных преобразователей, содержащий N преобразователей, устройство 9 синхронизации и два блока 6, 7 ППЗУ, каждый из которых содержит N запоминающих устройств,, Особенностью изобретения является введение блоков перемножителей, блоков накопительных сумматоров, блоков квадраторов, блока вычислителей модуля, блока функциональных преобразователей, АЦП, второго блока ППЗУ и устройства синхронизации, что позволяет повысить быстродействие. 1 ил„ СП с

1У-4- Ц1

п-I h

Fifra или

х «I - х «agj u - е

W

in

и: in 1 Ж -1- I IS.

1У Г LjT

Cvl

СХ5

/V

/

л (-, - I 2, €{

ВД-ЗД

7 ГЗ

/V7t

г

| Устройство для измерения вращающего момента электрического двигателя | 1957 |

|

SU116600A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-11-23—Публикация

1990-08-07—Подача