1

(21)4872539/24

(22) 19.07.90

(46) 23.09.92. Бюл. № 35

(71)Московский институт радиотехники, электроники и автоматики

(72)Н.Н.Евтихиев, Е.В.Емелин, Д.Э.Краснов, И.В.Ланин, Е.Г.Литвинов и В.Л.Тауб- кин

(56)Авторское свидетельство СССР № 1256041,кл G 06 F 15/20,1985.

Европейский патент N 0049039, кл. G 06 F 15/347, опублик. 1984.

(54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ВЕКТОРОВ

(57)Изобретение относится к вычислительной технике и может быть использовано в качестве специализированного вычислителя в системах обработки данных, Цель изобретения - повышение быстродействия при выполнении над векторами операций типа

пп

У (f (ai, bi) л 3i bi, а также расширение

О

функциональных возможностей за счет вып

числения функции (ai bi). Устройство со- i о

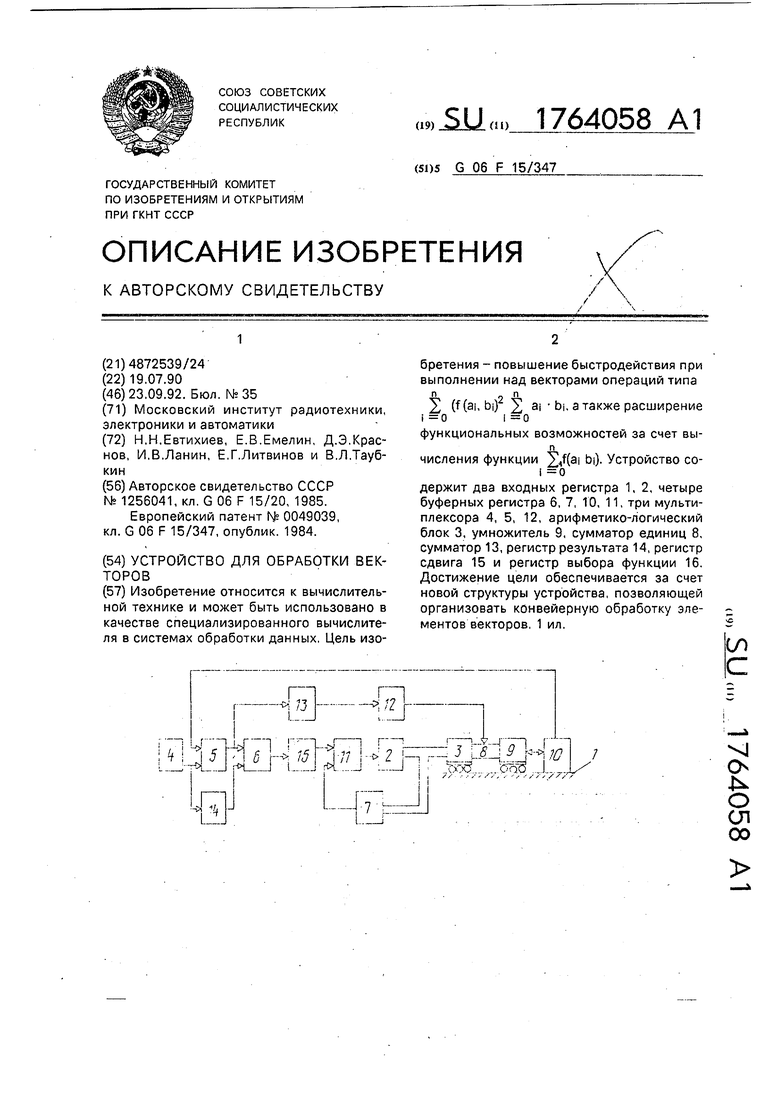

держит два входных регистра 1, 2, четыре буферных регистра 6, 7, 10, 11, три мультиплексора 4, 5, 12, арифметико-логический блок 3, умножитель 9, сумматор единиц 8, сумматор 13, регистр результата 14, регистр сдвига 15 и регистр выбора функции 16. Достижение цели обеспечивается за счет новой структуры устройства, позволяющей организовать конвейерную обработку элементов векторов 1 ил.

сл С

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для умножения двух чисел | 1989 |

|

SU1667059A2 |

| МАТРИЧНЫЙ СПЕЦПРОЦЕССОР | 1994 |

|

RU2079879C1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

„J

vj о ь о сл

00

Изобретение относится к вычислительной технике и может быть использовано в качестве специализированного вычислителя в системах обработки данных.

Известно устройство, содержащее матрицу ячеек, каждая из которых имеет элементы И, ИЛИ, НЕ, триггеры, и предназначенное для выполнения операции сжатия векторов. Недостатком известного устройства являются узкие функциональные возможности, которые не позволяют выполнять

операции Г (f (a, bi))2, 2Э| D| и

i 0

i 0

i 0

элементы первого и второго векторов, имеющие размерность N; f (a,, bi) - произвольная простейшая функция двух аргументов; Si - функция бинарной корреляции двух векторов.

Наиболее близким к изобретению является устройство для обработки разряженных векторов, содержащее девять буферных регистров, арифметико-логический узел, узел логики управления, сдвиговый регистр и счетчик. Недостатком указанного устройства является его малое быстродействие.

Цель изобретения - повышение быстродействия при выполнении над векторами

операций типа 2) (f (а,, Ь,)) , 2а b| - a

также расширение функциональных возможностей за счет вычисления функции

(a,, b,).

i 0

Поставленная цель достигается тем, что в устройство для обработки векторов, содержащее первый и второй входные регистры, регистр выбора функции, арифметико-логический блок, четыре буферных регистра, регистр результата и регистр сдвига, первый и второй выходы которого соединены соответственно с управляющими входами первого, второго, третьего и четвертого буферных регистров, причем входы первого и второго операндов устройства соединены соответственно с информационными входами первого и второго входных регистров, выходы которых соединены соответственно с входами первого и второго операндов арифметико-логического узла, вход кода операции устройства соединен с входом регистра выбора функции, выход регистра результата соединен с выходом результата устройства, первый вход синхронизации которого соединен с входом синхронизации первого входного регистра, вход запуска регистра сдвига и вход синхронизации второго входного регистра соединены с вторым входом синхронизации устройства,

управляющий вход регистра результата соединен с третьим входом регистра сдвига, введены три мультиплексора, сумматор единиц, умножитель и сумматор, причем информационный вход регистра результата

соединен с выходом сумматора, входы младших разрядов первого слагаемого которого соединены с выходом первого мультиплексора, первый и второй информационный входы которого соединены соответственно с выходом значащих разрядов третьего и выходом четвертого буферных регистров, информационный вход третьего буферного регистра соединен с выходом умножителя, первый и второй информационные входы которого соединены соответственно с выходами первого и второго буферных регистров, информационные входы которых соединены соответственно с выходами

второго и третьего мультиплексоров, первые информационные входы которых соединены соответственно с выходами первого и второго входных регистров, первый выход регистра выбора функции соединен с входом задания режима работы арифметико- логического узла, выход которого соединен с вторыми информационными входами второго и третьего мультиплексоров и входом сумматора единиц, выход которого соединен с информационным входом четвертого буферного регистра, управляющие входы второго и третьего мультиплексоров соединены с вторым выходом регистра выбора функции, третий выход которого соединен с управляющим входом первого мультиплексора, выход регистра результата соединен с входом второго слагаемого сумматора, входы старших разрядов первого слагаемого которого соединены с выходом знакового разряда третьего буферного регистра.

Функциональная схема устройства представлена на чертеже.

Устройство содержит первый 1 и второй

2 входные регистры, арифметико-логический блок 3, мультиплексоры 4 и 5, буферные регистры 6 и 7, сумматор единиц 8, умножитель 9, буферные регистры 10 и 11, мультиплексор 12, сумматор 13, регистр результата 14, сдвиговый регистр 15, регистр выбора функции 16, информационные входы 17 и 18, вход задания функции 19, выход 20, входы 21 и 22 синхронизации устройства.

Устройство работает следующим образом. Перед началом работы происходит обнуление регистров 1,2,6, 7, 10, 11, 14, 16 и установка в исходное состояние регистра 15 (цепи сброса и начальной установки на чертеже не показаны). Затем по входу 19 в регистр 16 заносится управляющее слово, по которому осуществляется установка реализуемой узлом 3 элементарной функции и коммутация мультиплексоров 4, 5 и 12 (цепи синхронизации на чертеже не показаны). Далее устройство осуществляет собственно обработку следующим образом.

Векторы Аи В подаются на вход устройства поэлементно, но асинхронно Элемент вектора А через вход 17 подается на регистр 1 и сопровождается импульсом строба с входа 21 для записи в регистр. Соответствующий элемент вектора В через вход 18 подается на регистр 2 и сопровождается стробом с входа 22 для записи в регистр. Строб записи с входа 22 также подается на вход сдвигового регистра 15, который выполняет функцию временной задержки строба. Сдвинутые по времени относительно строба с входа 22 импульсы с регистра 15 подаются на входы буферных регистров 6. 7, 10, 11 и регистр результата 14, Коммутацией мультиплексоров 4, 5, 12 устанавливаются три режима работы устройства.

В первом режиме после записи соответствующих элементов векторов А и В в регистры 1 и 2 выполняется функция в блоке 3 и результат операции, пройдя через мультиплексоры 4 и 5, фиксируется в регистрах 6 и 7 стробом с регистра 15 Содержимое регистров 6 и 7 перемножается на умножителе 9 и записывается в буферный регистр 11 стробом со сдвигового регистра 15. Содержимое регистра 11 через мультиплексор 12 поступает в сумматор 13 и результат выполненной операции записывается в регистр результата 14. Тем самым реализуется первая указанная функция устройства. Во втором режиме после записи в регистры 1 и 2 соответствующих элементов векторов А и В информация через мультиплексоры 4 и 5 перезаписывается в регистры 6 и 7 Далее порядок вычислений тот же что и в первом случае. Так реализуется вторая функция устройства. В третьем режиме после записи соответствующих элементов векторов А и В в регистры 1 и 2 выполняется предписанная функция в блоке 3 и результат операции подается на вход сумматора единиц 8, информация с выхода которого фиксируется в буферном регистре 10 стробом с регистра 15. Выход регистра 10 через мультиплексор 12 подается на вход сумматора 13 и фиксируется в регистре 14 стробом с регистра 15.

В этом режиме реализуется третья функция работы устройства

Векторы А и В подаются на вход устройства последовательно, а на выходе регистра 14 формируется результат выбранной функции обработки векторов.

Изобретение позволяет повысить быстродействие устройства при выполнении

операций типа 2) ОЧ3 - bi))2 2l а , b, ,

которое достигается преимущественно за счет применения конвейерной обработки элементов векторов и расширить функцио

нальные возможности устройства за счет реализации функции ЈЛ (ai, bi), где а и Ь, i 0

соответствующие элементы первого и второго векторов, имеющие разрядность N;

f(ah bi)- произвольная простейшая функция двух аргументов; 2/i - функция бинарной корреляции двух векторов.

Формула изобретения Устройство для обработки векторов,

содержащее первый и второй входные регистры, регистр выбора функции, арифметико-логический блок, четыре буферных регистра, регистр результата и регистр сдвига, первый и второй выходы которого

соединены соответственно с управляющими входами первого, второго, третьего и четвертого буферных регистров, причем входы первого и второго операндов устройства соединены соответственно с информационными входами первого и второго входных регистров, выходы которых соединены соответственно с входами первого и второго операндов арифметико-логического узла, вход кода операции устройства соединен с

входом регистра выбора функции, выход регистра результата соединен с выходом результата устройства, первый вход синхронизации которого соединен с входом синхронизации первого входного регистра вход

запуска регистра сдвига и вход синхронизации второго входного регистра соединены с вторым входом синхронизации устройства, управляющий вход регистра результата соединен с третьим выходом регистра сдвига,

отличающееся тем, что, с целью повышения быстродействия при выполнении

п

над векторами операций типа Ј ( (а - bi)) ,

i 0

П

2a i bi, а также расширения функциональ 0

ных возможностей за счет вычисления фун- п

кций .if(ai bi) (где ai и bi - соответствующие

i 0

элементы первого и второго векторов, имеющие разрядность N;f(ai, bi)- произвольная простейшая функция двух аргументов; 2i - функция бинарной корреляции двух векторов, в него введены три мультиплексора, сумматор единиц, умножитель и сумматор, причем информационный вход регистра результата соединен с выходом сумматора, входы младших разрядов первого слагаемого которого соединены с выходом первого мультиплексора, первый и второй информационные входы которого соединены соответственно с выходом значащих разрядов третьего и выходом четвертого буферных регистров, информационный вход третьего буферного регистра соединен с выходом умножителя, первый и второй информацион- ные входы которого соответственно соединены с выходами первого и второго буферных регистров информационные входы которых соответственно соединены с выходами второго и третьего мультиплексоров, первые информационные входы которых соответственно соединены с выходами первого и второго входных регистров, первый выход регистра выбора функции соединен с входом задания режима работы арифметико-логического узла, выход которого соединен с вторыми информационными входами второго и третьего мультиплексоров и входом сумматора единиц, выход которого соединен с информационным входом четвертого буферного регистра, управляющие входы второго и третьего мультиплексоров соединены с вторым выходом регистра выбора функции,

третий выход которого соединен с управляющим входом первого мультиплексора, выход регистра результата соединен с входом второго слагаемого сумматора, входы старших разрядов первого слагаемого которого

соединены с выходом знакового разряда третьего буферного регистра.

Авторы

Даты

1992-09-23—Публикация

1990-07-19—Подача