двоичный код, блок 6 сдвига влево, четыре мультиплексора 18.1, 18.2, 19i и 20, восемь блоков 8-15 буферных регистров, два коммутатора 21.1 и

21.2, преобразователь 16 дополнительного кода в прямой код, арифметический блок 7 порядков и элемент ИЛИ 17 с соответствующими связями. 22 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| Операционное устройство | 1985 |

|

SU1367012A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1336029A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Устройство для деления чисел с фиксированной запятой | 1986 |

|

SU1451682A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Арифметическое устройство | 1986 |

|

SU1363186A1 |

Изобретение относится к вычислительной технике и позволяет обрабатывать данные, представленные в различных форматах. Целью изобретения является повышение производительности. Арифметическое устройство содержит блок 1 местной памяти, умножитель 2, блок 3 сдвига вправо, арифметико-логический блок 4 мантисс, преобразователь 5.количества старших нулей в (Л Фиг. /

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных быстродействующих вычислительных устройств.1

Целью изобретения является повышение производительности.

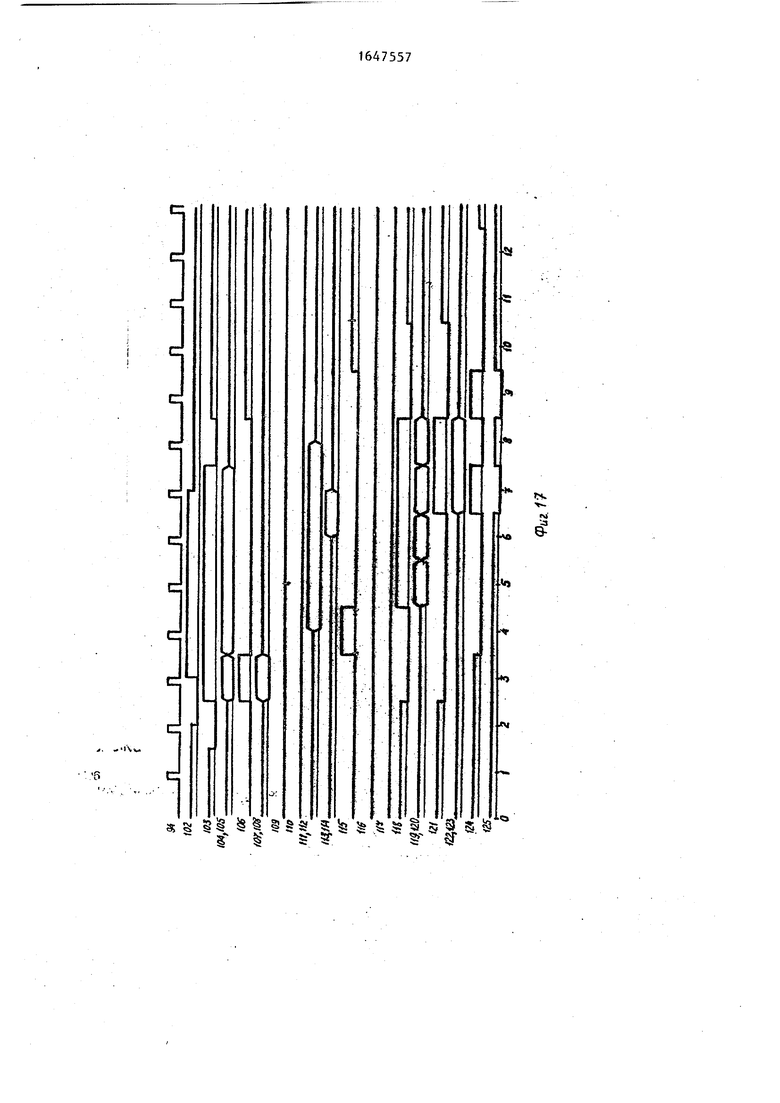

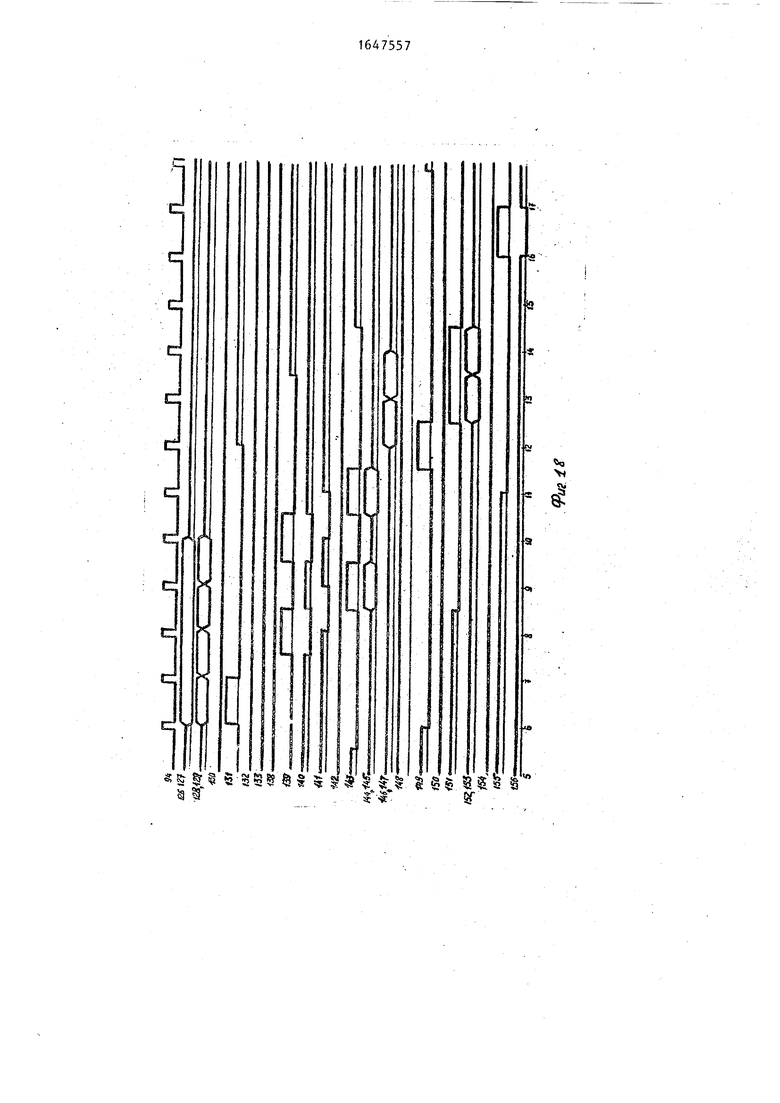

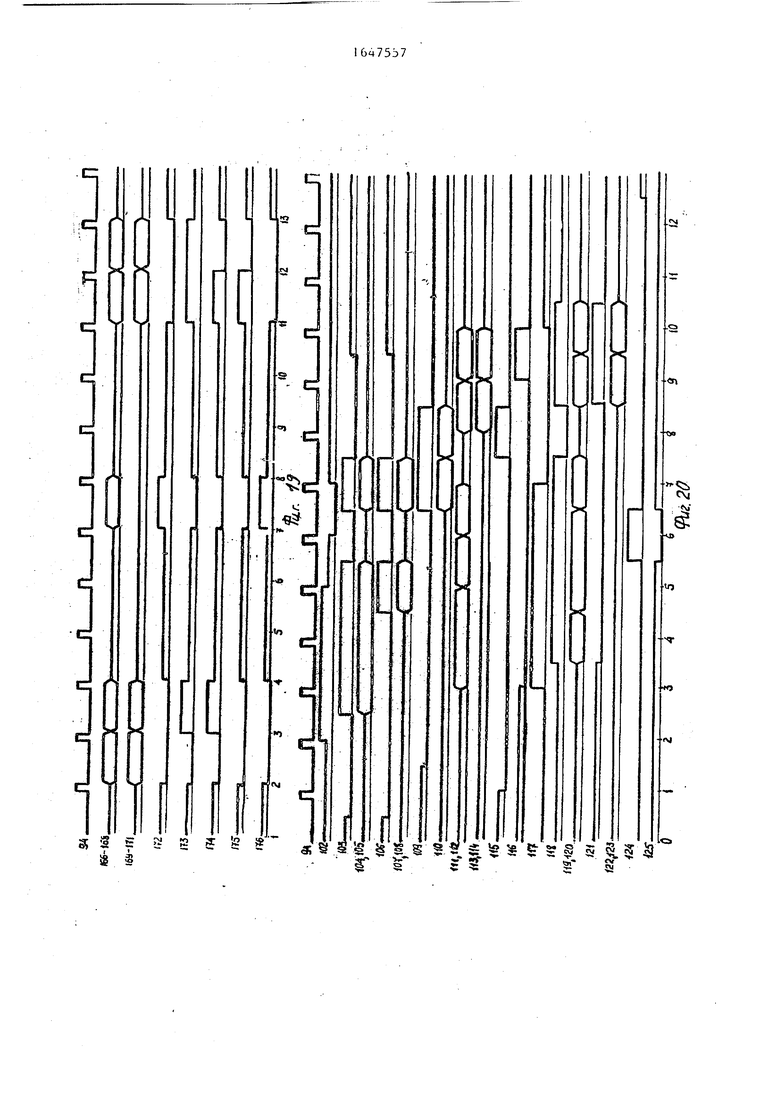

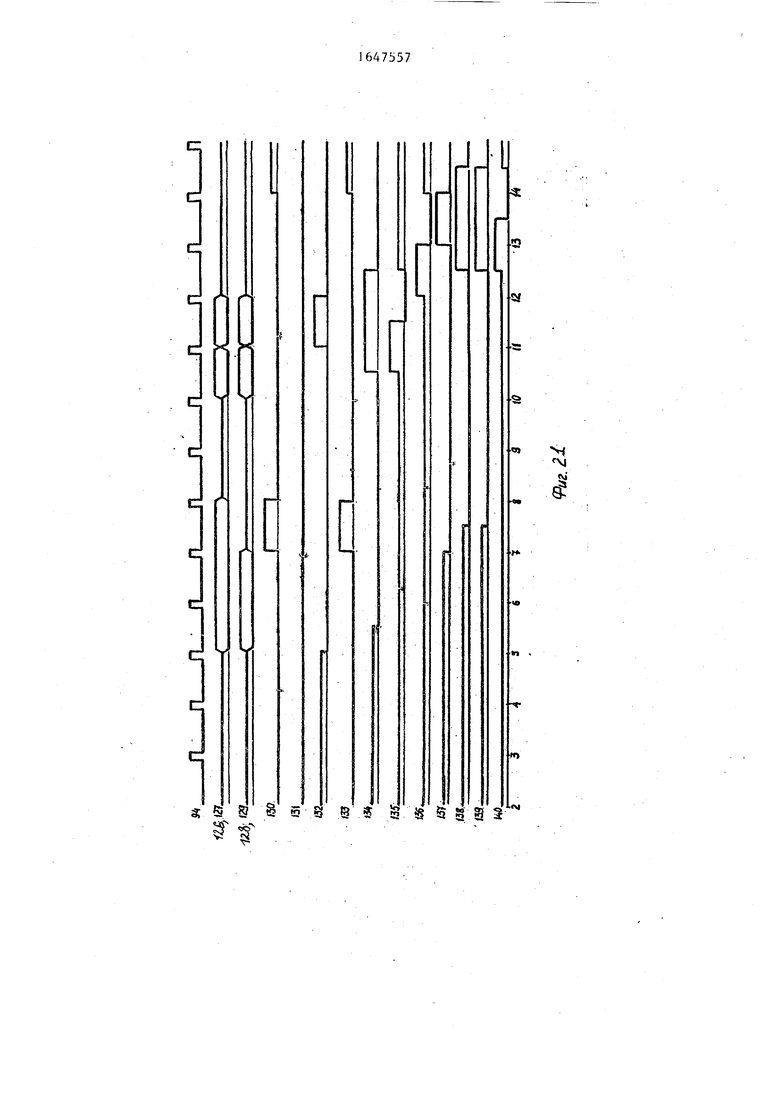

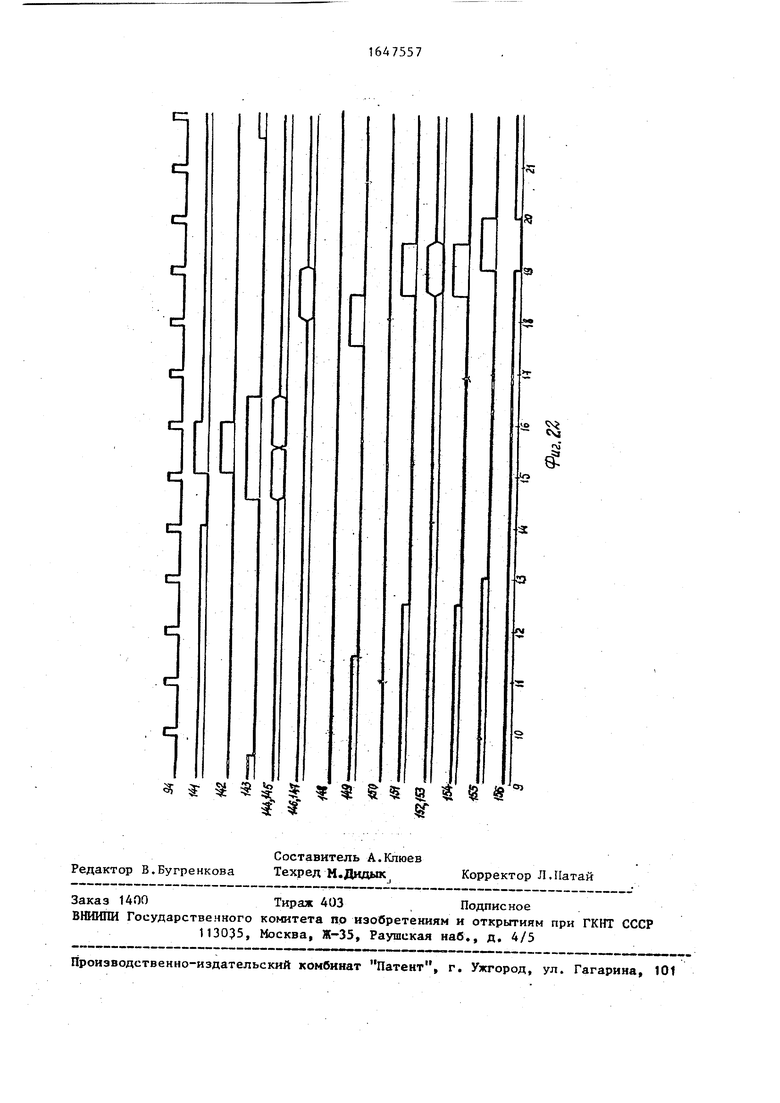

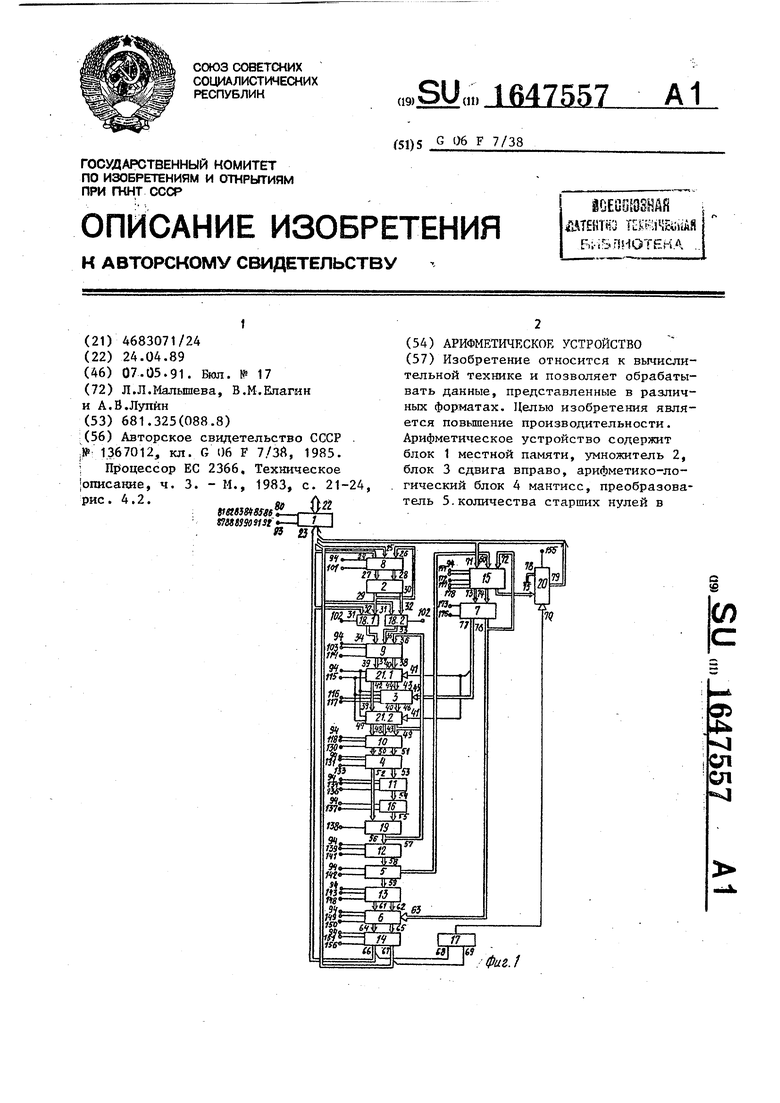

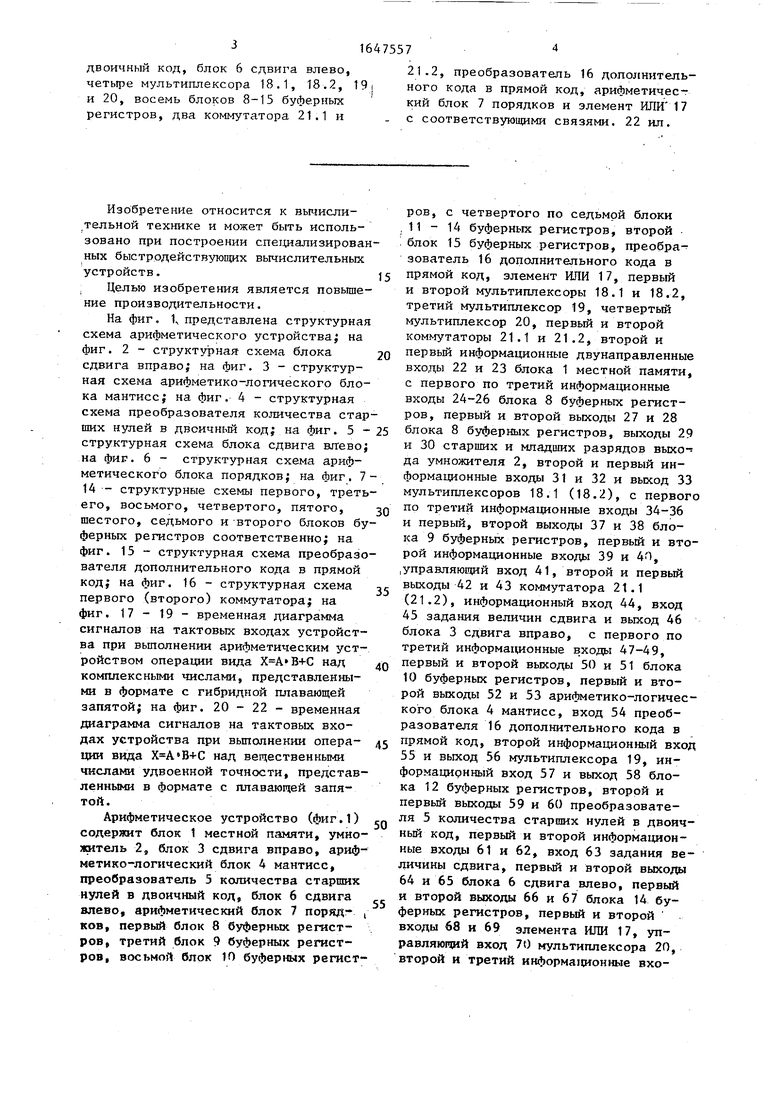

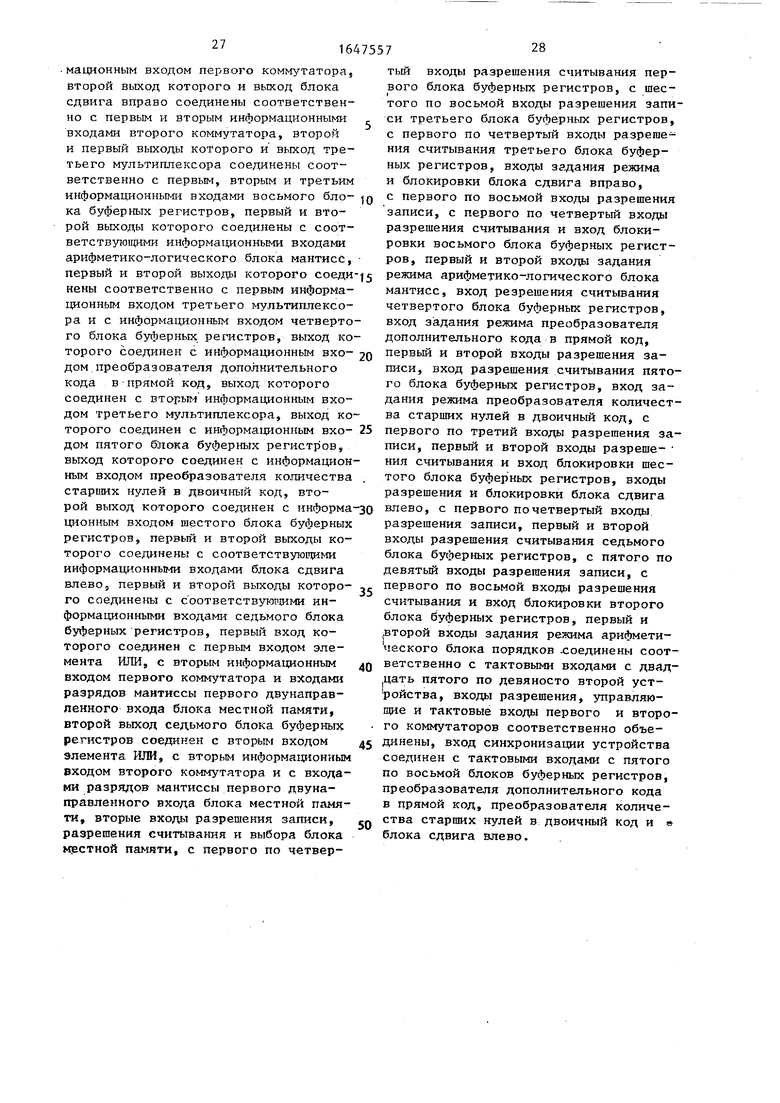

На фиг. 1, представлена структурная схема арифметического устройства; на фиг. 2 - структурная схема блока 2 сдвига вправо; на фиг. 3 - структурная схема арифметико-логического блока мантисс; на фиг. 4 - структурная схема преобразователя количества старших нулей в двоичный код; на фиг. 5-2 структурная схема блока сдвига влево; на фиг. 6 - структурная схема арифметического блока порядков; на фиг. 7- 14 - структурные схемы первого, третьего, восьмого, четвертого, пятого, шестого, седьмого и второго блоков буферных регистров соответственно; на фиг. 15 - структурная схема преобразователя дополнительного кода в прямой код; на фиг. 16 - структурная схема первого (второго) коммутатора; на фиг. 17 - 19 - временная диаграмма сигналов на тактовых входах устройства при выполнении арифметическим устройством операции вида над комплексными числами, представленными в формате с гибридной плавающей запятой; на фиг. 20 - 22 - временная диаграмма сигналов на тактовых входах устройства при выполнении опера- ции вида над вещественными числами удвоенной точности, представленными в формате с плавающей запятой.

Арифметическое устройство (фиг.1) содержит блок 1 местной памяти, умножитель 2, блок 3 сдвига вправо, арифметико-логический блок 4 мантисс, преобразователь 5 количества старших нулей в двоичный код, блок 6 сдвига влево, арифметический блок 7 поряд- , ков, первый блок 8 буферных регистров, третий блок 9 буферных регистров, восьмой блок 10 буферных регистров, с четвертого по седьмой блоки ,11 - 14 буферных регистров, второй блок 15 буферных регистров, преобразователь 16 дополнительного кода в прямой код, элемент ИЛИ 17, первый и второй мультиплексоры 18.1 и 18.2, третий мультиплексор 19, четвертый мультиплексор 20, первый и второй коммутаторы 21.1 и 21.2, второй и первый информационные двунаправленные входы 22 и 23 блока 1 местной памяти, с первого по третий информационные входы 24-26 блока 8 буферных регистров, первый и второй выходы 27 и 28 блока 8 буферных регистров, выходы 29 и 30 старших и младших разрядов выхо- да умножителя 2, второй и первый информационные входы 31 и 32 и выход 33 мультиплексоров 18.1 (18.2), с первог по третий информационные входы 34-36 и первый, второй выходы 37 и 38 блока 9 буферных регистров, первый и второй информационные входы 39 и 40, управляющий вход 41, второй и первый выходы 42 и 43 коммутатора 21.1 (21.2), информационный вход 44, вход 45 задания величин сдвига и выход 46 блока 3 сдвига вправо, с первого по третий информационные входы 47-49, первый и второй выходы 50 и 51 блока 10 буферных регистров, первый и второй выходы 52 и 53 арифметико-логического блока 4 мантисс, вход 54 преобразователя 16 дополнительного кода в прямой код, второй информационный вхо 55 и выход 56 мультиплексора 19, ин- формацирнный вход 57 и выход 58 блока 12 буферных регистров, второй и первый выходы 59 и 60 преобразователя 5 количества старших нулей в двоичный код, первый и второй информационные входы 61 и 62, вход 63 задания величины сдвига, первый и второй выходы 64 и 65 блока 6 сдвига влево, первый и второй выходы 66 и 67 блока 14 буферных регистров, первый и второй входы 68 и 69 элемента ИЛИ 17, управляющий вход 70 мультиплексора 20, второй и третий информационные входы 71 и 72, с первого по третий выходы 73 - 75 блока 15 буферных регистров, второй и первый выходы 76 к 77 арифметического блока 7 порядков, первый информационный вход 78 и выход 79 мультиплексора 20, входы 80-83 разрядов первого адресного входа, входы 84-87 разрядов второго адресного входа, первый вход 88 разрешения записи, первый вход 89 разрешения считывания, первый вход 90 выбора, второй вход 91 разрешения записи, второй вход 92 разрешения считывания и второй вход 93 выбора блока 1 местной памяти, вход 94 синхронизации устройства, с первого по третий входы 95-97 разрешения записи и с первого по четвертый входы 98-101 разрешения считывания блока 8 буферных регистров, управляющий вход 102 мультиплексора 18.1 (18.2), с первого по восьмой входы 103-110 разрешения записи и с первого по четвертый входы 111-114 разрешения считывания блока 9 буферных регистров, вход 115 разрешения коммутатора 21.1 (21.2), вход 116 задания режима и вход 117 блокировки блока 3 сдвига вправо, с первого по

восьмой входы 118-125 разрешения запи- 30 ционным входом мультиплексора 190,

си, с первого по четвертый входы 126- 129 разрешения считывания и вход 130 блокировки блока 10 буферных регистров, вход 131 задания вида операции, первый и второй входы 132 и 133 задания режима арифметико-логического блока 4 мантисс, первый и второй входы 134 и 135 разрешения записи и выход 136 разрешения считывания блока 11 буферных регистров, вход 137 задания режима преобразователя 16 дополнительного кода в прямой код, управляющий вход 138 мультиплексора 19, первый и второй входы 139 и,140 разрешевыход 183 (разряды 1-10) - с вторым информационным входом мультиплексора 190, выход 184 (разряды 3-14) - с первыми входами элементов ИЛИ 188

,5 группы, выход 185 (разряды 1-14) - с первым информационным входом мультиплексора 189, второй информационный вход мультиплексора 189 соединен с входом нулевого потенциала устройст40 ва, выход мультиплексора 189 соединен с первым информационным входом мультиплексора 192, выход мультиплексора 190 соединен с информационным входом регистра 187, выход которого сое- ния записи и выход 141 разрешения счи- 45 динен с вторыми входами элементов ИЛИ тывания блока 12 буферных регистров, 188 группы, выходы с первого по деся- вход 142 задания режима преобразова- тый разрядов выхода регистра 187 сое.- теля 5 количества старших нулей в дво- динены с входами соответствующих раз- ичный код, с первого по третий входы рядов второго информационного входа 143-145 разрешения записи, первый и 50 мультиплексора 191, первый информаци- второй входы 146 и 147 разрешения счи- онный вход и выход которого соединены тывания и вход 148 блокировки блока 13 буферных регистров, вход 149 разрешения и вход 150 блокировки блока 6 сдвига впево, с первого по четвертый 55 входы 151-154 разрешения записи, первый и второй входы 155-156 разрешения считывания блока 14 буферных реги- .с тров, с первого по девятый входы 157с выходами элементов ИЛИ 188 группы и с входами младших разрядов второго информационного входа мультиплексора 192, входы двух старших разрядов вторых информационных входов мультиплексоров 190-192 соединены с входом нулевого потенциала устройства, выход мультиплексора 192 является выходом 46

165 разрешения записи, с первого по шестой входы 166-171 разрешения считывания и вход 172 блокировки блока 15 буферных регистров, вход 173 задания вида операции, первый и второй входы 174 и 175 задания режима и вход 176 переноса арифметического блока 7 порядков, седьмой и восьмой входы 177

и 178 разрешения считывания блока 15 буферных регистров.

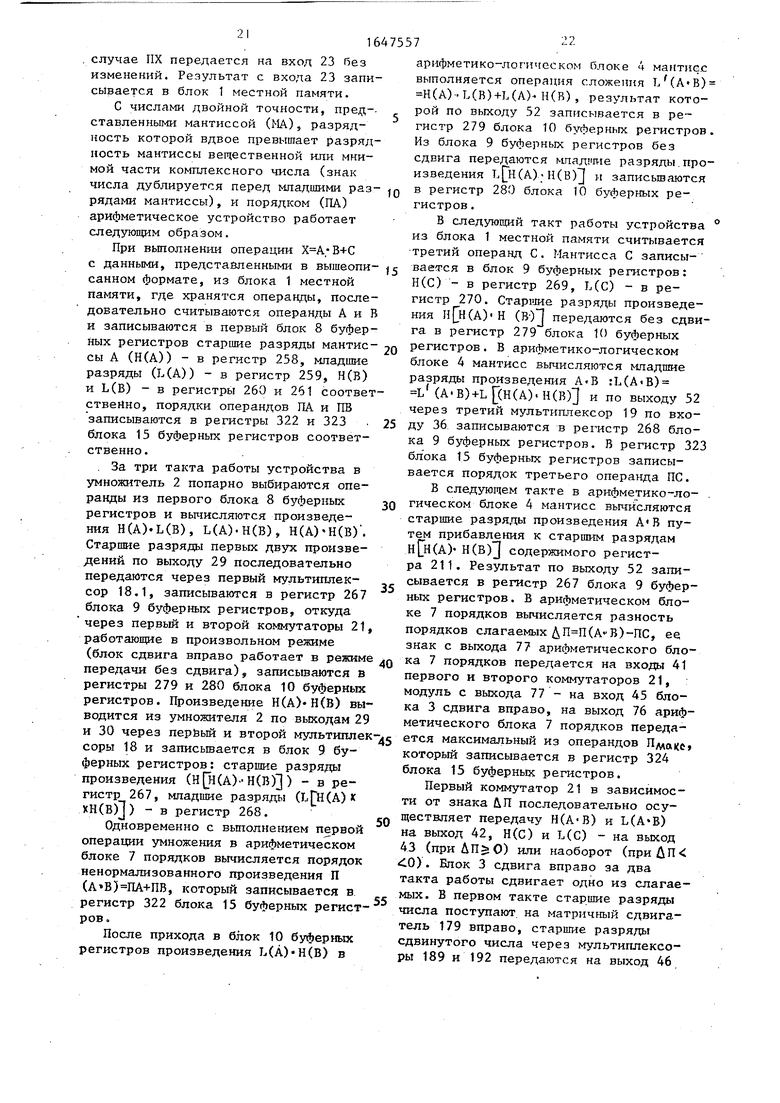

Блок 3 сдвига вправо (фиг.2) содер- ° жит матричный сдвигатель 179 вправо, управляющий вход 180 матричного сдви5 гателя 179 вправо, группу элементов И 181, выходы 182-185 разрядов выхода матричного сдвигателя 179 вправо, регистр 186 управляющей информации, регистр 187, группу элементов ИЛИ 188,

0 мультиплексоры 189-192, элементы И 193 и 194, элементы НЕ 195 и 196, информационный вход 197 матричного сдвигателя 179 вправо, причем вход знакового разряда входа 44 соединен с выхо5 дом знакового разряда выхода 46, входы значащих разрядов входа 44 соединены с входом 197, выход 182 (разряды 15-26 выхода матричного сдвигателя 179 вправо) соединен с первым информавыход 183 (разряды 1-10) - с вторым информационным входом мультиплексора 190, выход 184 (разряды 3-14) - с первыми входами элементов ИЛИ 188

группы, выход 185 (разряды 1-14) - с первым информационным входом мультиплексора 189, второй информационный вход мультиплексора 189 соединен с входом нулевого потенциала устройства, выход мультиплексора 189 соединен с первым информационным входом мультиплексора 192, выход мультиплексора 190 соединен с информационным входом регистра 187, выход которого сое- динен с вторыми входами элементов ИЛИ 188 группы, выходы с первого по деся- тый разрядов выхода регистра 187 сое.- динены с входами соответствующих раз- рядов второго информационного входа мультиплексора 191, первый информаци- онный вход и выход которого соединены

с выходами элементов ИЛИ 188 группы и с входами младших разрядов второго информационного входа мультиплексора 192, входы двух старших разрядов вторых информационных входов мультиплексоров 190-192 соединены с входом нулевого потенциала устройства, выход мультиплексора 192 является выходом 46

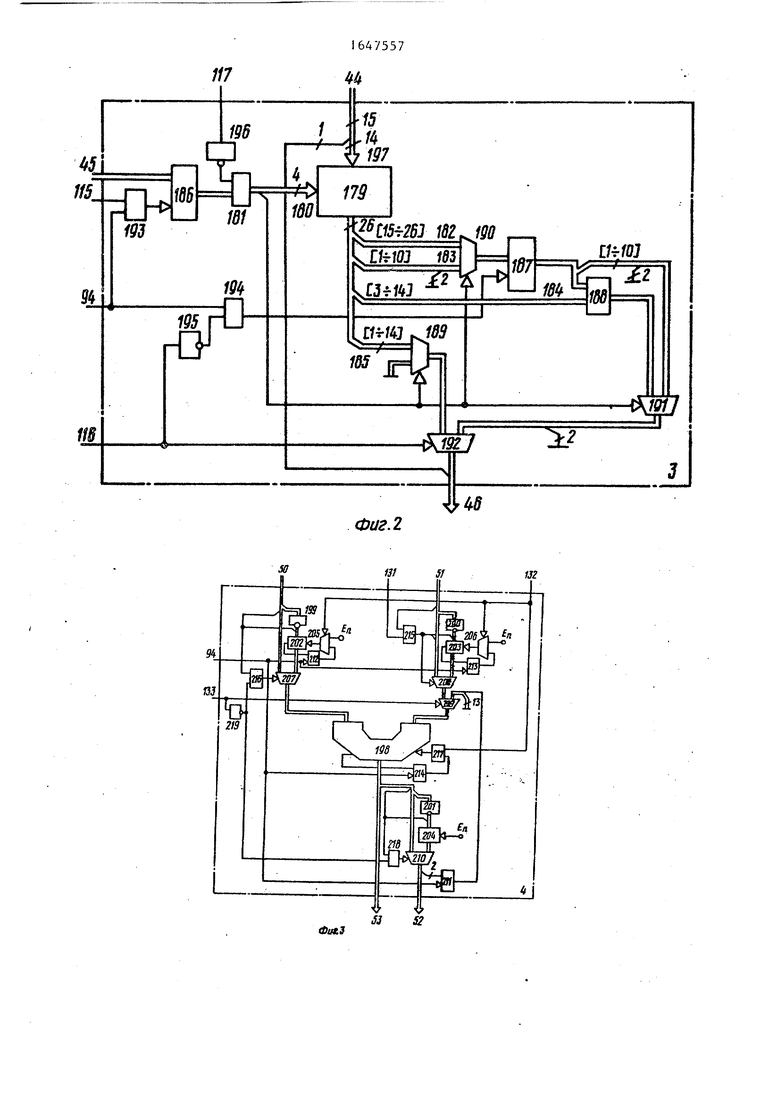

блока 3 сдвига вправо, выход регистра 186 управляющей информации соединен с первыми входами элементов И 181 группы, выход старшего элемента И 181 группы соединен с управляющими входами мультиплексоров 189 - 191, выходы младших элементов И 181 группы соединены с управляющим входом 180 матричного сдвигателя 179 вправо, вход 94 соединен с первыми входами элементов И 193 и 194, вход 115 соединен с вторым входом элемента И 193, выход которого соединен с входом разрешения записи регистра 186, вход 116 соеди- нен с управляющим входом мультиплексора 192 и через элемент НЕ 195 соединен с вторым входом элемента И 194, выход которого соединен с входом разрешения записи регистра 187, вход 117 через элемент НЕ 196 соединен с вторыми входами элементов И 181 группы. Арифметико-логический блок 4 мантисс (фиг. 3) содержит сумматор 198, с первой по третью группы элементов НЕ 199-201, с первого по третий узлы 202 204 прибавления переноса, с первого по шестой мультиплексоры 205 - 210, . регистр 211, с первого по третий триггеры 212 - 214, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 215, с первого по третий элементы И 216 - 218, элемент НЕ 219, причем вход 50 соединен с первым информационным входом мультиплексора 207, вход знакового разряда входа 50 соеди нен с первым входом элемента И 216 и с входом знакового разряда информационного входа узла 202 прибавления переноса, входы значащих разрядов входа 50 через элементы НЕ 199 группы соединены с входами разрядов информационного входа узла 202 прибавления переноса, вход знакового разряда входа 51 соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 215, входы знача- щих разрядов входа 51 соединены с первым информационным входом мультиплексора 208 и через элементы НЕ 200 группы - с входами соответствующих разрядов узла 203 прибавления перено- са, выход которого и выход узла 202 прибавления переноса соединены с вторыми информационными входами мультиплексоров 208 и 207 соответственно, выходы переноса из третьего числового разряда узлов 202 и 203 прибавления переноса соединены с информационными входами триггеров 212 и 213 соответственно, выходы которых соединены с вторыми информационными входами мультиплексоров 205 и 206 соответственно, первые информационные входы мультиплексоров 205 и 206 соединены с входом единичного потенциала устройства, а выходы их соединены с входами переноса узлов 202 и 203 прибавления переноса соответственно, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 215 соединен с входами знаковых разрядов первого информационного входа мультиплексора 208 и информационного входа узла 203 прибавления переноса, с управляющим входом мультиплексора 208, выход элемен- ;та И 216 соединен с управляющим входом мультиплексора 207, выход мультиплексора 207 соединен с входом первого слагаемого сумматора 198, выход мультиплексора 208 соединен с первым информационным входом мультиплексора

209,выход которого соединен с входом второго слагаемого сумматора 198, выход суммы сумматора 198 является выходом 53 арифметико-логического блока мантисс и соединен с первым информа-- ционным входом мультиплексора 210, выход знакового разряда выхода суммы сумматора 193 соединен с первым входом элемента И 218 и с входом знакового разряда информационного входа узла 204 прибавления переноса, выходы значащих разрядов выхода суммы сумматора 198 соединены через соответствующие элементы НЕ 201 группы с входами соответствующих разрядов информационного входа узла 204 прибавления переноса, вход переноса которого соединен с входом единичного потенциала устройства, выход переноса из третьего значащего разряда выхода суммы сумматора 198 соединен с информационным входом триггера 214, выход которого соединен с первым входом элемента И 217, выход элемента И 217 соединен

с входом переноса в младший разряд сумматора 198, выход узла 204 прибавления переноса соединен с вторым информационным входом мультиплексора .

210,выход которого является выходом 52 арифметико-логического блока мантисс, выходы двух старших числовых разрядов выхода мультиплексора 210 соединены с информационным входом регистра 211, выход элемента И 218 соединен с управляющим входом мультиплексора 210, выход регистра 211 соединен с входами младших разрядов второго информационного входа мультиплексора 209, входы стартчих разрядов второго информационного входа мультиплексора 209 соединены с входом нулевого потенциала устройства, вход 131 соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 215, вход 94 соединен с входами разрешения записи регистра 211 и триггеров 212-214, вход 132 соединен с вторым входом элемента И 217, с уп- . Q равляющими входами мультиплексоров 205 и 206, вход 133 соединен с управляющим входом мультиплексора 209, через элемент НЕ 219 - с вторыми входами элементов И 216 и 218.

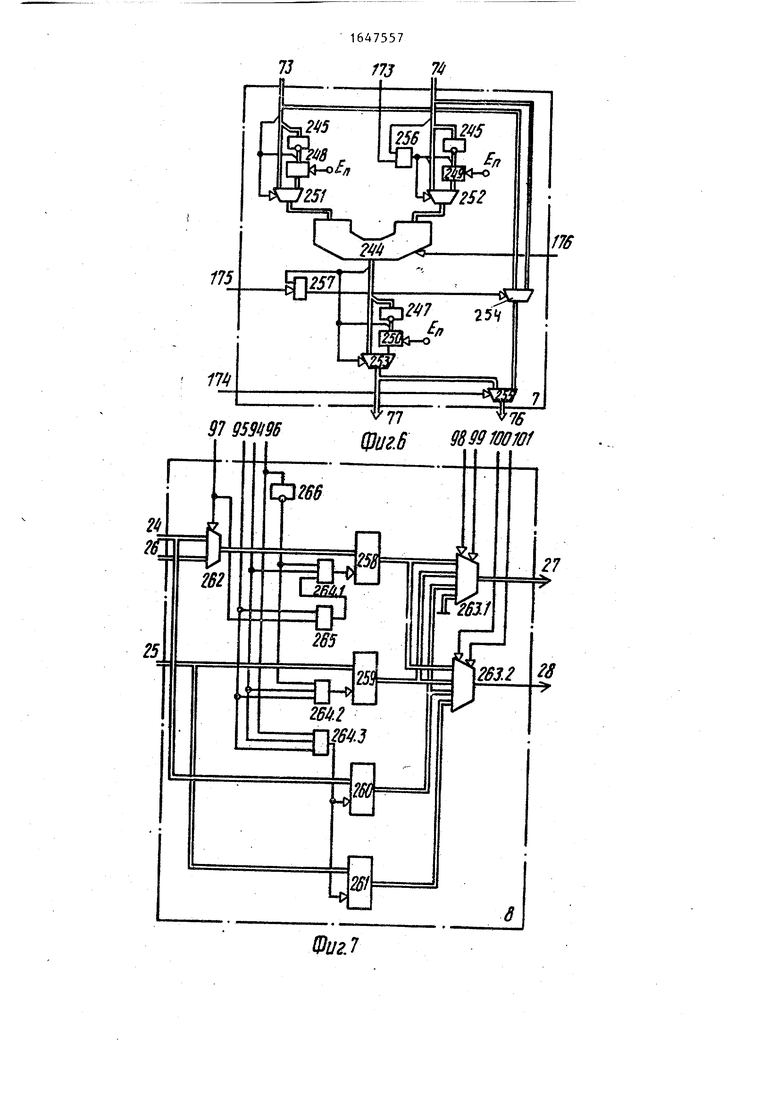

Преобразователь 5 количества старших нулей в двоичный код (фиг. 4) содержит группу шифраторов 220, каждый из которых содержит элементы НЕ 221, элементы И 222, элемент И-НК 223, элемент И 224 и элемент И-НЕ 225, группу элементов И 226, группу элементов И 227, элемент ИЛИ 228, коммутатор 229, элемент НЕ 230, элемент И-КЕ 231, группу элементов ИЛИ 232, вход 233 знакового разряда входа 58, триггер 234, причем вход 233 соединен с выходом знакового разряда выхода 59, входы значащих разрядов входа 58 соединены с информационным входом коммутатора 229, выходы разрядов выхода которого соединены . с выходами соответствующих разрядов выхода 59 и соответственно с входами разрядов входов шифраторов 220 группы, выход восьмого элемента И 226 группы соединен с информационным вхо- дом триггера 234, выход которого соединен с первым входом элемента И-НЕ 231, выход которого соединен с первыми входами элементов И 227 группы, вторые входы которых соединены соответственно с выходом третьего элемента И 226 группы и выходами элементов ИЛИ 232 группы,, выходы элементов И 227 группы являются выходами разрядов выхода 60, вход 94 соединен с первым входом элемента И 228, выход которого соединен с входом разрешения записи триггера 234, вход 142 соединен с управляющим входом коммутатора 229, с вторым входом элемента И-НЕ 231 и через элемент НЕ 230 - с вторым входом элемента И 228.

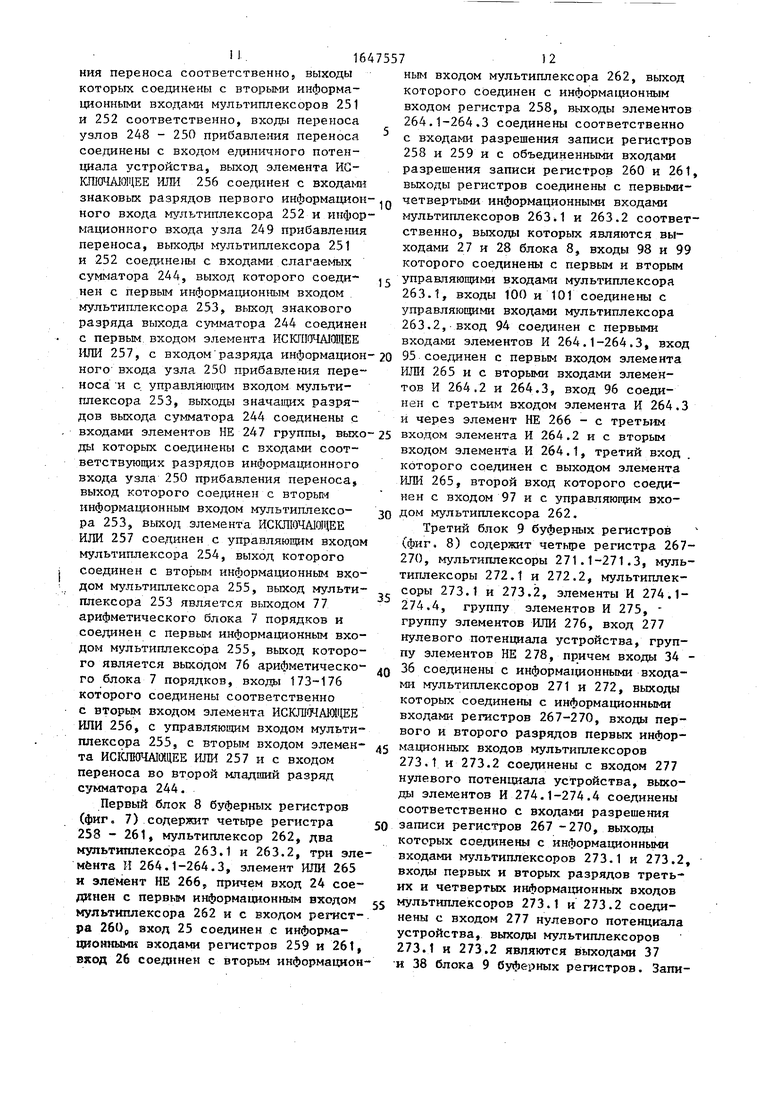

Блок 6 сдвига влево (фиг. 5) содержит матричный сдвигатель 235 влево, регистр 236 управляющей информации, группу элементов И 237, мультиплексор 238, элемент И 239 и элемент

J5

20

25

45

-

50

55

30

35

40

Q

НЕ 240, причем вход -знакового разряда входа 61 соединен с выходами знаковых разрядов выходов 64 и 65, входы значащих разрядов входов 61 и 62 соединены соответственно с входами старших и младших разрядов информационного входа сдвнгателя 235, выходы 241 (разрядов 1-12), 242 (разрядов 3-14) и 243 (разрядов 13-24) выхода сдвига- теля 235 соединены соответственно с входами разрядов первого и второго информационных входов мультиплексора 238 и с выходами значащих разрядов

5 выхода 65, вход 63 соединен с информационным входом регистра 236, выходы разрядов которого соединены с первыми входами элементов И 237 группы, выходы которых соединены с входами

0 разрядов управляющего входа сдвигате- ля 235, выходы разрядов мультиплексора 238 являются выходами значащих .разрядов выхода 64, выходы 94 и 149 соединены с первым и вторым входами

5 элемента И 239, выход которого соединен с входом разрешения записи регистра 236, вход 150 соединен через элемент НЕ 240 с вторыми входами элементов И 237 и с управляющим входом мультиплексора 238.

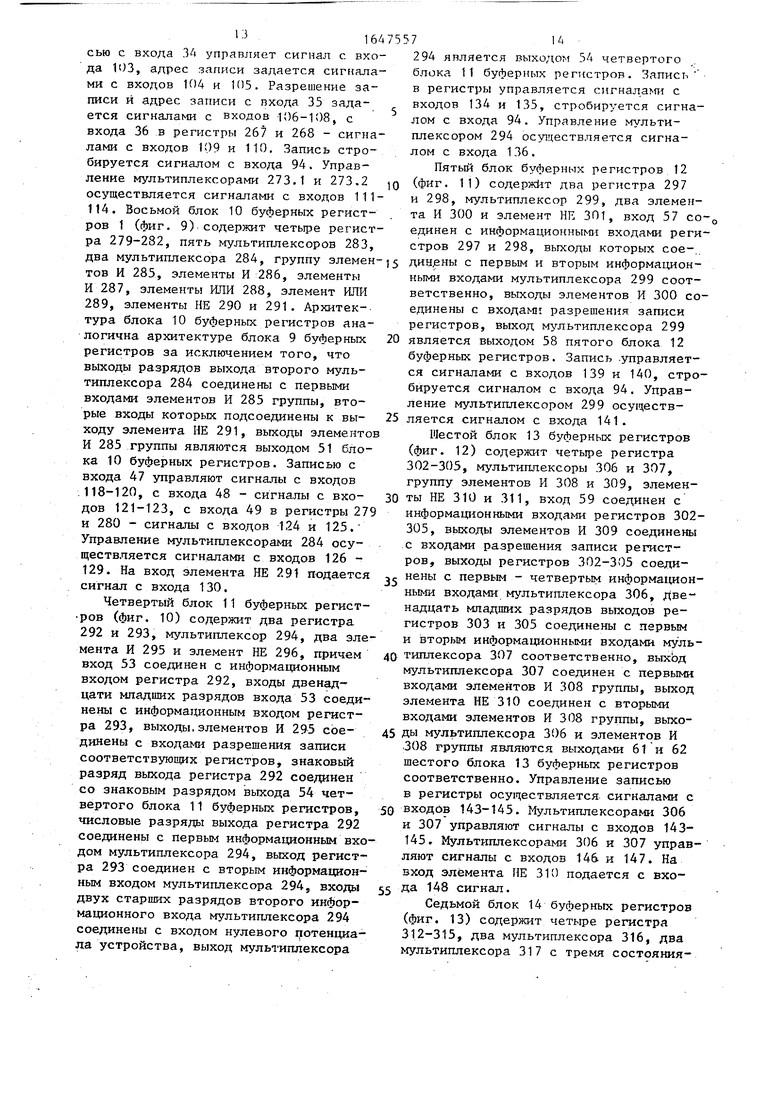

Арифметический блок 7 порядков (фиг. 6) содержит сумматор 244, с первой по третью группы элементов НЕ 245 - 247, с первого по третий узлы 248 - 250 прибавления переноса, с первого по пятый мультиплексоры 251 - 255, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 256 и 257, причем вход 73 соединен с первыми информационными входами мультиплексоров 251 и 254, вход его знакового разряда соединен с входом знакового разряда информационного входа узла 248 прибавления переноса и с управляющим входом муль5 типлексора 251, входы числовых разрядов входа 73 соединены с входами элементов НЕ 245 группы, вход 74 соединен с вторым информационным входом

мультиплексора 254, вход знакового

0 разряда входа 74 соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 256, входы значащих разрядов входа 74 соединены с входами соответствующих разрядов первого информационного входа

5 мультиплексора 252 и с входами элементов НЕ 246 группы, выходы элементов НЕ 245 и 246 групп соединены со входами значащих разрядов информационными входами узлов 248 и 249 прнбавле0

5

0

ния переноса соответственно, выходы которых соединены с вторыми информационными входами мультиплексоров 251 и 252 соответственно, входы переноса узлов 248 - 250 прибавления переноса соединены с входом единичного потенциала устройства, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 256 соединен с входами

знаковых разрядов первого информацион- -д четвертыми информационными входами кого входа мультиплексора 252 и инфор- мультиплексоров 263.1 и 263.2 соответ- мационного входа узла 249 прибавления переноса, выходы мультиплексора 251 и 252 соединены с входами слагаемых

15

сумматора 244, выход которого соединен с первым информационным входом мультиплексора 253, выход знакового разряда выхода сумматора 244 соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ

ственно, выходы которых являются выходами 27 и 28 блока 8, входы 98 и 99 которого соединены с первым и вторым управляющими входами мультиплексора

ИЛИ 257, с входом разряда информацион-20 95 соединен с первым входом элемента ного входа узла 250 прибавления пере- ИЛИ 265 и с вторыми входами элемен- носа и с управляющим входом мульти- тов И 264.2 и 264.3, вход 96 соеди- плексора 253, выходы значащих разря- иен с третьим входом элемента И 264.3 дов выхода сумматора 244 соединены с и через элемент НЕ 266 - с третьим входами элементов НЕ 247 группы, выхо-25 входом элемента И 264.2 и с вторым ды которых соединены с входами соответствующих разрядов информационного входа узла 250 прибавления переноса, выход которого соединен с вторым информационным входом мультиплексовходом элемента И 264.1, третий вход которого соединен с выходом элемента ИЛИ 265, второй вход которого соединен с входом 97 и с управляющим вхо- 30 Дом мультиплексора 262.

ра 253, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 257 соединен с управляющим входом мультиплексора 254, выход которого соединен с вторым информационным входом мультиплексора 255, выход мультиплексора 253 является выходом 77 арифметического блока 7 порядков и соединен с первым информационным входом мультиплексора 255, выход которого является выходом 76 арифметического блока 7 порядков, входы 173-176 которого соединены соответственно с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 256, с управляющим входом мультиплексора 255, с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 257 и с входом переноса во второй младший разряд сумматора 244.

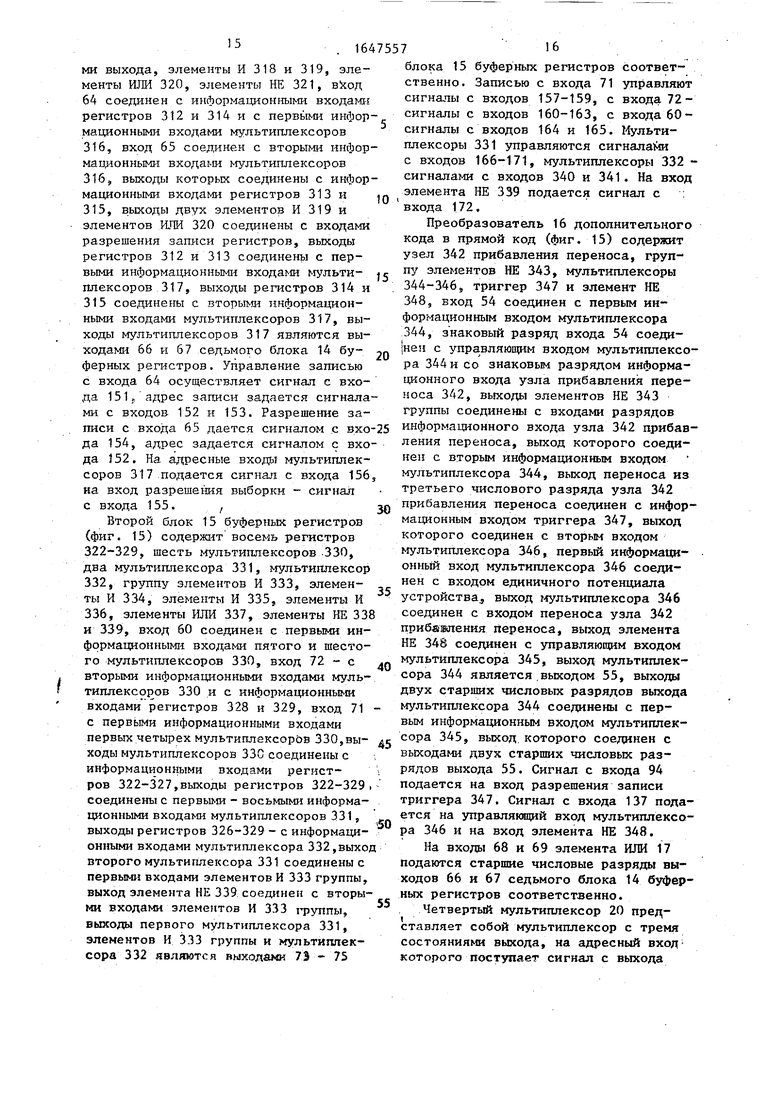

Первый блок 8 буферных регистров (фиг. 7) содержит четыре регистра 258 - 261, мультиплексор 262, два мультиплексора 263.1 и 263.2, три элемента И 264.1-264.3, элемент ИЛИ 265 и элемент НЕ 266, причем вход 24 соединен с первым информационным входом мультиплексора 262 и с входом регистра 260„ вход 25 соединен с информационными входами регистров 259 и 261, вход 26 соединен с вторым информацнонным входом мультиплексора 262, выход которого соединен с информационным входом регистра 258, выходы элементов 264.1-264.3 соединены соответственно с входами разрешения записи регистров 258 и 259 и с объединенными входами разрешения записи регистров 260 и 261, выходы регистров соединены с первымичетвертыми информационными входами мультиплексоров 263.1 и 263.2 соответ

ственно, выходы которых являются выходами 27 и 28 блока 8, входы 98 и 99 которого соединены с первым и вторым управляющими входами мультиплексора

95 соединен с первым входом элемента ИЛИ 265 и с вторыми входами элемен- тов И 264.2 и 264.3, вход 96 соеди- иен с третьим входом элемента И 264.3 и через элемент НЕ 266 - с третьим входом элемента И 264.2 и с вторым

входом элемента И 264.1, третий вход которого соединен с выходом элемента ИЛИ 265, второй вход которого соединен с входом 97 и с управляющим вхо- Дом мультиплексора 262.

5

Третий блок 9 буферных регистров (фиг. 8) содержит четыре регистра 267- 270, мультиплексоры 271.1-271.3, мультиплексоры 272.1 и 272.2, мультиплексоры 273.1 и 273.2, элементы И 274.1- 274.4, группу элементов И 275, - группу элементов ИЛИ 276, вход 277 нулевого потенциала устройства, группу элементов НЕ 278, причем входы 34 - 0 36 соединены с информационными входами мультиплексоров 271 и 272, выходы которых соединены с информационными входами регистров 267-270, входы первого и второго разрядов первых информационных входов мультиплексоров 273.1 и 273.2 соединены с входом 277 нулевого потенциала устройства, выходы элементов И 274.1-274.4 соединены соответственно с входами разрешения записи регистров 267 -270, выходы которых соединены с информационными входами мультиплексоров 273.1 и 273.2, входы первых и вторых разрядов третьих и четвертых информационных входов мультиплексоров 273.1 и 273.2 соединены с входом 277 нулевого потенциала устройства, выходы мультиплексоров 273.1 и 273.2 являются выходами 37 и 38 блока 9 буферных регистров. Запи5

0

5

1 3164

сью с входа 34 управляет сигнал с входа 103, адрес записи задается сигналами с входов 104 и 105. Разрешение записи и адрес записи с пхода 35 задается сигналами с входов 106-108, с входа 36 в регистры 267 и 268 - сигналами с входов 109 и 110. Запись стро- бируется сигналом с входа 94. Управление мультиплексорами 273.1 и 273.2 осуществляется сигналами с входов 111- 114. Восьмой блок 10 буферных регистров 1 (фиг. 9) содержит четыре регистра 279-282, пять мультиплексоров 283, два мультиплексора 284, группу элементов И 285, элементы И 286, элементы И 287, элементы ИЛИ 288, элемент ИЛИ 289, элементы НЕ 290 и 291. Архитектура блока 10 буферных регистров аналогична архитектуре блока 9 буферных регистров за исключением того, что выходы разрядов выхода второго мультиплексора 284 соединены с первыми входами элементов И 285 группы, вторые входы которых подсоединены к выходу элемента НЕ 291, выходы элементов И 285 группы являются выходом 51 блока 10 буферных регистров. Записью с входа 47 управляют сигналы с входов 118-120, с входа 48 - сигналы с входов 121-123, с входа 49 в регистры 279 и 280 - сигналы с входов 124 и 125. Управление мультиплексорами 284 осуществляется сигналами с входов 126 - 129. На вход элемента НЕ 291 подается сигнал с входа 130.

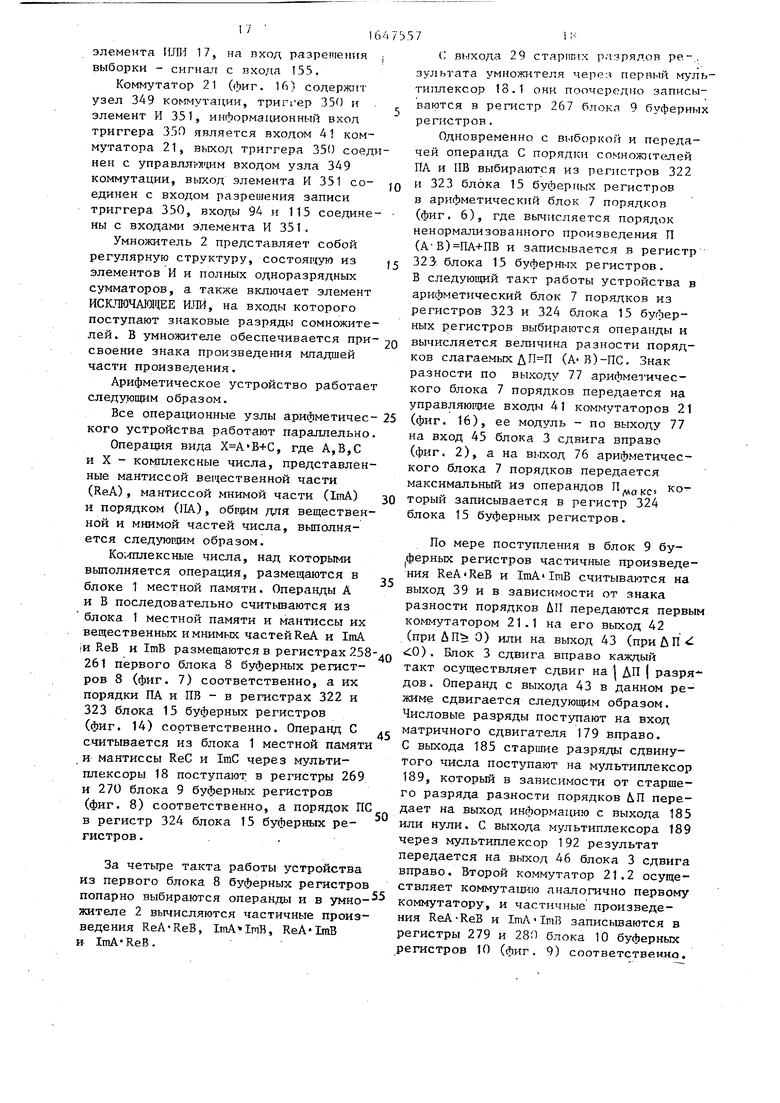

Четвертый блок 11 буферных регист- Фов (фиг. 10) содержит два регистра 292 и 293, мультиплексор 294, два элемента И 295 и элемент НЕ 296, причем вход 53 соединен с информационным входом регистра 292, входы двенадцати младших разрядов входа 53 соединены с информационным входом регистра 293, выходы,элементов И 295 соединены с входами разрешения записи соответствующих регистров, знаковый разряд выхода регистра 292 соединен со знаковым разрядом выхода 54 четвертого блока 11 буферных регистров, числовые разряды выхода регистра 292 соединены с первым информационным входом мультиплексора 294, выход регистра 293 соединен с вторым информационным входом мультиплексора 294, входы двух старших разрядов второго информационного входа мультиплексора 294 соединены с входом нулевого потенциала устройства, выход мультиплексора

55714

294 является выходом 54 четвертого блока 11 буферных регистров. Запись в регистры управляется сигналами с входов 134 и 135, стробируется сигналом с входа 94. Управление мультиплексором 294 осуществляется сигналом с входа 136.

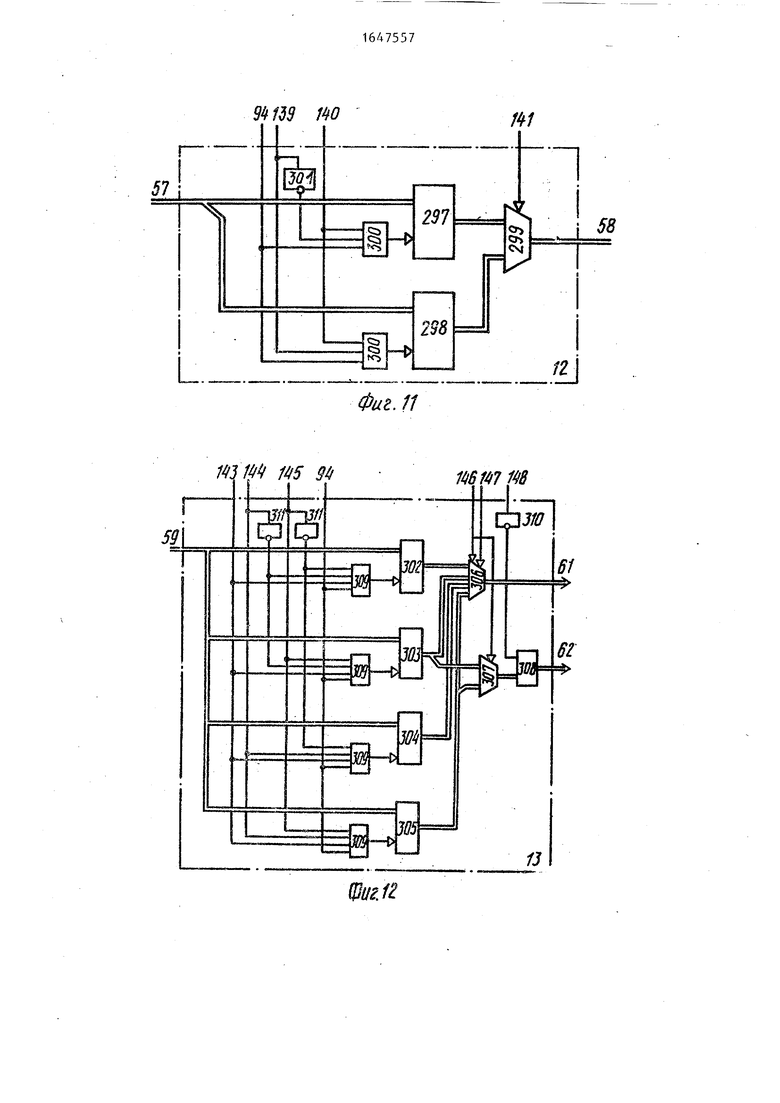

Пятый блок буферных регистров 12

(фиг. 11) содержит два регистра 297 и 298, мультиплексор 299, два элемента И 300 и элемент НЕ 301, вход 57 со-0 единен с информационными входами регистров 297 и 298, выходы которых соез динены с первым и вторым информационными входами мультиплексора 299 соответственно, выходы элементов И 300 соединены с входами разрешения записи регистров, выход мультиплексора 299

0 является выходом 58 пятого блока 12 буферных регистров. Запись управляется сигналами с входов 139 и 140, стробируется сигналом с входа 94. Управление мультиплексором 299 осуществ5 ляется сигналом с входа 141.

Шестой блок 13 буферных регистров (фиг. 12) содержит четыре регистра 302-305, мультиплексоры 306 и 307, группу элементов И 308 и 309, элемен0 ты НЕ 310 и 311, вход 59 соединен с информационными входами регистров 302- 305, выходы элементов И 309 соединены с входами разрешения записи регистров, выходы регистров 302-305 соеди5 нены с первым - четвертым информационными входами мультиплексора 306, двенадцать младших разрядов выходов регистров 303 и 305 соединены с первым и вторым информационными входами муль0 тшшексора 307 соответственно, выход мультиплексора 307 соединен с первыми входами элементов И 308 группы, выход элемента НЕ 310 соединен с вторыми входами элементов И 308 группы, выхо5 ДЫ мультиплексора 306 и элементов И 308 группы являются выходами 61 и 62 шестого блока 13 буферных регистров соответственно. Управление записью в регистры осуществляется сигналами с

0 входов 143-145. Мультиплексорами 306 и 307 управляют сигналы с входов 143- 145, Мультиплексорами 306 и 307 управляют сигналы с входов 146- и 147. На вход элемента НЕ 310 подается с вхо5 да 148 сигнал.

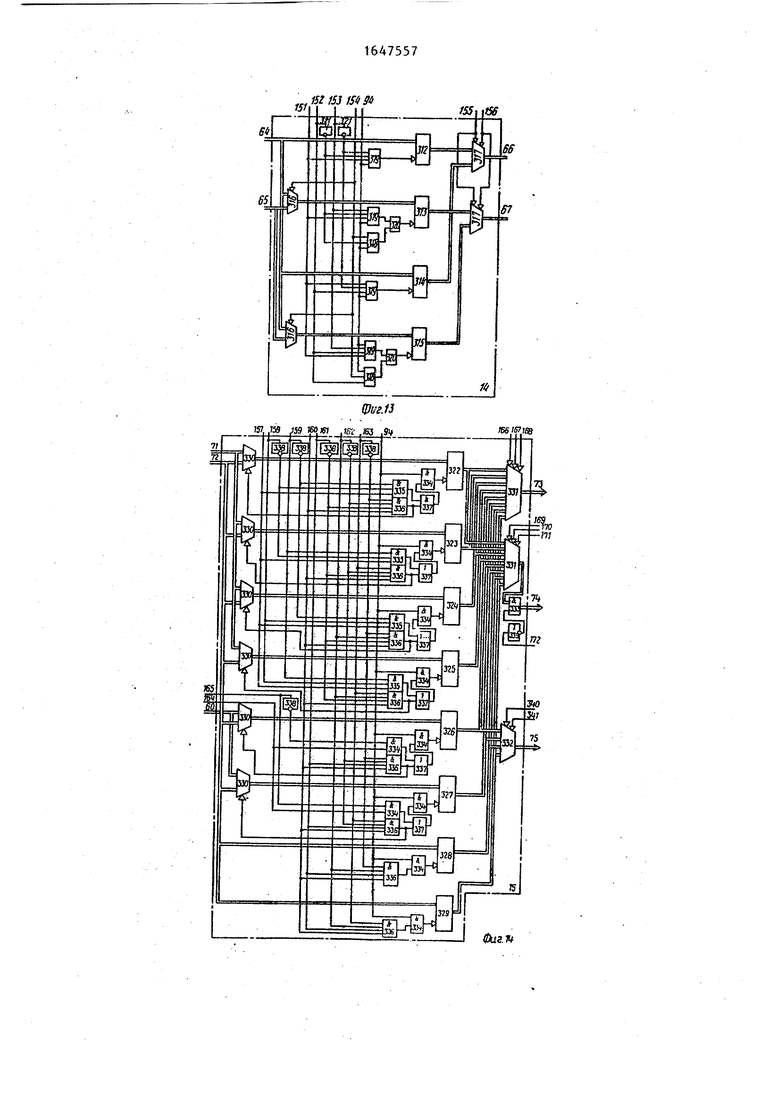

Седьмой блок 14 буферных регистров (фиг. 13) содержит четыре регистра 312-315, два мультиплексора 316, два мультиплексора 317 с тремя состояниями выхода, элементы И 318 и 319, элементы ИЛИ 320, элементы НЕ 321, вход 64 соединен с информационными входами регистров 312 и 314 и с первыми информационными входами мультиплексоров 316, вход 65 соединен с вторыми информационными входами мультиплексоров 316, выходы которых соединены с информационными входами регистров 313 и JQ 315, выходы двух элементов И 319 и элементов ИЛИ 320 соединены с входами разрешения записи регистров, выходы регистров 312 и 313 соединены с первыми информационными входами мультиплексоров 317, выходы регистров 314 и 315 соединены с вторыми информационными входами мультиплексоров 317, выходы мультиплексоров 317 являются выходами 66 и 67 седьмого блока 14 буферных регистров. Управление записью с входа 64 осуществляет сигнал с входа 151 адрес записи задается сигналами с входов 152 и 153. Разрешение за15

20

блока 15 буферных регистров соответственно. Записью с входа 71 управляют сигналы с входов 157-159, с входа 72- сигналы с входов 160-163, с входа 60- сигналы с входов 164 и 165. Мультиплексоры 331 управляются сигналами с входов 166-171, мультиплексоры 332 - сигналами с входов 340 и 341. На вход элемента НЕ 339 подается сигнал с входа 172.

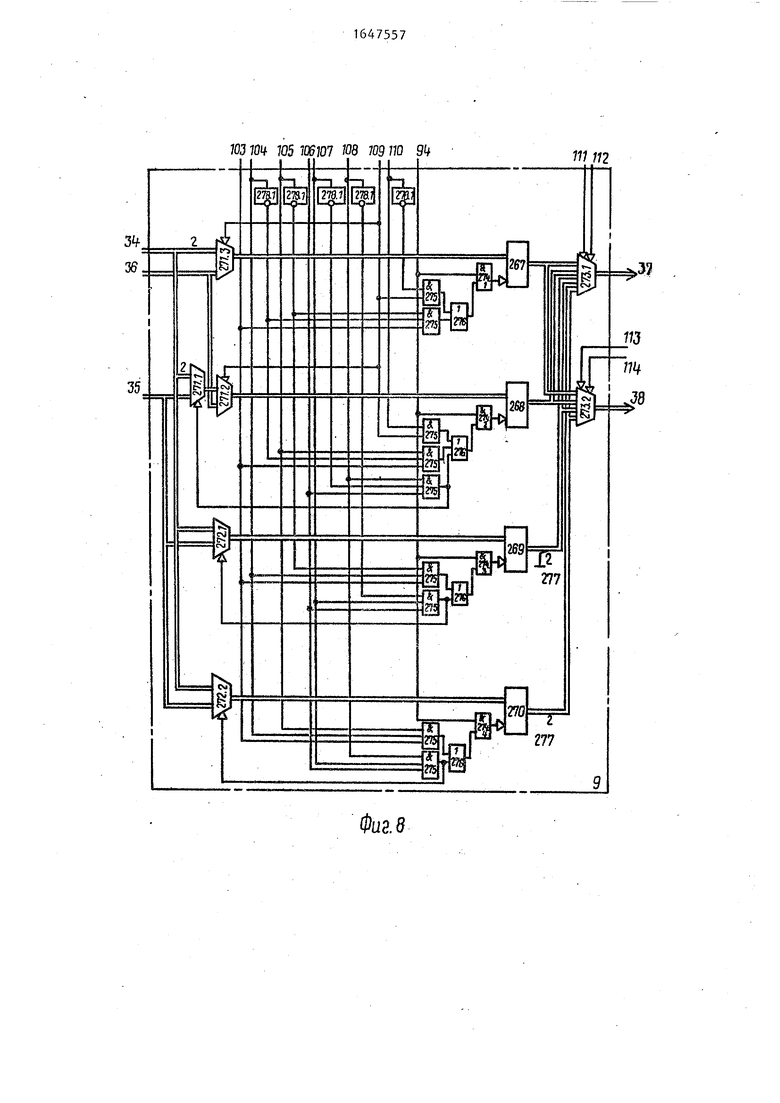

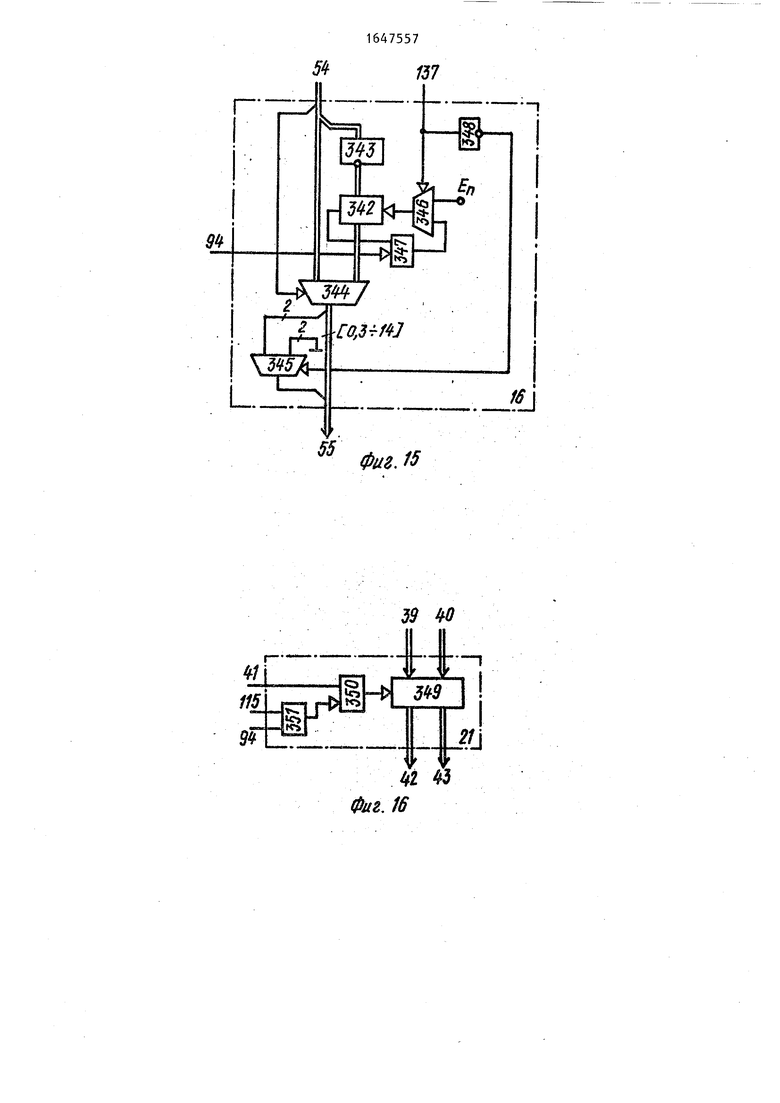

Преобразователь 16 дополнительного кода в прямой код (фиг. 15) содержит узел 342 прибавления переноса, группу элементов НЕ 343, мультиплексоры 344-346, триггер 347 и элемент НЕ 348, вход 54 соединен с первым информационным входом мультиплексора 344, знаковый разряд входа 54 соединен с управляющим входом мультиплексора 344 и со знаковым разрядом информационного входа узла прибавления переноса 342, выходы элементов НЕ 343 группы соединены с входами разрядов

лиси с входа 65 дается сигналом с вхо-25 информационного входа узла 342 прибавда 154, адрес задается сигналом с входа J52. На адресные входы мультиплексоров 317 подается сигнал с входа 156, на вход разрешения выборки - сигнал с входа 155. ,

Второй блок 15 буферных регистров (фиг. 15) содержит восемь регистров 322-329, шесть мультиплексоров 330, два мультиплексора 331, мультиплексор 332, группу элементов И 333, элементы И 334, элементы И 335, элементы И 336, элементы ИЛИ 337, элементы НЕ 338 и 339, вход 60 соединен с первыми информационными входами пятого и шестого мультиплексоров 330, вход 72 - с

вторыми информационными входами мультиплексоров 330 и с информационными входами регистров 328 и 329, вход 71 с первыми информационными входами первых четырех мультиплексоров 330,вы- ходы мультиплексоров 330 соединены с информационными входами регистров 322-327,выходы регистров 322-329, соединены с первыми - восьмыми информационными входами мультиплексоров 331, выходы регистров 326-329 - с информационными входами мультиплексора 332,выход второго мультиплексора 331 соединены с первыми входами элементов И 333 группы, выход элемента НЕ 339 соединен с вторыми входами элементов И 333 группы, выходы первого мультиплексора 331, элементов И 313 группы и мультиплексора 332 являются выходами 73-75

0

блока 15 буферных регистров соответственно. Записью с входа 71 управляют сигналы с входов 157-159, с входа 72- сигналы с входов 160-163, с входа 60- сигналы с входов 164 и 165. Мультиплексоры 331 управляются сигналами с входов 166-171, мультиплексоры 332 - сигналами с входов 340 и 341. На вход элемента НЕ 339 подается сигнал с входа 172.

Преобразователь 16 дополнительного кода в прямой код (фиг. 15) содержит узел 342 прибавления переноса, группу элементов НЕ 343, мультиплексоры 344-346, триггер 347 и элемент НЕ 348, вход 54 соединен с первым информационным входом мультиплексора 344, знаковый разряд входа 54 соединен с управляющим входом мультиплексора 344 и со знаковым разрядом информационного входа узла прибавления переноса 342, выходы элементов НЕ 343 группы соединены с входами разрядов

0

0

5

ления переноса, выход которого соединен с вторым информационным входом мультиплексора 344, выход переноса из третьего числового разряда узла 342 прибавления переноса соединен с информационным входом триггера 347, выход которого соединен с вторым входом мультиплексора 346, первый информационный вход мультиплексора 346 соединен с входом единичного потенциала 5 устройства выход мультиплексора 346 соединен с входом переноса узла 342 прибашэтения переноса, выход элемента НЕ 348 соединен с управляющим входом мультиплексора 345, выход мультиплексора 344 является выходом 55, выходы двух старших числовых разрядов выхода мультиплексора 344 соединены с первым информационным входом мультиплексора 345, выход которого соединен с выходами двух старших числовых разрядов выхода 55. Сигнал с входа 94 подается на вход разрешения записи триггера 347. Сигнал с входа 137 подается на управляющий вход мультиплексора 346 и на вход элемента НЕ 348.

На входы 68 и 69 элемента ИЛИ 17 подаются старшие числовые разряды выходов 66 и 67 седьмого блока 14 буферных регистров соответственно.

Четвертый мультиплексор 20 представляет собой мультиплексор с тремя состояниями выхода, на адресный вход которого поступает сигнал с выхода

0

5

элемента ИЛИ 17, на вход разрешения ( выборки - сигнал с входа 155.

Коммутатор 21 (фиг. 16) содержит узел 349 коммутации, триггер 350 и элемент И 351, информационный вход триггера 350 является входом 41 коммутатора 21, выход триггера 350 соединен с управляющим входом узла 349 коммутации, выход элемента И 351 со- единен с входом разрешения записи триггера 350, входы 94 и 115 соедине- ны с входами элемента И 351.

Умножитель 2 представляет собой регулярную структуру, состоящую из элементов И и полных одноразрядных сумматоров, а также включает элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, на входы которого поступают знаковые разряды сомножителей. В умножителе обеспечивается при- своение знака произведения младшей части произведения.

Арифметическое устройство работает следующим образом.

Все операционные узлы арифметичес- кого устройства работают параллельно.

Операция вида Х А В+С, где А,В,С и X - комплексные числа, представленные мантиссой вещественной части (ReA), мантиссой мнимой части (ImA) и порядком (ПА), общим для вещественной и мнимой частей числа, выполняется следующим образом.

Комплексные числа, над которыми выполняется операция, размещаются в блоке 1 местной памяти. Операнды А и В последовательно считываются из блока 1 местной памяти и мантиссы их вещественных и мнимых частей ReA и ImA iH ReB и ImB размещаются в регистрах 258 261 первого блока 8 буферных регистров 8 (фиг. 7) соответственно, а их порядки ПА и ПВ - в регистрах 322 и 323 блока 15 буферных регистров (фиг. 14) соответственно. Операнд С считывается из блока 1 местной памяти и мантиссы ReC и ImC через мультиплексоры 18 поступают в регистры 269 и 270 блока 9 буферных регистров (фиг. 8) соответственно, а порядок ПС в регистр 324 блока 15 буферных регистров .

За четыре такта работы устройства из первого блока 8 буферных регистров попарно выбираются операнды и в умно- - жителе 2 вычисляются частичные произведения ReA-ReB, , ReA-ImB и ImA ReB.

JQ

j 2Q

25

30

Q

35

0

-

С выхода 29 старших разрядов ре-, зультата умножителя первый мультиплексор 13.1 они поочередно записываются в регистр 267 блока 9 буферных регистров.

Одновременно с выборкой и передачей операнда С порядки сомножителей ПА и ПВ выбираются из регистров 322 и 323 блока 15 буферных регистров в арифметический блок 7 порядков (фиг. 6), где вычисляется порядок ненормализованного произведения П (А В)ПА+ПВ и записывается в регистр 323 блока 15 буферных регистров. В следующий такт работы устройства в арифметический блок 7 порядков из регистров 323 и 324 блока 15 буферных регистров выбираются операнды и вычисляется величина разности порядков слагаемых (А-В)-ПС. Знак разности по выходу 77 арифметического блока 7 порядков передается на управляющие входы 41 коммутаторов 21 (фиг. 16), ее модуль - по выходу 77 на вход 45 блока 3 сдвига вправо (фиг. 2), а на выход 76 арифметического блока 7 порядков передается максимальный из операндов , который записывается в регистр 324 блока 15 буферных регистров.

По мере поступления в блок 9 буферных регистров частичные произведения ReA ReB и ImA« ItnB считываются на выход 39 и в зависимости от знака разности порядков ДИ передаются первым коммутатором 21.1 на его выход 42 (при ДП 0) или на выход 43 (при Д П 4. Ј0) . Блок 3 сдвига вправо каждый такт осуществляет сдвиг на 1 ДП | разря дов. Операнд с выхода 43 в данном режиме сдвигается следующим образом. Числовые разряды поступают на вход матричного сдвигателя 179 вправо. С выхода 185 старшие разряды сдвинутого числа поступают на мультиплексор 189, который в зависимости от старшего разряда разности порядков &П передает на выход информацию с выхода 185 или нули. С выхода мультиплексора 189 через мультиплексор 192 результат передается на выход 46 блока 3 сдвига вправо. Второй коммутатор 21.2 осуществляет коммутацию аналогично первому коммутатору, и частичные произведения ReA-ReB и ImAImB записываются в регистры 279 и 280 блока 10 буферных регистров 10 (фиг. 9) соответственно.

После их поступления в блок 10 буферных регистров частичные произведения считываются в арифметико-логический блок 4 мантисс (фиг. 3). Вычисли- ется мантисса вещественной части произведения Re()ReA ReB-ImA-ItnB, которая записывается в регистр 279 блока Ю буферных регистров через третий мультиплексор 19 по входу 49.

После прохождения через коммутаторы 21 и блок 3 сдвига вправо частичного произведения 1таА«1тчВ в слудую- щие два такта работы устройства из блока 9 буферных регистров считывают- ся попарно операнды ReA-ImB и ReC, ItnA ReB и ImC и передаются на выходы первого коммутатора 21.1: ReA«ItnB и ImA-ReB - на выход 42, ReC и ImC - на выход 43 при и наоборот - при . Операнды и ReC записываются в регистры 280 ч 281 блока 10 буферных регистров. В следующем такте операнды ImA ReB и ImC записываются в регистры 279 и 281 соответ- ственно.

После поступления мантисс ReA-ImB и ReC в блок 10 буферных регистров в арифметико-логическом блоке 4 мантисс вычисляется мантисса вещественной части результата ReX-Re(A-B)+ReC, которая с выхода 52 арифметико-логического блока мантисс записывается в регистр 297 блока 12 буферных регистров (фиг. 11). В следующие два такта работы устройства вычисляется мантисса мнимой части произведения Im(A B) ReAItnB- -IniA ReB, которая записывается в регистр 279 блока 10 буферных регистров, и мантисса мнимой части резуль тата (A«B)+ImC, которая записывается в регистр 297 блока 12 буферных регистров. Опасность возникновения переполнения в арифметико-логическом блоке мантисс ликвидирована путем расширения разрядной сетки арифметико логического блока на два разряда лева.

После записи в блок 12 буферных регистров мантисса ReX проходит через преобразователь 5 количества старших нулей в двоичный код (фиг. 4) и записывается в регистр 302 блока 13 буферных регистров (фиг. 12), а результат работы преобразователя N(ReX) по выходу 60 записывается в регистр 326 блока 15 буферных регистров. Через такт преобразователь 5 количества

0 $ о 5

0

5

старших нулей в двоичный код обрабатывает мантиссу ImX, которая записывается в регистр 303 блока 13 буферных регистров, а параметр нормализации N(ImX) записывается в регистр 327 блока 15 буферных регистров.

В арифметическом блоке 7 порядков (фиг. 6) порядок ненормализованного результата увеличивается на два. Увеличенный порядок записывается в регистр 328 блока 15 буферных регистров.

После поступления в блок 15 буферных регистров параметра нормализации мантиссы мнимой части N(ImX) оба параметра нормализации передаются в арифметический блок 7 порядка, который выполняет операцию вычитания, по знаку результата которой через мультиплексоры 254 и 255 на выход 76 передается минимальный из операндов: NA,V1H MHnfN(ReX), N(ImX, записывающийся в регистр 329 блока 15 буферных регистров, и по входу 63 - в регистр управляющей информации блока 6 сдвига влево (фиг. 5).

После записи параметра нормализации поочередно выбираются из блока 13 буферных регистров мантиссы вещественной и мнимой частей результата ReX и ImX по входу 61s поступают на матричный сдвигатель 235 влево блока 6 сдвига влево (по входу 62 в это время поступают нули), сдвигаются на NMMH разрядов, после чего старшие разряды сдвинутых мантисс по выходу 64 записываются в регистры 292 и 293 блока 14 буферных регистров (фиг. 13) соответственно.

Одновременно в арифметическом блоке 7 порядков вычисляется порядок нормализованного результата ПХИТдюцс- -Ммйн, который с выхода 76 арифметического олока 7 порядков записывается в регистр 329 блока 15 буферных регистров.

Нормализованный результат - мантиссы ReX и ImX из блока 14 буферных регистров по выходам 66 и 67 и порядок ИХ из блока 15 буферных регистров по выходу 75 через четвертый мультиплексор 20 - передается на вход 23, причем старшие числовые разряды мантисс ReX и ImX по входам 68 и 69 поступают на элемент ИЛИ 17. Если сигнал па выходе элемента ИЛИ 17 равен нулю (обе мантиссы равны нулю), четвертый мультиплексор 20 передает на вход 23 нулевой порядок, в противном

1647557

случае ИХ передается на вход 23 без изменений. Результат с входа 23 записывается в блок 1 местной памяти.

С числами двойной точности, представленными мантиссой (МА), разрядность которой вдвое превышает разрядность мантиссы вещественной или мнимой части комплексного числа (знак

числа дублируется перед младшими раз- JQ в регистр 280 блока 10 буферных рерядами мантиссы), и порядком (ПА) арифметическое устройство работает следующим образом.

При выполнении операции X A;B+C с данными, представленными в вышеопи- j санном формате, из блока 1 местной памяти, где хранятся операнды, последовательно считываются операнды А и В и записываются в первый блок 8 буфергистров.

В следующий такт работы устройств из блока 1 местной памяти считываетс третий операнд С. Мантисса С записывается в блок 9 буферных регистров: Н(С) - в регистр 269, L(C) - в регистр 270. Стармие разряды произведе ния (А) Н (В) передаются без сдв га в регистр 279 блока Ю буферных

ных регистров старшие разряды мантис- 2Qрегистров. В арифметико-логическом

сы А (Н(А)) - в регистр 258, младшиеблоке 4 мантисс вычисляются младшие

разряды (L(A)) - в регистр 259, Н(В)разряды произведения А«В :L(A«B)

и L(B) - в регистры 260 и 261 соответ- L((A-B)+L (Н(А) Н(В) и по выходу 52 ственно, порядки операндов ПА и ПВ

25

30

записываются в регистры 322 и 323 блока 15 буферных регистров соответственно.

За три такта работы устройства в умножитель 2 попарно выбираются операнды из первого блока 8 буферных регистров и вычисляются произведения H(A) L(B), L(A)-H(B), H(A)-H(B). Старшие разряды первых двух произведений по выходу 29 последовательно передаются через первый мультиплексор 18.1, записываются в регистр 267 блока 9 буферных регистров, откуда через первый и второй коммутаторы 21, работающие в произвольном режиме (блок сдвига вправо работает в режиме п передачи без сдвига), записываются в регистры 279 и 280 блока 10 буферных регистров. Произведение Н(А)-Н(В) выводится из умножителя 2 по выходам 29

35

через третий мультиплексор 19 по входу 36 записываются в регистр 268 блока 9 буферных регистров. В регистр 32 блока 15 буферных регистров записывается порядок третьего операнда ПС.

В следующем такте в арифметико-логическом блоке 4 мантисс вычисляются старшие разряды произведения А В путем прибавления к старшим разрядам (А) H(B)J содержимого регистра 211. Результат по выходу 52 записывается в регистр 267 блока 9 буферных регистров. В арифметическом блоке 7 порядков вычисляется разность порядков слагаемых (А-В)-ПС, ее знак с выхода 77 арифметического блока 7 порядков передается на входы 41 первого и второго коммутаторов 21, модуль с выхода 77 - на вход 45 блока 3 сдвига вправо, на выход 76 арифметического блока 7 порядков передаи 30 через первый и второй мультиплек-д ется максимальный из операндов

соры 18 и записывается в блок 9 буферных регистров: старшие разряды произведения ((А)-- Н(вУ ) - в регистр 267, младшие разряды (LЈH(A)к ХН(В)) - в регистр 268.

Одновременно с выполнением первой операции умножения в арифметическом блоке 7 порядков вычисляется порядок ненормализованного произведения П ()ПА+ПВ, который записывается в регистр 322 блока 15 буферных регистров.

После прихода в блок 10 буферных регистров произведения L(A)-H(B) в

который записывается в регистр 324 блока 15 буферных регистров.

Первый коммутатор 21 в зависимости от знака ЛЛ последовательно осу- CQ ществляет передачу Н(А-В) и L() на выход 42, Н(С) и L(C) - на выход 43 (приДП О) или наоборот (приЛП 0). Блок 3 сдвига вправо за два такта работы сдвигает одно из слагаемых. В первом такте старшие разряды числа поступают на матричный сдвига- тель 179 вправо, старшие разряды сдвинутого числа через мультиплексоры 189 и 192 передаются на выход 46

арифметико-логическом блоке 4 мантисс выполняется операция сложения L () H(A)-L(B)+L(A)- H(R), результат которой по выходу 52 записывается в регистр 279 блока 10 буферных регистров. Из блока 9 буферных регистров без сдвига передаются млад тие разряды произведения (A); Н(В)| и записываются

в регистр 280 блока 10 буферных регистров.

В следующий такт работы устройства ° из блока 1 местной памяти считывается третий операнд С. Мантисса С записывается в блок 9 буферных регистров: Н(С) - в регистр 269, L(C) - в регистр 270. Стармие разряды произведения (А) Н (В) передаются без сдвига в регистр 279 блока Ю буферных

L((A-B)+L (Н(А) Н(В) и по выходу 52

через третий мультиплексор 19 по входу 36 записываются в регистр 268 блока 9 буферных регистров. В регистр 323 блока 15 буферных регистров записывается порядок третьего операнда ПС.

В следующем такте в арифметико-логическом блоке 4 мантисс вычисляются старшие разряды произведения А В путем прибавления к старшим разрядам (А) H(B)J содержимого регистра 211. Результат по выходу 52 записывается в регистр 267 блока 9 буферных регистров. В арифметическом блоке 7 порядков вычисляется разность порядков слагаемых (А-В)-ПС, ее знак с выхода 77 арифметического блока 7 порядков передается на входы 41 первого и второго коммутаторов 21, модуль с выхода 77 - на вход 45 блока 3 сдвига вправо, на выход 76 арифметического блока 7 порядков передакоторый записывается в регистр 324 блока 15 буферных регистров.

Первый коммутатор 21 в зависимости от знака ЛЛ последовательно осу- Q ществляет передачу Н(А-В) и L() на выход 42, Н(С) и L(C) - на выход 43 (приДП О) или наоборот (приЛП 0). Блок 3 сдвига вправо за два такта работы сдвигает одно из слагаемых. В первом такте старшие разряды числа поступают на матричный сдвига- тель 179 вправо, старшие разряды сдвинутого числа через мультиплексоры 189 и 192 передаются на выход 46

и

20

23

блока сдвига вправо, выдвинутые вправо разряды через мультиплексор 190 записываются в регистр 187. Во втором такте в блок 3 сдвига вправо по- ступают младшие разряды мантиссы. Результат с выхода 184 логически складывается с содержимым регистра 187 в группе элементов ИЛИ 188, к образованные младшие разряды сдвинутого числа JQ через мультиплексоры 191 и 192 передаются на выход 46 блока 3 сдвига вправо. После прохождения второго коммутатора 21 операнды записываются в блок Ю буферных регистров: Н(А«В) и Н(С) - в регистры 269 и 270, L(A B) и L(C) - в регистры 267 и 268 соответственно.

После прихода в блок 10 буферных регистров младших разрядов слагаемых в арифметико-логическом блоке 4 мантисс образуются младшие разряды суммы L(X)L(A«B)+L(C), которые с выхода 53 арифметико-логического блока 4 мантисс записываются в регистр 25 293 блока 11 буфер mix регистров.

В следующий такт в арифметико-логическом блоке 4 мантисс вычисляются старшие разряды суммы IJ(X)H() + +Н(С) с прибавлением в качестве переноса содержимого триггера 214, с выхода 53 они записываются в регистр 292 блока 11 буферных регистров.

В преобразователе 16 осуществляется преобразование младших разрядов суммы в прямой код. Результат по входу 55 через третий мультиплексор 19 записывается в регистр 293 блока 12 буферных регистров. Одновременно в арифметическом блоке 7 порядков порядок ПМсие увеличивается на два и записывается в регистр 328 блока 15 буферных регистров.

В преобразователе 16 преобразуются в прямой код старшие разряды суммы, через третий мультиплексор 19 они записываются в регистр 297 блока 12 буферных регистров.

Старшие разряды результата Н(Х)

проходят через преобразователь 5 количества старших нулей в двоичный код и записываются в регистр 302 блока 13 буферных регистров, В случае равенства старших разрядов нулю в триггер 234 записывается единица. Результат работы преобразователя количества старших нулей в двоичный код по выходу 60 за- Писывается в регистр 326 блока 5 буферных регистров.

164755724

На преобразователь количества старших нулей в двоичный код подаются младшие разряды результата L(X). Коммутатор 220 сдвигает числовые разряды операнда на два разряда влево с заполнением нулями двух.младших разрядов, С выхода 59 операнд L(X) записывается в регистр 303 блока 13 буферных регистров. При нулевом сигнале на выходе триггера 234 на выход 60 передается число старших нулей, в противном случае на выход 60 передается нуль.Информация с выхода 60 записывается в регистр 327 блока 15 буферных регистров.

В арифметическом блоке 7 порядков вычисляется параметр нормализации результата N(X)N(H(X))+N(L(X)), который с выхода 76 арифметического блока порядков записывается в регистр 329 блока 15 буферных регистров и передается на вход 63 блока 6 сдвига влево.

Из блока 13 буферных регистров по входам 61 и 62 считывается мантисса результата Н(Х) и Ь(Х)„ сдвигается на N(X) разрядов в блоке 6 сдвига влево и по выходам 64 и 65 записывается в регистры 312 и 313 блока 14 буферных регистров.

В арифметическом блоке 7 порядков вычисляется порядок нормализованного результата П(Х)(ч-N(X) и записывается в регистр 329 блока 15 буферных регистров.

Мантисса результата из блока 14 буферных регистров по выходам 66 и 67 и порядок результата из блока 15 буферных регистров через четвертый мультиплексор 20 передаются на вход 23, откуда записывается в блок 1 местной памяти.

Дополнительный положительный технический эффект от использования предлагаемого устройства по сравнению с известным заключается в следующем:

в предлагаемом устройстве реализован принцип конвейерной обработки информации;

операционные узлы устройства организованы таким образом, что обеспечивают возможность работы с данными, представленными в двух форматах, с гибридной плавающей запятой и с плавающей запятой ,

число буферных регистров в блоках на входах операционных узлов предлагаемого устройства позволяет проводить обработку в конвейерном

30

35

40

45

50

55

режиме комплексных чисел, представленных в формате с гибридной плавающей запятой.

Формула изобретен, и я

Арифметическое устройство, содержа- щее блок местной памяти, умножитель, блок сдвига вправо, арифметико-логический блок мантисс, преобразователь количества старших нулей в двоичный код, четыре мультиплексора, первый коммутатор, арифметический блок порядков, с первого по четвертый блоки буферных регистров и элемент ИЛИ, причем выходы разрядов мантиссы первого двунаправленного входа блока местной памяти соединены соответственно с входами разрядов первого и второго информационных входов первого блока буферных регистров, первый и второй выходы которого соединены с входами соответствующих сомножителей умножителя, выходы старших и младших разрядов выхода которого соединены соответственно с первыми информационными входами первого и второго мультиплексоров, первый выход преобразователя количества старших нулей та двоичный код соединен с первым информационным входом второго блока буферных регистров, второй информационный вход которого соединен с входами разрядов порядка первого двунаправленного входа блока местной памяти, первый и второй выходы второго блока буферных регистров соединены с соответствующими информационными входами арифметического блока порядков, первый выход которого соединен с входом задания величины сдвига блока вправо, выход знакового разряда первого выхода арифметического блока порядков соединен с управляющим входом первого коммутатора, первый выход которо го соединен с информационным входом блока сдвига вправо, первый выход третьего блока буферных регистров соединен с первым информационным входом первого коммутатора, выход элемента ИЛИ соединен с управляющим входом четвертого мультиплексора, первый информационный вход которого соединен с входом нулевого потенциала устройства, вход синхронизации которого соединен с тактовыми входами с первого по четвертый блоков буферных регистров, с тактовыми входами первого

0

5

0

5

0

5

0

5

0

5

коммутатора, блока сдвига вправо и . арифметико-логического блока мантисс, первый и второй адресные входы, первый вход разрешения записи, первый вход разрешения считывания и первый вход выбора блока местной памяти соединены соответственно с первым и вторым адресными, входами, с первого по третий тактовыми входами устройст- |ва, с первого по третий входы разрешения записи первого блока буферных регистров, объединенные управляющие входы первого и второго мультиплексо - роз , с первого по пятый входы разрешения записи третьего блока буферных регистров, объединенные входы разрешения первого коммутатора и блока сдвига вправо, вход задания вида операции арифметико-логического блока мантисс, первый и второй входы разрешения записи четвертого блока буферных регистров, управляющий вход третьего мультиплексора, с первого по четвертый входы разрешения записи второго блока буферных регистров, вход задания вида операции и вход переноса арифметического блока порядков, вход разрешения четвертого мультиплексора соединен соответственно с четвертого по двадцать четвертый тактовыми входами устройства, отлича ющее- с я тем, что, с целью повышения производительности, оно содержит второй коммутатор, с пятого по восьмой блоки буферных регистров, блок сдвига влево и преобразователь дополнительного кода в прямой код, причем второй выход арифметического блока порядков соединен с входом задания величины сдвига блока сдвига влево и с третьим информационным входом второго блока буферных регистров, третий выход которого соединен с вторым информационным входом четвертого мультиплексора, выход которого соединен с входами разрядов порядка первого двунаправленного входа блока местной памяти, второй двунаправленный вход которого является информационным входом- выходом устройства, выход старших разрядов выхода умножителя соединен с третьим информационным входом первого блока буферных регистров, выходы первого, второго и третьего мультиплексоров соединены с соответствующими информационными входами третьего блока буферных регистров, второй выход которого соединен с вторым инфорч

ационным входом первого коммутатора, второй выход которого и выход блока сдвига вправо соединены соответственно с первым и вторым информационными входами второго коммутатора, второй и первый выходы которого и выход третьего мультиплексора соединены соответственно с первым, вторым и третьим нформационными входами восьмого бло- jg ка буферных регистров, первый и втоой выходы которого соединены с соответствующими информационными входами арифметико-логического блока мантисс, ервый и второй выходы которого соеди- йены соответственно с первым информационным входом третьего мультиплексора и с информационным входом четвертого блока буферных регистров, выход которого соединен с информационным вхо- 20 ом преобразователя дополнительного кода в прямой код, выход которого соединен с вторым информационным вхоом третьего мультиплексора, выход которого соединен с информационным вхо- 25 дом пятого блока буферных регистров, выход которого соединен с информационным входом преобразователя количества . старших нулей в двоичный код, второй выход которого соединен с информа-30 ционным входом шестого блока буферных регистров, первый и второй выходы которого соединены с соответствующими информационными входами блока сдвига влево, первый и второй выходы которо- ,, го соединены с соответствующими информационными входами седьмого блока буферных регистров, первый вход которого соединен с первым входом элемента ИЛИ, с вторым информационным дд входом первого коммутатора и входами разрядов мантиссы первого двунаправленного входа блока местной памяти, второй выход седьмого блока буферных регистров соединен с вторым входом 45 элемента ИЛИ, с вторым информационным входом второго коммутатора и с входами разрядов мантиссы первого двунаправленного входа блока местной памяти, вторые входы разрешения записи, CQ разрешения считывания и выбора блока местной памяти, с первого по четвертый входы разрешения считывания первого блока буферных регистров, с шестого по восьмой входы разрешения записи третьего блока буферных регистров, с первого по четвертый входы разрешения считывания третьего блока буферных регистров, входы задания режима и блокировки блока сдвига вправо, с первого по восьмой входы разрешения записи, с первого по четвертый входы разрешения считывания и вход блокировки восьмого блока буферных регистров, первый и второй входы задания режима арифметико-логического блока мантисс, вход реэрешения считывания четвертого блока буферных регистров, вход задания режима преобразователя дополнительного кода в прямой код, первый и второй входы разрешения записи, вход разрешения считывания пятого блока буферных регистров, вход задания режима преобразователя количества старших нулей в двоичный код, с первого по третий входы разрешения записи, первый и второй входы разреше- ния считывания и вход блокировки шестого блока буферных регистров, входы разрешения и блокировки блока сдвига влево, с первого по четвертый входы разрешения записи, первый и второй входы разрешения считывания седьмого блока буферных регистров, с пятого по девятый входы разрешения записи, с первого по восьмой входы разрешения считывания и вход блокировки второго блока буферных регистров, первый и второй входы задания режима арифметического блока порядков .соединены соответственно с тактовыми входами с двадцать пятого по девяносто второй устройства, входы разрешения, управляющие и тактовые входы первого и второго коммутаторов соответственно объединены, вход синхронизации устройства соединен с тактовыми входами с пятого по восьмой блоков буферных регистров, преобразователя дополнительного кода в прямой код, преобразователя количества старших нулей в двоичный код и блока сдвига влево.

ФмЗ

58 ад

59

238

т

237

-i «/

тО-h

61 вг

/ :

is

А

12

26

235

24

П&Ж/ 243

9 959И9Б

77V76

Фиг.6 9899 WO 101

т ш

ад Oil 601 Ш L01901 50L Щ Ш

LSSLWI

w n nm m глад л

# / /35

ns tn

%3.ff

Z. Л7

т ш т

т№ т $4

w

Фиг. 11

твт т

Щи г. 11

mmw9t

(риг.М

IS 7 J59 ttOJSI ISi ja &

I6SI671SB

Фаг ft

Фиг. м

42 43

Фив. 16

r

I

§§ |§§S| §|5|S °

I

г.

S

и

fe

5

г- m in

i-- r

vЈJ

W

or

Й

-SSI №

/f

«s/

-я

«w w

fl . № -W W

«F

Я/

да

X

sx

II

3Ј Ј j Is

VAЛ

SX f C

Sf

«

JL

Ј

я

i

r-v

1Л

O Г

r o

CM Ш,

-fsa &i

SЈI ftf

ш -гс

Јf

Ьв

Й «ЯтаЈ

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Бетонный полый камень | 1925 |

|

SU2366A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| - М., 1983, с | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1991-05-07—Публикация

1989-04-24—Подача