Изо.бретение относится к вычислительной технике и может быть использовано при проектировании арифмети- ческих устройств вычислительных машин.

Цель изобретения - повышение быстродействия выполнения основных команд и команды деления при одновременном сокращении оборудования.

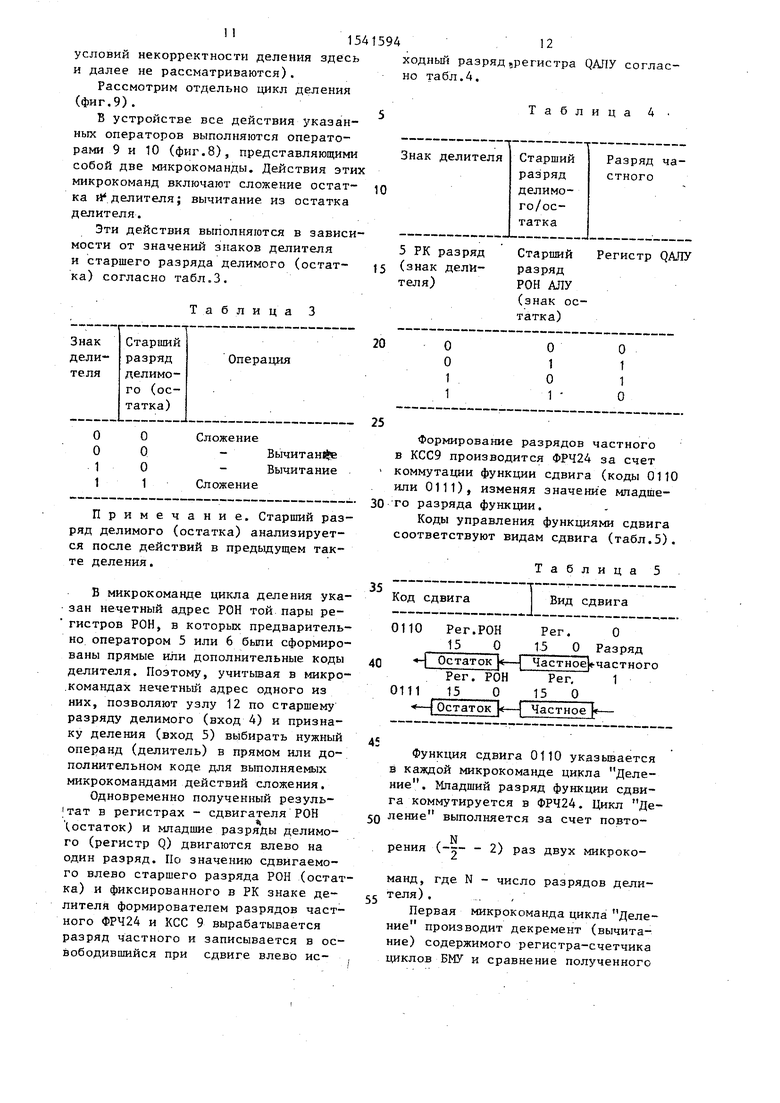

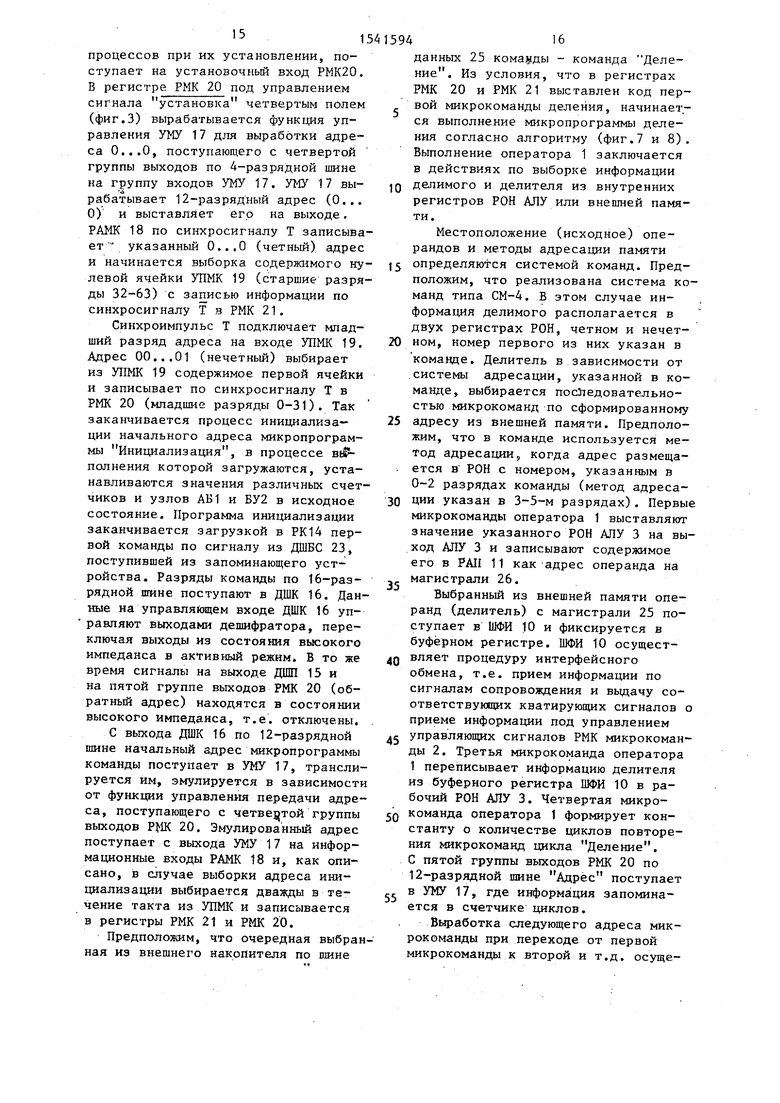

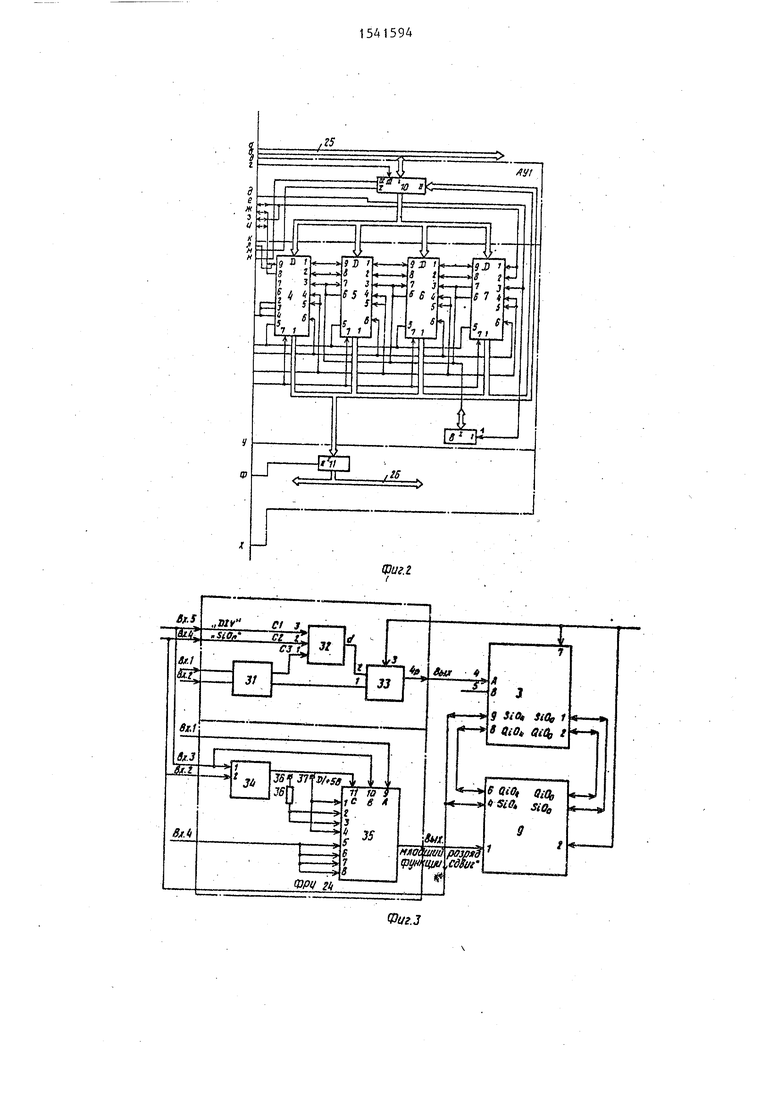

На фиг.1 и 2 показаны схемы арифметического устройства с микропро % граммным управлением; на фиг.З - структурные схемы первого узла выборки операндов и формирователя разря

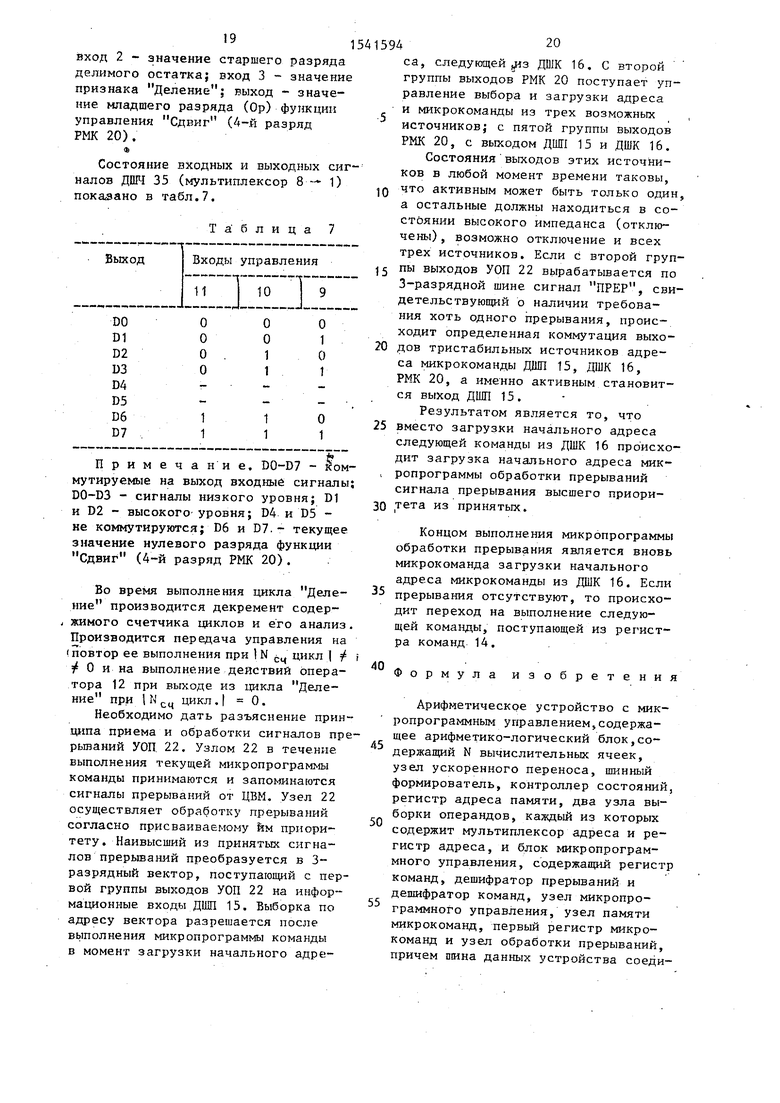

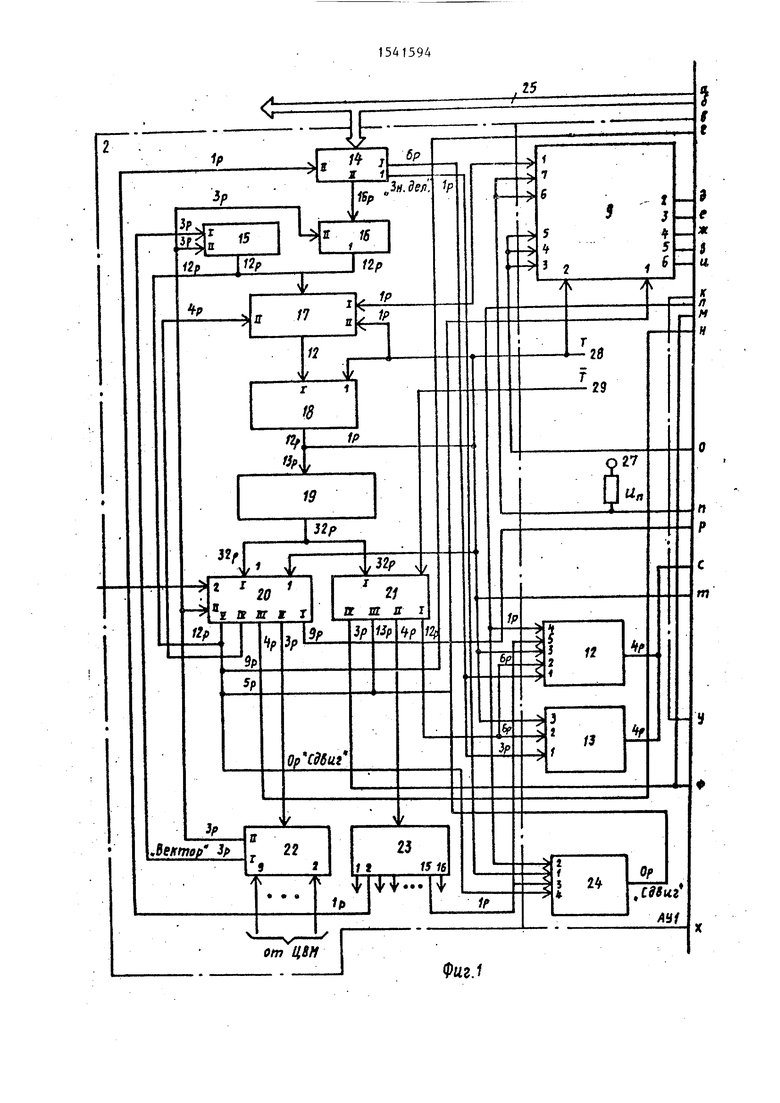

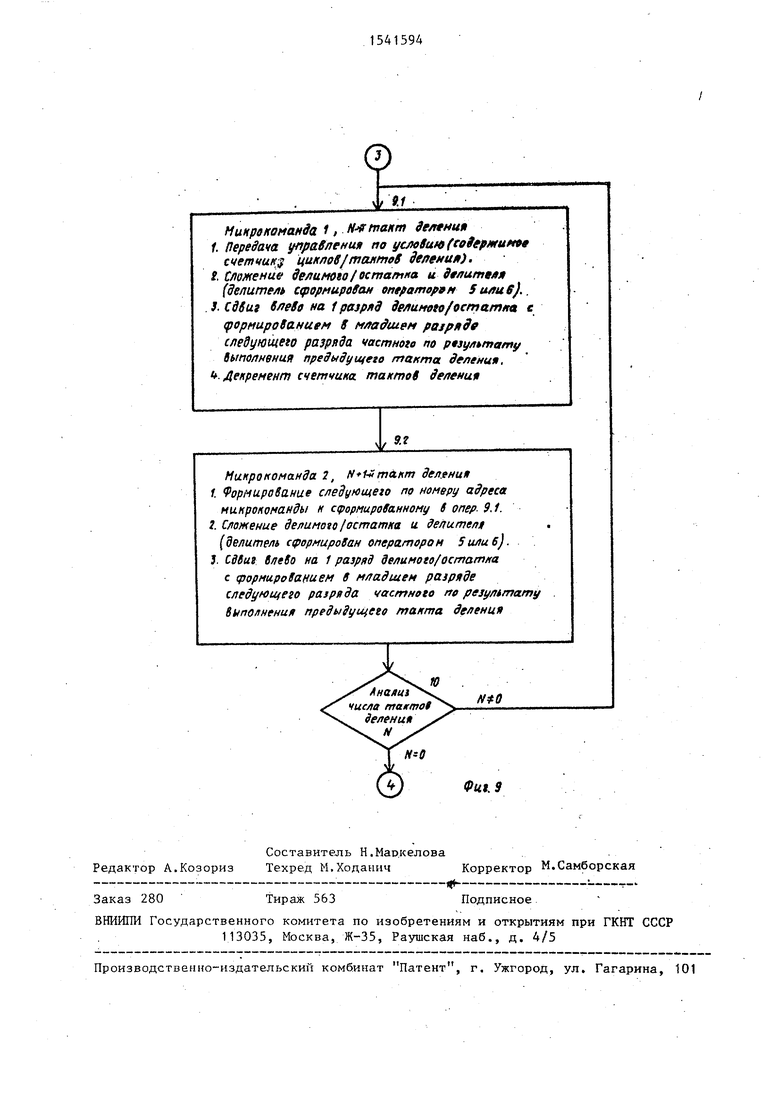

дов частного; на фиг,4 - формат мик- рокоманды; на фиг.5 - схема организации микропрограммного управления; на фиг.6 - временная диаграмма организации микропрограммного управления;, на фиг.7 и 8 - алгоритмы деления; на фиг.9 - содержание алгоритма выполнения цикла Деление.

рифметическое устройство (фиг.1 и 2) содержит арифметико-логический блок 1 (АБ), выполняющий арифметические и логические операции над опе-с рандами; блок 2 микропрограммного управления (БМУ), управляющий работой АБ.

АБ1 содержит арифметико-логический узел 3 (АЛУ), состоящий из вычислительных ячеек 4-7 (1-N) (больших интегральных схем, например, БИС.1804 ВС1); узел 8 ускоренного переноса (2УУП) (БИС 1804 ВР1), служащий для организации ускоренного переноса между ячейками АЛУ; контроллер 9 состояний (КСС) - (БИС 1804ВР2), служа щий для связи сдвиговых элементов

АЛУЗ, управления сигналами переноса, записью, считывания и модификации признаков состояния, выработки флага (сигнала передачи управления) для организации ветвлений по микрокоманде; шинный формирователь 10 (ЩФИ), служащий для организации обмена информацией интерфейсной шине; регистр 11 адреса памяти (РАЛ), предназначенный для хранения адреса запоминающего устройства во время операций выборки или записи информации; первый узел 12 выборки операндов (УВО) и второй узел 13 выборки операндов.

Блок 2 микропрограммного управления (БМУ) содержит регистр 14 команд (РК), служащий для хранения во время выполнения каналом информации о команде; дешифратор 15 векторов прерываний (ДШП) - (БИС555РТ7 (2Кх8), перекодировщик кодов векторов прерываний в начальные адреса соответствующих микропрограмм обработки прерываний; дешифратор 16 команд (ДШК), представляющий собой постоянное запоминающее устройство, дешифрирующее код операций в начальный адрес микропрограммы этой операции; узел 17 микропрограммного уравления (УМУ) - (БИС1804ВУ4), вырабатывающий следующий адрес микрокманды в зависимости от сигнала Г

10

25

415944

управления (флаг) устройства КСС9; регистр 18 формирования адреса (старшие разряды), служащий для хранения адреса микрокоманды во время выборки ее из узла памяти; узел 19 памяти микрокоманд (УПМК) - четыре восьмиразрядные секции ВМС 556РТ16 (8Кх х8); первый регистр 20 микрокоманд (РМК) - конвейерный регистр, служащий для хранения микрокоманды на время ее выполнения (32 разряда) синхронно с сигналом второй регистр 21 микрокоманд (РМК) - конвейерный регистр, служа-щий для хранения микрокоманды и время ее выполнения (32 разряда) синхронно с сигналом Т; узел 22 обработки прерываний (УОП) - (БИС 585И314), служащий для управления приоритетами уровней прерываний, приема сигналов прерываний и формирование их векторов; дешифратор 23 битовых управляющих сиг- налов (ДШБС), формирователь 24 разрядов частного (ФРЧ), шину 25 данных и шину 26 адреса, источник 27 постоянного тока; вход 28 тактовых прямых сигналов; вход 29 тактовых инверсных сигналов; вход 30 Установ15

20

ка.

Узел 12 содержит (фиг.З) мультиплексор 31 адреса, дешифратор 32 адреса и регистр 33 адреса и отличается от узла 13 наличием дешифратора 33 адреса. Формирователь разрядов частного содержит дешифратор 34 адреса и дешифратор 35 частного, вход 36 логической 1, вход 37 логического О.

Для синхронизации временных процессов информация об адресе микрокоманды на выходе регистра 33 должна быть синхронна с работой АЛУ 3. С этой целью прием адреса по входу РА стробирован синхроимпульсом Т, стро- бирующим и работу АЛУ 3.

Дешифратор 32 нулевого разряда адреса (ДША) узла 12 эмулирует нулевой разряд адреса d в зависимости от входных сигналов С1-СЗ по формуле

d - (С, где С,, С и

С2) СЭ,

С3

входы дешифратора 32; - выход дешифратора 32.

515А

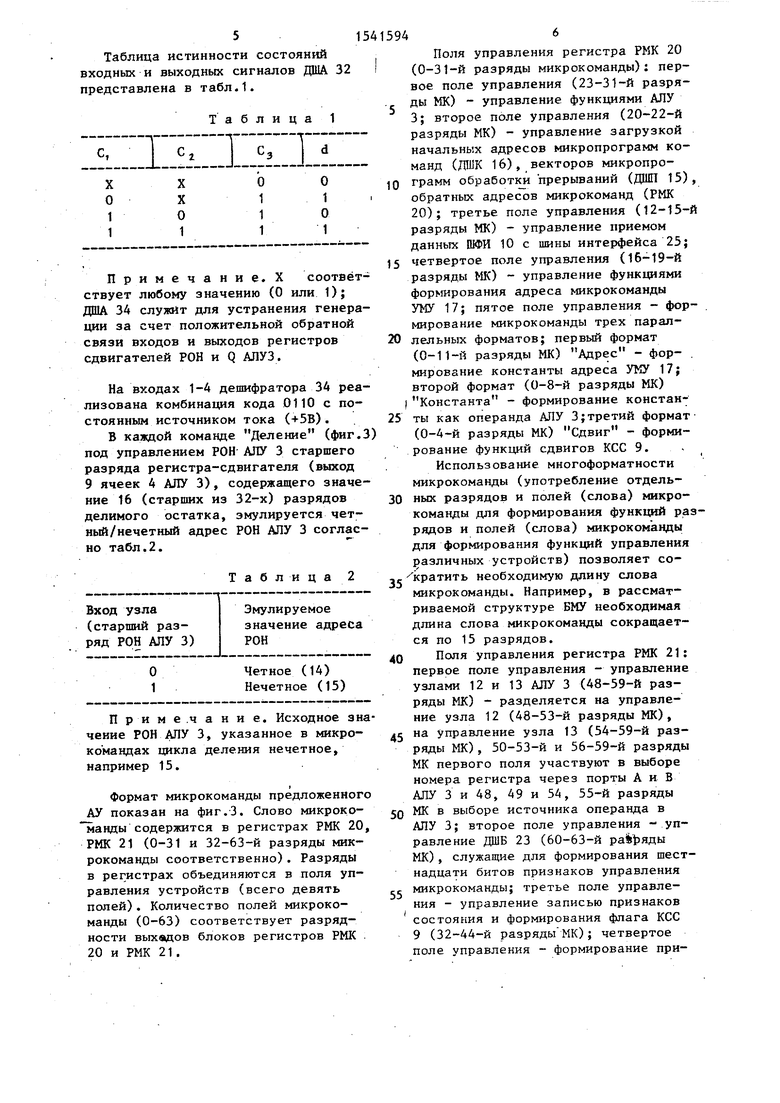

Таблица истинности состояний входных и выходных сигналов ДША 32 I представлена в табл.1.

Таблица 1 С,J Сг Сз

Примечание. X соответствует любому значению (0 или 1); ДША 34 служит для устранения генерации за счет положительной обратной связи входов и выходов регистров сдвигателей РОН и Q АЛУЗ.

На входах 1-4 дешифратора 34 реализована комбинация кода 0110 с постоянным источником тока (+5В).

В каждой команде Деление (фиг.З под управлением РОН АЛУ 3 старшего разряда регистра-сдвигателя (выход 9 ячеек 4 АЛУ 3), содержащего значение 16 (старших из 32-х) разрядов делимого остатка, эмулируется четный/нечетный адрес РОН АЛУ 3 согласно табл.2.

Таблица 2

Эмулируемое значение адреса РОН

О 1

Четное (14) Нечетное (15)

Примечание. Исходное значение РОН АЛУ 3, указанное в микрокомандах цикла деления нечетное, например 15.

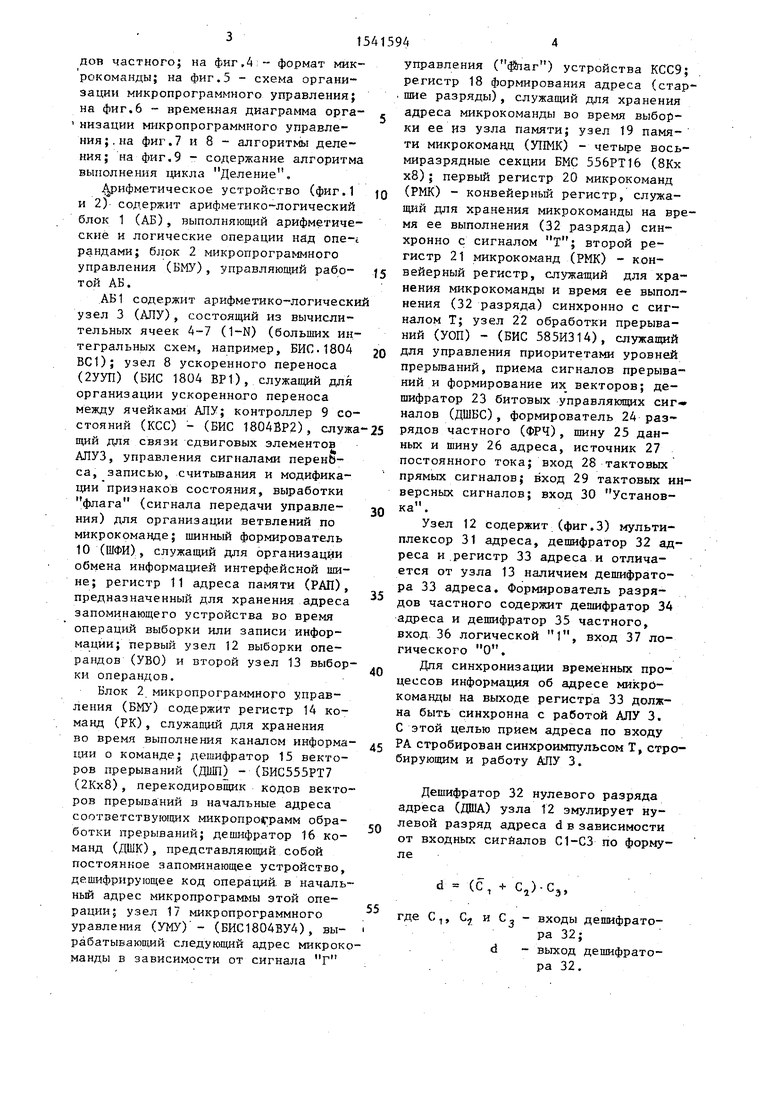

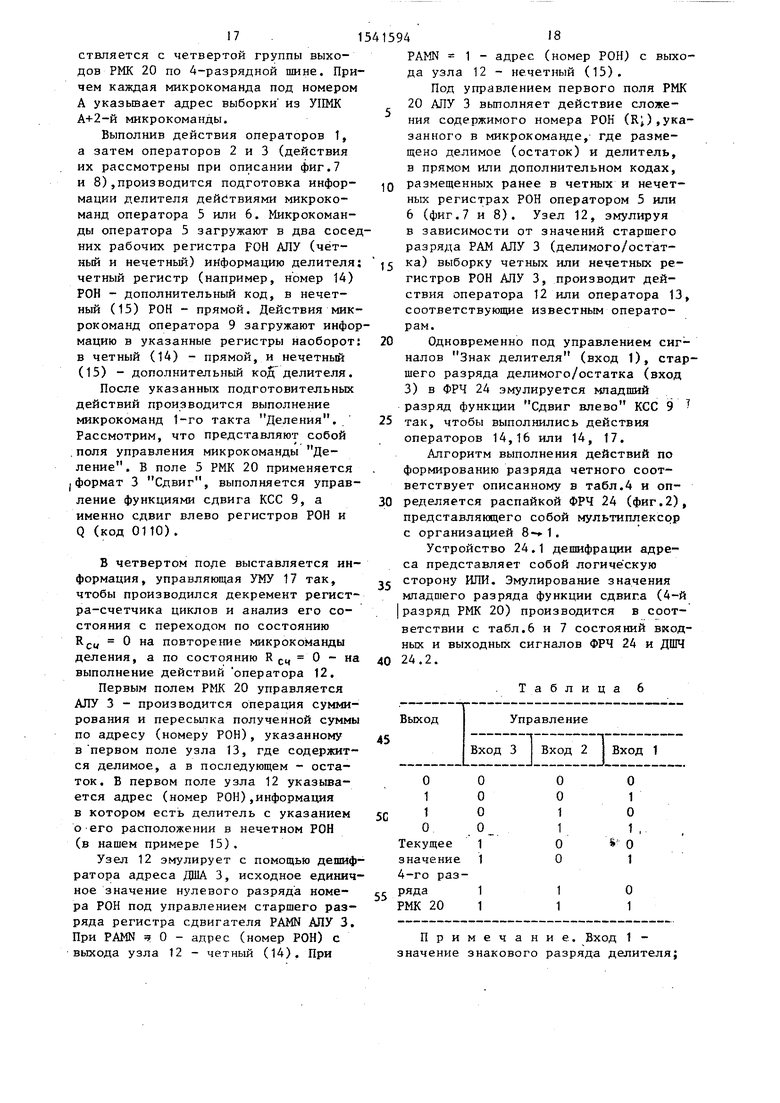

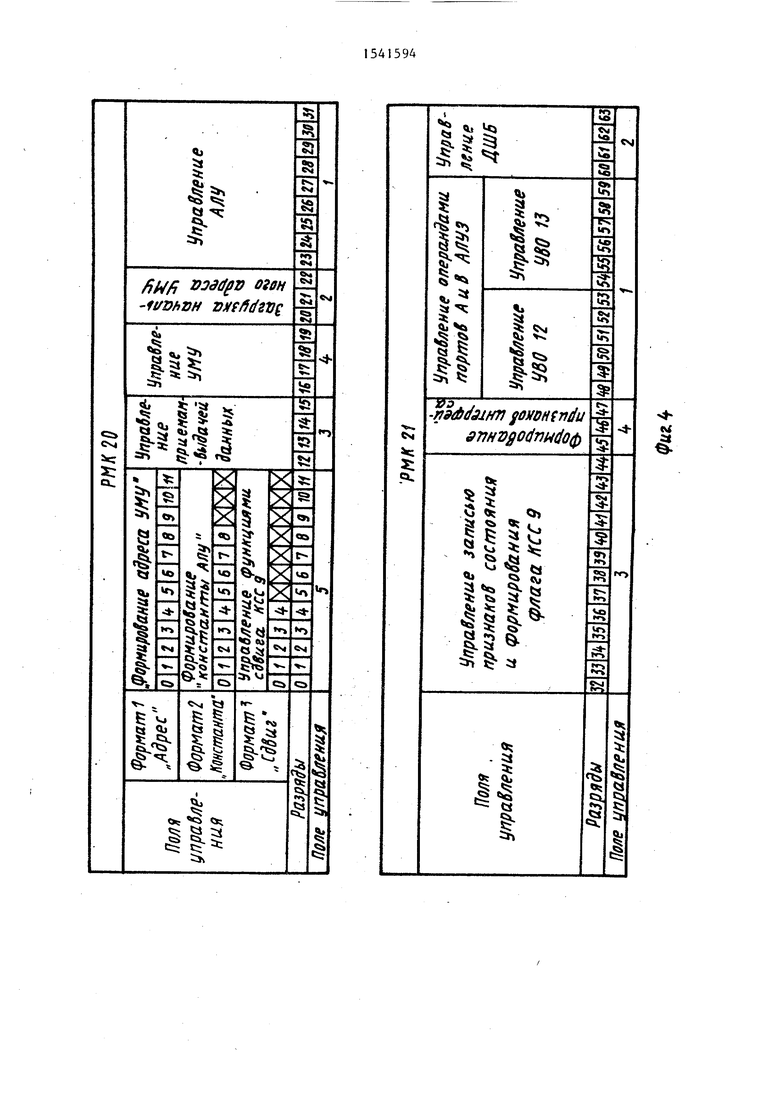

Формат микрокоманды предложенного АУ показан на фиг.З. Слово микроко- манды содержится в регистрах РМК 20, РМК 21 (0-31 и 32-63-й разряды микрокоманды соответственно) . Разряды в регистрах объединяются в поля управления устройств (всего девять полей). Количество полей микрокоманды (0-63) соответствует разрядности выходов блоков регистров РМК 20 и РМК 21.

5946

Поля управления регистра РМК 20 (0-31-й разряды микрокоманды): первое поле управления (23-31-й разряды МК) - управление функциями АЛУ 3; второе поле управления (20-22-й разряды МК) - управление загрузкой начальных адресов микропрограмм команд (ДШК 16), векторов микропро- 0 грамм обработки прерываний (ДШП 15), обратных адресов микрокоманд (РМК 20); третье поле управления (12-15-й разряды МК) - управление приемом данных ШФИ 10 с шины интерфейса 25; 5 четвертое поле управления (16-19-й разряды МК) - управление функциями формирования адреса микрокоманды УМУ 17; пятое поле управления - формирование микрокоманды трех парал- 0 лельных форматов; первый формат (0-11-й разряды МК) Адрес - формирование константы адреса УМУ 17; второй формат (0-8-й разряды МК) I Константа - формирование констан- 5 ты как операнда АЛУ 3;третий формат (0-4-й разряды МК) Сдвиг - формирование функций сдвигов КСС 9.

Использование многоформатности микрокоманды (употребление отдельных разрядов и полей (слова) микрокоманды для формирования функций разрядов и полей (слова) микрокоманды для формирования функций управления различных устройств) позволяет совратить необходимую длину слова микрокоманды. Например, в рассматриваемой структуре БМУ необходимая длина слова микрокоманды сокращается по 15 разрядов.

Поля управления регистра РМК 21: первое поле управления - управление узлами 12 и 13 АЛУ 3 (48-59-й разряды МК) - разделяется на управление узла 12 (48-53-й разряды МК), 5 на управление узла 13 (54-59-й разряды МК), 50-53-й и 56-59-й разряды МК первого поля участвуют в выборе номера регистра через порты А и В АЛУ 3 и 48, 49 и 54, 55-й разряды 0 МК в выборе источника операнда в АЛУ 3; второе поле управления - управление ДШБ 23 (60-63-й разряды МК), служащие для формирования шестнадцати битов признаков управления е микрокоманды; третье поле управления - управление записью признаков состояния и формирования флага КСС 9 (32-44-й разряды МК); четвертое поле управления - формирование при0

5

0

715

знаков интерфейса, служащих сигналами сопровождения информации интерфейса и управления работой ШФИ10 и PAII11 (45-47-й разряды МК) .

В структурной схеме организации микропрограммного управления (фиг,5) показаны взаимосвязи основных потоков информации УСУ 2 и A3 1 между блоками УМУ 17, РАЖ 18, УПМК 19, РМК 70 „ РМК 21 узлов 12 и 13, АЛУ 3 и КСС 9.

С выхода УМУ 17 по 12-разрядной шине адрес микрокоманды поступает на первую группу входов РАМК 18. Код адреса микрокоманды фиксируется передним фронтом строба Т по первому входу РАМК 18. Временный строб Т - сигнал с периодом 0,5 мкс, скважностью 2. Временной сигнал Т - инверсный сигнал Т.

С выхода РАМК 18 12 старших разрядов адреса с микрокоманды поступают на вход узла 19. Туда же подсоединен сигнал Т; являющийся в этом случае нулевым (младшим разрядом адреса). Поэтому за период прохо&де- ния сигнала Т дважды будет выбираться из узла 19 информация по 32-разрядной шине по нечетному, а затем по (четному адресу. Считанная информация |из УПМК 19 записывается на первые группы входов регистров РМК 20 и РМК 21 в момент переднего фронта сигналов Т и Т, поступающих на первые входы регистров. Информация с первой группы выходов РМК 21 о выборе источников операндов, сдвинутая на полтакта вперед относительно такта работы АЛУ 3, поступает на входы МПА узлов 12 и 13 и синхронизируется стробом Т.

С выбранными узлами 12 или 13 по четырехразрядным входам адреса ячеек 4-7 операндом производятся арифметические и логические операции в АЛУ 3. Результатом операций является выборка признаков состояния с выходом признака состояний ячеек АЛУ 3, поступающих, соответственно на входы признаков условия перехода КСС 9 для хранения и модификации.

Результатом после обработки сигналов состояния на 13-разрядной шине (третья группа выходов РМК 21), поступающих на вход микрокоманд КСС 9, является выработка сигнала F на выходе условия перехода КСС 9, посту5948

лающего в узел 17 на вход (CL). При выработке сигнала F с выхода КСС 9 информация по 12-разрядной шине с

пятой группы выходов РМК 20 проходит по первой группе входов в узел 17 как информация следующего адреса МК. В случае отсутствия сигнала F от КСС 9 12-разрядный адрес из УМУ 17

Q формируется в зависимости от кодовой комбинации на 4-разрядной шине входов в узел 17.

Рассмотрим сущность взаимодействия блоков 1 и 2.

Начало работы инициируется сигналом Установка, поступающим на вход РМК20, по которому адрес микрокоманды с пятого выхода регистра 20 записывается синхронно с сигналом

Q Т за два такта через узел 17 в РАМК 18. Это и является исходным состоянием для начала работы устройства.

Адрес МК формируется на входе узла 19 последовательно за период

5 сигнала Т дважды: в нечетный и четный полупериоды, отличающиеся между собой на единицу младшего разряда. Информация, выбранная по нечетному адресу записывается в РМК 21 по сиг0 налу Т,а по четному в РМК 20 - по сигналу Т. Информация, хранящаяся в регистре РМК 20, управляет работой АЛУ 3. Номер регистра общего назначения (РОН) АЛУ 3 вырабатывается

c узлами 12 и 13 синхронно сигналу Т. Пунктирами на фиг.4 показано прохождение информации одновременно для трех последовательных значений следующего адреса микрокоманд (А А + 1, А + 2).

В момент интервала времени X происходят следующие действия.

Под управлением регистров 20 и 21 выполняются арифметические или логи-

5 ческие операции в АЛУ 3 для Ж А, формируются по ее результатам признаки слова состояния процесса и записываются по концу интервала времени в КСС 9, Под управлением ре- гистра РАМК 18 и признака Т дважды выбираются (нечетный, затем четный адрес МК А+1) информация из ЗУМК 19 и по окончании интервала времени X записывается соответственно в РМК 21 (нечетный адрес) и РЖ 20 (четный адрес). Под управлением 4-раэ- рядной шины с четвертой группы выходов РМК 20 в УМУ 17 формируется следующий адрес выборки микрокоманды

0

91

А+2 и по окончании интервала времени X записывается в РАМК 18.

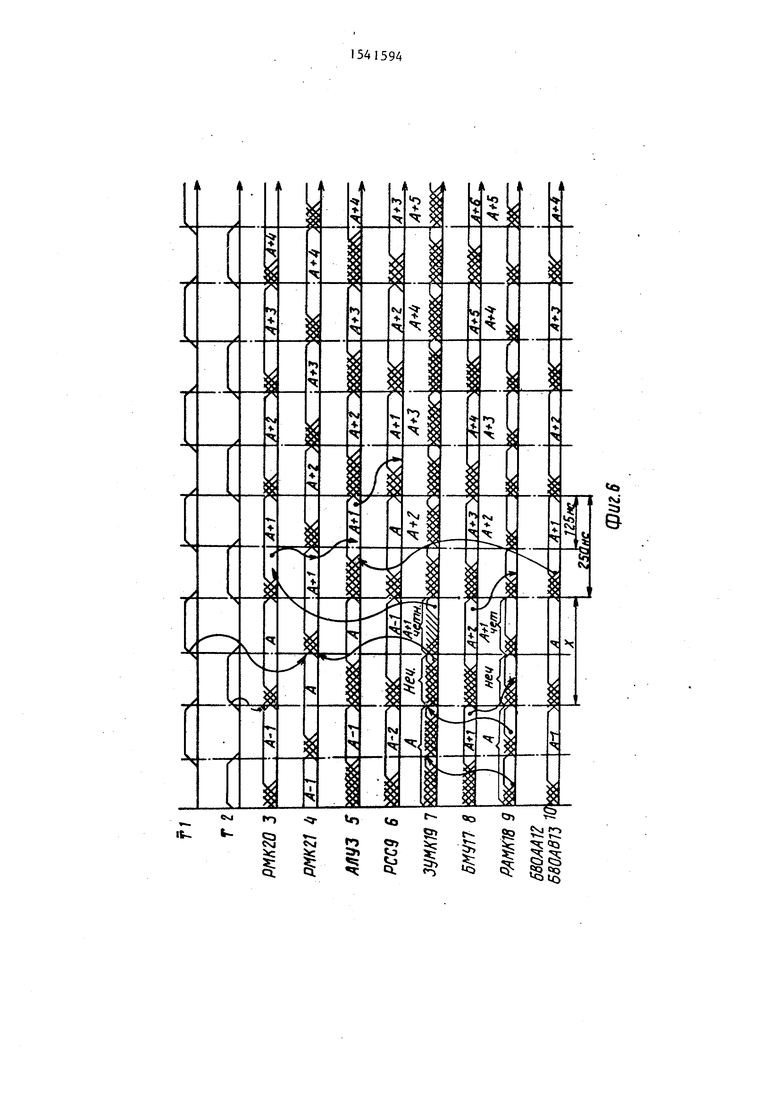

Динамику формирования следующего адреса микрокоманды, работу АПУ и КОС поясняет временная диаграмма, представленная на фиг.6, на которой по вертикали обозначены сверху вниз номера циклограмм, по горизонтали - длительности и виды циклограмм с выделением интервала времени X.

На циклограммах 1 и 2 показана последовательность синхроимпульсов Т и Т, синхронизирующих работу устройства. На циклограммах 1-10 рассмотрена работа последовательности микрокоманд от А-1 до А+5.

Предположим, что момент времени X соответствует выполнению микрокоманды А по циклограмме 5 в АЛУ 3.

Тогда в регистре РМК 20 (циклограммы 3 и 4) существует информация, управляющая работой А-й микрокоманды, а в регистре РМК 21 в течение первого полупериода существует информация для А-й микрокоманды, а в течение второй половины периода - для А+1-й микрокоманды. Б то же время под управлением РАМК 18, содержащим информацию о номере микрокоманды А-Н (циклограмма 9), выбирается из УП 19 (циклограмма 7) нечетный, а затем четный адрес А+1-й микрокоманды.

Выбранная информация, соответствующая А+1-й микрокоманде, из УПМК 19 по нечетному адресу записывается в РМК 21 (циклограмма 4) и по четному адресу - в РМК 20 (циклограмма 3). Номер РОН АЛУ 3, содержащий операнд, необходимый для выполнения операции АЛУ, хранится в узле 12 или 13 синхронно с работой АЛУ 3 (циклограмма 10).

Из временной диаграммы (фиг.6) и структурной схемы организации управления (фиг.5) видно, что в предложенной схеме реализован конвейер на 2 выработки следующего адреса микрокоманды, т.е. когда выполняются действия под управлением микрокоманды А в АЛУ 3, под управлением РАМК 18 выбирается из УПМК 19 информация А+1-й микрокоманды, а в УМУ 17 вырабатывается адрес А+2-й микрокоманды. Совмещение процесса выработки.следующего адреса для микрокоманд А, А+1, А+2 создает воз1594

10

5

можность значительного сокращения времени его выполнения.

Двукратная выборка из УЛМК за один такт позволяет в два раза сокра- тить количество микросхем УПМК 19. Временной такт (при двукратной выборке информации из ЗУМК 19) уменьшается с Т 300 не до Т 250 не Q в конкретном примере реализации.

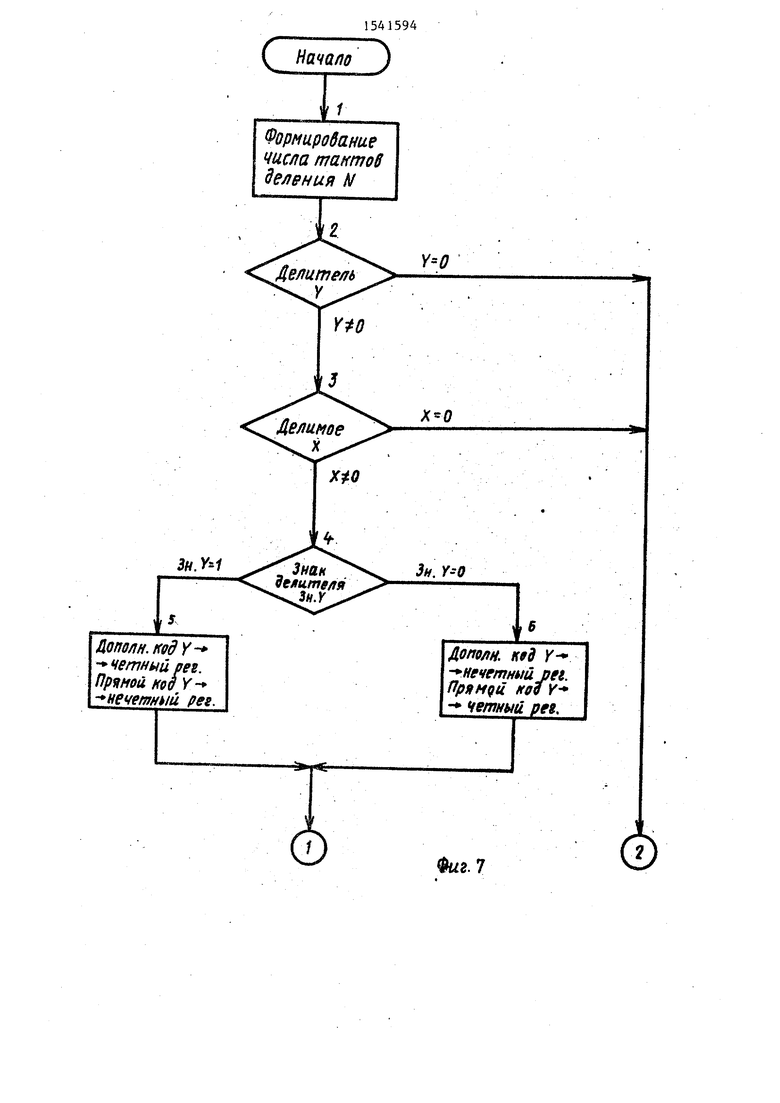

На фиг.7 и 8 приведены алгоритмы выполнения операции деления (способ деления - без восстановления остатка).

Оператор 1 выполняет следующие действия: устанавливает необходимое число циклов (равное количеству разрядов делителя в счетчике циклов УМУ 17; из внешней памяти выбирают- 0 ся значения делимого (двойной длины - 32 разряда) и делителя (16 разрядов) ; делимое размещается в реги- страх-сдвигателях РОН и РАЛУ 3; делитель в другом регистре РОН АЛУ 3. 5 Операторы 2 и 3 по значению делителя Y 0 или делимого X 0 передают управление на выполнение действий оператора 12, формирующего признаки слова состояния по резуль- 0 татам выполнения операции деления, при значениях операндов Y 0,X f О передается управление на оператор 4.

Оператор 4 по значению старшего знакового разряда делителя передает управление на оператор 5 в случае Зн Y 1, или на оператор 6 в случае Зн Y 0.

Оператор 5 выполняет подготовительные операции по размещению в Q двух соседних регистрах РОН АЛУ значения делителя так, чтобы в выбранном номере - четном размещался прямой код делителя, а в нечетном - дополнительный. Оператор 6 выполня- с ет действия, обратные действиям оператора 5, т.е. в нечетный РОН АЛУ записывается дополнительный, а в четный прямой код делителя. Оператор 7 выполняет действия первого Q такта деления, после чего производится анализ результатов выполнения действия первого такта оператором 8.

В случае некорректности деления (переполнение разрядной сетки 16-раз- с рядного результата деления) передается управление оператору на формирование признаков выполнения операции, иначе выполняются остальные такты деления операторами 9-11 (анализ

5

1

условий некорректности деления здесь и далее не рассматриваются).

Рассмотрим отдельно цикл деления (фиг.9).

В устройстве все действия указанных операторов выполняются операторами 9 и 10 (фиг.8), представляющими собой две микрокоманды. Действия этих микрокоманд включают сложение остатка и делителя; вычитание из остатка делителя.

Эти действия выполняются в зависимости от значений знаков делителя и старшего разряда делимого (остатка) согласно табл.3.

Таблица 3

154159412

ходный разряд регистра РАПУ согласно табл.4.

10

Т а

лица

Т а

лица

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Система обработки нечеткой информации | 1987 |

|

SU1444803A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Устройство для организации мультиветвления процессов в электронной вычислительной машине | 1980 |

|

SU922743A1 |

Изобретение относится к области вычислительной техники и может быть использовано при проектировании арифметических устройств вычислительных машин. Цель изобретения - повышение быстродействия основных команд операций деления при одновременном сокращении оборудования. Устройство содержит арифметико-логический блок, выполненный из N вычислительных ячеек и узла ускоренного переноса, шинный формирователь, контроллер состояний, регистр адреса памяти, два узла выборки операндов, каждый из которых содержит соединенные мультиплексор адреса и регистр адреса, и блок микропрограммного управления, состоящий из регистра команд, дешифратора команд, дешифратора прерывания, узла микропрограммного управления, узла памяти микрокоманд, первого регистра микрокоманд и узла обработки прерываний, а также связи между указанными элементами согласно чертежу. Новым является введение в блок микропрограммного управления регистра адреса микрокоманд, второго регистра микрокоманд, дешифратора битовых сигналов и формирователя разрядов частного. В узел выборки операндов введен дешифратор адреса, включенный между вторым выходом мультиплексора адреса и вторым входом регистра адреса. Формирователь разрядов частного содержит дешифратор частного и дешифратор адреса. 9 ил.

Примечание. Старший разряд делимого (остатка) анализируется после действий в предыдущем такте деления.

В микрокоманде цикла деления указан нечетный адрес РОН той пары регистров РОН, в которых предварительно оператором 5 или 6 были сформированы прямые или дополнительные коды делителя. Поэтому, учитывая в микрокомандах нечетный адрес одного из них, позволяют узлу 12 по старшему разряду делимого (вход 4) и признаку деления (вход 5) выбирать нужный операнд (делитель) в прямом или дополнительном коде для выполняемых микрокомандами действий сложения.

Одновременно полученный результат в регистрах - сдвигателя РОН (.остаток) и младшие разряды делимого (регистр Q) двигаются влево на один разряд. Но значению сдвигаемого влево старшего разряда РОН (остатка) и фиксированного в РК знаке делителя формирователем разрядов частного ФРЧ24 и КСС 9 вырабатывается разряд частного и записывается в освободившийся при сдвиге влево ис

Формирование разрядов частного в КСС9 производится ФРЧ24 за счет коммутации функции сдвига (коды 0110 или 0111), изменяя значение младшего разряда функции.

Коды управления функциями сдвига соответствуют видам сдвига (табл.5).

35

Таблица 5 Вид сдвига

Код сдвига

0

0110

Per.РОН 15 О

Per. 15 О

О Разряд

«-{ Остаток |«- Частное-частного

Per. РОНPer, 1

0111 15 015 О

Остаток -)Частное |«-

Функция сдвига 0110 указывается в каждой микрокоманде цикла Деление . Младший разряд функции сдвига коммутируется в ФРЧ24. Цикл Де- ление выполняется за счет повторения (-Ј2)

раз двух микроко

манд, где N - число разрядов делителя) .

Первая микрокоманда цикла Деление производит декремент (вычитание) содержимого регистра-счетчика циклов БМУ и сравнение полученного

результата с нулем. Если N ф 0 происходит передача управления на повторение микрокоманды, если N 0 передается управление на оператор 12.

Таким образом, цикл Деления заключается в выполнении циклически двух микрокоманд (при организации конвейера выборки следующего адреса микрокоманды с модулем два), в каждо из которых происходит формирование одного разряда частного. В итоге за цикл деления формируются два разряда частного.

Микрокоманды (21-я и 9.2-я) цикла Деление отличаются между собой только адресной функцией УМУ 2 (фиг.7). В первой микрокоманде (адрес А) производится декремент счетчика (уменьшение счетчика на единицу младшего разряда) цикла УМУ 2, передача управления в зависимости от его значения. Во второй микрокоманде производится безусловная (обязательная после условной: условия ветвлений) передача управления на микрокоманду с адресом А+1.

Работа по выполнению арифметических и логических операций над операндами в АЛУ 3 производится под управлением полей микрокоманды с первых групп выходов РМК 21 (12-разрядная шина) и РМК 20 (9-разрядная шина) . Под управлением сигналов на первой группе выходов РМК 21 производится выбор узлов 12 и 13 источников адресов операндов внутреннего ОЗУ АЛУ 3 (источник 1-й - РК 14, источник 2-й - РМК 21). С выходов РМК 20 производится управление арифметическими или логическими операциями в АЛУ 3 над операндами. Операнды могут быть использованы в зависимости от значений функций управления АЛУ 3, поступающих с первы& (9-разрядная шина) и пятых (5-разрядная шина) выходов РМК 20, из внутреннего ОЗУ АЛУ 3 или с шины данных 25 через ШФИ 10 на D-входы АЛУ 3.

По результатам выполнения операций над операндами в АЛУ 3 вырабатываются признаки (Z, С, V, N-вхо- ды КСС 9) слова состояния АЛУ 3. По сигналам управления с третьей группы выходов РМК 21 (13-разрядная тина) в КСС 9 запоминаются и обрабатываются признаки слова состояния и в зависимости от их комбинаций вырабатывается сигнал F для органи1594

14

зации процесса ветвлений микропрограммы . Процесс обмена информацией с внешними устройствами производится по шинам адреса 26 и данных 25. При необходимости перехода обмена информацией с внешними Носителями информации по интерфейсу типа узкая шина шины Адрес и Данные объединяются.

С первых выходов РАЛ 11 в шину 26 адреса поступает 16-разрядный код адреса и признаки для его сопровождения .

5 Результат операций над операндами с первых выходов ячеек 4-7 АЛУ 3 поступает на первые входы ШФИ 10 для запоминания в буферном регистре и трансляции через выходы ШФИ 10 на 0 D-входы ячеек 4-7 АЛУ 3 в качестве операнда следующей операции или через первые входы/выходы ШФИ 10 на шину 25 данных для запоминания во внешних носителях информации. 5 в случае запоминания результата вычислений во внешнем ОЗУ микрокоманды генерируют адрес ячейки внешнего ОЗУ с первых выходов РАЛ 11 на шину 26, обеспечивают работу ин- 0 терфейса по приему адреса с РАЛ 11 и данных с ШФИ 10 по шине 25 во внешние ОЗУ.

За счет свертки временных процессов, происходящих в ЕМУ 2 во вре- - мя выборки адреса следующей микрокоманды, достигается при сокращении оборудования БМУ 2 более короткий такт обработки информации (250 не).

0 Различные типы операций арифметических и логических операций выполняются за время: Типа регистр регистра 1 мкс (4 такта) 5 Память - регистр 2 мкс (8 тактов) Умножение 6-10 мкс (24 40 тактов) Деление10-15 мкс (40 60 тактов)

0 Диапазон времени выполнения определяется реализуемой системой команд.

Рассмотрим работу АУ, начиная с момента включения, т.е. инициализа- с ции начального адреса микропрограммы включения. Сигнал Установка по входу 30, сигнализирующий об отсутствии вторичных напряжений питания АЛУ или наличии переходных

15

процессов при их установлении, поступает на установочный вход PMK2Q. В регистре РМК 20 под управлением сигнала установка четвертым полем (фиг.З) вырабатывается функция управления УМУ 17 для выработки адреса 0...0, поступающего с четвертой группы выходов по 4-разрядной шине на группу входов УМУ 17. УМУ 17 вырабатывает 12-разрядный адрес (0... 0) и выставляет его на выходе. РАМК 18 по синхросигналу Т записывает указанный 0...0 (четный) адрес и начинается выборка содержимого нулевой ячейки УПМК 19 (старшие разряды 32-63) с записью информации по синхросигналу Т в РМК 21.

Синхроимпульс Т подключает младший разряд адреса на входе УПМК 19. Адрес 00...01 (нечетный) выбирает из УПМК 19 содержимое первой ячейки и записывает по синхросигналу Т в РМК 20 (младшие разряды 0-31). Так заканчивается процесс инициализации начального адреса микропрограммы Инициализация, в процессе BI&- полнения которой загружаются, устанавливаются значения различных счетчиков и узлов АБ1 и БУ2 в исходное состояние. Программа инициализации заканчивается загрузкой в РК14 первой команды по сигналу из ДШБС 23, поступившей из запоминающего устройства. Разряды команды по 16-разрядной шине поступают в ДШК 16. Данные на управляющем входе ДШК 16 уп- равляют выходами дешифратора, переключая выходы из состояния высокого импеданса в активный режим. В то же время сигналы на выходе ДШП 15 и на пятой группе выходов РМК 20 (обратный адрес) находятся в состоянии высокого импеданса, т.е. отключены.

С выхода ДШК 16 по 12-разрядной шине начальный адрес микропрограммы команды поступает в УМУ 17, транслируется им, эмулируется в зависимост от функции управления передачи адреса, поступающего с четвертой группы выходов РМК 20. Эмулированный адрес поступает с выхода УМУ 17 на информационные входы РАМК 18 и, как описано, в случае выборки адреса инициализации выбирается дважды в течение такта из УПМК и записывается в регистры РМК 21 и РМК 20.

Предположим, что очередная выбраная из внешнего накопителя по шине

159416

данных 25 команды - команда Деление. Из условия, что в регистрах РМК 20 и РМК 21 выставлен код первой микрокоманды деления, начинается выполнение микропрограммы деления согласно алгоритму (фиг.7 и 8). Выполнение оператора 1 заключается в действиях по выборке информации

JQ делимого и делителя из внутренних регистров РОН АЛУ или внешней памяти.

Местоположение (исходное) операндов и методы адресации памяти

15 определяются системой команд. Предположим, что реализована система команд типа СМ-4. В этом случае информация делимого располагается в двух регистрах РОН, четном и нечет20 ном, номер первого из них указан в команде. Делитель в зависимости от системы адресации, указанной в команде, выбирается последовательностью микрокоманд по сформированному

25 адресу из внешней памяти. Предположим, что в команде используется метод адресации9 когда адрес размещается в РОН с номером, указанным в 0-2 разрядах команды (метод адреса30 ции указан в 3-5-м разрядах). Первые микрокоманды оператора 1 выставляют значение указанного РОН АЛУ 3 на выход АЛУ 3 и записывают содержимое его в РАН 11 как адрес операнда на магистрали 26.

Выбранный из внешней памяти операнд (делитель) с магистрали 25 поступает в ШФИ 10 и фиксируется в буферном регистре. ШФИ 10 осущестдд вляет процедуру интерфейсного обмена, т.е. прием информации по сигналам сопровождения и выдачу соответствующих кватирующих сигналов о приеме информации под управлением

дс управляющих сигналов РМК микрокоманды 2. Третья микрокоманда оператора 1 переписывает информацию делителя из буферного регистра ШФИ 10 в рабочий РОН АЛУ 3. Четвертая микро5Q команда оператора 1 формирует константу о количестве циклов повторения микрокоманд цикла Деление. С пятой группы выходов РМК 20 по 12-разрядной шине Адрес поступает в УМУ 17, где информация запомина35

55

ется в счетчике циклов.

Выработка следующего адреса микрокоманды при переходе от первой микрокоманды к второй и т.д. осуществляется с четвертой группы выходов РМК 20 по 4-разрядной шине. Причем каждая микрокоманда под номером А указывает адрес выборки из У11МК А+2-и микрокоманды.

Выполнив действия операторов 1, а затем операторов 2 и 3 (действия их рассмотрены при описании фиг.7 и 8),производится подготовка информации делителя действиями микрокоманд оператора 5 или 6. Микрокоманды оператора 5 загружают в два соседних рабочих регистра FOH АЛУ (четный и нечетный) информацию делителя; четный регистр (например, номер 14) РОН - дополнительный код, в нечетный (15) РОН - прямой. Действия микрокоманд оператора 9 загружают информацию в указанные регистры наоборот: в четный (14) - прямой, и нечетный (15) - дополнительный код делителя.

После указанных подготовительных действий производится выполнение микрокоманд 1-го такта Деления. Рассмотрим, что представляют собой поля управления микрокоманды Деление . В поле 5 РМК 20 применяется формат 3 Сдвиг, выполняется управление функциями сдвига КСС 9, а именно сдвиг влево регистров РОН и Q (код 0110).

В четвертом поде выставляется информация, управляющая УМУ 17 так, чтобы производился декремент регистра-счетчика циклов и анализ его состояния с переходом по состоянию

Lcu

0 на повторение микрокоманды

деления, а по состоянию R сч 0 - на выполнение действий оператора 12.

Первым полем РЖ 20 управляется АЛУ 3 - производится операция суммирования и пересылка полученной суммы по адресу (номеру РОН), указанному в первом поле узла 13, где содержится делимое, а в последующем - остаток. В первом поле узла 12 указывается адрес (номер РОН),информация в котором есть делитель с указанием о его расположении в нечетном РОН (в нашем примере 15).

Узел 12 эмулирует с помощью дешифратора адреса ДША 3, исходное единичное значение нулевого разряда номера РОН под управлением старшего разряда регистра сдвигателя PAMN АЛУ 3. При PAMN ъ 0 - адрес (номер РОН) с выхода узла 12 - четный (14). При

о

PAMN 1 - адрес (номер РОН) с выхода узла 12 - нечетный (15).

Под управлением первого поля РМК 20 АЛУ 3 выполняет действие сложения содержимого номера РОН (R),указанного в микрокоманде, где размещено делимое (остаток) и делитель, в прямом или дополнительном кодах,

0 размещенных ранее в четных и нечетных регистрах РОН оператором 5 или 6 (фиг.7 и 8). Узел 12, эмулируя в зависимости от значений старшего разряда РАМ АЛУ 3 (делимого/остат5 ка) выборку четных или нечетных регистров РОН АЛУ 3, производит действия оператора 12 или оператора 13, соответствующие известным операторам.

0 Одновременно под управлением сигналов Знак делителя (вход 1), старшего разряда делимого/остатка (вход 3) в ФРЧ 24 эмулируется младший разряд функции Сдвиг влево КСС 9 7

5 так, чтобы выполнились действия операторов 14,16 или 14, 17.

Алгоритм выполнения действий по формированию разряда четного соответствует описанному в табл.4 и оп0 ределяется распайкой ФРЧ 24 (фиг.2), представляющего собой мультиплексор с организацией 1.

Устройство 24.1 дешифрации адреса представляет собой логическую сторону ИЛИ. Эмулирование значения младшего разряда функции сдвига (4-й разряд РМК 20) производится в соответствии с табл.6 и 7 состояний входных и выходных сигналов ФРЧ 24 и ДШЧ 24.2.

5

С

5

О

1

1

О

Текущее значение 4-го разрядаРМК 20

1

О О 1

1

О О

1

о 1 о

1 о 1

о

1

Примечание. Вход 1 - значение знакового разряда делителя;

1915

вход 2 - значение старшего разряда делимого остатка; вход 3 - значение признака Деление ; выход - значение младшего разряда (Ор) функции управления Сдвиг (4-й разряд

РМК 20).

Состояние входных и выходных сигналов ДШЧ 35 (мультиплексор 8-1) показано в табл.7.

Таблица 7

Выход

Входы управления 11 I 10 1 9

ю

О О О О

1

О О

1 1

о 1

о

1

о

1

- комПримечание. DO-D7 мутируемые на выход входные сигналы; DO-D3 - сигналы низкого уровня; D1 и D2 - высокого уровня; D4 и D5 - не коммутируются; D6 и D7. - текущее значение нулевого разряда функции Сдвиг (4-й разряд РМК 20).

Во время выполнения цикла Деление производится декремент содер- жимого счетчика циклов и его анализ. Производится передача управления на повтор ее выполнения при IN сц цикл | ф 0 и на выполнение действий оператора 12 при выходе из цикла Деление при 1 N сц цикл, | 0.

Необходимо дать разъяснение принципа приема и обработки сигналов прерываний УОП 22. Узлом 22 в течение выполнения текущей микропрограммы команды принимаются и запоминаются сигналы прерываний от ЦВМ. Узел 22 осуществляет обработку прерываний согласно присваиваемому им приоритету. Наивысший из принятых сигналов прерываний преобразуется в 3- разрядный вектор, поступающий с первой группы выходов УОП 22 на информационные входы ДШП 15. Выборка по адресу вектора разрешается после выполнения микропрограммы команды в момент загрузки начального адре159А

20 са, следующей рз ДШК 16. С второй

группы выходов РМК 20 поступает управление выбора и загрузки адреса и микрокоманды из трех возможных источников; с пятой группы выходов РМК 20, с выходом ДШП 15 и ДШК 16. Состояния выходов этих источников в любой момент времени таковы,

что активным может быть только один, а остальные должны находиться в состоянии высокого импеданса (отключены) , возможно отключение и всех трех источников. Если с второй груп5 пы выходов УОП 22 вырабатывается по 3-разрядной шине сигнал ПРЕР, свидетельствующий о наличии требования хоть одного прерывания, происходит определенная коммутация выхо0 дов тристабильных источников адреса микрокоманды ДШП 15, ДШК 16, РМК 20, а именно активным становится выход ДШП 15.

Результатом является то, что

5 вместо загрузки начального адреса следующей команды из ДШК 16 происходит загрузка начального адреса микропрограммы обработки прерываний сигнала прерывания высшего приори0 тета из принятых.

Концом выполнения микропрограммы обработки прерывания является вновь микрокоманда загрузки начального адреса микрокоманды из ДШК 16. Если прерывания отсутствуют, то происходит переход на выполнение следующей команды, поступающей из регистра команд 14.

5

Формула изобретения

Арифметическое устройство с микропрограммным управлением,содержащее арифметико-логический блок,содержащий N вычислительных ячеек, узел ускоренного переноса, шинный формирователь, контроллер состояний, регистр адреса памяти, два узла выборки операндов, каждый из которых содержит мультиплексор адреса и регистр адреса, и блок микропрограммного управления, содержащий регистр команд, дешифратор прерываний и дешифратор команд, узел микропрограммного управления, узел памяти микрокоманд, первый регистр микрокоманд и узел обработки прерываний, причем пина данных устройства соедийена с информационным входом регистра команд и первым информационным входом шинного формирователя, информационные выходы которого соединены с информационными входами N вычислительных ячеек, информационные выходы которых соединены с информационными входами регистра адреса памяти, выходы которого являются шиной адреса устройства,первый и второй выходы двунаправленной цепи сдвига i-й вычислительной ячейки (где i - 1,2,...,N-1) соединены с первым и вторым двунаправленными входами сдвига (1+1)-й вычислительной ячейки соответственно, первый и второй двунаправленные входы сдвига первой вычислительной ячейки соединены с первым и вторым двунаправленными выходами сдвига соответственно контроллера состояний, третий и четвертый двунаправленные выходы сдвига которого соединены с первым и вторым двунаправленными выходами сдвига N-й вычислительной ячейки, первый, второй и третий выходы признака состояний первой вычислительной ячейки соединены с первым, вторым и третьим входами признаков условного перехода контроллера состояний, выход переноса которого соединен с входом последовательного переноса N-й вычислительной ячейки и с входом переноса узла ускоренного переноса, группа информационных входов которого соединена с входами последовательного переноса 1-х вычислительных ячеек и выходами распространения и разрешения переноса (i+1)-x вычислительных ячеек, первая группа выходов регистра команд соединена с группой информационных входов дешифратора команд, группа выходов которого соединена с первой группой адресных входов узла микропрограммного управления, вторая группа адресных входов которого соединена с группой выходов дешифратора прерываний, ин- . формационный вход которого соединен с выходом вектора узла обработки прерываний, вторая и третья группы выходов регистра команд соединены с управляющими входами мультиплексоров адреса первого и второго узлов выбора операндов соответственно, выходы которых соединены с информационными входами соответствующего регистра адреса, выход условия пе-

0

5

0

5

0

5

0

5

рехода контроллера состояний соеди- нен с входом разрешения выборки адреса узла микропрограммного управ- лення,вход прямых тактовых сигналов устройства соединен с синхровхода- ми контроллера состояний, узла микропрограммного управления, регистров адреса первого и второго узлов выбора операндов, выходы которых соединены с первым и вторым адресными входами соответственно всех вычислительных ячеек, отличающееся тем, что, с целью повышения быстродействия выполнения основных команд и команды операции деления при одновременном сокращении оборудования, в блок микропрограммного управления введены регистр адреса микрокоманд, второй регистр микрокоманд, дешифратор битовых управляющих сигналов и формирователь разрядов частного, содержащий дешифратор адреса и дешифратор частного, в первый узел выбора операндов введен дешифратор адреса, первый информационный вход которого соединен с выходом мультиплексора адреса первого узла выбора операндов, выход дешифратора адреса первого узла выбора операндов соединен с входом разрешения записи регистра адреса первого узла выбора операндов, выход узла микропрограммного управления соединен с информационным входом регистра адреса микрокоманд, выход которого соединен с адресными входами узла памяти микрокоманд, выход которого соединен с информационными входами первого и второго регистров микрокоманд, синхровход узла микропрограммного управления соединен с синхровходами регистра адреса микрокоманд, узла памяти микрокоманд, первого регистра микрокоманд и всех вытактовых сигналов устройства соединен с синхровходом второго регистра микрокоманд, первая группа выходов первого регистра микрокоманд соединена с входами микрокоманд всех вычислительных ячеек, вторая группа выходов первого регистра микрокоманд соединена с входами узла обработки

прерываний, выходы сигнала прерывания которого соединены с управляющими входами дешифратора прерываний, дешифратора команды и первого регистра микрокоманд, вход установки в

23

154

начальное состояние которого соединен с входом установки устройства, третья группа выходов первого регистра микрокоманд соединена с входами управления приемом данных, четвертая группа выходов первого регистра микрокоманд соединена с управляющими входами узла микропрограмм . много управления, третья группа адресных входов которого соединена с пятой группой выходов первого регистра микрокоманд, шестая группа выходов которого соединена с входом константы шинного формирователя, вход адреса которого соединен с информационным входом регистра адреса памяти, управляющие входы которого соединены с первой группой выходов второго регистра микрокоманд и с входами управления адреса шинного формирователя, седьмая группа выходов первого регистра микрокоманд соединена с первой группой входов микрокоманд контроллера состояний, вторая группа входов микрокоманд которого соединена с второй группой выходов второго регистра микрокоманд, третья группа выходов которого соединена с входами дешифратора битовых управляющих сигналов, первый выход которого соединен с входом разрешения записи регистра команд, выход знакового разряда которого соединен с первым управляющим входом дешифратора частного, второй управляющий вход которого соединен с первым информационным

59424

входом дешифратора адреса формирователя разрядов частного, вторым входом дешифратора адреса первого узла выбора операнда и вторым выходом дешифратора битовых управляющих сигналов, четвертая и пятая группы выходов второго регистра микрокоманд соединены с информационными входами

Q мультиплексоров адреса первого и второго узлов выбора операндов соответственно, выходы регистров адреса первого и второго узлов выбора операнда соединены с первыми и вторыми

5 входами адреса соответственно всех вычислительных ячеек, выход младшего разряда первого регистра микрокоманд соединен с первым, вторым, третьим и четвертым информационными

0 входами дешифратора частного, пятый и шестой информационные входы которого соединены с входом логической единицы устройства, вход логического нуля устройства соединен с седьмым

5 и восьмым информационными входами дешифратора частного, третий управляющий вход которого соединен с выходом дешифратора адреса, формирователя разрядов частного, второй ин0 формационный вход которого соединен с третьим информационным входом дешифратора адреса первого узла выбора операндов и вторым двунаправленным входом сдвига первой вычислительной

с ячейки, выход дешифратора частного соединен с входом микрокоманды сдвига контроллера состояний.

Формат 1 „Адрес

Формат Константа

Формат 1 „ Шаг

Разряды

Поле управления

ffopMupoSuHue адреса УМУ

Формирование константы АЛу

оТТШзЫЯбМлСХМХ

Управление функциями сШга. ffccg

ХХХХХХХ

Управление

пригнан- fad а ч ей.

Залных

УправлениеУМУ

§5

S§

И

& и

«I

Управление АЛУ

0123

4 5

8

10

11

ЩЩЩ15 ЩЩМ

ФигЬ

Фиг. 5

е

s «

wgiwi

Лорнирование признаков caeta состояния и, лор- ректоров ко, раум mania делении

ЕГ

( Конец . J

Ю

/iff О

Фиг. 9

| Самофалов К.Г | |||

| Электронные цифровые вычислительные машины | |||

| Киев: Вища школа, 1976 | |||

| Мик Дж., Брик Дж | |||

| Проектирование микропроцессорных устройств с раз- рядно-модульной организацией | |||

| М.: Мир, 1984, с.152-162, рис.3.23. |

Авторы

Даты

1990-02-07—Публикация

1988-07-08—Подача