Изобретение относится к вычислительной технике, предназначено для использования в качестве аппаратног расширителя в микропроцессорных системах и может найти применение в приборостроении, управляющих и информационно-измерительных системах.

Цель изобретения - повышение точности интерполяции функций за счет увеличения количества используемых узловых точек

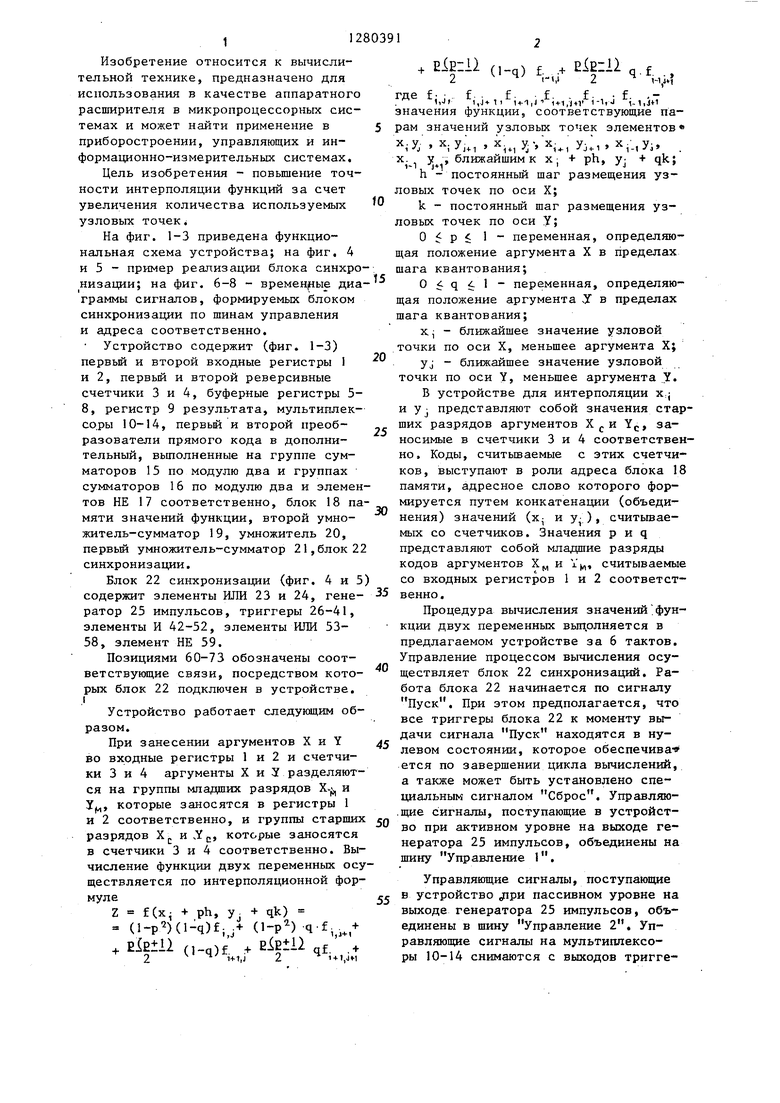

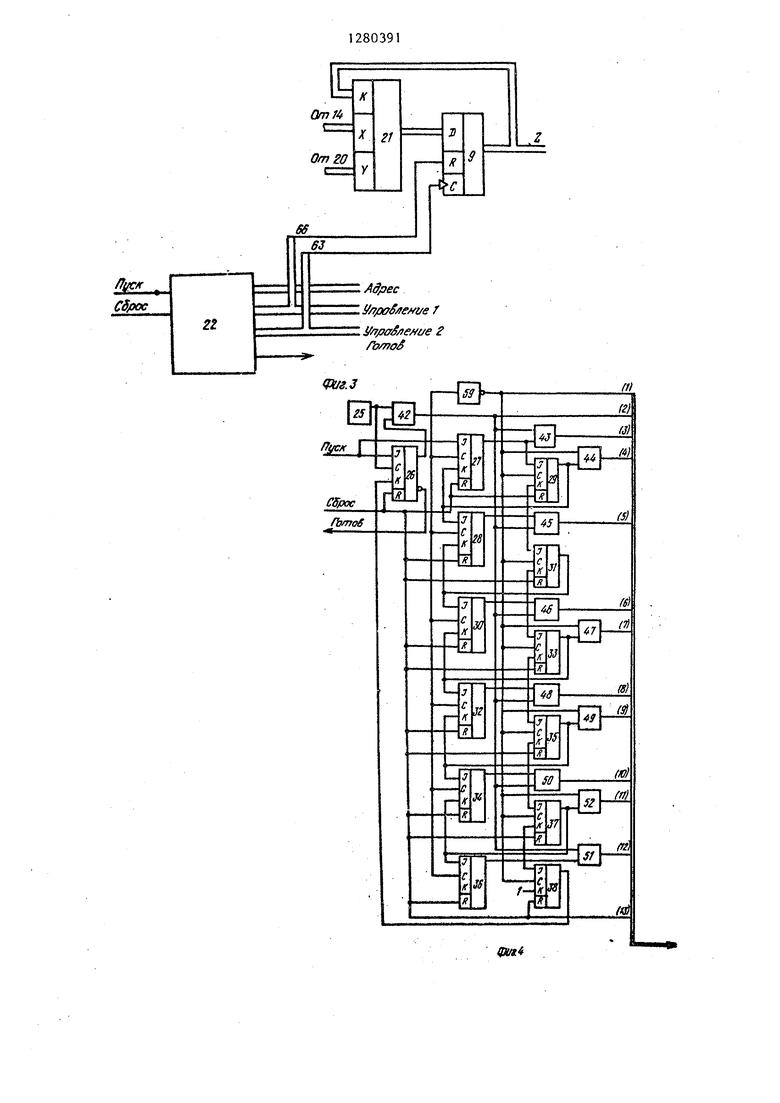

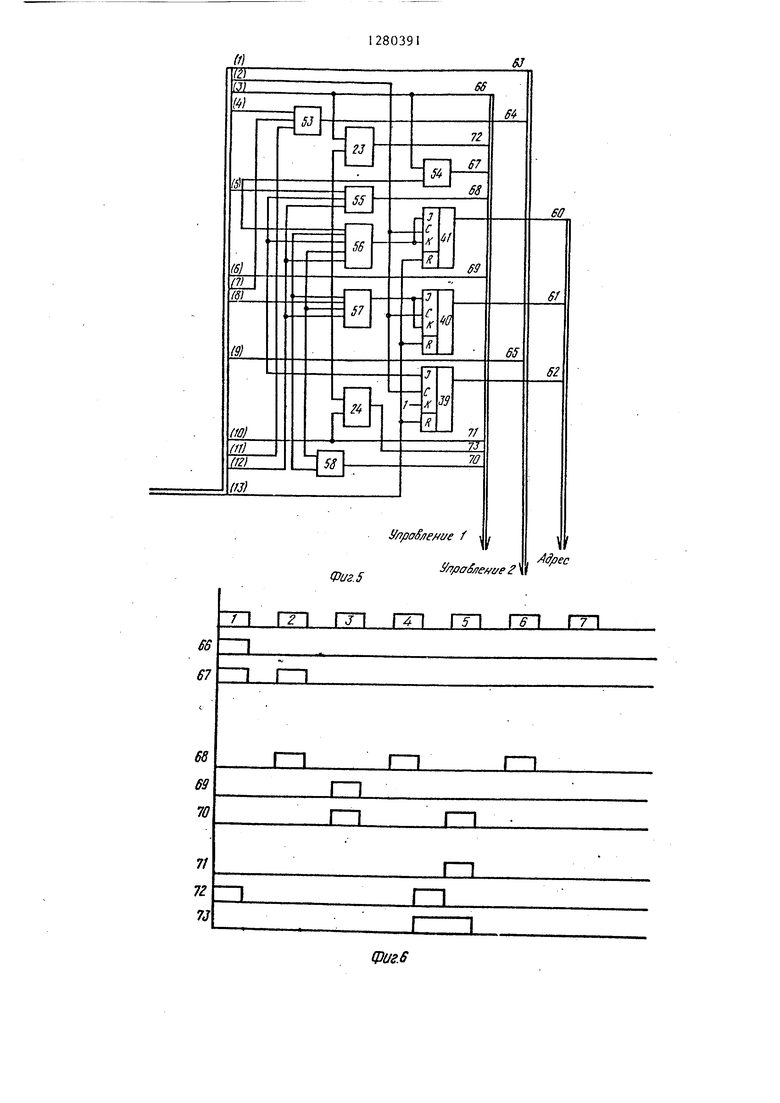

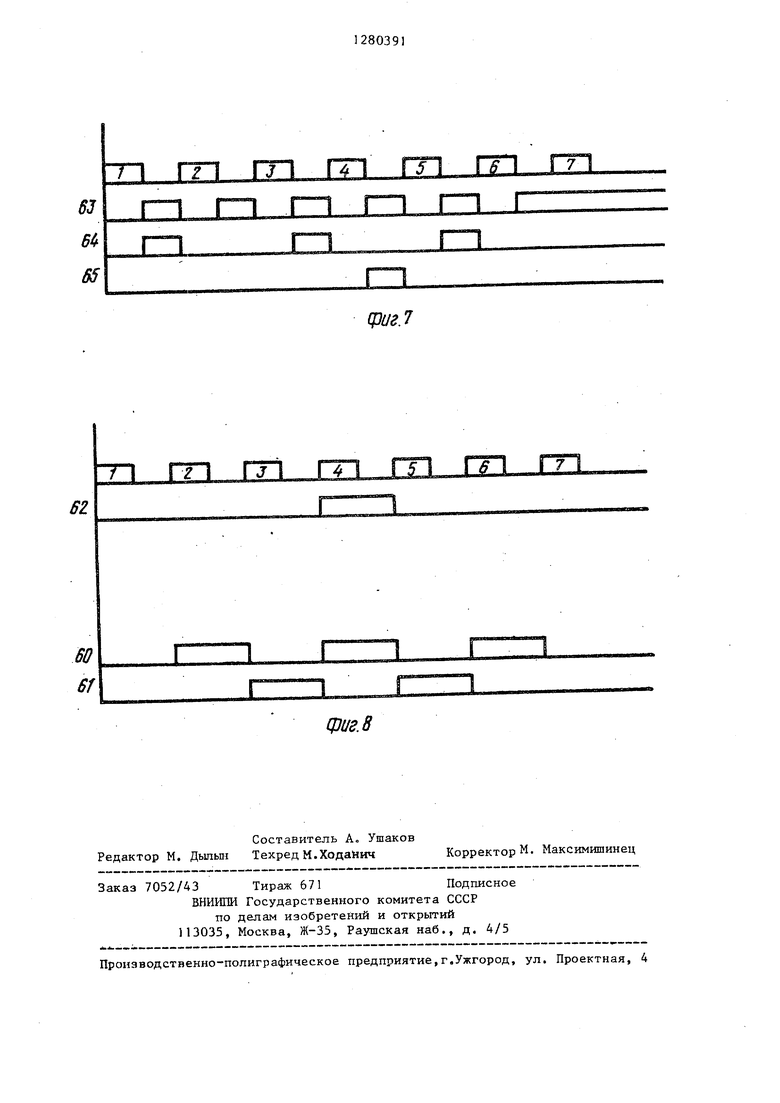

На фиг. 1-3 приведена функциональная схема устройства; на фиг. 4 и 5 - пример реализации блока синхр низации; на фиг. 6-8 - временные ди граммы сигналов, формируемых блоком синхронизагщи по шинам управления и адреса соответственно.

Устройство содержит (фиг. 1-3) первьй и второй входные регистры I и 2, первый и второй реверсивные счетчики 3 и 4, буферные регистры 5 8, регистр 9 результата, мультиплексоры 10-14, первьй и второй преобразователи прямого кода в дополнительный, выполненные на группе сумматоров 15 по модулю два и группах сумматоров 16 по модулю два и элеметов НЕ 17 соответственно, блок 18 пмяти значений функции, второй умножитель-сумматор 19, умножитель 20, первьй умножитель-сумматор 21,блок синхронизации.

Блок 22 синхронизации (фиг. 4 и

содержит элементы ИЛИ 23 и 24, гене

ратор 25 импульсов, триггеры 26-41, элементы И 42-52, элементы ИЛИ 53- 58, элемент НЕ 59.

Позициями 60-73 обозначены соответствующие связи, посредством которых блок 22 подключен в устройстве. I

Устройство работает следующим образом.

При занесении аргументов X и Y во входные регистры 1 и 2 и счетчики 3 и 4 аргументы X и У разделяются на группы младших разрядов Х.; и У(, которые заносятся в регистры 1 и 2 соответственно, и группы старших разрядов Xj, и ,Y(, которые заносятся в счетчики 3 и 4 соответственно. Вычисление функции двух переменных осуществляется по интерполяционной формуле

Z f(x- + ph, у, + qk)

(l-p)(l-q)f. (1-р) q.f,,-b

ElEiii (,q)f. ElEiii qf. , 2 - Ч ,+,j 2 i + i,jfi

.2lpo-.)f,.,.,f,.,.

i-i

i,

i,Ji i,j-ni i4.i,J Ui/j4v i-i.J i-i,5+ значения функции, соответствующие парам значений узловых точек элементов

У. i У.м i., У, ., yjli X, -, У. .

+ ph, yj + qk;

h - ПОСТОЯННЕЙ шаг размещения узловых точек по оси X;

k - ПОСТОЯННЕЙ шаг размещения узловых точек по оси У;

О 5 Р 1 переменная, определяющая положение аргумента X в пределах шага квантования;

О Ч i переменная, определяющая положение аргумента У в пределах шага квантования;

X i ближайшее значение узловой точки по оси X, меньшее аргумента X;

yj ближайшее значение узловой точки по оси Y, меньшее аргумента Y. В устройстве для интерполяции X:j и yj представляют собой значения старших разрядов аргументов Y, заносимые в счетчики 3 и 4 соответственно. Коды, считьшаемые с этих счетчиков, выступают в роли адреса блока 18 памяти, адресное слово которого формируется путем конкатенации (объединения) значений (х; и ) , считьгоае- мых со счетчиков. Значения р и q представляют собой младшие разряды кодов аргументов Х„ и Y, считываемые со входных регист1ров 1 и 2 соответст0

0

0

5

Процедура вычисления значений функции двух переменных вьтрлняется в предлагаемом устройстве за 6 тактов. Управление процессом вычисления осуществляет блок 22 синхронизации. Работа блока 22 начинается по сигналу Пуск. При этом предполагается, что все триггеры блока 22 к моменту выдачи сигнала Пуск находятся в нулевом состоянии, которое обеспечива- ется по завершении цикла вычислений, а также может быть установлено специальным сигналом Сброс. Управляющие сигналы, поступающие в устройство при активном уровне на выходе генератора 25 импульсов, объединены на шину Управление 1.

Управляющие сигналы, поступающие С в устройство при пассивном уровне на выходе генератора 25 импульсов, объединены в шину Управление 2. Управляющие сигналы на мультиплексоры 10-14 снимаются с выходов тригге0

ров 39-4 и объединены в шину Ад рее. Признаком завершения процесса вычисления является нулевое состояние триггера 26. В связи с этим выходной сигнал, снимаемый с инверс- ного плеча этого триггера, используется в качестве сигнала Готов.

Первьш такт вычислений начинается при поступлении сигнала Пуск на вход устройства. По переднему фронту сигнала Пуск производится занесение аргументов X и Y во входные регистры 1 и 2 и счетчики 3 и 4. Кроме того, сигнал Пуск запускает блок 2 управления. В первом также произво- дится вычисление слагаемого (1-р )х (l-q)f.j. Сомножитель (1-р ) вычисляется при помощи умножителя-сумматора 19, сомножитель (l-q)f; / - при помощи умножителя 20, а полное произ ведение (1-р)(l-q)f - при помощи умножителя-сумматора 21.

Сомножитель (1 -р ) вычисляется следующим образом.

Буферный регистр 5 обнуляется. Мультиплексор 11 включается на вход А. В буферный регистр 7 заносится код р из входного регистра 1, тот же код заносится и в регистр 9 через мультиплексор 10, который включает- ся на вход А. Мультиплексор 12 включается на вход А. При этом умножитель-сумматор 19 формирует произведение р , а инверсия кода р поступает на группу сумматоров 16 по моду лю два, где к инверсии р прибавляется единица младшего разряду что обеспечивает формирование кода 1-р Этот код поступает на вход X умножителя-сумматора 21. Кроме того, ука- занный код запоминается в буферном регистре 8 по сигналу, входящему в шину Управление 2. Синхронизация в буферном регистре 8 динамическая, по положительному фронту синхросигт нала.

/

Сомножитель (l-q)f,j вычисляется следующим образом.

Значение (1-q) формируется путем прибавления к инверсии кода q единицы младшего разряда, что осуществляется при помощи группы сумматоров 15 по модулю два. Код 1-q подается на вход сомножителя X умножителя 20 через мультиплексор 13, который включается на вход А. Значение f j считывается из блока.18 памяти.

Адресом для блока памяти является конкатенация старших разрядов Х и Y, аргументов Х, Y, считываемых со счетчиков 3 и 4 и поступающих на адресный вход блока 18 памяти. Выход блока 18 памяти соединен с входом сомножителя Y умножителя 20.

Таким образом, с выхода матричного умножителя 20 считывается искомое произведение, которое поступает на вход сомножителя Y умножителя-сумматора 21. Полное произведение (1-р) (l-q)fjj- формируется на умножителе- сумматоре 21, на вход сомножителя X которого подается (1-р ), на вход сомножителя Y - (l-q)f-j , а на вход слагаемого К - О устройства с выхода регистра 9 результата, который обнуляется сигналом, входящим в шину Управление 1.

Полученный результат заносится в регистр 9 по сигналу, входящему в шину Управление 2. Синхронизация в регистре 9 динамическая, по положительному фронту.

Во втором такте вычисляется сумма (l-p(I-q)fi,i+ (l-p)qf,. . Слагаемое (1-р )(l-q)f;j поступает на вход слагаемого К умножителя-сумматора 21 с выхода регистра 9 результата. Сомножитель (1-р) сохраняется в буфер ном регистре 8 после первого такта. Для передачи его на вход X умножите- ля-сумматора 21 мультиплексор 14 переключается на вход В. Сомножитель qfjj, вычисляется умножителем 20. При этом значение q считьшается с входного регистра 2 и поступает на вход сомножителя X умножителя 20. Для этого мультиплексор 13 переключается на вход В. Значение , считьшается из блока 18 памяти, для чего адресное слово блока 18 памяти во втором такте меняется путем увеличения кода в счетчике 4 на единицу по сигналу, входящему в шину Управление 1. Полученньш во втором такте результат заносится в регистр 9 результата по сигналу, входящему в шину Управление 2. Кроме того, во втором такте по сигналу входящему в шину Управление 1, в буферный регистр 5 заносится код р, что необходимо для вычислений.в третьем такте. В третьем такте вычисляется сум- ма (1-p2)(l-q)f,j + (l-p )q f../

+ - )f;;+,,j Первых два слагаемых этой суммы поступают на вход

слагаемого К умножителя-сумматора 21 с выхода регистра 9 результата

Третье слагаемое формируется следующим образом.

Сомножитель р()/2 вычисляется умножителем-сумматором 19. Для этой дели код р в буферных регистрах 5 и 6, занесенный в лредшествующих тактах, по сигналуS входящему в шину Управление 1, сдвигается на один разряд в сторону младших разрядов-, В освобождающийся при сдвиге разряд заносится ноль через последователь- ньш вход L. В буферном регистре 7 сохраняется код р, занесенный в него в первом такте. Коды буферных регистров 5, 6 и 7 подаются на входы k, X, Y умножителя-сумматора 19. Мултиплексоры li и 12 при этом BKJro4emj на входы А, Искомое произведение через мультиплексор 14j переключаемьй на вход С, поступает па вход X умножителя-сумматора 21, кроме того по сигналу, входящему в шину Управление 2, оно заносится в- буферньш ре- :гистр 8, Сомножитель (l-q)f 1 ;вычис- ляется в умножителе 20. Код -q как ;и в первом такте поступает с группы сумматоров 15 по модулю два через мультиплексор ГЗ на вход сомножителя X умножителя 20. Мультиплексор 13 при этом включен на вход А. Ордината .- ; считьшается из блока 8- памяти

1 1 1 J,

путем увеличения кода в. счетчике 3 |на единицу и уменьшения кода в счетчике 4 на единицу по сигналамг входящим в шину Управление I. Полученный в третьем такте результат заносится в регистр результата 9 по сигналу, входящему в шину Управление 2

В четвертом такте производятся следующие действия.

Во-первых, к ранее полученной сумме прибавляется слагаемое L ,

а во-вторых, вычисляется значение, которое входит в пятое слагаемое интерполяционного выражения. Первая часть вычислений осуществляется следующим образом. Код р(р-М)/2 сохраняется в буферном регистре 8 после третьего такта вычислений и подается на вход X умножителя-сумматора 2 через мультиплексор 14, включаемый на вход В. Код ранее полученной суммы поступает на вход К умножителя- сумматора 21 с выхода регистра 9 ре

зультата,Сомножитель gf,j + , вычисляется умнбжителем 20, для чего значение q подается через мультиплексор 13 на вход сомножителя X матричного умножителя 20, Коммутатор-для этого пе- реключается на вход В. Ордината f,i+- считьшается из блока 18 памяти. Адрес блока 18 памяти формируется в четвертом такте следующим образом.

Код в счетчике 3 не изменяется, а код в счетчике 4 увеличивается на единицу по сигналу, входящему в инну Управление 1,

Результат, полученный в умножителе-сумматоре 21, записывается в регистр 9 результата по сигналу, входящему в шину Управление 2. Причем динамическая синхронизация в регистре 9 результата предохраняет полученный в матричном умножителе 21 код от искажений, обусловленных действием других сигналов, входящих в шину Управление 2,

Формирование кода р-1 производится следующим образом. На вход слагаемого К умножителя-сумматора 19 подается код -1 через мультиплексор 11, для чего он переключается на вход В, а на вход сомножителя J умножителясумматора 19 подается код 1 через мультиплексор 12, который переключается на вход Во На вход сомножителя X умножителя-сумматора 19 подается код р, записанный в буферном регистре 7. Таким образом, на выходе умножителя-сумматора 19 формируется ис- комьш код р-1. Этот код через мультиплексор 10, которьш переключается на вход В, записывается в буферный регистр 6 по сигналу, входящему в шину Управление 2. Кроме того, по сигналам, входящим в щину Управление 2, сдвигается код в буферном регистре 7 и уменьшается на единицу код в счет- чике 3, что необходимо для вычисчений в пятом такте.

В пятом такте к ранее полученной сумме прибавляется слагаемое

EiE-1 (i-q)f.,j. Сомножитель р(р-1)/

/2 формируется умножителем-сумматором 19, Для этой цели код р-1, записанный в буферном регистре 6, пода- ется через мувгньтиплексор 12, который переключается на вход Ар на вход сомножителя Y умножителя-сумматора 19, на вход сомножителя X которого поступает код р/25 записанный в буферном регистре 7. Вуферньй регистр 5 обнуляется по сигналу, входящему в шину Управление 1, и на вход слагаемого К умножителя-сумматора 19 поступает О устройства через мультиплексор 11, которьй переключается на вход А. Результат через мульти- |Плексор 14, который переключается |На вход С, поступает на вход сомножи теля X умножителя-сумматора 21. Кро- Ю зультата по сигналу, входящему в пшме того, сомножитель р(р-1)/2 записывается в буферньш регистр 8 по си1- налу, входящему в шину Управление 2. На вход слагаемого К умножителя-сумматора 21 поступает с регистра 9 результата ранее полученная сумма, а на вход сомножителя Y - сомножитель (l-q). Этот сомножитель формируется умножителем 20. На вход сомножителя X умножителя 20 поступает через мультиплексор 13, включенньй на вход А, значение 1-q, формируемое группой сумматоров 15 по модулю два, а на вход сомножителя Y - ордината из блока 18 памяти. Адрес орди- наты f.,j вычисляется путем вычитания единиц из кодов счетчиков 3 и. 4 по сигналам, входящим в шину Управление 1. Отметим, что во втором полупериоде четвертого такта было так- же осуществлено вычитание единицы из кода счетчика 3. Эти действия обеспечивают переход от ординаты f: . -.t , использовавшейся в четвертом

ну Управление 2. Результат шестого такта является искомым результатом вычисления функции двух переменных. Он поступает на выход устройства в целой и сопровождается признаком Готов , вырабатываемым в блоке 22.

20

25

1-1,J

r+i,J-H такте, к ординате i

мой в пятом такте. Результат такта записывается в регистр

используе- 35 пятого 9 резульФормула изобретения

Устройство для вычисления функций, содержащее два реверсивных счетчика, блок памяти значений функции, два входных регистра, два мультиплексора, два преобразователя прямого кода в дополнительньй, три буферных регистра и регистр результата, первьй умножитель-сумматор и блок синхронизации, информационные входы первого и второго реверсивных счетчиков являются входами старших разрядов первого и второго аргументов устройства соответственно, информационные входы первого и второго входных регистров являются входами младших разрядов первого и второго аргументов устройства соответственно, выходы первого и второго реверсивных счетчиков подключены к первому и второму адресным входам блока памяти значений функции, выход первого мультиплексора подключен к входу первого сомножителя умножителя-сумматора, выход которого подключен к информационному входу регистра результата, выход которого . является выходом результата устройства и соединен с входом слагаемого умножителя сумматора, первьй информаци- ньй вход первого мультиплексора подключен к выходу первого буферного регистра, с первого по одиннадцатьй выходы блока синхронизации подключены к первому и второму управляющим входам первого мультиплексора, к управляющему входу второго мультиплексора, к входам синхронизации регистра результата, первого, второго и третьего буферных регистров и к входу сброса регистра результата, к входам задания режима суммирования пертата по сигналу, равленйе 2.

входящему в шину

В шестом такте к ранее полученной сумме прибавляется слагаемое

Е-2-2. qf; . Кор, сомножителя

р(р-1)/2 сохраняется в буферном ре- гистре 8 после пятого такта и подается на вход сомножителя X умножителя- сумматора 21 через мультиплексор 14, который переключается на вход В. На вход слагаемого К умножителя-сумма- тора 21 поступает ранее .полученная сумма с выхода регистра 9 результата Сомножитель qf,.|,j4.,Формируется умножителем 20 и поступает на вход сомножителя Y умножителя-сумматора 21, в котором и формируется искомьй результат. Сомножитель q поступает на вход сомножителя X умножителя 20 с прямого выхода входного регистра 2 через

мультиплексор 13, которьй переключается на вход В, а ордината ;,|Счи- тывается из блока 18 памяти и поступает на вход Y умножителя 20. Для формирования адреса искомой ординаты код в счетчике 4 увеличивается на единицу по сигналу, входящему в шину Управление 1. Результат шестого такта записывается в регистр 9 ре

ну Управление 2. Результат шестого такта является искомым результатом вычисления функции двух переменных. Он поступает на выход устройства в целой и сопровождается признаком Готов , вырабатываемым в блоке 22.

.

20

25

35 40

.

Формула изобретения

Устройство для вычисления функций, содержащее два реверсивных счетчика, блок памяти значений функции, два входных регистра, два мультиплексора, два преобразователя прямого кода в дополнительньй, три буферных регистра и регистр результата, первьй умножитель-сумматор и блок синхронизации, информационные входы первого и второго реверсивных счетчиков являются входами старших разрядов первого и второго аргументов устройства соответственно, информационные входы первого и второго входных регистров являются входами младших разрядов первого и второго аргументов устройства соответственно, выходы первого и второго реверсивных счетчиков подключены к первому и второму адресным входам блока памяти значений функции, выход первого мультиплексора подключен к входу первого сомножителя умножителя-сумматора, выход которого подключен к информационному входу регистра результата, выход которого . является выходом результата устройства и соединен с входом слагаемого умножителя сумматора, первьй информаци- ньй вход первого мультиплексора подключен к выходу первого буферного регистра, с первого по одиннадцатьй выходы блока синхронизации подключены к первому и второму управляющим входам первого мультиплексора, к управляющему входу второго мультиплексора, к входам синхронизации регистра результата, первого, второго и третьего буферных регистров и к входу сброса регистра результата, к входам задания режима суммирования пер912

вого и второго реверсивных счетчиков и к входу задания режима вычитания второго реверсивного счетчика, входы синхронизации первого и второго входных регистров и первого и второго ре- версивных счетчиков объединены, о т- личающее ся тем, что, с целью повьшения точности интерполяции функций за счет увеличения количества используемых узловых точек, в не- го введены четвертьм буферный регистр, второй умножитель-сумматор, умножитель и с третьего по пятьш мультиплексоры, выход первого входного регистра подключен к информаци- окным входам второго и четвертого буферных регистров и к первому информационному входу второго мультиплексора, выход которого подключен к информационному входу третьего буфер- кого регистра, выход которого подключен к первому информационному входу четвертого мультиплексора, второй информационный вход и выход которого подключены к входу первой константы устройства и к входу первого сомножителя второго, умножителя-сумматора соответственно, выход которого подключен к вторым информационным входа |первого и второго мультиплексоров и (Через второй прео бразова рель прямого кода в дополнительный к третьему ин- формационному входу первого мультиплексора, выход которого подключен к информационному входу первого бу- ферного регистра, выход второго буферного регистра подключен к первому информационному входу третьего мультиплексора, второй информационный вход и выход которого соединены с входом второй константы устройства и входом слагаемого второго умножителя сумматора соответственно, вход второго сомножителя которого соединен с выходом четвертого буферного регист-

1

10

ра, выход второго входного регистра соединен с первым информационным входом пятого мультиплексора и через первый преобразователь прямого кода в дополнительный с вторым информационным входом пятого мультиплексора выход которого подключен к входу первого сомножителя умножителя, вход второго сомножителя которого и выход соединены с выходом блока памяти значений функции и с входом второго сомножителя первого умножителя-сумматора соответственно, вход пус:ка блока синхронизации является входом пуска устройства и соединен с входом синхронизации первого входного регистра, первьй выход блока синхронизации подключен к управляющему входу пятого мультиплексора, третий выход блока синхронизации подключен к управляющим входам третьего и четвертого мультиплексоров, восьмой выход блока синхронизации подключен к входу синхронизации четвертого буферного регистра, девятьш выход блока синхронизации подключен к входам разрешения записи информации второго и третьего буферных регистров, с двенадцатого по четырнадцатьш выходы блока синхронизации подключены к входу разрешения записи информации четвертого буферного регистра,, к входу сброса второго буферного регистра и к входу задания режима вычитания первого реверсивного счетчика, причем с второго по четвертьм буферные регистры выполнены в виде регистров сдвига, последовательные информационные входы которых соединены с входом логического нуля устройства , вход сброса и пятнадцатый вы-- ход блока синхрО1 изации являются входом сброса и вы - ходом признака окончания вы - числений устройства.

iy/fflffS/tef/t/e 7

//7/5CfS/ e/fije 2 /Ъ/noS

W

I2I Ш (4)

М- 12L

(81

(9)

ffo

(Ш

ja

(Ш

Фа г. 5

71 ГП m ГП m m

6B 67

68 69 70

7/ 7Z 7J

S3

66

S

i

If

60

S9

W

6f

65

/-

33

7/

/J

7ff

ynpaS/ie/ ue f

y/7flaS e//c/e 2

dpec

HI

n m m m m m

63 Btf 65

m m

ТП ГТ1 rn rn ГТ1 m m

62.

фиг. 8

Составитель АО Ушаков Редактор М. Дыльш Техред М.Ходайич

Заказ 7052/43 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

тго делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие,г.Ужгород, ул. Проектная, 4

97.7

КорректорМ. Максимишинец

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Устройство для вычисления функций в модулярной системе счисления | 1985 |

|

SU1322268A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Устройство для вычисления функций | 1986 |

|

SU1388848A1 |

| Устройство для вычисления координат | 1989 |

|

SU1635178A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| ГЕНЕРАТОР СЛУЧАЙНОГО ПРОЦЕССА | 1991 |

|

RU2050585C1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

Изобретение относится к вычислительной технике и предназначено для использования в микропроцессорных системах. В устройстве вьшолняется вычисление функции двух переменных путем реализации алгоритма интерполяции по ше сти узловым точкам аппаратными средствами с совмещением во времени отдельных вычислительных операций, что позволяет повысить точность вычислений. Вычисление функции Z проводится по формуле Z f(x,+ ph,y. + як) (1-р)

| Интерполятор поверхности | 1980 |

|

SU942040A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1985-03-18—Подача