Изобретение относится к импульсной технике и предназначено для контроля работоспособности элементов автоматики и телемеханики.

Целью изобретения является расширение области применения за счет обеспечения контроля работы реверсивного счетчика при сложении и вычитании входной последовательности импульсов.

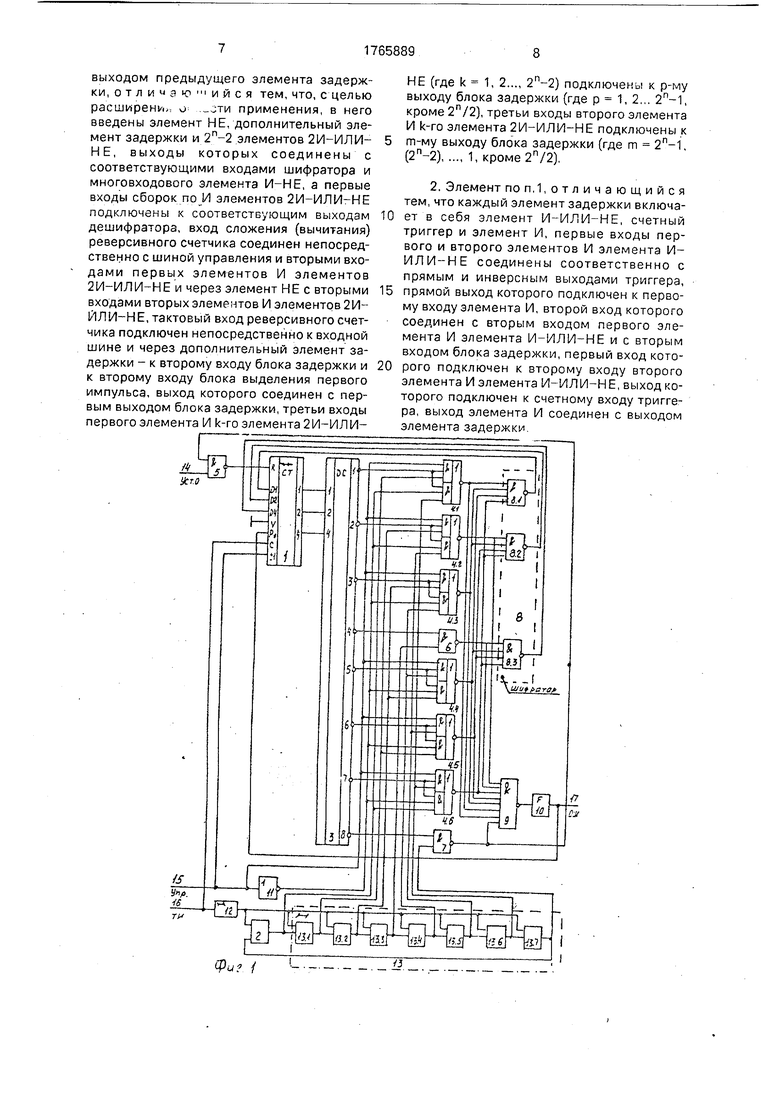

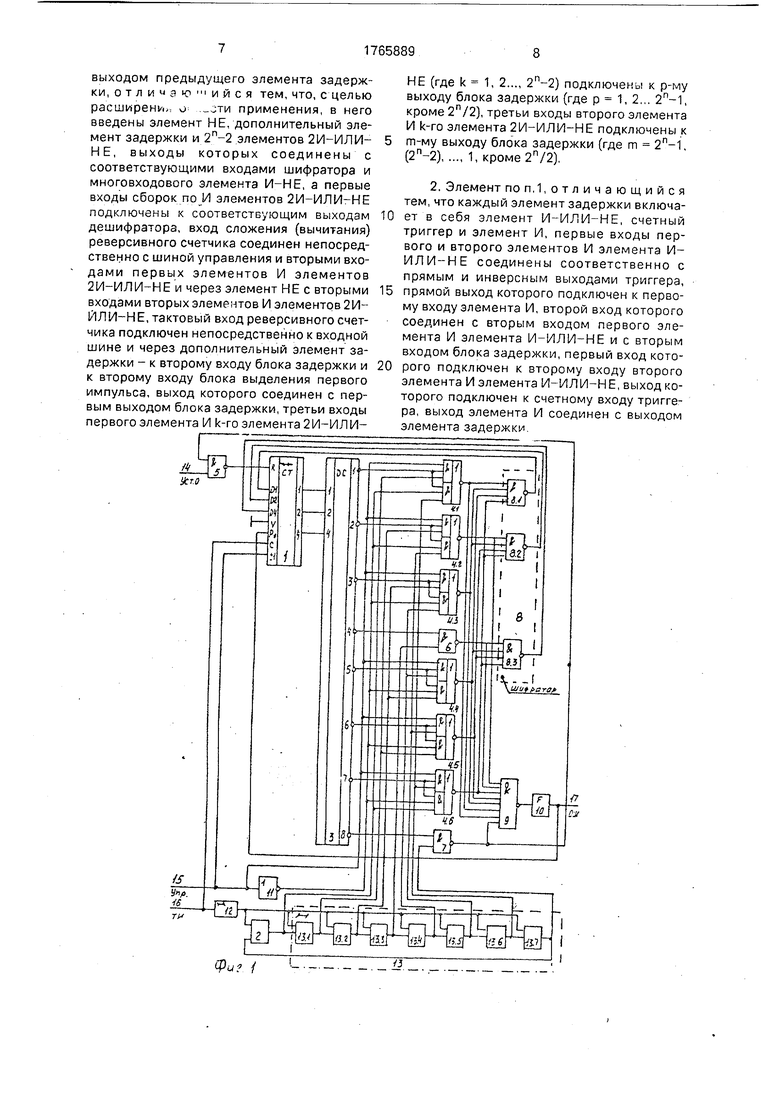

В качестве примера на фиг.1 приведена структурная электрическая схема трехразрядного реверсивного счетного элемента с контролем; а диаграммы - на фиг.2.

Счетный элемент с контролем содержит реверсивный счетчик 1, блок 2 выделения первого импульса, дешифратор 3, элементы 2И-ИЛИ-НЕ 4.1,.4.6, элементы И-НЕ 5...7, шифратор 8, состоящий из элементов И-НЕ 8.1...8.3, многовходовый элемент И- НЕ 9, формирователь импульсов 10, элемент НЕ 11, элемент задержки 12, блок задержки 13, состоящий из элементов задержки 13.1...13.7, шину 14 установки (Уст.0), входную шину 15 управления,

входную шину 16 (ТИ), выходную шину 17 контроля (ОШ).

Информационные входы счетчика 1 соединены с соответствующими выходами шифратора 8. Входы дешифратора 3 соединены с выходами счетчика 1. Первые входы элементов И-НЕ 6, 7 подключены соответ2П

ственно к выходам -го и 2п-го дешифратора 3, выход первого элемента И-НЕ 6 соединен с соответствующим входом шифратора 8 и многовходового элемента И-НЕ 9. Выход элемента И-НЕ 9 через формирователь 10 соединен с выходной шиной 17 контроля и с входом управления загрузкой счетчика 1, вход установки в ноль которого подключен к выходу третьего элемента И- НЕ 5. Первый вход элемента И-НЕ 5 соединен с шиной установки 14, а второй вход - с соответствующим входом многовходового элемента И-НЕ 9 и выходом второго элемента И-НЕ 7. Первый вход элемента И-НЕ 7 подключен к последнему выходу дешифратора 3. Вторые входы элементов И-НЕ 6, 7

VJ ON СЛ 00 00 О

2n соединены соответственно с -м и 2п-м

выходами блока задержки 13. Первый вход блока задержки 13 подключен к выходу блока 2 выделения первого импульса, соеди- ненного первым входом с (2п-1) выходом блока задержки. Выходы элементов 2И- ИЛИ-НЕ 4.1...4,6 соединены с соответствующими входами шифратора 8 и многовходового элемента И-НЕ.

Первые входы сборки по И элементов 2И-ИЛИ-НЕ 4.1..,4.6 подключены к соответствующим выходам дешифратора 3. Вход сложения (вычитания) реверсивного счетчика 1 соединен с входной шиной уп- равления 15 и вторыми входами первых элементов И элементов 2И-ИЛИ-НЕ 4.1...4.6 и через элемент НЕ 11 - с вторыми входами вторых элементов И элементов 2И-ИЛИ- НЕ 4.1.„4.6. Тактовый вход счетчика 1 под- ключей к входной шине 16 и через элемент задержки 12 ко второму входу блока 2 выделения первого импульса и второму входу блока задержки, третий вход первого элемента И К-го элемента 2И-ИЛИ-НЕ 4.6, где К 1,2.„(2п-2) соединен ср-м выходом блока задержки 13 (где р 1,2...(2п-2), а третий вход второго элемента И К-го элемента 2И-ИЛИ-НЕ 4.6 соединен с m-м выходом блока задержки 13 (где т (2п-1), (2п-2)...,

2П 1, кроме -«-).

Блок 2 выделения первого импульса содержит, например, триггер и элемент И, первый и второй входы которого соединены соответственно с сигнальным входом блока 2 и с выходом триггера, входы установки в ноль и в единицу которого соединены соответственно с выходом элемента И и с вхо- дом установки блока 2, выход которого соединен с выходом элемента И.

Блок задержки 13 содержит, например, последовательно соединенные элементы 13.1...13.7 задержки, выходы которых явля- ются выходами блока задержки, вторые входы элементов задержки подключены ко второму входу блока задержки, а каждый из элементов 13.1...13.7 задержки содержит элемент И-ИЛИ-НЕ, счетный триггер и элемент И. Первые входы элементов И элемента И-ИЛИ-НЕ соединены соответственно с прямым и инверсным выходами триггера, прямой выход которого, кроме того,подключен к первому входу элемента И, второй вход которого соединен с вторым входом первого элемента И элемента И-ИЛИ-НЕ и со вторым входом блока задержки. Первый вход блока задержки сое- динен со вторым входом второго элемента

И элемента И-ИЛИ-НЕ, выход которого подключен к счетному входу триггера.

Время задержки элемента 12 должно удовлетворять условию 0,5ТТИ t Тти, где Тти - период следования тактовых импульсов.

В случае использования в качестве источника 1 двоичного реверсивного счетчика дешифратор 3 представляет собой дешифратор двоичного кода в позиционный, а шифратором является шифратор позиционного кода в двоичный. Шифратор стандартный и может быть реализован, например, на элементах И-НЕ 8,1...8.3.

Формирователь импульсов 10 формирует отрицательный импульс, длительность которого т 2tcp.iT, где tcp.rr - время срабатывания триггера счетчика 1.

Устройство работает следующим образом.

В исходном состоянии по отрицательному импульсу на шине 14 (Уст.О) счетчик 1 устанавливается в нулевое состояние, на выходах дешифратора 3 и формирователя импульсов 10 положительные потенциалы, блок 2 выделения первого импульса открыт, на его выходе отрицательный потенциал. На выходах элементов 2И-ИЛИ-НЕ 4.1...4.6 и элементов И-НЕ 6, 7 положительные потенциалы за счет присутствия на выходах блока задержки 13 отрицательных потенциалов (фиг.2).

Пусть счетчик работает на сложение.

Первый импульс входной последовательности с шины 16 (ТИ) поступает на счетный вход счетчика 1, а также через элемент задержки 12 на вход блока задержки 13 и блок 2 выделения первого импульса, Через время, равное времени задержки элемента задержки 12, на выходе блока 2 появляется положительный импульс, который поступает на третий вход первого элемента И элемента 2И-ИЛИ-НЕ 4.1, Блок 2 запирается и последующие импульсы с входной шины 16 не проходят на вход блока задержки. На втором входе первого элемента И элемента 2И-ИЛИ-НЕ4.1 положительный потенциал шины управления 15.

По заднему фронту первого импульса входной последовательности на шине 16 на первом выходе, соответствующем коду числа один, дешифратора 3 появляется отрицательный импульс, который поступает на первый вход первого элемента И элемента 2И-ИЛИ-НЕ4.1 (фиг.2).

Если счетчик 1 исправен, то положительный импульс с выхода блока 2 поступает на третий вход первого элемента И элемента 2И-ИЛИ-НЕ 4.1 в то время, когда на первом входе первого элемента И элемента 2И-ИЛИ-НЕ 4.1 присутствует отрицательный имп,льс с первого выхода дешифратора 3, на выходе элемента 2И-ИЛИ-НЕ 4.1 сохраняется положительный потенциал. На выходе формирователя 10 импульсов сохраняется положительный потенциал, соответствующий отсутствию ошибки в счетчике 1 (фиг.2).

В результате сбоя или отказа в счетчике 1 импульс с одного из выходов блока задер- жки 13 не совпадает с импульсом с соответствующего одного из выходов дешифратора 3.

Возможно рассмотреть два случая.

Первый, когда импульс на выходе (на- пример, соответствующий числу два - фиг.2) дешифратора 3 отсутствует, т.е. на первом входе первого элемента И элемента 2И-ИЛИ-НЕ 4.2 присутствует положительный потенциал, в этом случае импульс с выхода элемента 13.1 задержки блока задержки 13 открывает первый элемент И элемента 2И-ИЛИ-НЕ 4.2 и на его выходе появляется отрицательный импульс, который через элемент И-НЕ 9 поступает на вход формирователя 10 импульсов, на выходе которого формируется отрицательный импульс, длительность которого равна т (фиг.2), свидетельствующий об ошибке.

Импульс с выхода элемента 2И-ИЛИ- НЕ 4.2 поступает на соответствующий вход шифратора 8, генерирующего на своих выходах код числа два. Одновременно отрицательного импульс с выхода формирователя 10 импульсов поступает на выход- ную шину 17, сигнализируя об ошибке, и на вход управления загрузкой счетчика 1. По заднему фронту импульса формирователя 10 импульсов в счетчик 1 вносится код числа два, соответствующий выходному импуль- су дешифратора 3, состояние счетчика 1 исправляется и его работа продолжается (фиг.2).

Во втором случае, когда импульс на выходе (например, соответствующий числу пять - фиг.2), счетчик 1 работает на вычитание, отсутствует, а импульс на выходе че- тыре дешифратора 3 повторяет (во времени) импульс на выходе, соответствующем числу пять, т.е. в этом случае импульс с выхода элемента 13.2 задержки блока задержки 13 открывает второй элемент И элемента 2И-ИЛИ-НЕ 4.4 в то время, когда на его первом и втором входах присутствуют положительные потенциалы (фиг.2), На вы- ходе элемента 2И-ИЛИ-НЕ 4.4 формируется отрицательный импульс, который аналогично описанному выше формирует сигнал ошибки и формирует на выходе шифратора 8 код, который записывается в счетчик 1. Счетный элемент исправляется и его работа продолжается.

В обоих случаях импульс с выхода формирователя 10 поступает на вход управления загрузкой счетчика 1 и вносит в него числовой код, соответствующий числу входных импульсов, при этом счетчик 1 продолжает счет импульсов (на сложение или на вычитание), цикл работы продолжается, т.е. при случайном сбое или отказе сигнал ошибки представляет собой одиночный отрицательный импульс, длительность которого равна длительности импульса на выходе формирователя 10.

Конструктивные особенности предлагаемого технического решения позволяют расширить область применения за счет обеспечения контроля работы реверсивного счетчика 1 как на сложение, так и на вычитание, после каждого импульса входной последовательности, а также коррекции содержимого счетчика при обнаружении сбоя.

Формула изобретения 1. Счетный элементе контролем, содержащий n-разрядный реверсивный счетчик, информационные входы которого соединены с соответствующими выходами шифра- тора, блок задержки, блок выделения первого импульса, дешифратор, входы которого соединены с выходами счетчика, первый, второй, третий элементы И-НЕ, первые входы первого и второго из которых соединены соответственно с 2п/2 и 2П выходами дешифратора, выход первого элемента И-НЕ соединен с соответствующим входом шифратора и многовходового элемента И-НЕ, выход которого через формирователь импульсов соединен с выходной шиной контроля и входом управления загрузкой счетчика, вход установки в О которого соединен с выходом третьего элемента И-НЕ, первый вход которого подключен к шине установки, второй вход - к соответствующему входу многовходового элемента И-НЕ и выходу второго элемента И-НЕ, второй вход которого соединен с 2П выходом блока задержки, 2п/2 выход которого подключен к второму входу первого элемента И-НЕ, блок задержки включает п-1 элемент задержки, вход первого из которых соединен с первым входом блока задержки и с выходом блока выделения первого импульса, первый вход которого соединен с 2П выходом блока задержки, который подключен к выходу последнего элемента задержки, вход второго и каждого последующего элемента задержки соединен с одним из выходов блока задержки и

выходом предыдущего элемента задержки, отличаю ийся тем, что, с целью расширена/ vi ти применения, в него введены элемент НЕ, дополнительный элемент задержки и 2п-2 элементов 2И-ИЛИ- НЕ, выходы которых соединены с соответствующими входами шифратора и многовходового элемента И-НЕ, а первые входы сборок noj/1 элементов 2И-ИЛИ-НЕ подключены к соответствующим выходам дешифратора, вход сложения (вычитания) реверсивного счетчика соединен непосредственно с шиной управления и вторыми входами первых элементов 1/1 элементов 2И-ИЛИ-НЕ и через элемент НЕ с вторыми входами вторых элементов И элементов 2И- ЙЛИ-НЕ, тактовый вход реверсивного счетчика подключен непосредственно к входной шине и через дополнительный элемент задержки - к второму входу блока задержки и к второму входу блока выделения первого импульса, выход которого соединен с первым выходом блока задержки, третьи входы первого элемента И k-ro элемента 2И-ИЛИНЕ (где k 1, 2..., 2п-2) подключено к р-му выходу блока задержки (где р 1, 2.,. 2п-1, кроме 2п/2), третьи входы второго элемента И k-ro элемента 2И-ИЛИ-НЕ подключены к m-му выходу блока задержки (где т 2п-1, (2п-2) 1, кроме 2п/2),

2, Элемент по п. 1, отличающийся тем, что каждый элемент задержки включает в себя элемент И-ИЛИ-НЕ, счетный триггер и элемент И, первые входы первого и второго элементов И элемента И- ИЛИ-НЕ соединены соответственно с прямым и инверсным выходами триггера,

прямой выход которого подключен к первому входу элемента И, второй вход которого соединен с вторым входом первого элемента И элемента И-ИЛИ-НЕ и с вторым входом блока задержки, первый вход которого подключен к второму входу второго элемента И элемента И-ИЛИ-НЕ, выход которого подключен к счетному входу триггера, выход элемента И соединен с выходом элемента задержки

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетный элемент с контролем | 1986 |

|

SU1370779A1 |

| Устройство ранжирования экстремальных значений | 1985 |

|

SU1291960A1 |

| Цифровой измеритель интервалов между серединами импульсов произвольной длительности | 1980 |

|

SU918931A1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Устройство для измерения коэффициента прямоугольности амплитудно-частотной характеристики радиоприемников | 1990 |

|

SU1755383A1 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1370643A2 |

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| Генератор случайного потока импульсов | 1982 |

|

SU1095366A1 |

| Устройство для контроля периода импульсной последовательности | 1988 |

|

SU1511855A1 |

| Способ регулирования частоты вращения трехфазного асинхронного электродвигателя | 1985 |

|

SU1376209A1 |

Использование: изобретение относится к импульсной технике и предназначено для контроля работоспособности элементов автоматики и телемеханики. Сущность изобретения: счетный элемент с контролем содержит n-разрядный реверсивный счетчик, блок выделения первого импульса, дешифратор, (2п-2) элемента 2И-ИЛИ-НЕ, три элемента И-Hfc, шифратор, многовходо- вый элемент И-НЕ, формирователь, элемент НЕ, дополнительный элемент задержки, блок задержки. 1 з.п. ф-лы, 2 ил.

Ф /

15 -

с/ось: с.we

L JT-JL П. JH -TL.-TL. Л.

---

..«..

, Л .JT..TbJH, Л- Л-Л -- Л

JT.

JT

,,„п„.

и

.. Ј

L .

ЛТ, jn,TT

JT

.„л

| Счетный элемент с контролем | 1983 |

|

SU1129740A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Счетный элемент с контролем | 1986 |

|

SU1370779A1 |

Авторы

Даты

1992-09-30—Публикация

1990-08-08—Подача