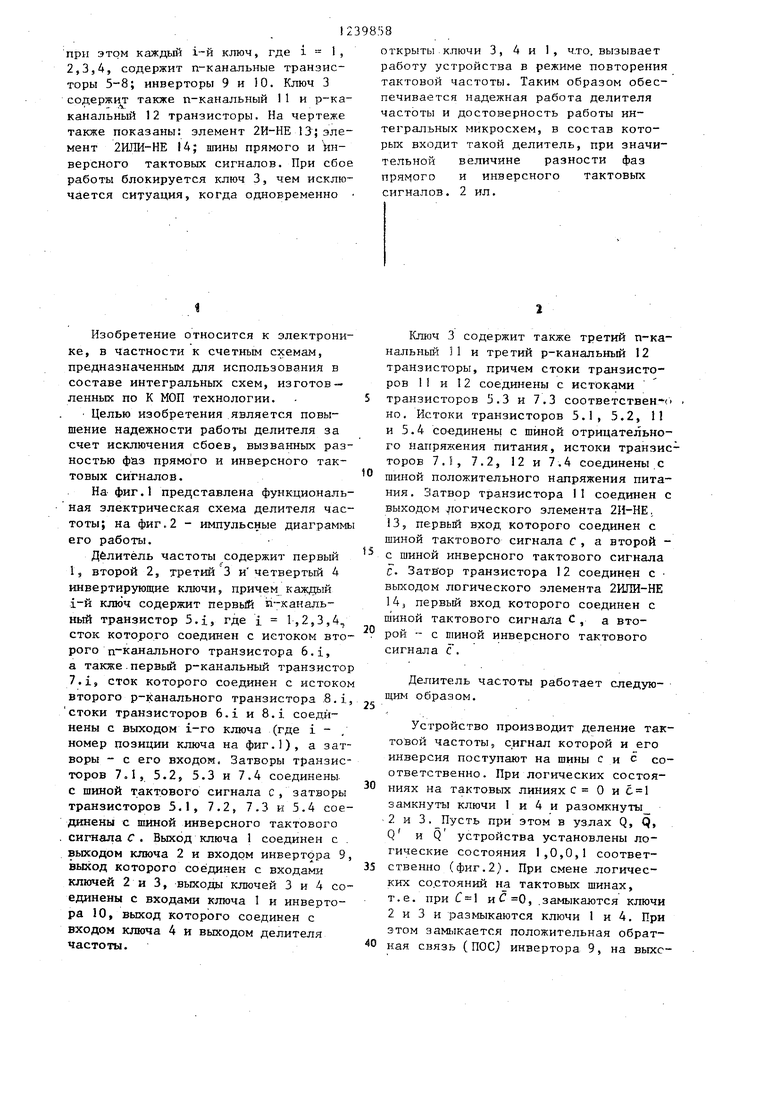

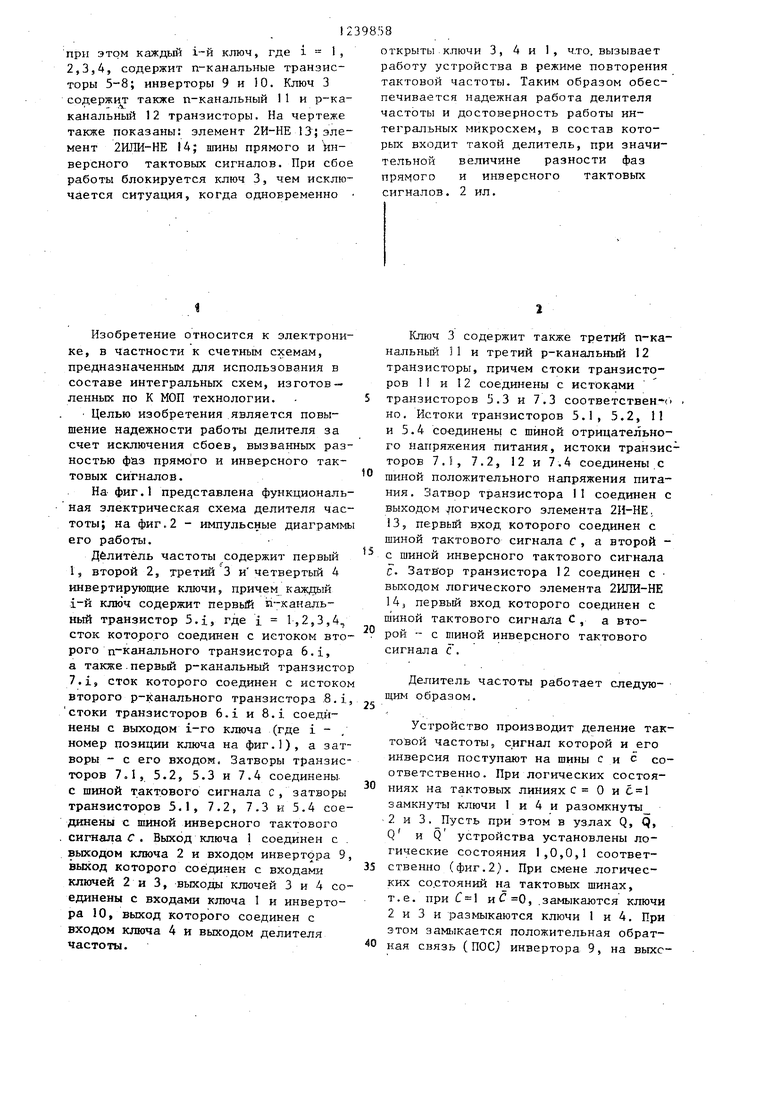

при этом каждый i-й ключ, где i - 1, 2,3,4, содержит п-канальные транзисторы 5-8; инверторы 9 и 10. Ключ 3 содержит также п-канальный 1 и р-ка- канальный 12 транзисторы. На чертеже также показаны: элемент 2И-НЕ 13; элемент 2ИЛИ-НЕ 14; нганы прямого и инверсного тактовых сигналов. При сбое работы блокируется ключ 3, чем исключается ситуация, когда одновременно

Изобретение относится к электроние, в частности к счетным схемам, редназначенным для использования в оставе интегральных схем, изготовенных по К МОП технологии.

Целью изобретения является повыение надежности работы делителя за счет исключения сбоев, вызванных разностью фаз прямого и инверсного тактовых сигналов.

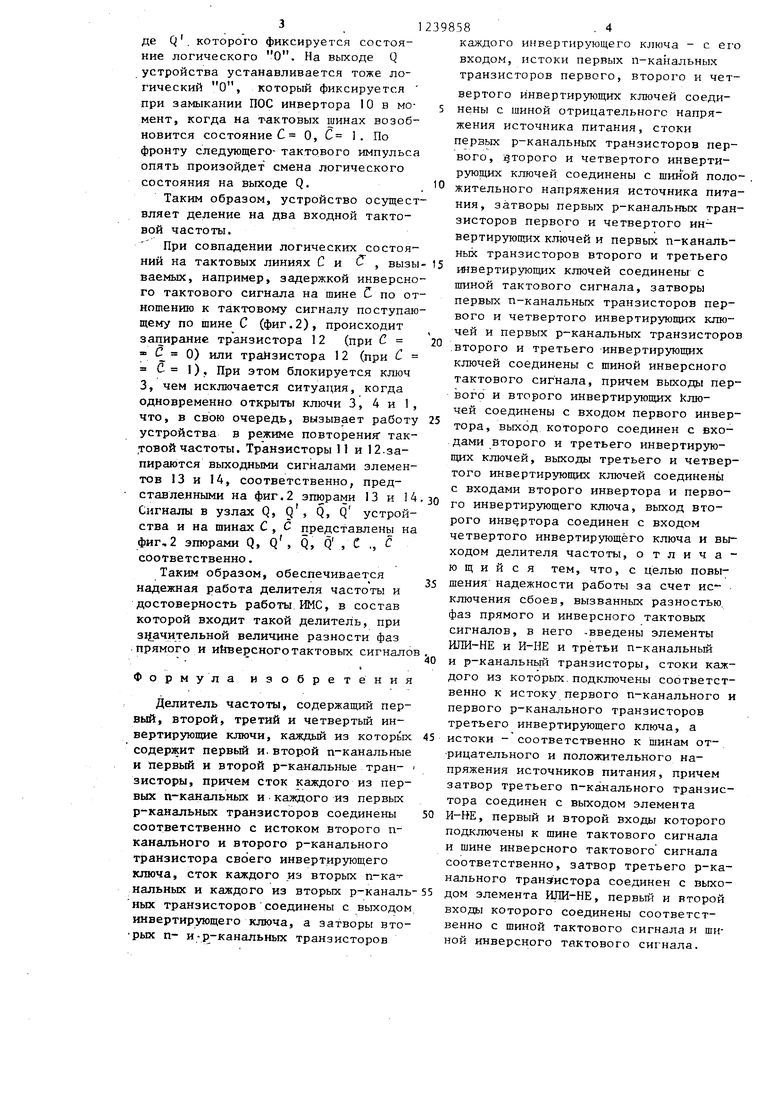

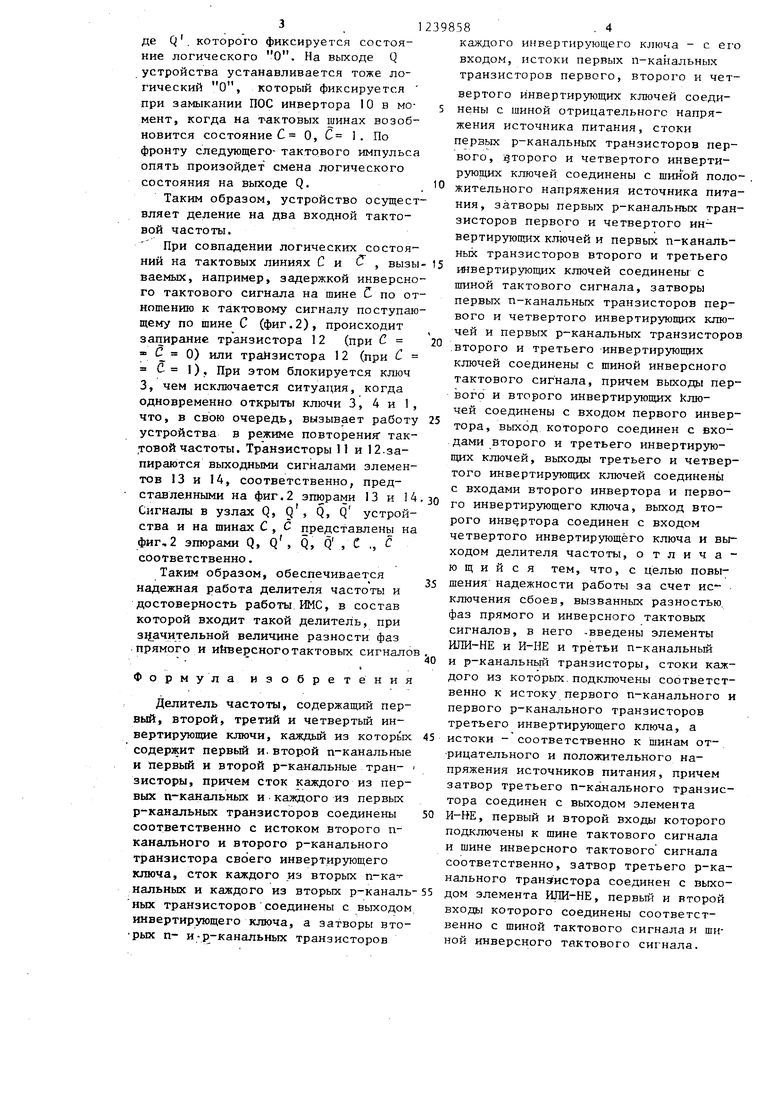

На фиг.1 представлена функциональная электрическая схема делителя частоты; на фиг.2 - импульсные диаграммы его работы.

Делитель частоты содержит первый 1, второй 2, третий 3 и четвертый 4 инвертирующие ключи, причем каждый i-й ключ содержит первьй п-канальный транзистор 5.1, где i 1,2,3,4, сток которого соединен с истоком второго п-канального транзистора 6.i, а также.первый р-канальный транзистор 7.1, сток которого соединен с истоком второго р-канального транзистора .8.1,

стоки транзисторов 6.1 и 8.1 соединены с выходом 1-го ключа (где 1 - , номер позиции ключа на фиг.1), а затворы с его входом. Затворы транзисторов 7.1, 5.2s 5.3 и 7.4 соединены с шиной тактового сигнала с, затворы транзисторов 5.1, 7.2, 7.3 и 5.4 соединены с шиной инверсного тактового

сигаала с , Выход ключа 1 соединен с . выходом ключа 2 и входом инвертора 9, 1аыход которого соединен с входами ключей 2 и 3, выходы ключей 3 и 4 соединены с входами ключа 1 и инвертора 10, выход которого соединен с входом ключа 4 и выходом делителя частоты.

открыты ключи 3, 4 и 1, ч.то. вызывает работу устройства в режиме повторения тактовой частоты. Таким образом обеспечивается надежная работа делителя частоты и достоверность работы интегральных микросхем, в состав которых входит такой делитель, при значительной величине разности фаз прямого и инверсного тактовых сигналов. 2 ил.

Ключ 3 содержит также третий п-канальный 31 и третий р-канальный 12 транзисторы, причем стоки транзисторов 11 и 12 соединены с истоками

транзисторов 5.3 и 7.3 соответствен- но. Истоки транзисторов 5.1, 5.2, 11 и 5.4 соединены с шиной отрицательного Напряжения питания, истоки транзисторов 7.1, 7.2, 12 и 7.4 соединены.с шиной положительного Напряжения питания. Затвор транзистора II соединен с выходом логического элемента 2Н-НЕ. 3, первый вход которого соединен с шиной тактового сигнала С , а второй с шиной инверсного тактового сигнала с. Затв ор транзистора 12 соединен с выходом логического элемента 2И1Ш-НЕ 14з первый вход которого соединен с шиной тактового сигнала С, а второй с шиной инверсного тактового сигнала с .

25

Делитель частоты работает следующим образом.

Устройство производит деление тактовой частоты, сигнал которой и его инверсия поступают на шины с и с соответственно. При логических состоя- ниях на тактовых линиях с О и с 1 замкнуты ключи I и 4 и разомкнуты 2 и 3.Пусть при этом в узлах Q, Q, . Q Ир устройства установлены логические состояния 1,0,0,1 соответ- ственно (фиг.2). При смене логических со.стояний на тактовых шинах, т.е. при С , .замыкалотся ключи 2 и 3 и размыкаются ключи 1 и 4. При этом зам1.1кается положительная обратная связь (nOCj инвертора 9, на выхсде Q . которого фиксируется состояние логического О. На выходе Q устройства устанавливается тоже логический О, который фиксируется при замыкании ПОС инвертора 10 в мо- мент, когда на тактовых шинах возобновится состояние С О, С 1. По фронту следующего- тактового импульса опять произойдет смена логического состояния на выходе Q.,

Таким образом, устройство осуществляет деление на два входной тактовой частоты.

При совпадении логических состоя - ний на тактовых линиях С и , вызы ваемых, например, задержкой инверсного тактового сигнала на шине С по отношению к тактовому сигналу поступающему по шине С (фиг,2), происходит за11ирание транзистора 12 (при С - С 0) или транзистора 12 (при С, - С 1), При этом блокируется ключ 3, чем исключается ситуация, когда одновременно открыты ключи 3, 4 и 1, что, в свою очередь, вызывает работу устройства в режиме повторения так- ,товой частоты. Транзисторы 11 и 12.запираются выходными сигналами элементов 13 и 14, соответственно, представленными на фиг.2 эпюрами 13 и 4 Сигналы в узлах Q Q , Q, Q устройства и на шинах С, С представлены на фиг,2 эпюрами Q, Q , Q, Q , С ,, С соответственно.

Таким образом, обеспечивается надежная работа делителя частоты и достоверность работы ИМС, в состав которой входит такой делитель, при з1- ачительной величине разности фаз прямого и ийверсноготактовых сигналов

Формула изобретения

Делитель частоты, содержащий первый, второй, третий и четвертый инвертирующие ключи, каждый из которьк содержит первый и.второй п-канальные и первый и второй р-канальные тран- зисторы, причем сток каждого из первых п-канальных и каждого из первых р-канальных транзисторов соединены соответственно с истоком второго п- канального и второго р-канального транзистора своего инвертирующего ключа, сток каждого из вторых п-ка- нальных и каждого из вторых р-каиаль ных транзисторов соединены с выходом инвертирующего ключа, а затворы вто- рых п- и -р-канальных транзисторов

5 10

15 20 5 о

5

0

5 0 5

каждого инвертирующего ключа - с ei-o входом, истоки первых п-канальных транзисторов первого, второго и четвертого инвертирующих ключей соединены с шиной отрицательного напряжения источника питания, стоки первых р-канальных транзисторов первого, j Toporo и четвертого инвертирующих ключей соединены с шинной положительного напряжения источника питания, затворы первых р-канальных транзисторов первого и четвертого инвертирующих ключей и первых п-канальных транзисторов второго и третьего инвертирующих ключей соединены с шиной тактового сигнала, затворы первых п-канальных транзисторов первого и четвертого инвертирующих ключей и первых р-канальных транзисторов .второго и третьего инвертирующих ключей соединены с шиной инверсного тактового сигнала, причем выходы пер- isoro и второго инвертирующих Ключей соединены с входом первого инвертора, вькод которого соединен с входами второго и третьего инвертирующих ключей, выходы третьего и четвертого инвертирующих ключей соединены с входами второго инвертора и первого инвертирующего ключа, выход второго инвертора соединен с входом четвертого инвертирующего ключа и выходом делителя частоты, отличающийся тем, что, с целью повышения надежности работы за счет исключения сбоев, вызванных разностью, фаз прямого и инверсного тактовых сигналов, в него -введены элементы ИЛИ-НЕ и И-НЕ и третьи п-канальный и р-канальнь1Й транзисторы, стоки каждого из которых.подключены соответственно к истоку первого п-канального и первого р-канального транзисторов третьего инвертирующего ключа, а истоки - соответственно к шинам от- рицательного и положительного напряжения источников питания, причем затвор третьего п-канального транзистора соединен с выходом элемента И-НЕ, первый и второй входы которого подключены к шине тактового сигнала и шине инверсного тактового сигнала соответственно, затвор третьего р-канального транзистора соединен с выходом элемента ИЛИ-НЕ, первый и второй входы которого соединены соответственно с шиной тактового сигнала и шиной инверсного тактового сигнала.

1-Г и LJ

n TL-Jl-JTi..

L

J

L

L

J

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Счетчик с начальной установкой | 1988 |

|

SU1615879A1 |

| D-триггер на КМДП-транзисторах | 1990 |

|

SU1728963A1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ | 1991 |

|

RU2010361C1 |

| ДИНАМИЧЕСКИЙ D-ТРИГГЕР | 2018 |

|

RU2679220C1 |

| КОЛЬЦЕВОЙ КМОП ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2011 |

|

RU2455755C1 |

| Компаратор | 1989 |

|

SU1690184A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

Изобретение относится к счетным схемам, предназначенным для использования в составе интегральных микросхем, изготовленных по К МОП технологии. Цель изобретения - повышение надежности работы делителя достигается путем исключения сбоев, вызванных разностью фаз прямого и инверсного тактовых сигналов. Делитель частоты содержит инвертирующие ключи 1-4, (Л

| Устройство для загрузки мусора в контейнер | 1987 |

|

SU1413044A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США W 3873852, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-06-23—Публикация

1984-10-01—Подача