(54) ЦИФРОВЫЕ ЭЛЕКТРОННЫЕ ЧАСЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов коррекции угла зажигания по сигналам детонации | 1988 |

|

SU1550205A1 |

| Многоканальный счетчик импульсов | 1983 |

|

SU1170610A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР С ПАРАЛЛЕЛЬНЫМ СДВИГОМ | 1969 |

|

SU250544A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Многоканальный измеритель временных интервалов в сериях импульсов | 1984 |

|

SU1257601A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Устройство для временного программного управления | 1985 |

|

SU1290259A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

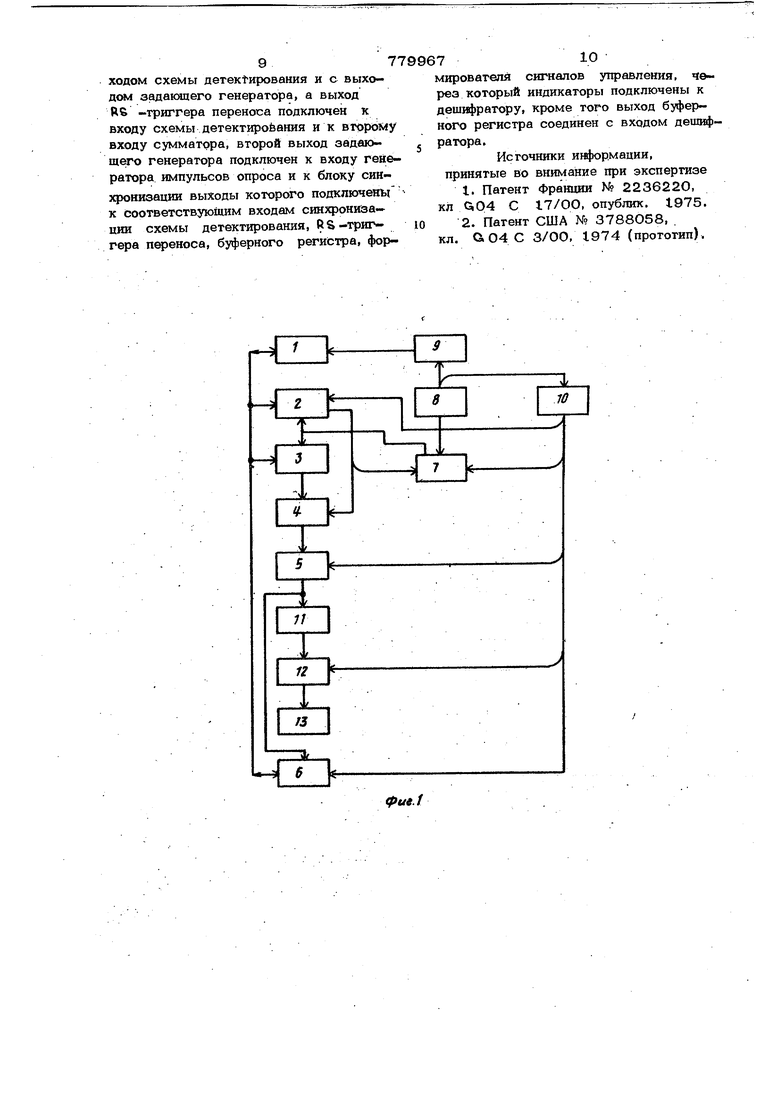

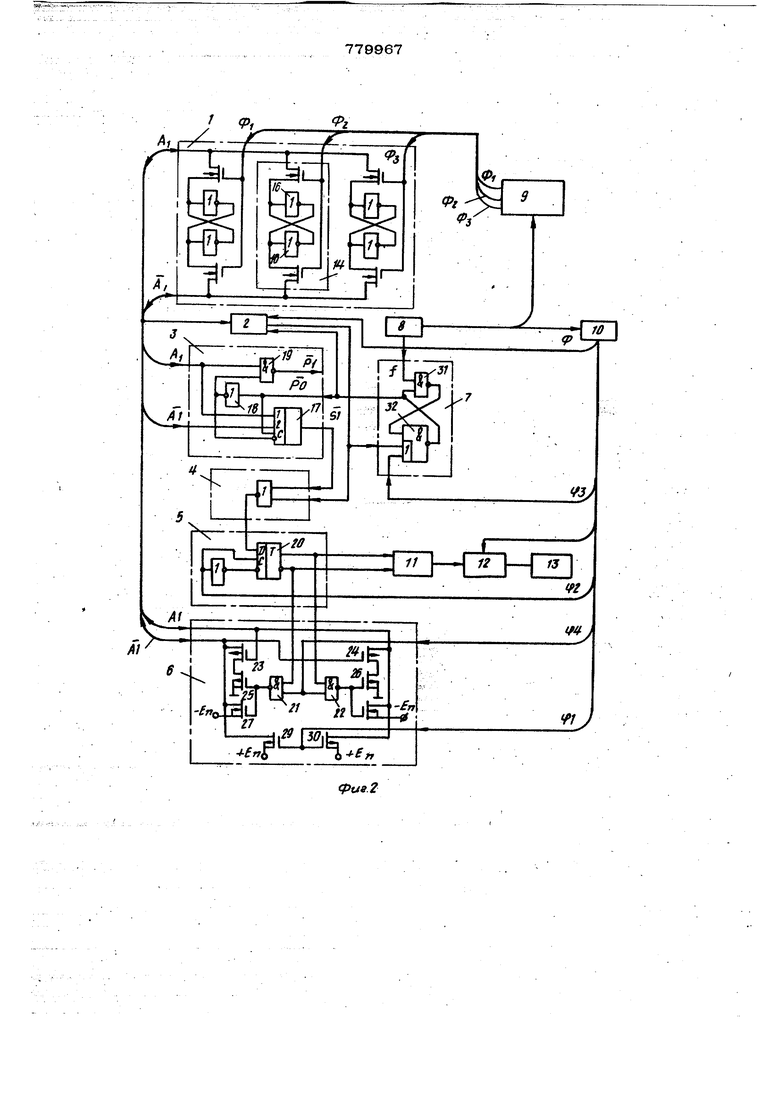

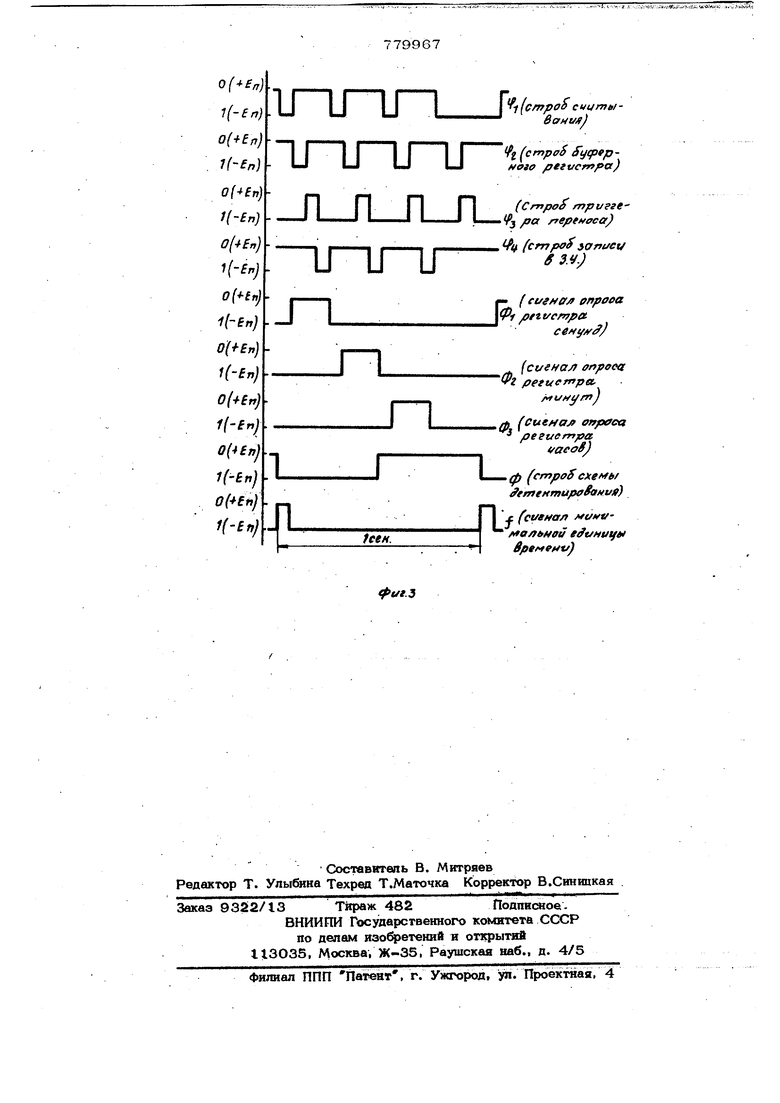

Изобретение относится к элекгронной технике, в часгности, к цифровьм электЧ ройным часам, в том числе к наручным часам. Известны цифровые электронные часы, содержащие генератор постоянной частоты, сигнал которого преобразуется последовательно соединенными двоичными делителями-счетчиками в информационные сигналы меньшей частоты (секунд, минут и т.д.), подающиеся в мультиплекс ном режиме на общий для всех счетчиков дешифратор, управляющий цифровым индикатором. Схема таких часов сложна, число элементов и межсоединений быстро возрастает при расширении функциональных возможностей часов 1. Наиболее близким по технической сущности прототипом являются цифровые электронные часы, содержащие задак щий генератор, запоминающее устройство и сумматор, входы которых соединены с выходами запоминающего устройства, схему установки запоминающего устройства в ноль, соединенную с выходами схемы детектирования, дешифратор временной информации, блок синхронизации и цифровой индикатор 2. Схема этих часов содержит меньшее количество элементов и межсоединений, однако, число элементов быстро возрастает При расширении функциональных возможностей часов. Крометого, так как цикл сдвига по пегле-регистр-сумматор должен происходить за минимальную единицу времени, то при увеличении объема памяти (длины регистра) вследствие увеличения частоты импульсов сдвига растет потребление , что приводит к уменьшению срока службы элементов питания наручных чйсов. Целью изобретения является увеличение надежности и снижения потребления энергии. Цель достигается тем, что в цифровые электронные часы введены: генератор им пульса опроса запоминающего устройства, соединенный с адресными входами эапо минаюшего устройства, RS триггер переноса, буферный регистр, схема записи информации в запоминающее устройство и формирователь сигналов управления индикатором, причем запоминающее устройство выполнено в виде регистров, поразрядно связанных общей шиной записи - считывания с сумматором, схемо детектирования, схемой записи информации в запоминающее устройство, при этом выходы сумматора соединены посредством схемы установки запоминающего устройства с информационными входами буферйого регистра, выходы которогчэ подключены к деш№})ратору и к схеме записи информации в запоминающее устройство, входы установки RS -триггера переноса связаны с выходом схемы детектирования и с выходом задающего гейёратора, а выходы RS -триггера перенос подключен к входу схемы детектирования и к второму входу сумматора, второй выход задающего генератора подключен к входу генератора импульсов опроса и блоку синхронизации, Ьыходы которого подключены к соответствующим входам схемы детектирования, RS -триггера переноса, буферного регистра, формирователя сигналов уп{5авления, через который индикаторы подключены к дещифратору, кроме того выход буферного регистра соединен с входом дешифратора. На фиг. I изображена структурная схема предлагаемых электронных часов; на фиг. 2 - один из вариантов функциональной схемы щестиразрядного операционного устройства цифровых электронных часов, осуществляющих счет и инди .кацию секуйд, минут, часов, схема кото рых вьшолнена на К/МДП транзисторах; на фиг; 3 - пример временной работы электронных часов, показанных ,фиг,2. На фиг. 2 приведен только младший разрядоперационного устройства. Схема и подключение пятя старщих разрядов операционного устройства идентичны схе ме и подключению младшего разряда. Часы содержат регистровое запоминающее устройство (ЗУ) I, количество . регистров в крторомf равно количеству чисел, пре(цртавл$пощих временную информацию, схему детектирования содержимого ЗУ на соответствие предоп деленным числам 2, сумматор 3, схему установки, регистров ЗУ в начальное сос тояние 4, буфернь Й регистр 5, схему за писи информации в ЗУ 6, RS -триггер переноса 7, задающий генератор Шч-шуль- сов минимальной единицы времени 8, генератор импульсов опроса регистров ЗУ 9, блок синхронизации 10, дешифратор II временной информации, хранящейся в ЗУ формирователь с1П налов управления индикатором 12 и цифровой индикатор 13. Регистры ЗУ поразрядно связаны двунаправленной шиной записи считывания А, к одноименным разрядам которой подключены также входы разрядов схемы детектирования и сумматора и одноименные разряды схемы записи. Выходы каждого разряда- сумматора соединены посредством схемы установки регистров ЗУ с информационными входами соответствующих разрядов буферного регистра, а выходы каждого разряда буферного регистра соединены со входами дешифратора, ВыхЬды дешифратора подключены к цифровому индикатору через формирователь сигналов управления индикатором. Выход RS -триггера подан на вход переноса младшего разряда сумматора и на вход схемы детектирования, выход которой соединен с одним из входов установки RS -триггера и со входбм схемы установки регистров ЗУ. Второй вход установки RS -триггера подключен к выходу сигнала минимальной единицы времени генератора 8; Генератор 8, как правило, включает. высокочастотный Кварцевый генератор и делитель частоты. Выходные сигналы каскадов деления частоты обычно используются для формированияпоследовательностей тактовых сигналов. Выходы генератора 8, соединенные с входами генератора Q и блочка синхронизации, представляют собой i выходы каскадов деления частоты. Выходы генератора 9 подключены к адресным входам регистров ЗУ, а выходные сигналы блока синхронизации поданы на тактобые входы схемы детектирования, RS -триггера переноса, буферного регистра, схемы записи и формирователя сигналов управления индикатором. Более подробно устройство предлагаемых часов иллюстрируется с помощью варианта схемы часов, предет/эвленного на фиг. 2.. Разряды регистров ЗУ I представляют собой шеститранзисторные ячейки памяти 14, включакяцие и -канальные транзисторы выборки 15 и бистабильную ячейку из замкнутых в кольцо инверторов 16. Затворы транзисторов выборки всех шести разрядов каждого регистра объединены и образуют адресные входы регистров секунд, минут и часов, соединенные соответственно с Бы-, ходами Ф , Фд и Фз, генератора импульсов опроса регистров 9. Стоки транзисторов выборки одноименных раз рядов регистров ЗУ подключены к соответствующим разрядам парафазной ишны : записи-считывания А. На фиг. 2 показано подключение младших разрядов регистров ЗУ к младшему разряду шины записи-считывания:к прямой А и инвер ной А цепям шины, Разряд сумматора 3 содержит двухплечевой ключ 17: инвертор 18 и вентиль 2И-НЕ-19. Вход инвертора 18, со диненный с управляющим входом С ключа 19, является входом переноса разряда сумматора. Вход переноса Р младшего разряда сумматора подключен к вы ходу ftS -триггера 7, как показано на фиг. 2. Входы переноса остальных раз. рядов сумматора соединены с выходами вентилей 18 соответствующих предшествующих разрядов сумматора. Старший, шестой разряд сумматора, н содержит формирователя сигнала- перенос вентиля 2И-НЕ 18. Выход ключа 17, яв ляющийся выходом разряда сумматора, подключен к выходу вентиля 2 ИЛИ-НЕ соответствуютэго разряда схемы установки 4. Выходы разрядов схемы 4 соединены с информационными выходами однотактовы Д-триггеров 2О буферного регистра 5. Выходы триггеров 20 соедине ны со входами вентилей 2 И-НЕ 21 и 22 схемы записи 6, которая также содер жит П -канальные транзисторы 27, 28 и |э -канальные транзисторы 23-26,29, ЗО. RS - триггер переноса 7 состоит из вентиля 2 И-НЕ 31 и вентиля 2 ИЛИ-2И-НЕ 32. , Цифровые электронные часы работают следующим образом. При включении питания блоки 8,9tlO (фиг.2) начинают гене рацию последовательностей импульсов, форма и обозначение которых-приведены на фиг. 3. В течение одной секунды выходы сигналов опроса Ф , Ф , ф„ генератора 9 последовательно переходят в состояние логического нуля (положительный уровень пктация Е на фиг. З), в результате чего транзисторы выборке 15 регистров секунд, минут и часов поочередно переходят в проводящее состояниег подключая выходы инверторов 16 этих регистров « шине записи-ч:читывання А. Перед переходом в нулевое соСг тояние выходов генератора 9 единичная фаза (отрицательный, уровень питания-Е на фиг. З) строба считывания ЗУ Ч , поступающего с блока синхронизации на затворы транзисторов 29,30 схемы записи переводит эти транзисторы в проводящее состояние, устанавливая на прямых и инверсных цепях А потенциал +Е,, что необходимо для предотвраще1с1я паразитного переключения ячеек ЗУ в момент подключения инверторов 16 к шине А. В течение нулевой фазы строба записи , поступающего с блока синхронизации на вентили 2И-НЕ 21,22 схемы записи, выходы этих вентилей находятся в состоянии логической единицы. При этом -. -канальные транзисторы 27, 28 заперты, а. р-канальные транзисторы 25,26 находятся в проводящем состоянии. Логическая единица, появляющаяся в прямой либо в инверсной цепи каждого разряда шины А в результате подключения к ней инверторов 16, отпирает транзистор 23 либо 24 соответственно, сохраняя логический нуль в инверсной либо в прямой цепи каждого разряда шины. Таким образом, в течение нулевой фазы строба записи , совпадающей с нулевой фазой сигналов опроса регистров ЗУ. состояние шиньг А идентично сосостоянию опрашиваемого регистра ЗУ, т.е. происходит считывание содержимого регистра ЗУ на шину А... .При единичном уровне строба записи Ч на выходе ве нтиля 21 (если в триггер 20 буферного регистра 5 записан нуль) либо на выходе, вентиля 22 (если в триггер 2О записана единица) устанавливается уровень логического нуля, отпирающий соответственно один из мощных г -канальных транзисторов 27 или 28. В результате отпирания транзистора 27 уровень логической единицы устанавливается в инверсной цепи шины А и переводит ячейку ЗУ в нулевое состояние, а в результате отпирания транзистора 28 логическая единица в прямой цепи шины А устанавливает ячейку ЗУ в единичное состояние. Таким образом, ячейка ЗУ при единичном уровне строба записи устанавливается в состояняе триггера 20 буферного регистра, т.е. содержимое буферного регистра записывается в опрашиваемый в данный момент регистр ЗУ. Одновременно состояние буферного регистра, а значит очередное состояние регистра ЗУ, поступает на дешифратор II и отображается цифровым индикатором 13. В бу ферный регистр при единичной фазе стро;ба If. записываются выходные сигналы схемы установки 4 (Представляющие собой пибо инверсию выходных сигналов сумматора 3 (если на схему уста1яовкн с выхода схемы детектирования 2 поступает логический нуль), либо логические нули (если с выхода схемы детектирова ния поступает логическая единица), При считывании на шину А одного из регистров ЗУ на выходах сумматора, i -тый разряд которого выполняет логическую функцию вида S - Р. А + Р. (i -1,2,3,4,5,6), формируется сигнал, представл5пощий собой либо инверсию чис ла на единицу большего, чем nocTymmiiie на шину-А (если на вход переноса Р младшего разряда сумматора приходит логический нуль с выхода RS -триггера переноса 7), либо инверсию числа, посту пившаго на йшну А (если на входе р. логическая единица). Татшм образом, при очередном опросе регистра ЗУ его содержимое либо увеличивается на единицу если на выходе триггера переноса и на выходе схемы детектирования логические нули, либо становится равным нулю, если на выходе схемы, детектирования ло. гическая единица, либо не изменяется, если ка выходе триггера переноса логическая единица. На выходе схемы детектирования появляется логическая единица, если состояние шины А при единичной фазе строба Ф соответствует числу 59 или при нулевой фазе строба Ф соответствует числу 23, а на выходе триггера переноса логический нуль, т.е. единица на выходе схемы детектирования формируется при опросе регистров секунд и минут в случае появления на выходе сумматора инверсии числа .60 и при опросе регистр часов в случае появления на выходе сум матора инверсии числа 24. Счет времени осуществляется следую щим образом. Логический нуль ни вызсоде генератор секундных импульсов устанавливает в состояние логического нуля вызсод ttS триггера переноса. Если содержимое регистра секунд меньше 59, то при нулевой фазе сигнала опроса Ф на выходе схемы детектирования логический нуль и содержимое регистра секунд увеличивается на единицу, а при нулевой фазе строба 4j , устанавливается в единицу, выход Й5-триггера переноса, и содержимое регистров минут часов остается неизменным. Если содержимое регистра секунд равно 59, то при считывании регистра секунд на выходе схемы детектирования логическая единица, и в регистр секунд записывается нуль, а на выход е-триггера переноса сохраняется нулевой уровень, что при нулевой фазе сигнала Ф„ вызывает изменение состояния регистра минут. Если приэтом содержимое регистра минут меньше 59, то при нулевой . фазе сигнала опроса Ф на выходе схемы детектирования логический нуль и содержимое регистра минут увеличивается на единицу, а при нулевой фазе строба Ф, устанавливается в единицу Выхода триггера переноса, и содержимое регистра .остается неизменным. Если содержимое регистра минут равно 59, то при считывании регистра минут на выходе схемы, детектирования логическая единица, и в регистре минут записывается нуль, а на выходе триггера переноса сохраняется нулевой уровень, что при нулевой фазе сигнала Ф, вызывает изменение состояния регистра часов. Фор м-у ла изобретения Цифровые электронные часы, соде ржащие задакиций генератор, запоминающее устройство, схему детектирования и сумматор, входы которых соединены с выходами запоминающего устройства, схему установки запоминающего устройства в ноль, соединенную с выходом схемы детектирования, дешифратор временной информации, блок синхронизации и цифровой индик;атор, отличающиеся, тем, что, с целью увеличения надежности и снижения потребления энергии, в них введены генератор импульсов опроса запоминающего устройства, соединённый с адресными входами запоминающего устройства, Я5 -триггер переноса, буферный регистр, схема записи информации в запоминающее устройство и формирователь сигналов управления индикатором, причем запоминающее устройство вьгаолнено в виде регистров, поразрядно связанных общей шиной записи - считывания с сумматором, схемой детектирования, схемой записи информации в запоминающее устройство, при этом выходы сумматора соединены посредством схемы установки запоминающего устройства в ноль с информационными входами буферного регист. ра, выходы которого подключены к дещнф ратору и к схеме записи информации в запоминающее устройство, входы установ- ки R S -триггера переноса связаны с .выходом схемы nereKtHpoBaHHH и с выходом задающего генератора, а выход R6 -триггера переноса подключен к входу схемы детектирования и к второму входу сумматора, второй выход задающего генератора подключен к входу генератора импульсов опроса и к блоку синхронизации выходы которого подключены к соответствующим входам синхрониза- ции схемы детектирования, RS-триггера переноса, буферного регистра, формирователя сигналов управления, чв рез который индикаторы подключены к дешифратору, кроме того выход буферного регистра соединен с входом дешифратора.

Источники информации, принятые во внимание при экспертизе

779967

Авторы

Даты

1980-11-15—Публикация

1978-11-21—Подача