Изобретение относится к вычислительной технике и может быть использовано для распределения запросов между ЭВМ многомашинных вычислительных систем.

Целью изобретения является повышение быстродействия.

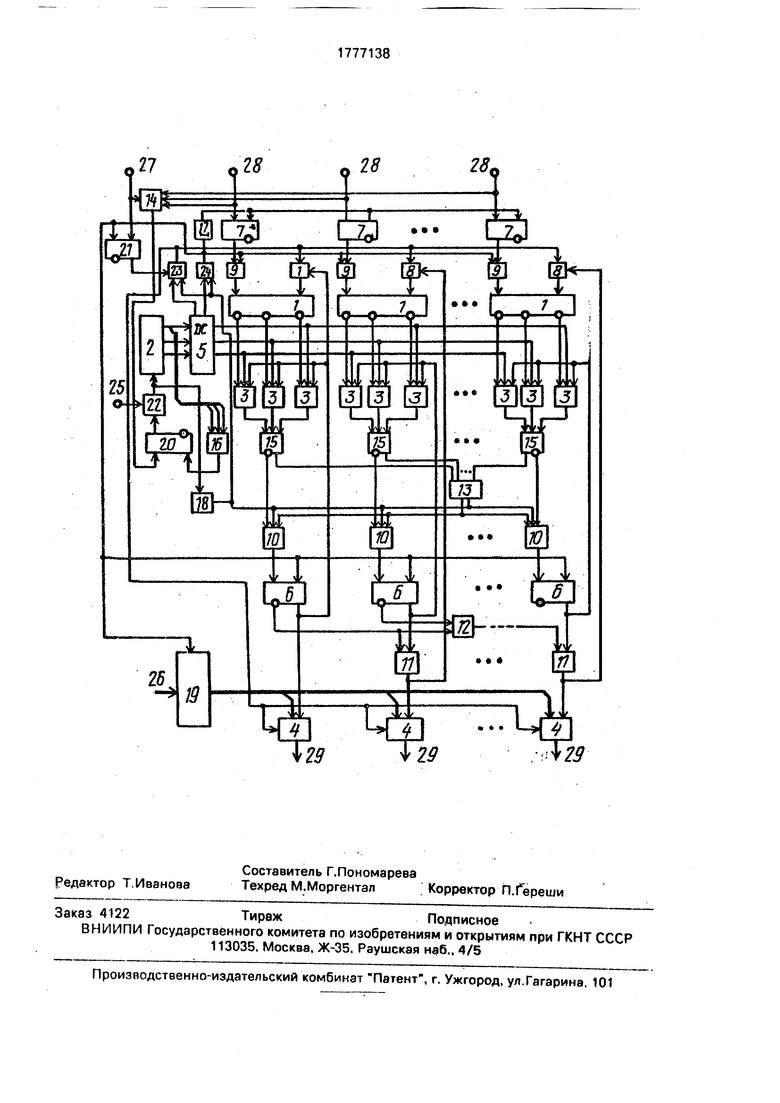

На чертеже представлена структурная схема устройства.

Устройство содержит группу из N счетчиков 1 запросов, счетчик 2 импульсов, две группы блоков элементов И 3, 4, дешифратор 5, две группы из N триггеров 6, 7, три группы из N элементов И 8. 9, 10, группу из (N-1)-ro элементов И 11, группу из (N-2)-x элементов И 12, элементы ИЛИ 13, 14, группу из N элементов ИЛИ 15, формирователь импульсов 16, элементы задержки 17, 18, регистр 19, триггеры 20, 21, элементы И 22, 23,24. На чертеже также показаны тактовый вход 25, информационный вход 26, запросный вход 27, сигнальные входы 28,и информационные выходы 29 устройства.

Устройство работает следующим образом. В исходном состоянии счетчики 1, 2. регистры 19, триггеры 7, 20, 21 находятся в нулевом состоянии, а триггеры 6 - в единичном состоянии. Состояние счетчика 1 соответствует числу заданий, находящихся в соответствующей ЭВМ системы. Для простоты изложения будем полагать, что все ЭВМ системы свободны. Первый блок элементов И 4 группы и первый элемент И 8 группы открыты единичным гютенциалом, поданным с выхода первого триггера 6 группы.

Поступающий на вход 26 устройства первый запрос записывается в регистр 19. Одновременно на запросный вход 27 поступает импульс, который установит триггер 21 в единичное состояние и через элемент ИЛИ 14 установит триггер 20 в единичное состояние, элемент И 22 откроется. С входа 25 тактовые импульсы будут поступать на вход счетчика 2. При поступлении первого

ч

Ј

VJ VJ VI

СО 00

тактового импульса на счетчик 2 на первом выходе дешифратора 5 появится единичный потенциал, который откроет элемент И 23, на третий вход которого также поступает единичный потенциал с выхода триггера 21. Первый тактовый импульс, пройдя элемент задержки 18, поступит через элемент И 23 на управляющие входы блока элементов И 4 группы и на входы элементов И 8 группы. Пройдя открытый первый элемент И 8, им- пульс поступит на суммирующий вход счетчика 1. Одновременно из регистра 19 первое задание поступит на первый выход 29 устройства. При поступлении второго тактового импульса сигнал со второго выхо- да дешифратора 5 откроет элемент И 24, и второй импульс, пройдя элемент задержки 18, открытый элемент И 24, установит регистр 19, триггер 21 в нулевое состояние, а триггеры 6 - в единичное состояние. При поступлении третьего тактового импульса на третьем выходе дешифратора 5 появится единичный потенциал, открывающий первые элементы И 3 блоков, и инверсные значения старших разрядов счетчиков 1 поступают на входы элемента ИЛИ 15. Так как все старшие разряды счетчиков находятся в нулевом состоянии, то на соответствующем входе всех элементов ИЛИ 15 будут единичные потенциалы, и все элементы И 10 будет закрыты потенциалом, поданным с инверсного выхода элемента ИЛИ 15, в результате чего триггеры б останутся в единичном состоянии.

При поступлении четвертого, как и по- следующих, тактового импульса на вход счетчика 2 на четвертом (очередном) выходе дешифратора 5 появится единичный сигнал, и инверсный код второго (очередного) старшего разряда каждого счетчика 1 поступит на вход соответствующего элемента ИЛИ 15.

Если с инверсных выходов соответствующего разряда счетчиков 1 поступят только единичные сигналы, то элементы И 10 оста- нутся закрытыми, так как на инверсных выходах элементов ИЛИ 15 будут нулевые потенциалы, и триггеры 6 останутся в единичном состоянии.

Если с инверсных выходов соответству- ющего разряда счетчиков 1 поступят только нулевые сигналы, то элементы И 10 останутся закрытыми, так как закрыт элемент ИЛИ 13, и триггеры 6 не изменят своего состояния.

Если с инверсных выходов соответствующего разряда счетчиков 1 на входы элементов ИЛИ 15 поступят единичные и нулевые потенциалы, то в этом случае открываются те элементы И 10, которые соответствуют нулевым потенциалам на входах элементов ИЛИ 15. Тактовый импульс с выхода элемента И 22, пройдя через элемент задержки 18 (время задержки которого должно быть не менее времени переходных процессов в счетчике 2, дешифраторе 5, элементах И 3 и ИЛИ 15) и открытые элементы И 10, установит соответствующие триггеры 6 в нулевое состояние, при этом соответствующие блоки элементов И 3 закроются, исключая из дальнейшего анализа последующие разряды счетчиков 1.

Поступление тактовых импульсов через элемент И 22 будет происходить до тех пор, пока не поступит (pi+З) импульсов. При поступлении (pi+3}-ro импульса счетчик 2 уста- навливается в нулевое состояние, формирователь 16 вырабатывает импульс, устанавливающий триггер 20 в нулевое состояние, и элемент И 22 закрывается. В единичном состоянии останутся только те триггеры 6, которые соответствуют минимальным значениям счетчиков 1. В этом случае будет открыт только тот блок элементов И 4. который соответствует первому триггеру, находящемуся в состоянии Г.

При поступлении очередного запроса устройство работает аналогично, с той разницей, что задание поступит на тот выход 29 устройства, который соответствует счетчику 1 с минимальным значением, а при равенстве значений в счетчиках 1 - на первый из минимальных.При выполнении задания в ЭВМ на соответствующий вход 28 устройства поступает сигнал, который устанавливает в единичные состояния соответствующий триггер 7 и через элемент ИЛИ 14 триггер 20. Элемент И 22 открывается. Тактовые импульсы поступают на вход счетчика 2. По первому тактовому импульсу изменений в схеме не произойдет, так как триггер 21 находится в нулевом состоянии и элемент И 23 закрыт. По второму тактовому импульсу триггер 21, регистр 19 подтверждают свое нулевое состояние, триггеры 6 установятся в единичное состояние, а на вычитающий вход счетчика 1, соответству ющего триггеру 7, находящемуся в единичном состоянии, с выхода элемента И 24 через открытый элемент И 9 поступит импульс, по которому содержимое счетчика 1 уменьшится на единицу. По последующим тактовым импульсам проводится выбор менее загруженной ЭВМ описанным выше способом.

Формула изобретения

Устройство для распределения заданий между ЭВМ, содержащее группу из N (N - число запросов) счетчиков запросов, счетчик импульсов, /jee группы из N блоков элементов И, дешифратор, первый триггер, две группы из N элементов И, первый элемент И. элемент ИЛИ. группу из N элементов ИЛИ, регистр и первый элемент задержки, причем тактовый вход устройства соединен с первым входом первого элемента И, выходы блоков элементов И первой группы являются группой информационных выходов устройства, 1-й сигнальный вход устройства (1-1,2,..., N) соединен с 1-м входом первого элемента ИЛИ, выход которого соединен с единичным входом первого триггера, единичный выход которого соединен с вторым входом первого элемента И, выход 1-го элемента И первой группы соединен с сумми- рующим входом 1-го счетчика запросов группы, группа инверсных выходов которого соединена с первой группой входов 1-го блока элементов И второй группы, вторая группа входов р-х элементов И всех блоков второй группы (р 1, 2, ..., pi, где pi - разрядность счетчиков запросов) соединены с (р+2)-м выходом дешифратора, группа входов которого соединена с группой выходов счетчика импульсов, группа выходов 1-го блока элементов И второй группы соединена с группой входов 1-го элемента ИЛИ группы, инверсный выход которого соединен с первым входом 1-го элемента И второй группы, запросный вход устройства соединен с (N+1J-M входом первого элемента ИЛИ, выход первого элемента И соединен с входом первого элемента задержки, отличаю - щ е е с я тем, что, с целью повышения быстродействия, в него введены две группы из N-1 и N-2 элементов И, две группы из N триггеров, третья группа из N элементов И, формирователь импульсов, второй и третий элементы И. второй триггер, второй элемент ИЛИ и второй элемент задержки, причем запросный вход устройства соединен с единичным входом второго триггера, единичный выход которого соединен с первым входом второго элемента И, второй вход которого соединен с первым выходом де- шифратора, второй выход которого соединен с первым входом третьего элемента И, выход которого соединен с нулевым входом второго триггера, единичными входами триггеров первой группы, входом установки в О регистра, первыми входами элементов И третьей группы, а также через второй элемент задержки - с нулевыми входами триггеров второй группы, единичный вход 1-го триггера второй группы является 1-м сигнальным входом устройства, единичный выход 1-го триггера второй группы соединен с вторым входом 1-го элемента И третьей группы, выход которого соединен с вычитающим входом 1-го счетчика запросов группы, выход первого элемента И соединен со счетным входом счетчика импульсов, разрядные выходы которого соединены с входами формирователя импульсов, выход которого соединен с нулевым входом триггера, выход первого элемента задержки соединен с вторым входом третьего элемента И, вторыми входами элементов И второй группы и третьим входом второго элемента И, выход которого соединен с первой группой входов блоков элементов И первой группы и первыми входами элементов И первой группы, третьи входы элементов И второй группы соединены с выходом второго элемента ИЛИ. входы которого соединены с прямыми выходами элементов ИЛИ группы, выход 1-го элемента И второй группы соединен с нулевым входом 1-го триггера первой группы, единичный выход которого соединен с третьей группой входов 1-го блока элементов И второй группы, единичный выход первого триггера первой группы соединен с второй группой входом первого блока элементов И первой группы и вторым входом первого элемента И первой группы, а нулевой выход соединен с первыми входами первых элементов И четвертой и пятой групп, нулевой выход k-ro триггера первой группы (k 2, 3,.... N-1) соединен с вторым входом (k-1)-ro элемента И пятой группы, выход которого соединен с первым входом k-ro элемента И четвертой группы, выход }-го элемента И пятой группы 0 1,2,..., N-3) соединен с первым входом Q+1)-ro элемента И пятой группы, единичный выход 1-го триггера первой группы (I 2, 3N) соединен

с вторым входом (1-1}-го элемента И четвертой группы, выход которого соединен с вторым входом 1-го элемента И первой группы и второй группой входов 1-го блока элементов И первой группы, информационные входы устройства соединены с информационными входами регистра, группа разрядных выходов которого соединена с группой входов блоков элементов И первой группы.

28

28

28.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления очередностью обслуживания | 1987 |

|

SU1481765A2 |

| Устройство для обслуживания запросов | 1987 |

|

SU1437864A1 |

| Устройство для вывода информации | 1984 |

|

SU1238090A1 |

| Устройство для сопряжения дискретных датчиков с электронной вычислительной машиной | 1982 |

|

SU1024898A2 |

| УСТРОЙСТВО ДЛЯ КОММУТАЦИИ СООБЩЕНИЙ | 1994 |

|

RU2110837C1 |

| Устройство для сопряжения двух электронных вычислительных машин (эвм) | 1984 |

|

SU1187172A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1571588A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ДОСТУПОМ К МАГИСТРАЛИ В ЛОКАЛЬНЫХ СЕТЯХ С МАГИСТРАЛЬНОЙ АРХИТЕКТУРОЙ | 1991 |

|

RU2017214C1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1476466A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ОБСЛУЖИВАНИЯ ЗАПРОСОВ | 2000 |

|

RU2157561C1 |

Изобретение может быть использовано для распределения запросов между ЭВМ многомашинных вычислительных систем. Целью изобретения является повышение быстродействия. Устройство для распределения заданий между ЭВМ содержит группу счетчиков запросов, счетчик импульсов, две группы блоков элементов И, дешифратор, два триггера, пять групп элементов И, три элемента И, два элемента ИЛИ, группу элементов ИЛИ, регистр, два элемента задержки, две группы триггеров, формирователь импульсов. В устройстве осуществляется параллельный просмотр загрузки всех ЭВМ. 1 ил.

| Устройство для распределения заданий между ЭВМ | 1983 |

|

SU1111163A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления обслуживанием запросов | 1982 |

|

SU1045228A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-11-23—Публикация

1991-01-16—Подача