ответственно с управляющими входами второго и первого коммутаторов, седьмой выход - с вторым входом вто рого регистра управления, а восьмой выход - с входами управления записью буферного регистра первого и второго регистров адреса и регистра счета, информационные входы которых соединены с выходом второго коммутатора, второй информационный вход которого подключен к второму выходу первого блока усиления, входы установки первого и второго регистров управления подключены к второму выходу блока управления передачей, а выходы соответственно - к вторым входами первого и второго блоков пре рывания, первому и второму входам блока управления передачей и втором и третьему информационным входам первого коммутатора, четвертый, пятый и шестой информационные входы которого соединены соответственно с выходами буферного регистра, второго регистра адреса и первым выходом регистра счета, третьи вход и выход блока управления передачей |соединены соответственно с вторыми выходом и входом блока управления шиной первой ЭВМ, четвертые вход и выход - соответственно с вторыми выходом и входом блока управления шиной второй ЭВМ, пятьй вход - с вт рым выходом регистра счета, а пятьш выход - с вторым входом записи буферного регистра и счетными входами регистра счета и первого и второго регистров адреса, причем блок управ ления передачей содержит десять эле ментов И, элемент И-НЕ, два элемента И-1ШИ, элемент НЕ, четыре тригге ра, элемент И-ИЛИ-НЕ, два формирователя импульсов, счетчик, дешифратор и генератор, причем первые и вт рые входы дешифратора соединены соответственно с первым и вторым входами блока, первый вход первого эле мента И, входы первого формировател импульсов и элемента НЕ соединены с третьим входом блока, второй вход i epBoro элемента И и первые входы второго элемента И и первого и втор го элементов И-ИЛИ непосредственно, а первый вход элемента И-ИЛИ-НЕ череэ второй формирователь импульсов соединены с четвертым входом блока, первый, второй и третий входы первого триггера соединены соответственно с выходами третьего и четверт го элементов И и вторым выходом второго формирователя импульсов, первый, второй и третий входы второго триггера подключены соответственно к выходам пятого и второго элементов И и к первому входу третьего элемента И и первому выходу первого формирователя импульсов, вторым выходом соединенного с вторым входом элемента И-ИЛИ-НЕ, первый, второй и третий входы третьего триггера подключены соответственно к выходам шестого и первого элементов И и первому выходу дешифратора, соединенного вторым и третьим выходами соответственно с первыми входами четвертого и пятого элементов И, вторые входы которых подключены к выходу третьего триггера, вторым входам второго и третьего элементов И и первым входам седьмого и восьмого элементов И, выход второго триггера соединен с первым входом четвертого триггера и входом генератора, первые входы девятого и десятого элементов И соединены соответственно с выходами первого триггера и счетчика, подключенного первым входом к первому выходу генератора, а вторым входом - к выходу восьмого элемента И, второй вход которого соединен с выходом элемента И-ИЛИ-НЕ, третьим входом подключенного к вторым входам первого и второго элементов И-ИЛИ и выходу четвертого элемента И, а четвертый входом - к выходу пятого элемента И, второму входу девятого элемента И и третьему входу первого элемента И-ИЛИ, четвертьй вход которого соединен с выходом элемента НЕ, первый вход шестого элемента И соединен с первым выходом дешифратора, а второй вход - с пятым входом блока и вторым десятого элемента И, выход четвертого триггера подключен к третьему входу второго элемента И-ИЛИ и первому входу элемента И-НЕ, второй вход которого и второй вход седьмого элемента И соединены соответственно с вторым и третьим выходами генератора, второй вход четвертого триггера соединен с выходом седьмого элемента И, выходы первого элемента И-1-ШИ и элемента И-ИЛИ-НЕ образуют пятый выход блока, выходы четвертого и пятого элементов И, четвертый выход генератора-) первый выход дешифратора и 7 Блок 5 формирования управляющих сигналов вьфабатывает управляющие воздействия дгтя блоков устройства и работает следующим образом (фиг.2 При обращении одной из ЭВМ к уст ройству, например, в том случае, есл вторая ЭВМ производит запись слова в один из регистров устройства, с входа 42 на входы элементов И-НЕ 30 (цепь 42а) поступает код адреса регистра. На другие входы зтих элементов, а также на вход элемента ИЛИ 31 с входа АЗ поступает сигнал выборки устройства, разрешающий прохож дение кода адреса через элементы ИНЕ 30 на вход дешифратора 27. На др гой вход дешифратора подается управляющий сигнал единичного уровня с элемента ИЛИ 31. При этом на одно из выходов дешифратора вырабатывает ся сигнал, разрешающий прохождение сигнала записи по цепи 426 через один из элементов И 34 и 35 на один из.выходов 49 и 50, которьш связан с адресуемым регистром. Если запись производится по кома де от первой ЭВМ, то код адреса ре.гистра поступает на вход дешифратора 27 по цепи 40а через И-НЕ 29. С входа 41 поступает сигнал.выборки устройства, разрешающий формирование сигнала записи, а с входа 40 подается импульс записи (цепь 406). Так же при наличии сигналов записи и выборки от первой ЭВМ, поступающи на входы элемента И 21, на выходе последнего и соответственно через элемент ИЛИ 24, на выходе 44 появля ется сигнал, управляющий работой коммутатора 3. Наличие сигнала (еди ничный уровень) означает, что выход коммутатора 3 соединен с выходом блока 2, а при отсутствии сигнала (нулевой уровень) выход коммутатора 3 подключен к выходу блока 9. При выполнении операции чтения регистра устройства одной из ЭВМ на выходе 47 через элементы И-НЕ 29 или 30, как это было описано для операции записи, поступает код регистра. Этот код управляет работой коммутатора i1, подключает его информационные входы к адресуемому регистру. Одновременно на входы эле мента И 22 (если чтение производит первая ЭВМ) или элемента И 23 (если чтение производит вторая ЭВМ) подаются сигналы выборки и чтения. С вы 28 хода этих элементов через элементы ИЛИ 25 или 26 на одном из выходов 45 или 46 появляется сигнал, разрешающий выдачу информации из регистра через соответствующий блок усиления на интерфейсную шину ЭВМ. Элементы ИЛИ 32, И-НЕ 38 и элемент 37 задержки формируют на выходе 51 ответньй синхросигнал при каждом обращении второй ЭВМ к устройству. В режиме передачи информации, когда устройство осуществляет управление интерфейсными шинами ЭВМ, блок 5 формирует управляющие сигналы для блоков 2 и 9 и коммутаторов 3 и 11. Формирование указанных сигналов синхронизируется блоком 18. С входа 39 сигналы синхронизации поступают на входы элементов ИЛИ 24 и 26 и элементы ИЛИ 25, вызывая появление сигналов на их выходах и, соответственно на выходах 44-46 блока. Наличие сигнала (единичный уровень) на выходах 45 и 46 означает переключение соответствукнцего блока усиления, связанного с данным выходом, в режим передачи информации на пшну ЭВМ. Отсутствие сигнала (нулевой уровень) означает нахождение блоков усиления в режиме приема информации с щины. Сигнал, поступаьощий на вход элемента ИЛИ 24, управляет работой коммутатора 3. Сигналы с входа 39 поступают на элементы И-НЕ 28, вызывая на выходе 47 установку кода, управляющего коммутатором 11. Блок 18 управления передачей вырабатывает сигнал управления и синхронизации для блоков устройства в режиме внепроцессорной передачи и работает следующим образом (фиг.З). Инициация режима внепроцессорной передачи начинается с появления на входах 76 и 77 кода направления передачи и сигнала запроса на передачу. В этом случае, с первого выхода дешифратора 55 на выходы 82 и 84 поступает сигнал (единичньй уровень), являющийся требованием для блоков 19 и 20 начать операции по захвату управления над интерфейсными шинами ЭВМ. На втором или третьем выходах дешифратора 55 устанавливается сигнал, определяющий направление передачи. Наличие сигнала (единичный уровень) на втором выходе означает передачу из первой ЭВМ во вторую. 9 . При наличии сигнала на третьем выходе происходит передача в обратном направлении. После завершения указанных операций по захвату управления над шинами на входах 78 и 79 и на входах элемента И 56 появляются сигналы единичного уровня, вызывающие установку триггера 63. При этом, на входах элементов И 60-65 и на связанных с ними входах сброса триггеров 68-70 появляется уровень логической единицы, который разрешит работу триггеров блока. Установка триггера 63 инициирует передачу первого слова. Рассмотрим, например, передачу в направлении от первой ЭВМ ко второй. В этом случае блок 18 вырабатывает сигналы управления для реализации операции чтения на шине первой ЭВМ, а затем для операции записи на шине второй ЭВМ. После установки триггера 63 на выходе элемента И 61 появляется единичный уровень сигнала, который поступает на счетный вход триггера 68 и вызьшает его установку. Единичньй уровень сигнала с выхода триггера 68 (цепь 83а) подается на вход блока 5 который обеспечивает выдачу адреса из регистра 14 через блок 2 на шину 4 первой ЭВМ и подключение входного коммутатора 3 к блоку 2. Одновременно этот сигнал (цепь 82а) поступает в блок 19, который вырабатыв ет сигналы управления, и синхронизации, соответствующие операции чте ния на шине первой ЭВМ. После получения сигнала синхронизации адресуемая ячейка выставляет данные на шину 4 и вырабатьшает ответный синх росигнал, который через блок 19 пос тупает на вход 78 и через элемент НЕ 52 и элемент И-ИЛИ 59 на выход 81 блока. По переднему фро ту этого сигнала происходи запись информации в буферный регистр 13. После окончания цикла чтения на шин первой ЭВМ с входа 78 по цепи 786 н вход одновибратора 54 поступает еди. ничный уровень сигнала. При этом, на выходах одновибратора 54 формируются импульсы, которые через элемент И 60 сбрасывают триггер 68, завершая на этом цикл обращения к шине 4, и устанавливают триггер 69, которьш разрешает работу элементов управления шиной второй ЭВМо Формир ванне управляющих воздействий при выполнении операций на шине второй ЭВМ тактируется импульсами с генератора 58. Генератор 58 вьфабатывает на своих выходах трехфазную последовательность сдвинутых относительно друг друга импульсов, обеспечивающих необходимые временные соотношения между интерфейсными сигналами. Последовательности импульсов формируются только в течение цикла обращения к шине 8 (при этом на выходе триггера 69 - единичный уровень). Пикл обращения к шине второй ЭВМ начинается с вьщачи адреса на шину. Управляет вьщачей адреса триггер 70, которьш устанавливается сигналом с выхода триггера 69, а сбрасывается тактовым импульсом с генератора 58,, С выхода триггера 70 сигнал (единичный уровень) через выход 83 поступает в блок 5, обеспечивая подключение регистра 15 к коммутатору 11 (сигнал по цепи 83в) и переключение блока 9 в режим передачи на шину (сигнал по цепи 836 через элемент И-ИЖ 73). Одновременно на входе элемента И-НЕ 74 устанавливается единичньй уровень, разрешающий прохождение тактового импульса с генератора 58 на выход 84. Этим тактовым импульсом происходит запуск блока 20, которьм формирует необходимые интерфейсные сигналы управления и синхронизации. Сигнал синхронизации, формируемый блоком 20 в течение цикла обращения к шине, поступает также на вход 79 и через элемент И-ИЛИ 73 поступает на вькод 83, обеспечивая выдачу слова данных из буферного регистра 13, через коммутатор 11 и блок 9 на шину второй ЭВМ По сбросу сигнала синхронизации (на выходе 796 нулевой уровень) на прямом и инверсном выходах одновибратора 53 ф|Ормируются импульсы, один из которых через элемент И-ИЛИ-НЕ 67 и выход 81 поступает на счетные входы регистров 14-16, вызывая увеличение содержимого регистров 14 и 15 адреса и уменьшение содержимого регистра 16, а импульс с инверсного выхода одновибратора 53 вызывает установку триггера 68, инициируя новый цикл обращения к шине первой ЭВМ. При осуществлении передачи в обратном направлении, от ЭВМ 2 тс ЭВМ 1, цикл передачи слова состоит из операции чтения на шине 8 и операции записи на шине 4. Первый цикл перевыход элемента Н-НЕ образуют четвертый выход блока, выходы десятого элемента И и счетчика образуют второй выход блока, выходы первого и четвертого триггеров, девятого элемента И и второго элемента И-ИЛИ образуют первьй выход блока, выходы первого триггера и пятого элемента И и первый выход дешифратора образуют третий выход блока, а блок управления шиной первой ЭВМ содержит два элемента И, четыре элемента И-НЕ, два элемента НЕ, формирователь импульса, три триггера и три элемента задержки, причем вход формирователя импульса и первый вход первого элемента И соединены с первым входом блока, входы сброса первого и второго триггеров, первый вход первого элемента И-НЕ, первый и второй входы второго элемента ИНЕ и вход первого элемента задержки образуют второй вход блока, выходы первого, второго, третьего и четвертого элементов И-НЕ, второго элемента И и первого элемента НЕ образуют первый выход блока, выход первого элемента И соединен через второй элемент задержки с входом сброса третьего триггера, соединённого выходом с входом первого элемента НЕ, инверсный выход второго триггера соединен с вторым входом первого элемента И и первым входом третьего элемента И-НЕ, инверсный выход второго триггера, выходы третьего триггера и. первого элемента И образуют второй выход блока, выход формирователя импульса соединен с входом установки первого триггера, входом второго элемента НЕ и через третий элемент задержки - с первым входом второго элемента И, выход первого элемента задержки подключен к выходу установки третьего триггера, инверсный выход первого триггера подключен к вторым входам первог и второго элементов И-НЕ, прямой выход первого триггера подключен к информационному входу второго триггера и второму входу третьего элемента И-НЕ, выход второго элемента НЕ соединен с синхровходом второго триггера, прямые выходы первого и второго триггеров подключены соответственно к первому и второму входам четвертого элемента И-НЕ, при этом блок управления шиной вто72

рой ЭВМ содержит пять элементов НЕ, пять элементов И-НЕ, три триггера и два элемента задержки, причем входы первого и второго элементов НЕ

образуют первый вход блока, вход сброса первого триггера, соединенный с первым входом первого элемента ИНЕ, синхровход второго триггера и первые входы второго, третьего, четвертого элементов И-НЕ образуют второй вход блока, выходы второго, третьего, первого и пятого элементов. И-НЕ, третьего и четвертого элементов НЕ образуют первый выход блока, прямой выход первого триггера соединен с входом четвертого элемента НЕ и информационными входами второго и третьего триггеров, прямой выход второго триггера соединен с входом третьего элемента НЕ и вторым входом четвертого элемента И- НЕ, инверсный выход третьего триггера, прямые выходы первого и второго триггеров, выход второго элемента НЕ образуют второй выход блока, выход первого элемента НЕ подключен к входу установки первого триггера и через первый элемент задержки - к первому входу пятого элемента И-НЕ, вход пятого элемента НЕ соединен с выходом второго элемента з.адержки и с входом сброса третьего триггера, а выход - с входом сброса второго триггера, выход .четвертого элемента И-НЕ подключен к синхровходу третьего триггера, прямой выход которого соединен с вторым входом второго и третьего элементов И-НЕ, инверсный выход первого триггера соединен с вторыми входами первого и пятого элементов И-НЕ, выход второго элемента НЕ соединен с входом второго элемента задержки, причем блок формирования управлякяцих сигналов содержит пять элементов И, пять элементов ИЛИ три группы элементов И-НЕ, дешифратор, группу элементов И, группу элементов ИЛИ, элемент задержки и элемент И-НЕ, причем первые входы первого и второго элементов И, первого элемента ИЛИ и элементов И-НЕ

первой группы соединены с вторым входом блока, вторые входы первого, второго элементов- И, элементов И-НЕ первой группы и первые входы второго элемента ИЛИ и третьего элемента И соединены с первым входом блока.

первые входы четвертого и пятого элементов И, элементов И-НЕ второй группы третьего элемента ИЛИ, вторые входы второго и третьего элементов ИЛИ подключены к третьему входу блока, вторые входы четвертого элемента И, первого элемента ИЛИ, элементов И-НЕ второй группы и первый вход элемента И-НЕ подключены к четвертому входу блока, первые входы четвертого и пятого элементов ИЛИ и элементов ИЛИ группы, первые и вторые входы элементов И-НЕ третьей группы соединены с пятым входом блока, выходы четвертого и пятого элементов ИЛИ и элементов ИЛИ группы являются соответственно пятым, четвертым и третьим выходами блока, выходы третьего и пятого :элементов И и элементов И группы являются соответственно первым, седь1

72

и восьмым выходами блока, выход элемента И-НЕ является вторым выходом блока, выходы элементов И-НЕ первой, второй и третьей групп соединены с первым входом дешифратора и с шестым выходом блока, выходы первого, четвертого и второго, элементов И подключены соответственно к вторым входам четвертого и пятого элементов ИЛИ и элементов ИЛИ группы выход первого элемента ИЛИ подключен к второму входу дешифратора,. выход которого соединен с вторыми входами третьего и пятогб элементов И и первыми входами элементов И группы, . выход третьего элемента ИЛИ соединен через элемент задержки с вторым входом элемента И-НЕ, а выход второго элемента ИЛИ - с вторым входами элементов И группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения двух вычислительных машин | 1980 |

|

SU922716A1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1605242A1 |

| Устройство для ввода аналоговых сигналов | 1990 |

|

SU1742810A1 |

| Устройство для сопряжения электронных вычислительных машин | 1981 |

|

SU1013938A1 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ДВУХ ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН (ЭВМ), содержащее два блока усиления, первый дешифратор, блок формирования управляющих сигналов, первые коммутатор, регистр управления и блок прерывания, причем первый выход первого блока усиления соединен с интерфейсной шиной первой ЭВМ, а второй выход - с первым входом первого регистра управления, второй вход которого соединен с первым выходом блока формирования управляющих сигналов, второй выход которого и первьш выход второго блока усиления подключены к интерфейсной шине второй ЭВМ, первые входы первого и второго блоков усиления подключены к выходу первого, коммутатора, первый вход первого дешифратора и первый вход первого блока прерывания соединены с интерфейсной шиной первой ЭВМ, отличающееся тем, что, с целью повьшения пропускной способности устройства, в него введены вторые коммутатор, дешифратор, регистр управления и блок прерывания, буферный регистр, два регистра адреса, регистр счета, блок управления передачей, блок управления шиной первой ЭВМ и блок управления шиной второй ЭВМ, причем первый выход первого дешифратора, второй вход первого блока усиления,, первые выход и вход блока управления шиной первой ЭВМ соединены с интерфейсной шиной первой ЭВМ, третий вход первого блока усиления соединен с третьим выходом блока формирования управляющих сигналов, четвертьй вход - с выходом первого регистра адреса и первым информацион§ ным входом первого коммутатора, а третий выход соединен с вторым входом (Л первого дешифратора и с первым входом блока формирования управляющих сигналов, второй выход первого дешифратора подключен к второму входу блока формирования управляющих сигналов, третьим входом соединенного с первым входом второго дешифратора и вторым выходом второго блока усиления, вторые входы вторых дешифратора и блока усиления, первые входы и выходы второго блока прерывания и блока управления шиной второй ЭВМ соединены с интерфейсной шиной второй ЭВМ, третий вход второго блока усиления соединен с четвертым выходом блока формирования управляющих сигнал bjB, а второй выход соединен с первым входом второго регистра управления и первым информационным входом второго коммутатора, четвертый вход блока формирования управляющих сигналов подключен к выходу второго дешифратора, пятый вход - к первому выходу блока управления передачей, пятый и шестой выходы соединены со

Изобретение относится к вычислительной технике к может быть использовано для сопряжения двух разнотипных электронных вычислительных машин (ЭВМ). . .

Цель изобретения - повьшение пропускной способности устройства посредством реализации процедуры внепроцессорной передачи информации между сопрягаемыми ЭВМ.

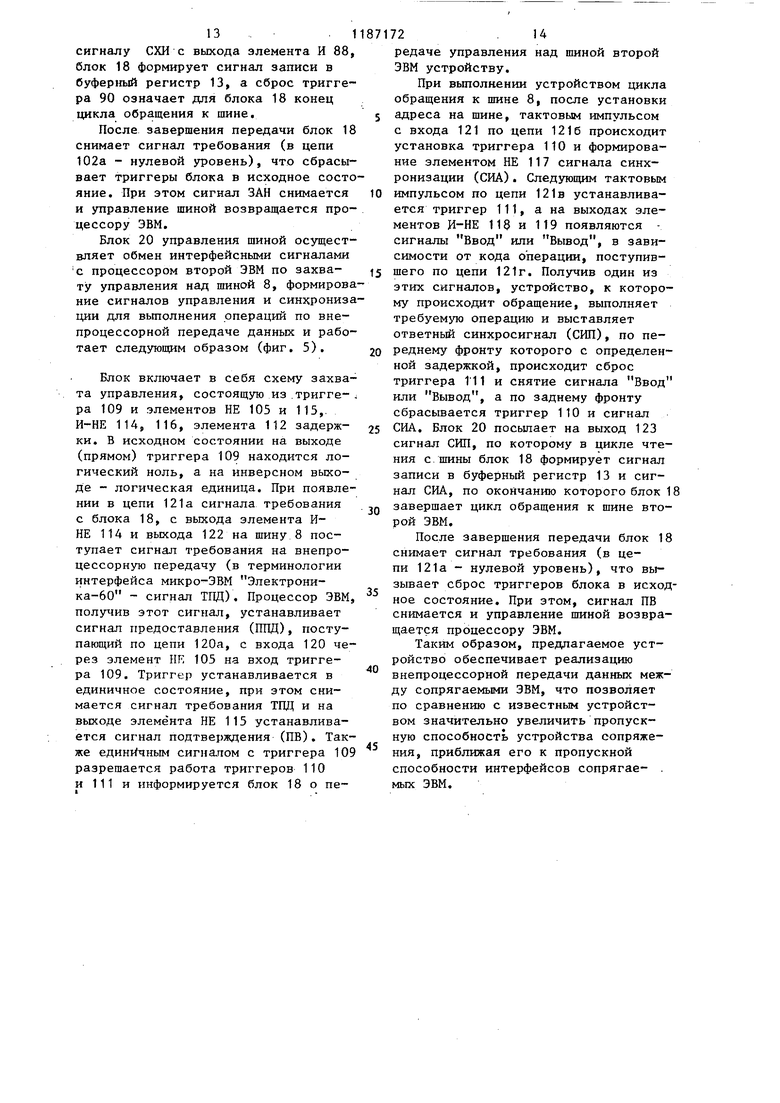

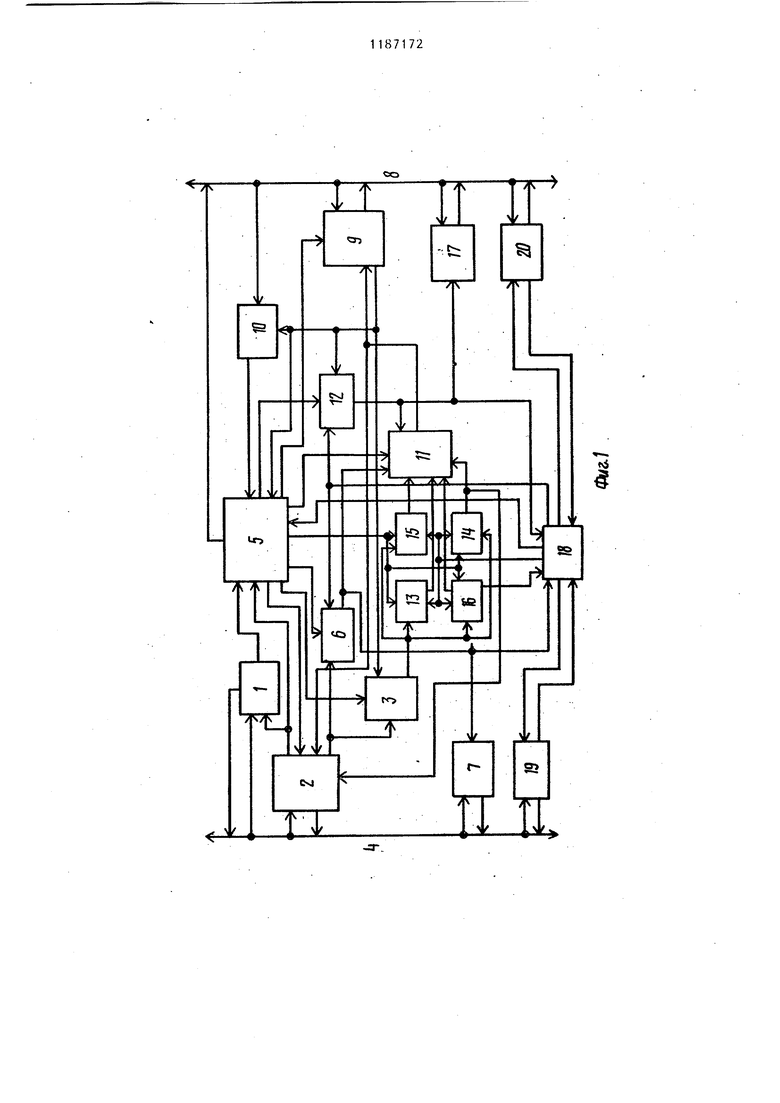

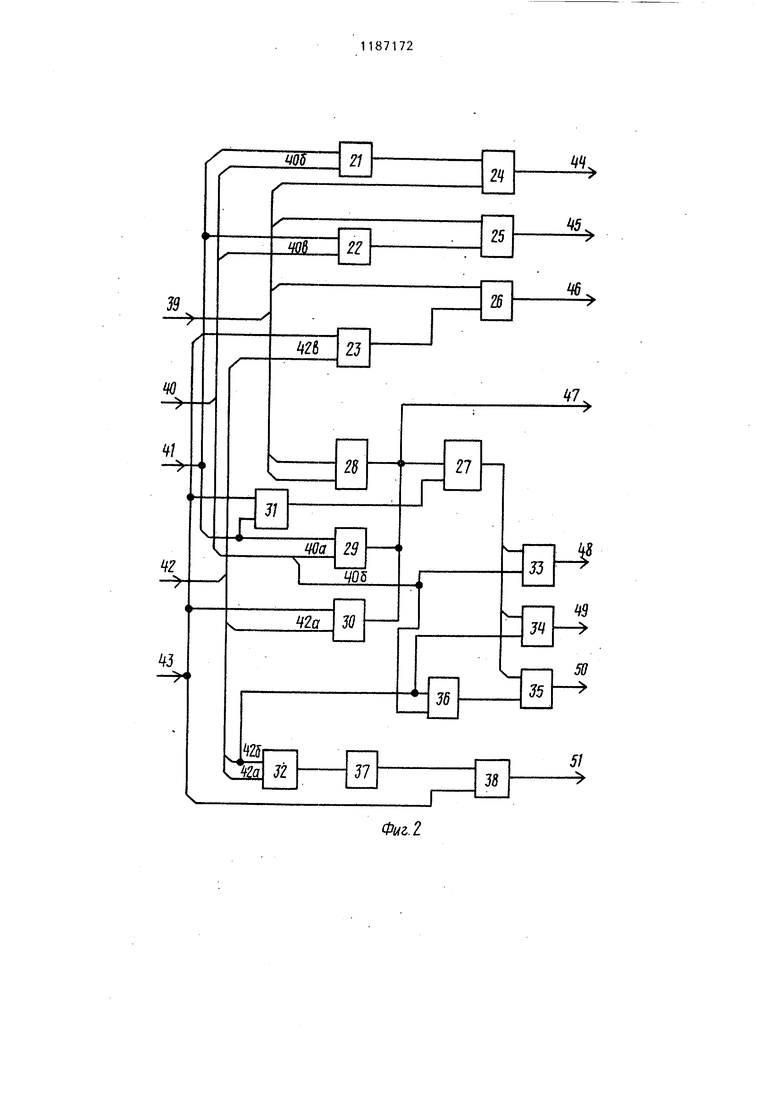

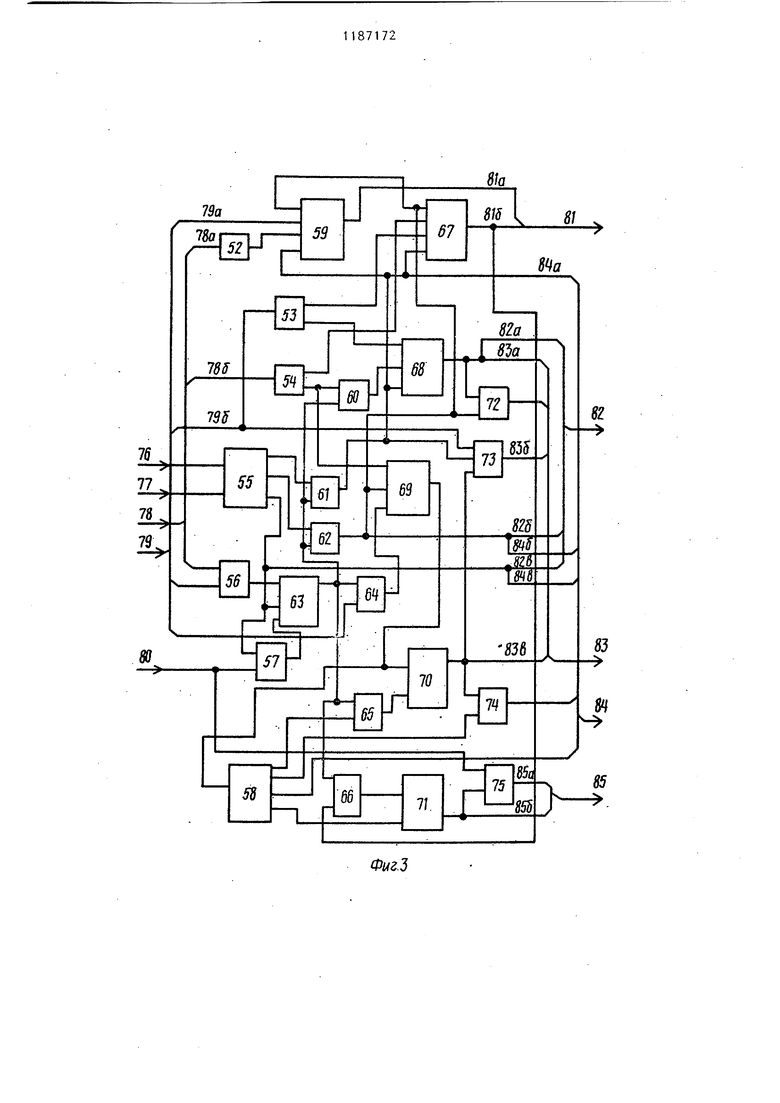

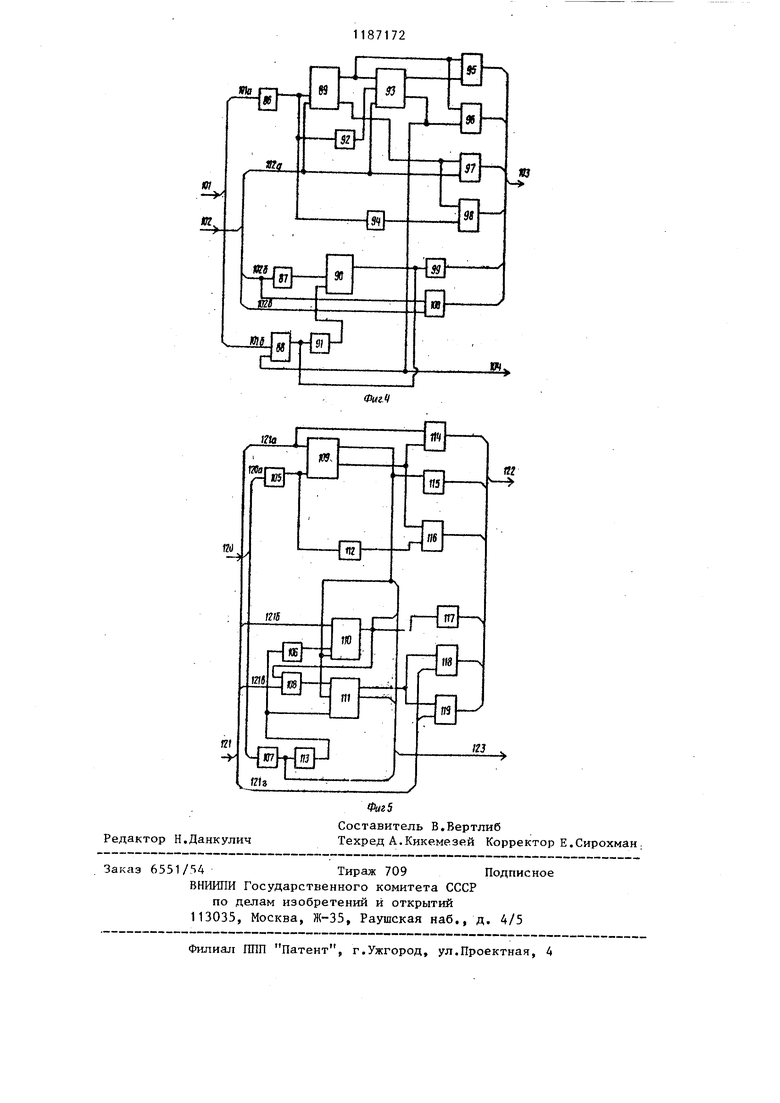

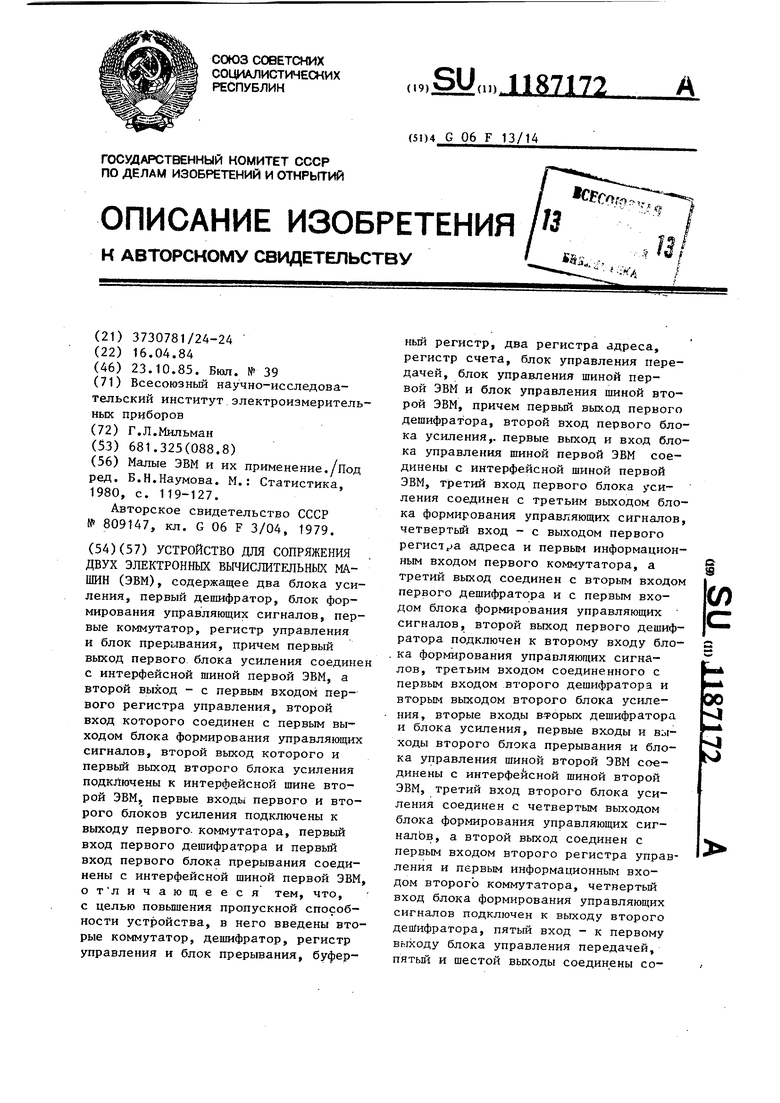

На фиг. 1 приведена структурная схема устройстваJ на фиг. 2 - функциональная схема блока формирования управляющих, сигналов J на фиг„ 3 то же, блок управления передачей; на фиг. 4 - то же, блок управления шиной первой ЭВМ; на фиг. 5 - то же, блок управления шиной второй ЭВМ.

Устройство содержит первый дешифратор 1, предназначенньй для распознавания адреса устройства при обращении к нему со стороны первой ЭВМ, первый блок 2 усиления, второй коммутатор 3, осуществляющий коммутацию данных, поступаклдих от обеих ЭВ1 на входы адресуемых регистров устройства, интерфейсную шину 4 первой ЭВМ, блок 5 формирования управляющих сигналов, служащий для управления

блоками устройства, первый регистр 6 управления, предназначенный для программного управления режимами работы устройства и контроля его состояния, со стороны первой ЭВМ, первый блок 7 прерывания, реализуюпщй процедуру прерывания программы первой ЭВМ, интерфейсную шину 8 второй ЭВМ, второй блок 9 усиления, второй дешифратор 10, служащий для распознавания адреса устройства при обращении к нему со стороны второй ЭВМ, первый коммутатор 11, подключающий выходы программно-адресуемых регистров устройства на входы блоков усиления, второй регистр 12 управления, предназначенньй для программного управления режимами работы устройства и контроля его состояния со стороны второй ЭВМ, буферньй регистр 13, используемый для хранения передаваемого слова, первьй регистр 14 адреса, служащий для хранения адреса передаваемого слова первой ЭВМ, второй регистр 15 адреса, служащий дпя хранения адреса передаваемого слова во второй ЭВМ, регистр 16 счета, служащий для хранения числа передаваемых слов, второй блок 17 прерыва3ния, реализующий процедуру прерывания программы второй ЭВМ, блок 18 управления передачей, вырабатывающий сигналы управления и синхронизации для блоков устройства в режиме внепроцессорной передачи, блоки 19 и. 20 управления шиной первой и второй ЭВМ, предназначенные для управления шинами 4 и 8 в режиме внепроцессорной передачи. Блок 5 формирования управляющих сигналов содержит (фиг. 2) первый, второй, четвертый элементы И 21-23, чётвертьй элемент ИЛИ 24, группу элементов ИЛИ 25, пятый элемент ИЛИ 26, дешифратор 27, третью, первую и вторую .группы элементов И-НЕ 2830, первый, третий элементы ИЛИ 31 и 32, третий и пятый элементы И 33 и ЗА, группу элементов И 35, второй элемент ИЛИ 36, элемент 37 задержки и элемент И-НЕ 38, пятьй, первый второй, третий и четвертый входы 39 43 блока и пятьш, третий, четвертый шестой, первый, седьмой, восьмой и второй выходы 44-51 блока. Блок 18 управления передачей содержит (фиг. 3) элемент НЕ 52, второй и первый формирователи 53 и 54 импульсов (одновибраторы), дешифратор 55, первый и шестой элементы И 56 и 57, генератор 58, первый элемент И-ИЛИ 59, третий, четвертый и пятый элементы И 60-62, третий триггер 63, второй, седьмой и восьмой элементы И 64-66, элег мент И-ШШ-НЕ 67, первьй и второй триггер 68 и 69, четвертый триггер 70, счетчик 71, девятьш элемент И 72, второй элемент И-ИЛИ 73, элемент И-НЕ 74, десятый элемент И 7 первый - пятьй входы 76-80 блока и пятьй, третий, первьй, четвертый и второй выходы 81-85 блока. Блок 19 управления шиной первой ЭВМ содержит (фиг. 4) формирователь 86 импульса (элемент И), первьй элемент 87 задержки, первьй элемент И 88, первьй и третий триггеры 89 и 90, второй элемент 91 задержки, второй элемент НЕ 92, второй триггер 93, третий элемент 94 задержки, чётвертьй, третий и первьй элементы И-НЕ 95-97, второй элемент И 98, первьй элемент НЕ 99, второй элемент И-НЕ 100, первый и второй входы 101 и 102 блока, первы и второй выходы 103 и 104 блока. 724 Блок 20 управления шиной второй ЭВМ содержит (фиг. 5) первьй, пятьй и второй элементы НЕ 105-107, чётвертьй элемент И-НЕ 108, первьй, второй и третий триггеры 109-111, первьй и второй элементы 112-113 задержки, первьй элемент И-НЕ 114, чётвертьй элемент НЕ 115, пятьй элемент ИНЕ 116, третий элемент НЕ 117, третий и второй элементы И-НЕ 118 и 119, первьй и второй входы 120 и 121 блока и первый и второй выходы 122 и 1-23 блока. Устройство работает следующим . образом. Устройство осуществляет обмен информацией между двумя разнотипными ЭВМ, одна из которых имеет интерфейс, например, типа Общая шина (ОШ), а другая - интерфейс, например, типа канала микроЭВМ Электроника-60. Любая передача информации между ЭВМ подразделяется на три этапа: подготовка, передача и окончание. Передача может подготавливаться и инициироваться любой из ЭВМ. I. Подготовка к передаче. Подготовка к передаче заключается в записи в регистры устройства исходной информации об обмене. В регистры 14 и 15 записьтаю ся начальный адрес передаваемого массива в передающей ЭВМ и начальный адрес в ЭВМприемнике, куда этот массив должен быть записан. В регистр 16 счета заносится число передаваемых слов, а в один из регистров 6 или 12 управления - код направления обмена. Исходная информация может быть записана в регистры одной или обеими ЭВМ, Рассмотрим, например, операцию записи в регистр устройства со стороны первой ЭВМ. Процессор ЭВМ выставляет на шину 4 адрес одного из регистров, данные, которые требуется записать, сигналы управления и синхронизации. Через блок 2 адрес поступает на дешифратор 1, на которьй также подается с общей шины 4 синхронизирующий сигнал. При совпадении адреса с заданным дешифратор 1 выдает сигнал выборки устройства в блок 5 и ответный синхросигнал - на общук шину 4 первой ЭВМ. Блок 5 вьфабатывает сигнал записи в регистр, адрес которого определяется младшими разрядами адресного слова, поступающего в блок 5 из блока 2. Одновременно на информационный вход выбранного регистра через блок 2 и коммутатор 3 подается записьгоаемое слово данных. Если запись происходит в регистр 6, то дан,ные поступают непосредственно с блока 2. Запись в регистры устройства второй ЭВМ производится аналогично, но в этом случае адрес устройства и дан ные поступают из канала 8 через второй блок 9 усиления и адрес распознается вторым дешифратором 10. II. Передача информации. Передача информации инициируется установкой определенных разрядов в регистрах 6 и 12 управления. Блок 18 анализирует состояние этих разрядов и при их установке вырабатывает сигналы требования передачи в блок 19 и блок 20, которые выставляют на связанные с ними шины 4 и 8 сигналы запроса на внепроцессорную передачу Далее блоки 19 и 20 осуществляют с процессорами ЭВМ обмен сигналами по захвату управления над системными шинами в соответствий с требованиями интерфейсов сопрягаемых ЭВМ. После того, как функция управления интерфейсньми шинами передача устройству блок 18 инициирует передачу первого слова. ч Рассмотрим, например, передачу из первой ЭВМ во вторую. Передача каждого слова заключается в выполнении устройством операции чтения на шине 4 первой ЭВМ по адресу, записан ному в регистре 14, и операции записи на шине 8 второй ЭВМ по .адресу, указанному в регистре 15. Операция чтения слова начинается с вьщачи адреса (ячейка памяти или регистр периферийного устройства), содержимое которого нужно передать из регистра 14 через блок 2 на шину 4 первой ЭВМ. Одновременно блок 19 выставляет на шину 4 соответствующие сигналы управления и синхронизации, принятые для интерфейса первой ЭВМ. Считьшаемое слово через блок 2 и коммутатор 3 записьгоается в буферный регистр 13. После завершения операции чтения блок 18 посьтает в блок 20 сигнал, инициирующий операцию записи. Адрес записи (ячейка памяти или регистр периферийного устройства) из регистра 15 и записываемое слово ранящееся в буферном регистре 13, через коммутатор 11 и блок 9 поступа-i т на шину 8 второй ЭВМ. Блок 20 вырабатывает необходимые для реализации операции записи интерфейсные сигналы. В процессе передачи слова 5шравление блоками 2 и 9, коммутаторами 3 и 11 осуществляется блоком 5 по импульсам синхронизации с блока 18. После передачи слова по сигналам с блока 18 происходит увеличение содержимого -регистров 14 и 15 и уменьшение содержимого регистра 16, затем инициируется передача следующего слова. Когда регистр 16 обнулится (т.е. заданное число передано), блок 18 |снимает сигнал-тредование передачи, поступающий в блоки 19 и 20. Последние в свою очередь снимают сигналы занятости интерфейсных шин 4 и 8, что означает возврат управления интерфейсами процессорам сопрягаемых ЭВМ. Техническая реализация передачи слова информации в обратном направлении осуществлена аналогично, но в начале цикла передачи устройство производит операцию чтения на шине 8 второй ЭВМ, а затем операцию записи на шине 4 первой ЭВМ. III. Окончание передачи. Завершение передачи заданного количества слов сопровождается установкой определенных разрядов в регистрах 6 и 12 управления. В свою очередь установка этих разрядов может вызвать прерывание одной или обеих ЭВМ (прерьшание каждой ЭВМ разрешается программной установкой определенного разряда в своем регистре управления). Если прерьшание разрешено, то блок 7 (17) прерывания выставляет на шину 4 (8) сигналы запроса на прерывание. Далее после обмена с процессорами ЭВМ сигналами, в соответствии с алгоритмом процедуры прерьгоания, принятым для каждого интерфейса сопрягаемых ЭВМ, выставляют ректор прерывания. Как правило, программа, обрабатьшающая прерьшание, производит считывание содержимого регистра управления, анаЛИЗ которого позволяет определить факт завершения передачи массива информации или возникшие при передаче ошибочные ситуации. II дачи начинается с установки тригге;ра 69 сигналом с выхода элемента И 62. Дальнейшая работа элементов блока происходит аналогично опи санной.Сигналом для завершения работы блока является импульс обнуления регистра 16 счета, поступающий на вход 80 (пятый вход блока). При этом через элемент И 57 происходит сброс триггера 63 и сброс триггеров 68-70 в исходное состояние. Одновременно импульс с входа 80 через элемент И 75 и выход 85 сбрасывает в регистрах 6 и 12 управления разряды запроса на передачу и устанавливает разряды Конец передачи Сброс разрядов запроса на передачу вызывает сброс сигнала на выходе дешифратора 55 и соответственно на выходах 82 rf 84 блокаi В блоке 18 предусмотрена регист рация ошибочных ситуаций, возникающих при обращении к несуществзпощим адресам на шинах ЭВМ. Схема, регист рирующая ошибки, содержит два элемента И 66 и 75 и счетчик 71. На счетный вход счетчика постоянно с генератора 58 подается тактовая час тота, а на вход сброса - импульсы с элемента И-ИЛИ-НЕ 67 (цепь 816), ко торые формирзтотся в конце каждого цикла передачи слова. Коэффициент пересчета счетчика таков, что он сбрасывается раньше, чем достигает своего переполнения. В том случае, когда происходит обращение к несуществующему адресу на шине ЭФМ устройство не получит ответный синхросигнал к блок зависнет, не закончив текущего цикла. По истечении некоторого времени, определяемого частотой генератора 58 и коэффициен том пересчета счетчика 71, на выходе последнего появится импульс переполнения, который по цепи 856 установит в регистрах 6 и 12 определенные разряды ошибки, а через элемент И 75 (цепь 85а) сбросит в них разряды запроса на передачу. Блок 19 управления шиной осущест ляет обмен интерфейсными сигналами с процессором первой ЭФМ по захвату управления над шиной 4 и формирорание сигналов синхронизации и управления для вьшолнения операций по внепроцессорной передаче данных. Блок 19 работает следующим образом (фиг. 4). В исходном состоянии, при отсутствии сигнала требования на передачу, поступающего из блока 18 (в цепи 102а - нулевой уровень), триггеры блока 89, 90 и 93 поддерживаются в нулевом состоянии. При этом, хотя бы на одном из входов элементов ИНЕ 95-97 и 100, элементов И 98 и НЕ 99, связанных по выходу с шиной ЭВМ, находится нулевой уровень и блок 19 логически отключен от шины. При поступлении с входа 102 сигнала требования на передачу . (цепь 102а) начинается цикл захвата интерфейсной шины. На выходе элемента И-НЕ 97 появляется сигнал (низкий уровень) требования на внепроцессорную передачу (в терминологии интерфейса Общая шина СМ ЭВМ-сигнал ЗЦЦ). Процессор ЭВМ, получив этот сигнал, отвечает сигналом разрешения (РПД), поступающим на вход 101 (первый вход блока) по цепи 101а. По переднему фронту сигнала РПД происходит установка тррпт.ера 89, формирование на выходе элемента И-НЕ 95 сигнала подтверяодения (ПВБ) и сброс сигнала ПД, а по заднему фронту устанавливается триггер 93 и на выходе элемента И-НЕ 96 формируется сигнал занятости шины (ЗАН). Одно- . временно сигнал с прямого выхода триггера 93 поступает через выход 104 в блок 18. На этом передача управления шиной 4 первой ЭВМ устройству завершается. При выполнении циклов передачи из блока 18 на выход 102 поступают сигналы установки адреса (цепь 1026) и код операции (цепь 102в). На выходе элемента И-НЕ 100 устанавливается управляющий сигнал (VI) определяющий вид операции: чтение или запись. Далее, с определенной задержкой, устанавливается триггер 90 и через элемент НЕ 99 на интерфейсную шину 4 посылается сигнал синхронизации (СХЗ). Получив этот сигнал, устройство, к которому происходит обращение, вьтолнит требуемую операцию и выставит ответный сигнал синхронизации (СХИ), который, поступив по входу 101 (цепь 1016), вызывает через определенную задержку сброс триггера 90 и снятие сигнала СХЗ. При операциях чтения с шины 4 по 13 .1 сигналу СХИ с выхода элемента И 88, блок 18 формирует сигнал записи в буферный регистр 13, а сброс триггера 90 означает для блока 18 конец цикла обращения к шине, После завершения передачи блок 18 снимает сигнал требования (в цепи 102а - нулевой уровень), что сбрасывает триггеры блока в исходное состо яние. При этом сигнал ЗАН снимается и управление шиной возвращается процессору ЭВМ. Блок 20 управления шиной осуществляет обмен интерфейсными сигналами С процессором второй ЭВМ по захвату управления над шиной 8, формирова ние сигналов управления и синхрониза ции для вьтолнения операций по внепроцессорной передаче данных и работает следующим образом (фиг. 5). Блок включает в себя схему захвата управления, состоящую из .триггера 109 и элементов НЕ 105 и 115,. И-НЕ 114, 116, элемента 112 задержки. В исходном состоянии на выходе (прямом) триггера 109 находится логический ноль, а на инверсном выходе - логическая единица. При появлении в цепи 121а сигнала требования с блока 18, с вькода элемента ИНЕ 114 и выхода 122 на шину 8 поступает сигнал требования на внепроцессорную передачу (в терминологии интерфейса микро-ЭВМ Электроника-60 - сигнал ТПД). Процессор ЭВМ, получив этот сигнал, устанавливает сигнал предоставления (ППД), поступающий по цепи 120а, с входа 120 через элемент ПТ 105 на вход триггера 109. Триггер устанавливается в единичное состояние, при этом снимается сигнал требования ТПД и на выходе элемента НЕ 115 устанавливается сигнал подтверждения (ПВ). Также единичным сигналом с триггера 109 разрешается работа триггеров 110 и 111 и информируется блок 18 о пе2.14 редаче управления над шиной второй ЭВМ устройству. При выполнении устройством цикла обращения к шине 8, после установки адреса на шине, тактовым импульсом с входа 121 по цепи 1216 происходит установка триггера 110 и формирование элементом НЕ 117 сигнала синхронизации (СИЛ). Следующим тактовым импульсом по цепи 121в устанавливается триггер 111, а на выходах элементов И-НЕ 118 и 119 появляются сигналы Ввод или Вывод, в зависимости от кода операции, поступившего по цепи 121г. Получив один из этих сигналов, устройство, к которому происходит обращение, выполняет требуемую операцию и выставляет ответньй синхросигнал (СИП), по переднему фронту которого с определенной задержкой, происходит сброс триггера Ill и снятие сигнала Ввод или Вывод, а по заднему фронту сбрасывается триггер 110 и сигнал СИЛ. Блок 20 посьшает на выход 123 сигнал СИП, по которому в цикле чтения с. шины блок 18 формирует сигнал записи в буферный регистр 13 и сигнал СИЛ, по окончанию которого блок 18 завершает цикл обращения к шине второй ЭВМ. После завершения передачи блок 18 снимает сигнал требования (в цепи 121а - нулевой уровень), что вызывает сброс триггеров блока в исходное состояние. При этом, сигнал ПВ снимается и управление шиной возвращается процессору ЭВМ. Таким образом, предпагаемое устройство обеспечивает реализацию внепроцессорной передачи данных между сопрягаемыми ЭВМ, что позволяет по сравнению с известным устройством значительно увеличить пропускную способность устройства сопряжения, приближая его к пропускной способности интерфейсов сопрягае- . мых ЭВМ.

| Малые ЭВМ и их применение./Под ред | |||

| Б.Н.Наумова | |||

| М.: Статистика, 1980, с | |||

| Способ получения камфоры | 1921 |

|

SU119A1 |

| Устройство для сопряжения двух элект-РОННыХ ВычиСлиТЕльНыХ МАшиН | 1979 |

|

SU809147A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-23—Публикация

1984-04-16—Подача