ю сд

00

со ас

Изобретение относится к вычислительной технике и технике связи и может быть использовано в системах цифровой обработки стационарных случайных процессов в качестве модулятора для цифровых фильтров и корреляторов, работающих в смешанном фор- йате.

Под форматом понимают способ пред фтавления величин, подаваемых на йходы устройств цифровой обработки ;;игналов, В смешанном формате работают устройства цифровой обработки фигналов, в частности цифровые фильтры, в которых используются разные форматы для входного сигнала и импульсной характеристики, или корре- шторы в которых одна из входных беличин представлена при помощи им- рульсно-кодовой модуляции (ИКМ), а вторая в формате многоуровневой дельца-модуляции или дифференциальной импульсно-кодовой модуляции (МДМ или

дикм) и

; Цель изобретения - повышение раз- |)ешаюш;ей способности и расширение рбласти применения за счет формиро- рания вьгходных сигналов в смешанном формате.

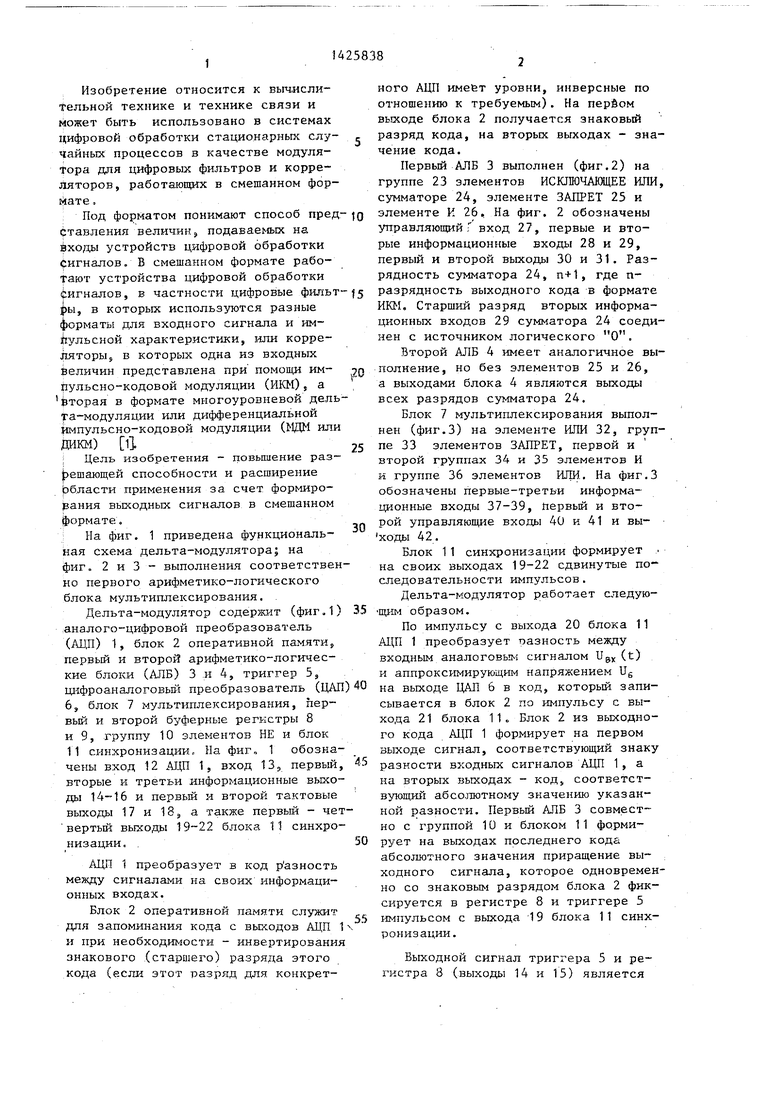

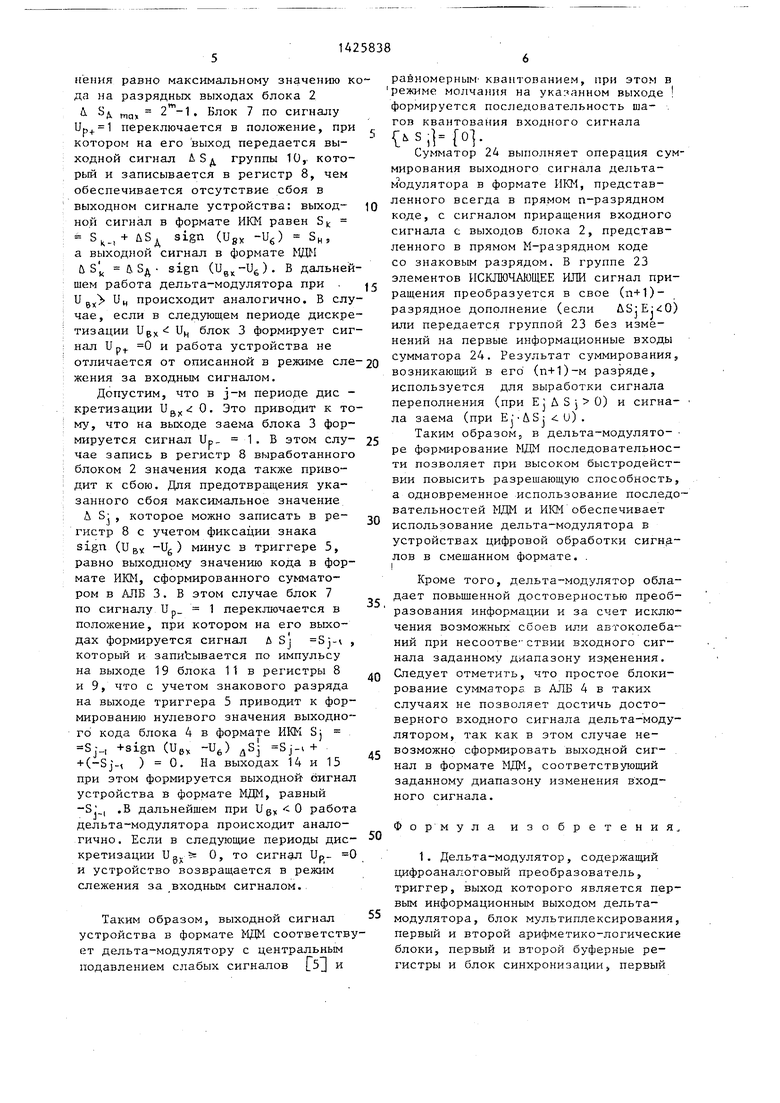

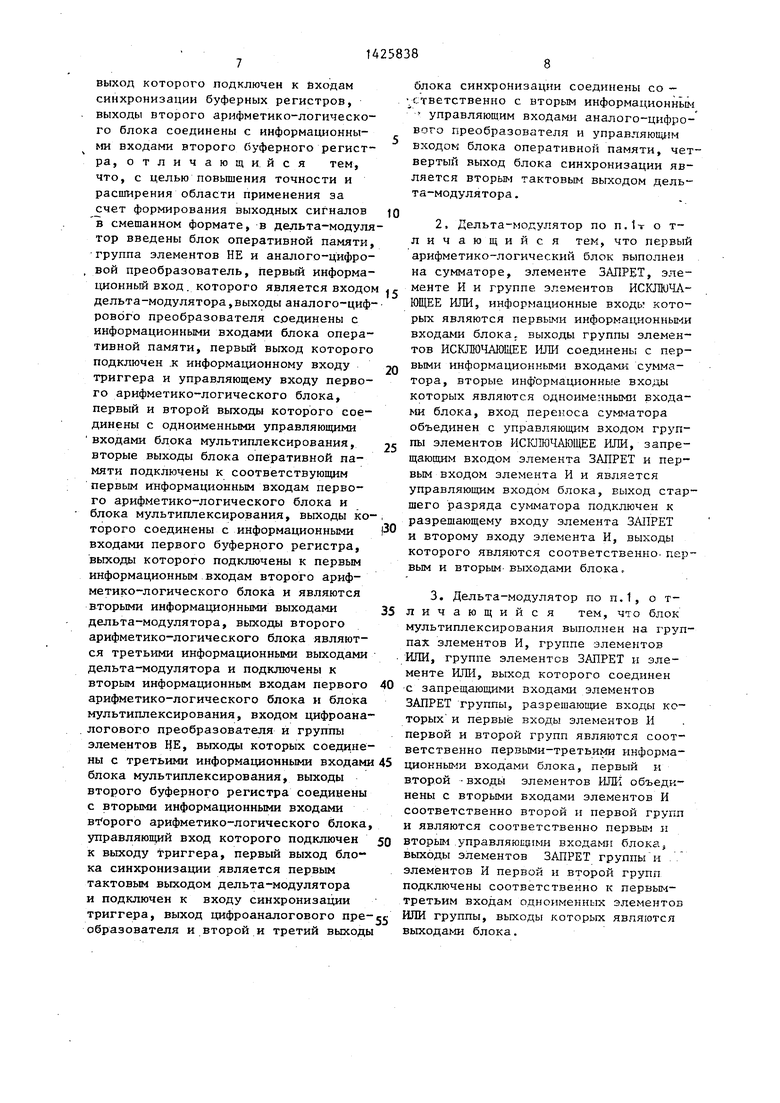

; На фиг. 1 приведена функциональная схема дельта-модулятора; на фиг. 2 и 3 - выполнения соответственно первого арифметико-логического блока мультиплексирования, .

Дельта-модулятор содержит (фиг.1) .аналого-цифровой преобразователь (AU,n) 1, блок 2 оперативной памяти первьш и второй арифметико-логические блоки (АЛБ) 3 ,и 4, триггер 5, щ фроаналоговьш преобразователь (ЦАП 6, блок 7 мультиплексирования, первый и второй буферные регистры 8 и 9, группу 10 элементов НЕ и блок 11 синхронизации. На фиг„ 1 обозначены вход 12 АЦП 1, вход 13, первый, вторые и третьи информационные выхода 14-16 и первый и второй тактовые выходы 17 и 18, а также первый - чет вертый выходы 19-22 блока 11 синхронизации. .

АЦП 1 преобразует в код р азность между сигналами на своих информационных входах.

Блок 2 оперативной памяти служит для запоминания кода с выходов АЦП 1 и при необходимости - инвертирования знакового .(старшего) разряда этого кода (если этот разряд для конкретного АЦП имеет уровни, инверсные по отношению к требуемым). На пербом вьжоде блока 2 получается знаковый с разряд кода, на вторьсх; выходах - значение кода.

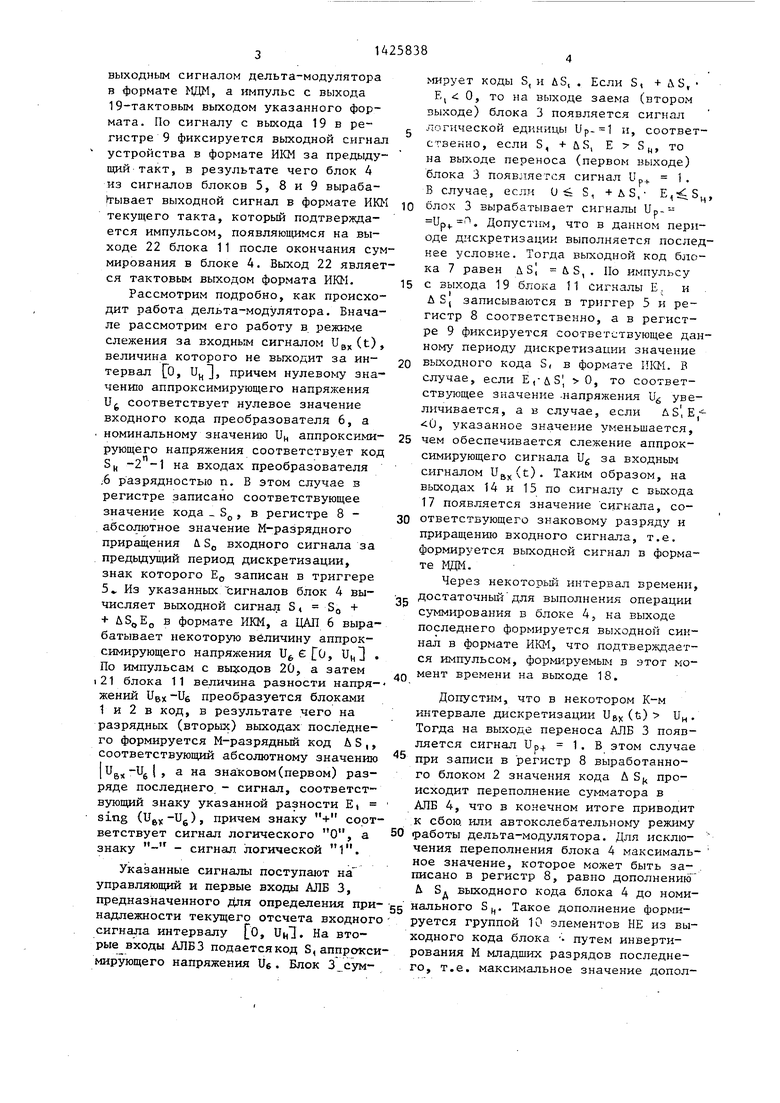

Первый АЛБ 3 выполнен (фиг.2) на группе 23 элементов ИСКЛОЧАЩЕЕ ИЛИ, сумматоре 24, элементе ЗАПРЕТ 25 и

0 элементе К 26, На фиг. 2 обозначены управляющий Г вход 27, первые и вторые информационные входы 28 и 29, первый и второй выходы 30 и 31. Разрядность сумматора 24, п+1, где п5 разрядность выходного кода в формате ИКМ. Старший разряд вторых информационных входов 29 сумматора 24 соединен с источником логического О.

Второй АЛБ 4 имеет аналогичное выQ полнение, но без элементов 25 и 26,

а выходами блока 4 являются выходы всех разрядов сумматора 24.

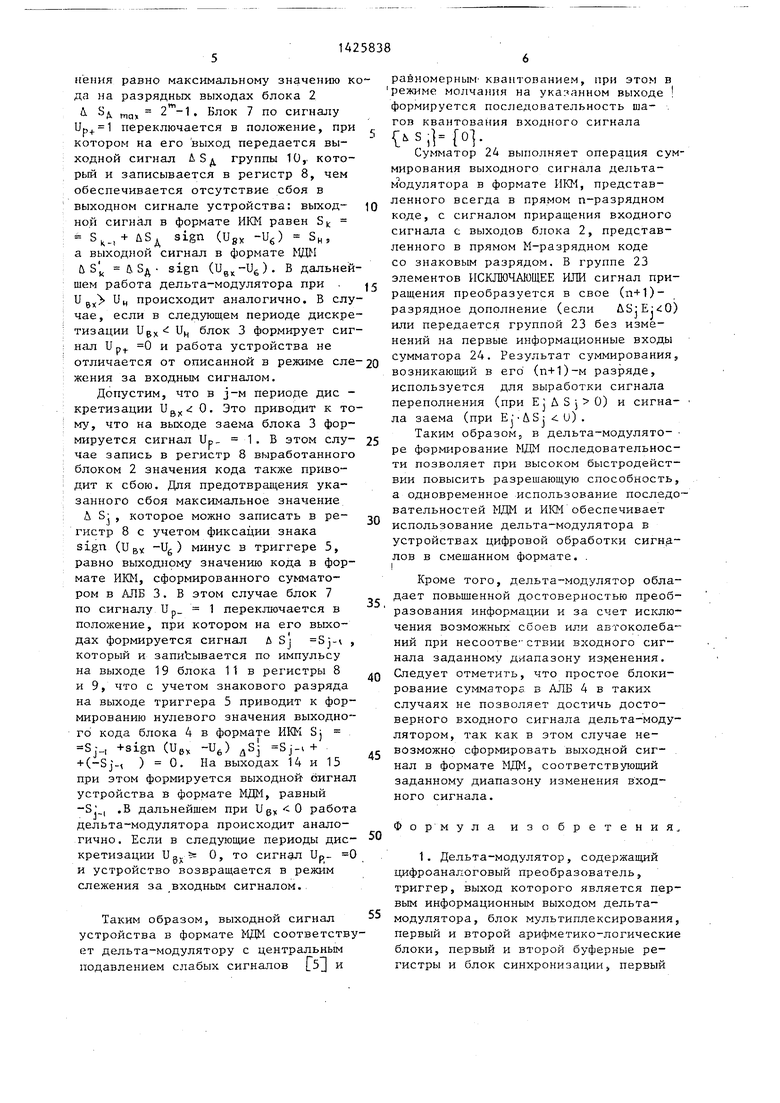

Блок 7 мультиплексирования выполнен (фиг.З) на элементе ИЛИ 32, груп5 пе 33 элементов ЗАПРЕТ, первой и второй группах 34 и 35 элементов И и группе 36 элементов ИЛИ.. На фиг.З обозначены первые-третьи информационные входы 37-39, Первьй и второй управляющие входы 40 и 41 и вы- ходы 42.

Блок 11 синхронизации формирует . на своих выходах 19-22 сдвинутые последовательности импульсов.

Дельта-модулятор работает следую5 щим образом.

По импульсу с 20 блока 11 АЦП 1 преобразует пазность между входным аналоговыь сигналом U (t) и аппроксимирующим напряжением Ug на выходе ЦАП 6 в код, который записывается в блок 2 по импульсу с выхода 21 блока 11,, Блок 2 из выходного кода АЦП 1 формирует на первом выходе сигнал, соответствующий знаку разности входных сигналов АЦП 1, а на вторых выходах - код, соответствующий абсо.лютному значению указанной разности. Первый АЛБ 3 совместно с группой 10 и блоком 11 форми0 рует на выходах последнего кода

абсолютного значения приращение выходного сигнала, которое одновременно со знаковым разрядом блока 2 фиксируется в регистре 8 и триггере 5

5 импульсом с выхода 19 блока 11 синхронизации.

Выходной сигнал триггера 5 и регистра 8 (выходы 14 и 15) является

0

0

5

выходным сигналом дельта-модулятора в формате МДМ, а импульс с выхода 19-тактовым выходом указанного формата. По сигналу с выхода 19 в регистре 9 фиксируется выходной сигнал устройства в формате ИКМ за предыдущий такт, в результате чего блок 4 из сигналов блоков 5, 8 и 9 вырабатывает выходной сигнал в формате ИКМ текущего такта, который подтверждается импульсом, появляющимся на выходе 22 блока 11 после окончания суммирования в блоке 4. Выход 22 является тактовым выходом формата ИКМ.

Рассмотрим подробно, как происходит работа дельта-модулятора. Вначале рассмотрим его работу в режиме слежения за входным сигналом ), величина которого не выходит за интервал о, , причем нулевому значению аппроксимирующего напряжения и соответствует нулевое значение входного кода преобразователя 6, а

номинальному значению UK аппроксимирующего напряжения соответствует код 5ц -2 -1 на входах преобразователя .6 разрядностью п. В этом случае в регистре записано соответствующее значение кода S, в регистре В - абсолютное значение М-разрядного приращения US входного сигнала за предьщуЕ ий период дискретизации, знак которого Eg записан в триггере 5 Из указанных сигналов блок 4 вычисляет выходной сигнал 84 Sj, + + uSgEj, в формате ИКМ, а ЦАП 6 вырабатывает некоторую величину аппроксимирующего напряжения U, 0, Цц 1 . По импульсам с выходов 20, а затем

21 блока 11 величина разности напря- жений преобразуется блоками 1 и 2 в код, в результате чего на разрядных (вторых) выходах последнего формируется М-разрядньй код AS,, соответствующий абсолютному значению , а на знаковом (первом) разряде последнего - сигнал, соответствующий знаку указанной разности Е( sing (Ugy-Ug), причем знаку + соответствует сигнал логического О, а знаку - - сигнал логической 1.

Указанные сигналы поступают на управляющий и первые входы АЛБ 3, предназначенного для определения принадлежности текущего отсчета входного сигнала интервалу О, Unl. На вторые входы АЛБЗ подаетсякод S,аппроксимирующего напряжения Us. Блок 3 суммирует коды S, и AS, . Если S, + AS, Е, ; О, то на выходе заема (втором выходе) блока 3 появляется сигнал

g логической единицы и, соответ- ствекно, если S, +US, , то на выходе переноса (первом выходе) блока 3 появляется сигнал Up.,. 1. В случае, если 0 S, +Л5,- E,S,

0 блок 3 вырабатывает сигналы . -. Допустим, что в данном периоде дискретизации выполняется последнее условие. Тогда выходной код блока 7 равен ДВ) & S, . Но импульсу

5 с выхода 19 блока 11 сигналы Е., и . Д S, записываются в триггер 5 и регистр 8 соответственно, а в регистре 9 фиксируется соответствующее данному периоду дискретизации значение

0 выходного кода S, в формате ИЮ-. В случае, если E,-&S| О, то соответствующее значение -напряжения U увеличивается, а в случае, если ДВ , Е, , указанное значение уменьшается,

5 чем обеспечивается слежение аппроксимирующего сигнала Ug за входным сигналом UB(t). Таким образом, на выходах 14 и 15 по сигналу с выхода 17 появляется значение сигнала, со0 ответствующего знаковому разряду и приращению входного сигнала, т.е. формируется выходной сигнал в формате МЩ,

Через некоторый интервал времени,

g достаточный для выполнения операции суммирования в блоке 4, на выходе последнего формируется выходной син- нал в формате ИКМ, что подтверждается импульсом, формируемым в этот моQ мент времени на выходе 18.

Допустим, что в некотором К-м интервале дискретизации Ug (t) U,. Тогда на выходе переноса АЛБ 3 появляется сигнал Uo-f 1. В этом случае

при записи в регистр 8 выработанного блоком 2 значения кода Д Sj происходит переполнение сумматора в АЛБ 4, что в конечном итоге приводит к сбою, или автоколебательному режиму

0 «работы дельта-модулятора. Для исключения переполнения блока 4 максималь- ное значение, которое может быть записано в регистр 8, равно дополнению Л S. выходного кода блока 4 до номи5 нального S. Такое дополнение формируется группой 10 элементов НЕ из выходного кода блока путем инвертирования М младших разрядов последнего, т.е. максимальное значение допелнения равно максимальному значению кода на разрядных выходах блока 2 Л та , Блок 7 по сигналу

max переключается

в положение, при

котором на его выход передается выходной сигнал Л5д группы 10,, который и записывается в регистр 8, чем обеспечивается отсутствие сбоя в выходном сигнале устройства: выходной сигнал в формате ИКМ равен Sic S, + йВд sign (Ugx -Uj SH, a выходной сигнал в формате МДМ U S U Зд sign (), В дальнейшем работа дельта-модулятора при и g и ц происходит аналогично. В случае, если в следующем периоде дискретизации и блок 3 формирует сигнал Up 0 и работа устройства не отличается от описанной в режиме ележения за входньм сигналом.

Допустим, что в J-M периоде дис - кретизации 0. Это приводит к тому, что на выходе заема блока 3 формируется сигнал Up. 1. Б этом случае запись в регистр 8 выработанного блоком 2 значения кода также приводит к сбою. Для предотвращения указанного сбоя максимальное значение

J-

Д Sj , которое можно записать в регистр 8 с учетом фиксации знака sign (иву Ug) минус в триггере 5, равно выходному значению кода в формате ИКМ, сформированного сумматором в АЛБ 3. В этом случае блок 7 по сигналу ир 1 переключается в положение, при котором на его выходах формируется сигнал Л Si Sj- , который и запиЬывается по импульсу на выходе 19 блока 11 в регистры 8 и 9, что с учетом знакового разряда на выходе триггера 5 приводит к формированию нулевого значения выходного кода блока 4 в формате ИКМ Sj , Sj, +sign (Ugx -Uj Sj -Sj-. + + (-Sj-, ) 0. Ha выходах 14 и 15 при этом формируется выходной сжгнал устройства в формате МДМ, равный -S I ,В дальнейшем при Ug, О работа дельта-модулятора происходит аналогично. Если в следующие периоды дискретизации Ug.. О, то сигнчШ Up- 0 и устройство возвращается в режим слежения за входным сигналом.,

Таким образом, выходной сигнал устройства в формате МДМ соответствует дельта-модулятору с центральным подавлением слабых сигналов i.5j и

0

5

0

равномерным- квантованием, при этом в режиме молчания на указанном выходе формируется последовательность ша- . гов квантования входного сигнала s,o.

Сумматор 2i выполняет операция суммирования выходного сигнала дельта- мЪдулятора в формате ИКМ, представленного всегда в прямом п-разрядном

5

0

5

0

5

коде, с сигналом приращения входного сигнала с выходов блока 2, представленного в прямом М-разрядном коде со знаковым разрядом. В группе 23 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ сигнал приращения преобразуется в свое ()- разрядное дополнение (если USjEj iO) или передается группой 23 без изменений на первые информационные входы сумматора 24. Результат суммирования, возникающий в его (п+1)-м разряде, используется для выработки сигнала переполнения (при Еj Д S j 0) и сигна- ла заема (при E/ USj-iU).

Таким образом, в дельта-модулято- - ре формирование МДМ последовательности позволяет при высоком быстродействии повысить разрешающую способность, а одновременное использование последовательностей МДМ и ИКМ обеспечивает использование дельта-модулятора в устройствах цифровой обработки сигналов в смешанном формате. .

Кроме того, дельта-модулятор обладает повышенной достоверностью преобразования информации и за счет исключения возможных сбоев или автоколебаний при несоотвв ствии входного сигнала заданному диапазону изменения. Следует отметить, что простое блокирование сумматора в АЛБ 4 в таких случаях не позволяет достичь достоверного входного сигнала дельта-модулятором, так как в этом случае невозможно сформировать выходной сиг- , нал в формате МДМ, соответствующий заданному диапазону изменения входного сигнала.

50

Формула

изо

р е т е н и я.

1. Дельта-модулятор, содержащий цифроаналоговый преобразователь, триггер, выход которого является первым информационным выходом дельта- модулятора, блок мультиплексирования, первый и второй арифметико-логические блоки, первый и второй буферные регистры и блок синхронизации, первый

выход которого подключен к йходам синхронизации буферных регистров, выходы второго арифметико-логического блока соединены с информационными входами второго буферного регистра, отличающийся тем, что, с целью повышения точности и расширения области применения за счет формирования выходных сигналов д в смешанном формате, в дельта-модулятор введены блок оперативной памяти, группа элементов НЕ и аналого-цифровой преобразователь, первый информационный вход . которого является входом е дельта-модулятора,выходы аналого-цифрового преобразователя соединены с информационными входами блока оперативной памяти, первьш выход которого подключен .к информационному входу 20 триггера и управляющему входу первого арифметико-логического блока, первый и второй выходы которого соединены с одноименными управляющими

входами блока мультиплексирования, 25 вторые выходы блока оперативной памяти подключены к соответствующим первым информационным входам первого арифметико-логического блока и блока мультиплексирования, выходы ко-, торого соединены с информационными |30 входами первого буферного регистра, выходы которого подключены к первым информационным входам второго арифметико-логического блока и являются вторыми информационными выходами 35 дельта-модулятора, выходы второго арифметико-логического блока являются третьими информационными выходами дельта-модулятора и подключены к вторым информационным входам первого 40 арифметико-логического блока и блока мультиплексирования, входом цифроаналогового преобразователя и группы элементов НЕ, выходы которых соединены с третьими информахщонными входами 45 блока мультиплексирования, выходы второго буферного регистра соединены с вторыми информационными входами вт орого арифметико-логического блока, управляющий вход которого подключен 50 к выходу триггера, первый выход блока синхронизации является первым тактовым выходом дельта-модулятора и подключен к входу синхронизации триггера, выход цифроаналогового пре- образователя и второй и третий выходы

блока синхронизации соединены со - ,стветственно с вторым информационней управляющим входами аналого-цифрового гфеобразователя и управляющим входом блока оперативной памяти, четвертый выход блока синхронизации является вторым тактовым выходом дельта-модулятора .

2,Дельта-модулятор по п.1т о т- личающийся тем, что первый арифметико-логический блок выполнен на сумматоре, элементе ЗАПРЕТ, элементе И и группе элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, информационные входы которых являются первыми информационными входами блока, выходы группы элементов ИСКЛЮЧАЮЩЕЕ КПК соединены с первыми информационными входами сумматора, вторые инф ормационкые входы которых являются одноименными входами блока, вход перекоса сумматора объединен с управляющим входом группы элементов ИСКПЮЧАЮ1ДЕЕ ИЛИ, запрещающим входом элемента ЗАПРЕТ и первым входом элемента И и является управляющим входом блока, выход старшего разряда сумматора подключен к разрешающему входу элемента ЗАПРЕТ

и второму входу элемента И, выходы которого являются соответственно.первым и вторым- выходами блока.

3.Дельта-модулятор по п.1, о т- личающийся тем, что блок мультиплексирования выполнен на группах элементов И, группе элементов ИЛИ, группе элементов ЗАПРЕТ и элементе ИЛИ, выход которого соединен

-с запрещающими входами элементов ЗАПРЕТ труппы, разрешающие входы которых и первые входы элементов И первой и второй групп являются соответственно первыми-третьими информационными входами блока, первый и второй - входы элементов ИШ объединены с вторыми входами элементов И соответственно второй я первой групп и являются соответственно первым я вторым .управляющими входами блокаj выходы элементов ЗАПРЕТ группы и элементов И первой и второй групп подключены соответственно к первым- третьим входам одноименных элементов ИЛИ группы, выходы которых являются выходами блока.

Ф(е.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1987 |

|

SU1494210A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1989 |

|

SU1661969A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1989 |

|

SU1661968A1 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| Цифровой фильтр | 1987 |

|

SU1425840A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1481893A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Цифровой фильтр с симметричной импульсной характеристикой | 1988 |

|

SU1589384A1 |

| Дельта-модулятор | 1988 |

|

SU1543547A1 |

Изобретение относится к вычислительной технике и технике связи. Использование изобретения в системах цифровой обработки случайных процессов позволяет повысить разрешающую ;способность И расширнть область применения за счет формирования выходных сигналов в смешанном.формате. Дельта- модулятор содержит арифметико-логические блоки 3,4, триггер 5, цифроана- логовый преобразователь 6, блок 7 мультиплексирования, буферные регистры 8,9 и блок 11 синхронизации. Благодаря введению аналого-цифрового преобразователя 1, блока 2 оператив- g ной памяти и группы 10 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ в дельта-модуляторе обеспечивается формирование выходных сигналов как в формате импульсно- кодовой модуляции, так и в формате многоуровневой дельта-модуляции. 2 3. п. ф-лы J 3 ил. (Л

Редактор А.Ворович

Составитель О.Ревинский

Трхред Л.Сердгокова Корректор С.Черни

Заказ 4783/55

Тираж 928

ВНИ-ШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Фиг.д

Подписное

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Доклады АН УССР, сер.А, 1983, № 4, с | |||

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Дельта-модулятор | 1983 |

|

SU1112552A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 1149411, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Авторское свидетельство СССР по заявке № 4047426/24,кл.Н 03 МЗ/02, 1986., 5 | |||

| Харатишвили Н.Г | |||

| Дифференциальная импульсно-кодовая модуляция, М.: Радно и связь, 1982, с.24, рис.2.16 | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР по заявке № 4101636/24,кл.Н 03 МЗ/02, 1986. | |||

Авторы

Даты

1988-09-23—Публикация

1987-01-12—Подача