Изобретение относится к технике электросвязи и может использоваться при построении многоканальных систем связи.

Известно устройство адаптивной импульсно-кодовой модуляции [1] (авт. св. N 520723, МКИ H 04 J 3/00 от 1974 г.), содержащее n-разрядный аналого-цифровой преобразователь, преобразователь параллельного кода в последовательный, регистры сдвига и переключатели. Данное устройство используется для уменьшения числа разрядов в кодовых комбинациях на выходе кодера. Достоинством устройства является снижение скорости передачи на выходе кодера, а соответственно увеличение пропускной способности канала. Однако устройство имеет низкую помехоустойчивость и допускает пропадание части информации дополнительных каналов.

Известна также цифровая система передачи телефонных каналов модуляции [2] (авт. св. N 1418922, МКИ H 04 J 33/00 от 1987 г.), содержащее кодер, декодер, измеритель мощности, схему совпадения, делитель, решающую схему и многоканальный ключ. Достоинством устройства является высокое качество обнаружения сигнала на фоне помех типа акустического шума и шума обратного разговора. Однако в устройстве не учитываются индивидуальные требования к задержке и точности передаваемой информации.

Наиболее близким по своей сущности к заявляемому устройству является устройство статистического уплотнения сигналов, описанное в авт. св. СССР N 575781, МКИ H 04 J 3/00 от 1975 г. [3]. Ближайший аналог (прототип) содержит блок управления, преобразователь параллельного кода в последовательный, блок объединения, М аналого-цифровых преобразователей, а также МхN блоков задержки, каждый из которых включает последовательно соединенные блок анализа, блок памяти и блок коммутации, причем М≥3, М≥4. Управляющие входы блоков задержки подключены к соответствующим управляющим выходам блока управления, а их информационные выходы - к соответствующим информационным входам блока преобразования параллельного кода в последовательный. Сигнальные выходы блоков задержки подключены к соответствующим сигнальным входам блока управления. Информационный вход каждого i-го блока задержки, где i=1,2,.., N, принадлежащего j-й группе блоков задержки, где j=1,2,.., М, подключен к соответствующему i-му выходу, j-го блока аналого-цифрового преобразования. Сигнальный и информационный входы блока объединения подключены соответственно к сигнальному выходу блока управления и выходу блика преобразования параллельного кода в последовательный. Выход блока объединения является выходом устройства, а входы блоков аналого-цифрового преобразования являются входами устройства.

Устройство использует метод блочной импульсно-кодовой модуляции (БИКМ) для передачи речи [4,5]. Этот метод относится к методам кодирования с переменной длиной кодового слова и позволяет использовать наряду со статистикой пауз статистику динамических уровней. По сравнению с описанными аналогами устройство обеспечивает относительно устойчивую работу при перегрузках системы, связанных с одновременным поступлением сигналов на все входы устройства.

Однако устройство-прототип имеет недостатки:

наличие неустранимых искажений во всех каналах (при перегрузке системы младшие разряды теряются), так как считывание разрядов происходит от старших разрядов всех каналов к младшим;

узкую область применения, так как устройство-прототип предназначено для передачи только однородной речевой информации и не позволяет учитывать различия индивидуальных требований к допустимым искажениям и задержке передаваемых сигналов от различных аналоговых источников.

Целью изобретения является разработка устройства статистического уплотнения с временным разделением каналов, позволяющего уменьшить или полностью исключить искажения в отдельных каналах, а также расширить область применения за счет учета индивидуальных требований к допустимым искажениям и задержке различных аналоговых сигналов.

Поставленная цель достигается тем, что в известное устройство, содержащее блоки управления, преобразования параллельного кода в последовательный, объединения, М блоков аналого-цифрового преобразования и М групп по N в каждой основных блоков задержки, где М≥3, М≥4, причем управляющие входы основных блоков задержки подключены к соответствующим управляющим выходам блока управления, а их информационные выходы - к соответствующим информационным входам блока преобразования параллельного кода в последовательный, сигнальные выходы основных блоков задержки подключены к соответствующим сигнальным входам блока управления, информационный вход каждого i-го основного блока задержки, где i=1,2,..,N, принадлежащего j-й группе блоков задержки, где j= 1,2,..,М, подключен к соответствующему i-му выходу j-го блока аналого-цифрового преобразования, сигнальный и информационный входы блока объединения подключены соответственно к сигнальному выходу блока управления и выходу блока преобразования параллельного кода в последовательный, выход блока объединения является выходом устройства, а входы блоков аналого-цифрового преобразования являются входами устройства, дополнительно введены М•N (К-1) блоков коммутации и М•N (К-1) дополнительных блоков задержки, где К≥2. Управляющие входы дополнительных блоков задержки подключены к соответствующим дополнительным управляющим выходам блока управления, а их информационные выходы - к соответствующим дополнительным входам блока преобразования параллельного кода в последовательный. Сигнальные выходы дополнительных блоков задержки подключены к соответствующим дополнительным сигнальным входам блока управления. Информационный вход каждого z-го дополнительного блока задержки, входящего в i-ю подгруппу j-й группы блоков задержки, где z=1,2,.., (К-1), подключен к выходу z-го блока коммутации. Информационный вход каждого z-го блока коммутации, начиная с z=2, подключен к дополнительному информационному выходу (z-1)-го дополнительного блока задержки. Информационный вход первого (z= 1) блока коммутации подключен к дополнительному информационному выходу соответствующего i-го основного блока задержки, принадлежащего j-й группе блоков задержки. Коммутирующие входы всех блоков коммутации подключены к соответствующим коммутирующим выходам блока управления.

Основной блок задержки состоит из коммутатора, блока памяти, блока анализа. Информационный выход блока анализа подключен ко входу блока памяти, выход которого подключен к информационному входу коммутатора и одновременно является дополнительным информационным выходом основного блока задержки. Сигнальный выход и вход блока анализа являются соответственно сигнальным выходом и информационным входом основного блока задержки. Выход и управляющий вход коммутатора являются соответственно информационным выходом и управляющим входом основного блока задержки.

Дополнительный блок задержки состоит из коммутатора, блока памяти, блока анализа. Информационный выход блока анализа подключен к входу блока памяти, выход которого подключен к информационному входу коммутатора, управляющий вход и выход которого являются соответственно управляющим входом и информационным выходом дополнительного блока задержки. Сигнальный выход и вход блока анализа являются соответственно сигнальным выходом и информационным входом дополнительного блока задержки. В каждом z-ом дополнительном блоке задержки при z = 1,2,.., (К-2), входящем в каждую из подгрупп блоков задержки, выход блока памяти одновременно является дополнительным информационным выходом дополнительного блока задержки.

Благодаря указанной совокупности признаков устранение или уменьшение потерь в отдельных каналах, а также расширение области применения устройства обеспечивается за счет дополнительной задержки части разрядов цифровых отсчетов в каналах, допускающих такую задержку и считывания различных разрядов в различных каналах в порядке снижения требуемой точности их восстановления.

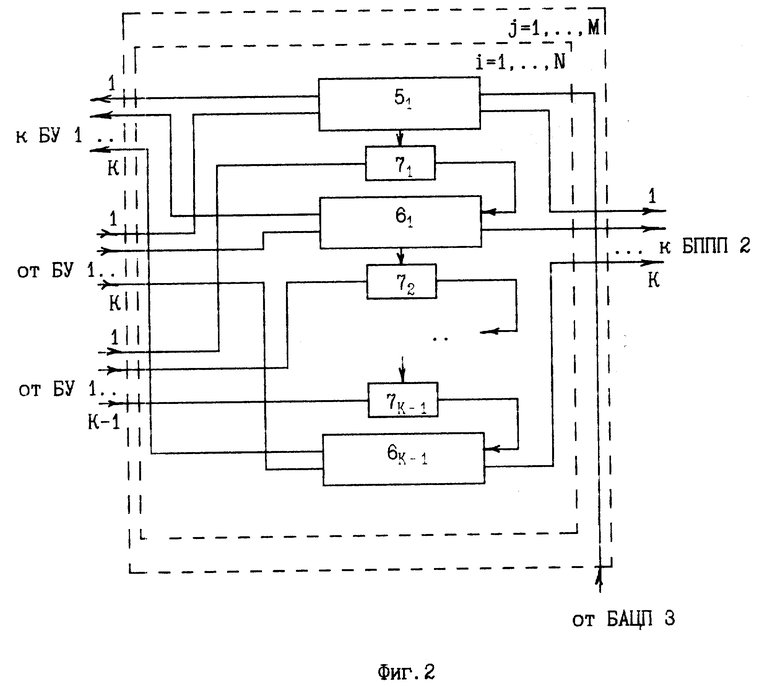

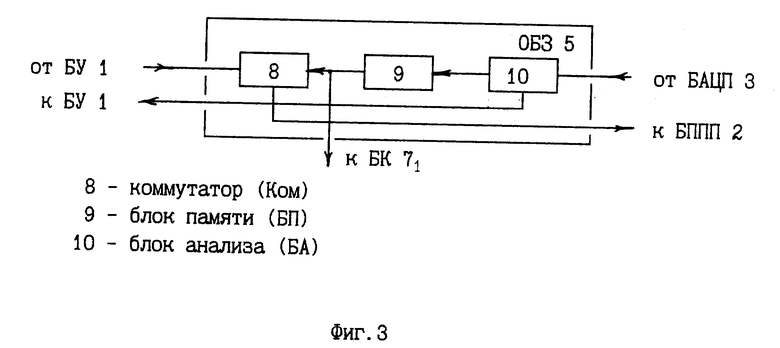

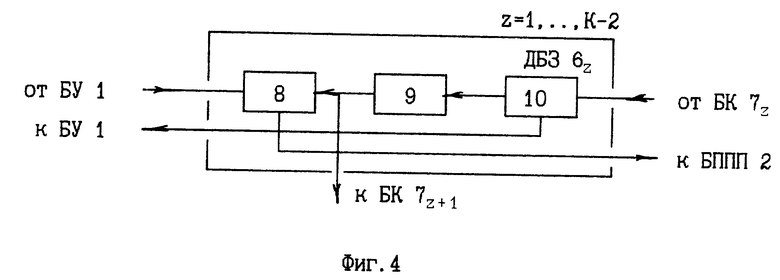

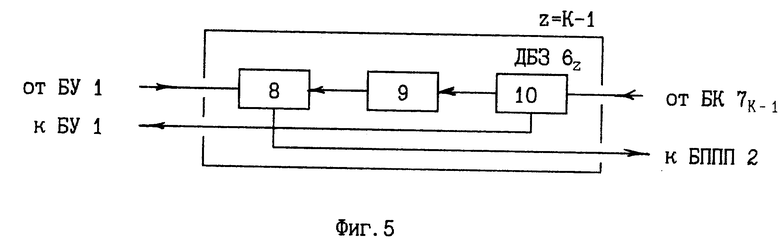

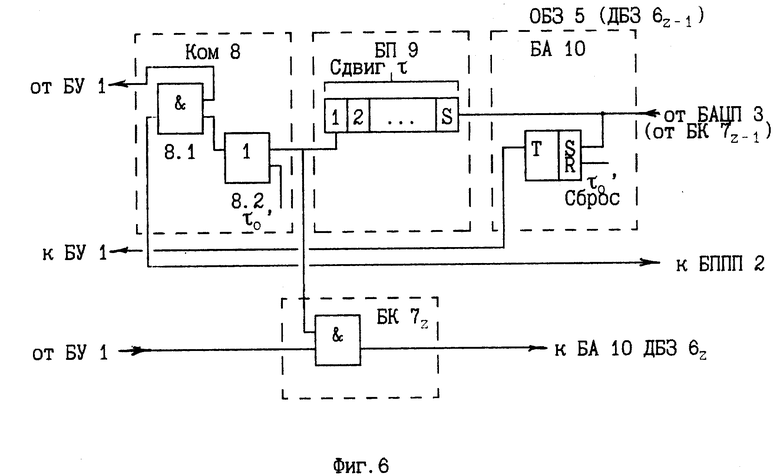

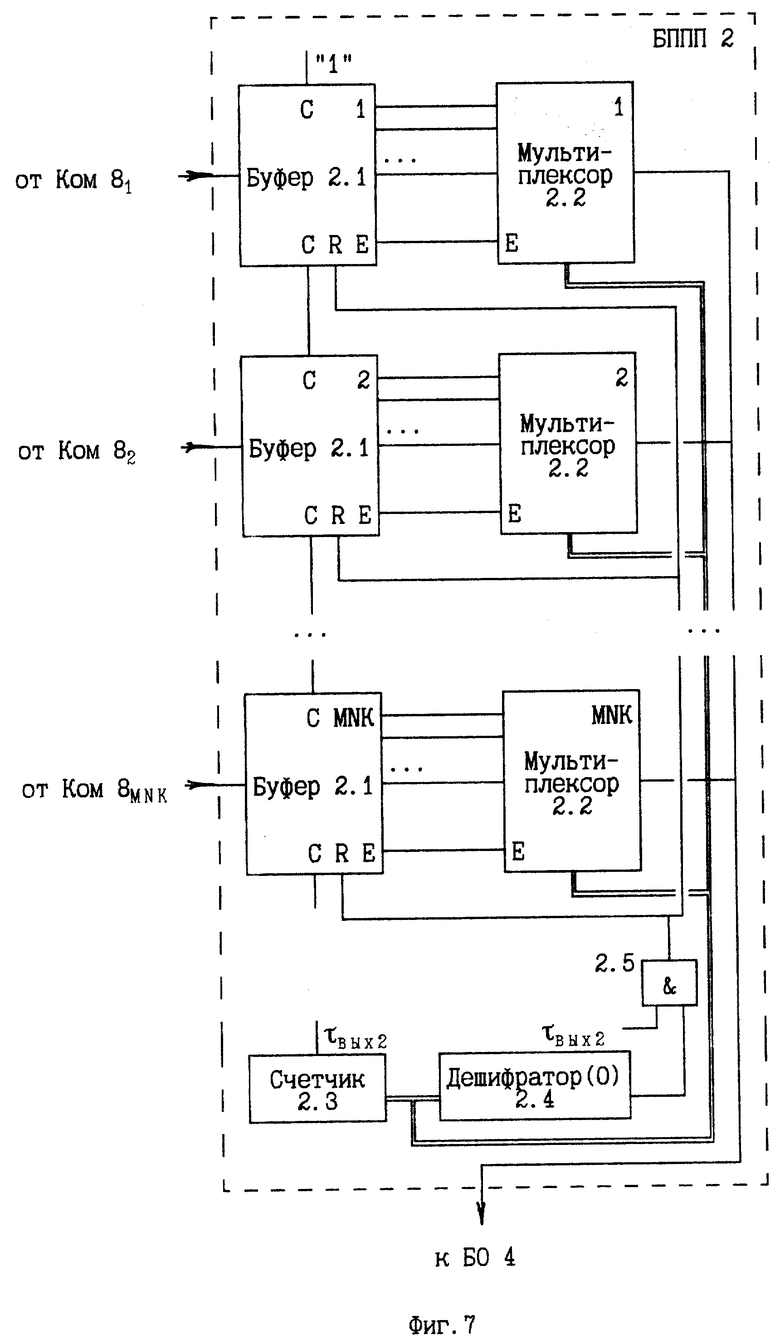

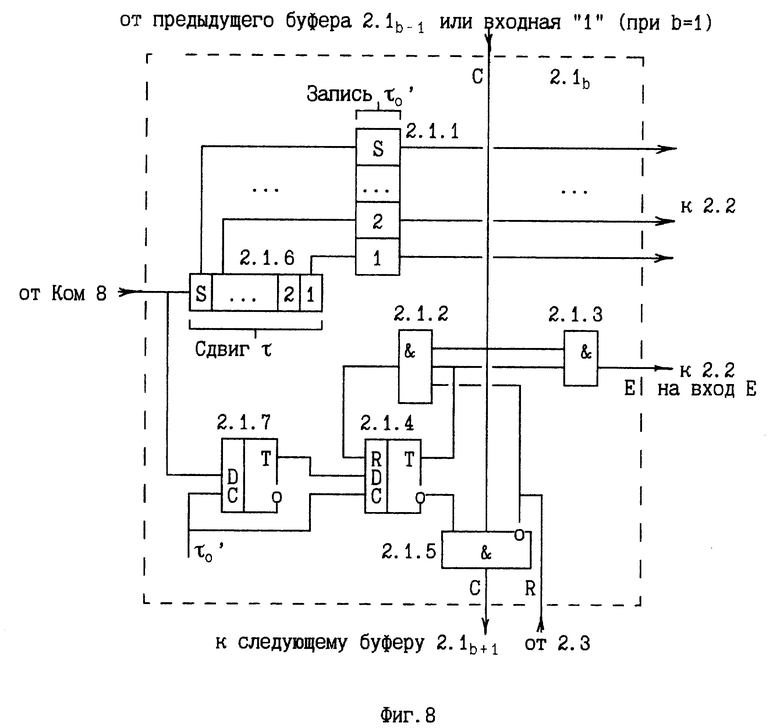

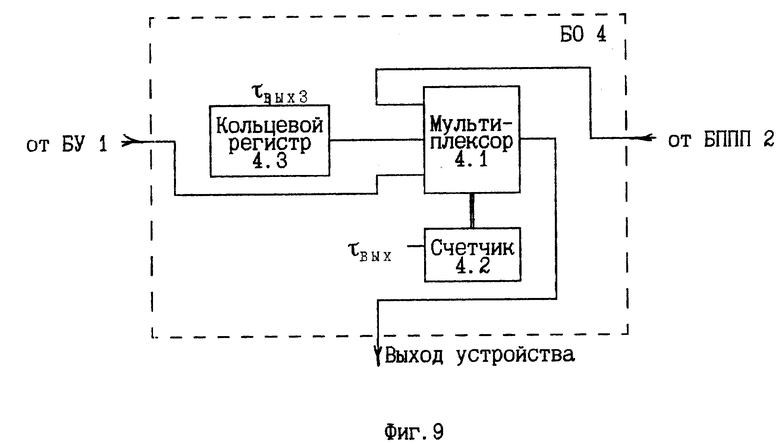

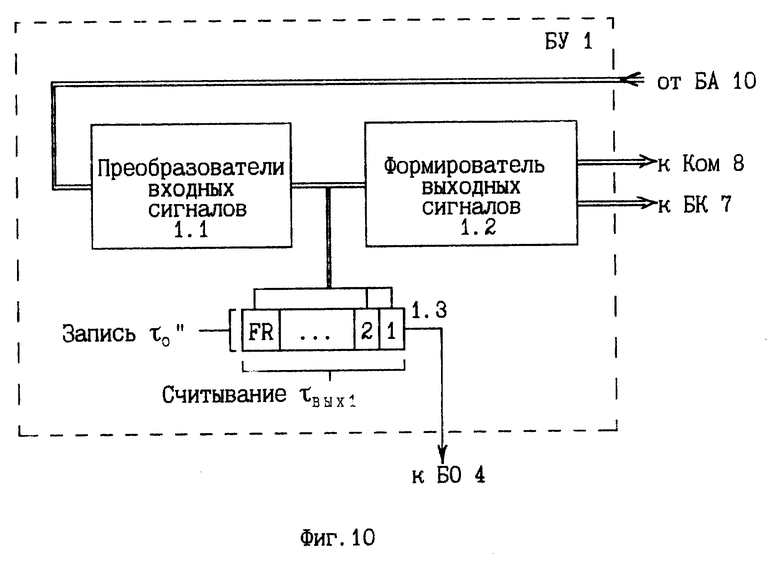

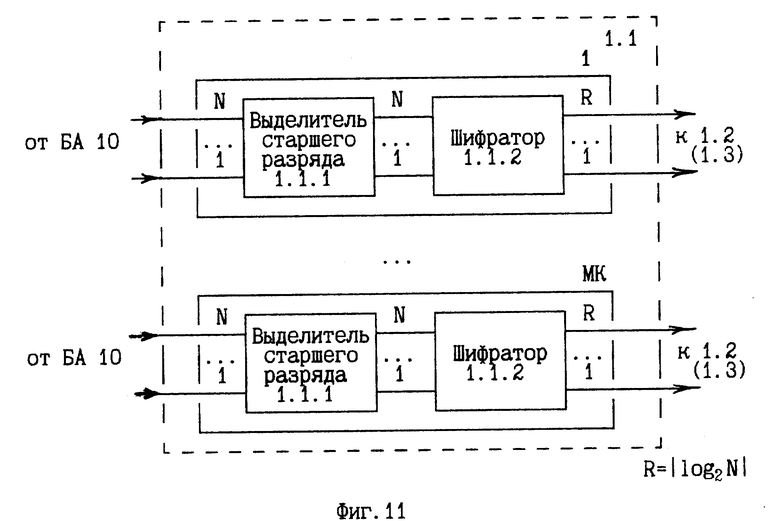

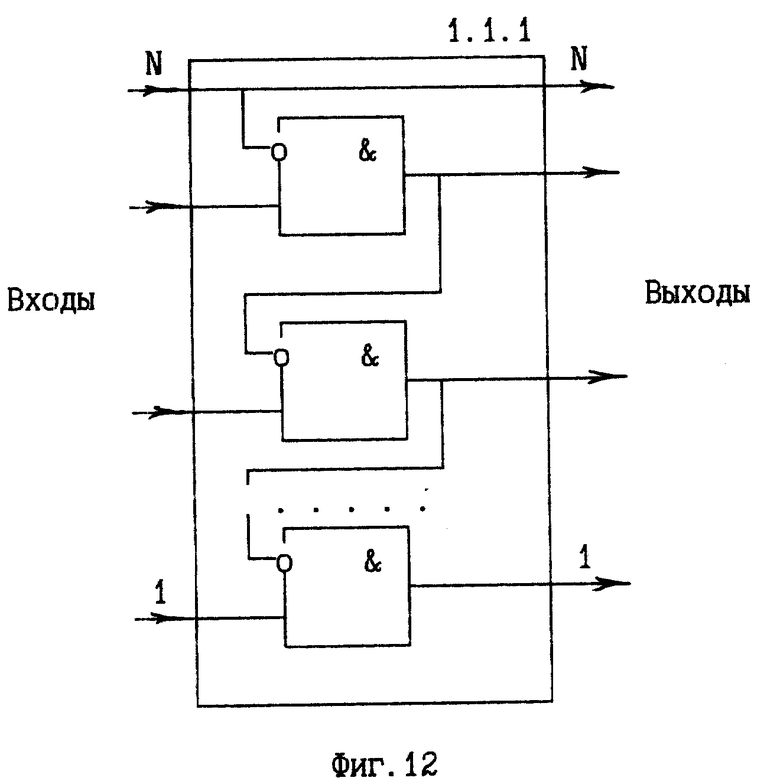

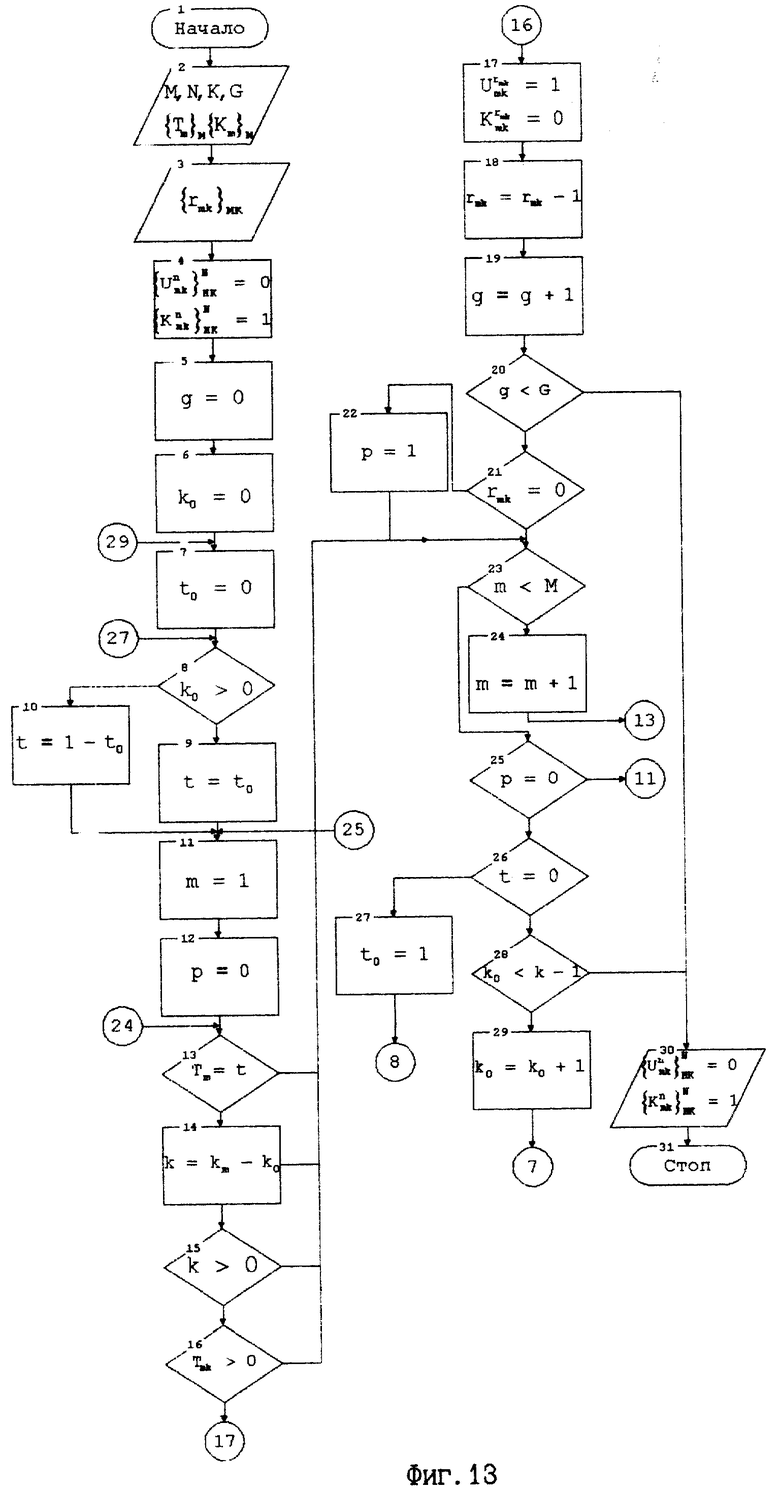

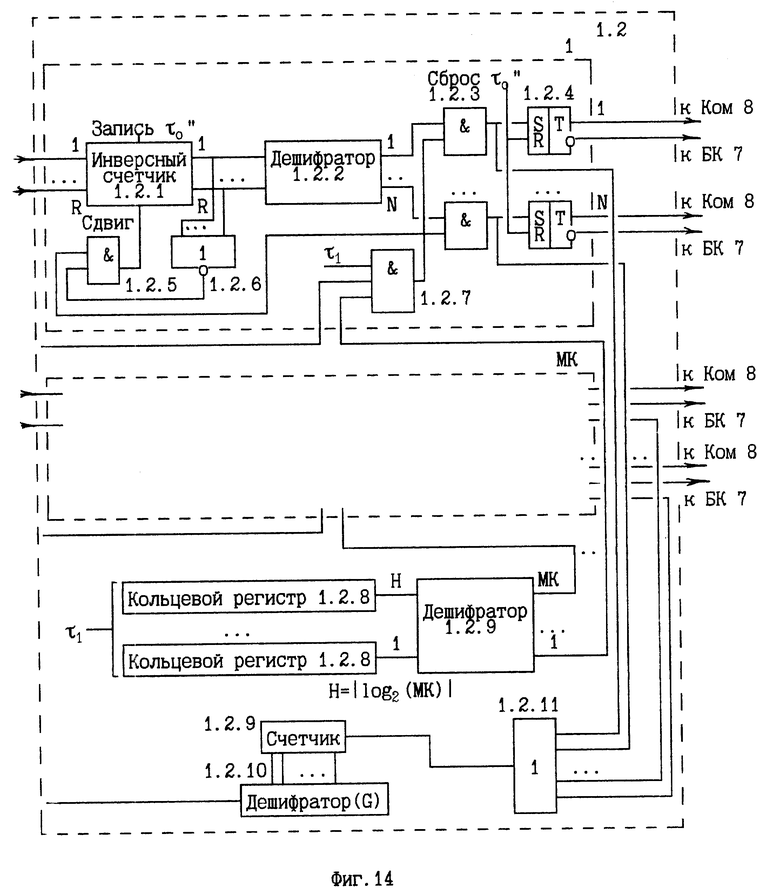

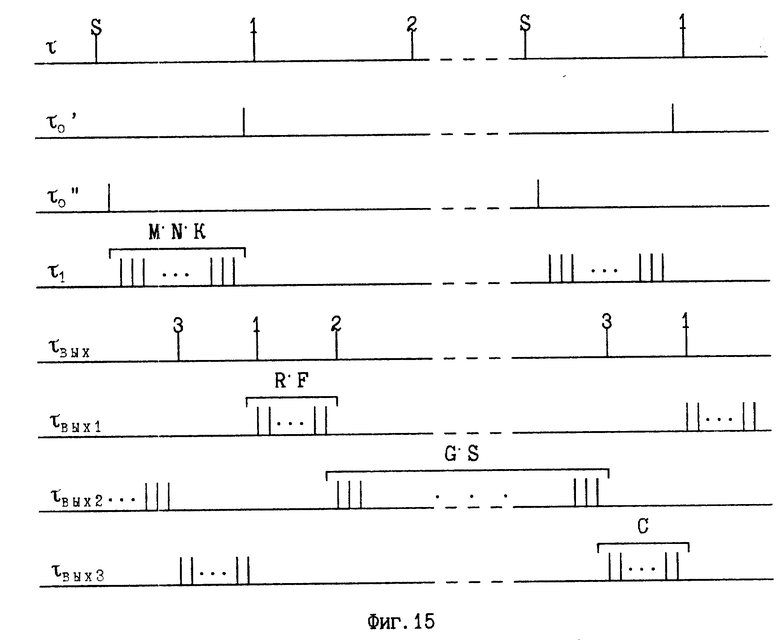

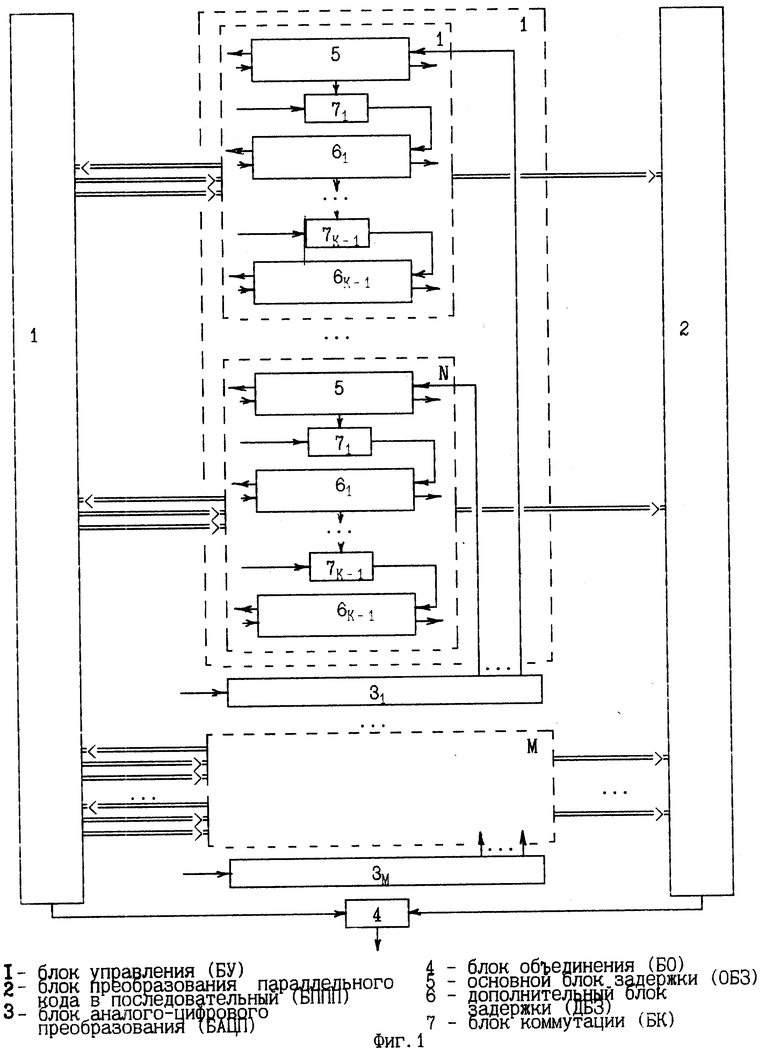

На фиг. 1 показана структурная схема устройства; на фиг. 2 - структурная схема устройства (дополнение); на фиг. 3 - структурная схема основного блока задержки; на фиг. 4 - структурная схема дополнительного блока задержки (кроме блоков с номерами (К-1)); на фиг. 5 - структурная схема дополнительного блока задержки (для блоков с номерами (К-1)); на фиг. 6 приведен пример реализации коммутатора, блока анализа, блока памяти и блока коммутации; на фиг. 7 - пример реализации блока преобразования параллельного кода в последовательный; на фиг. 8 - пример реализации буфера в блоке преобразования параллельного кода в последовательный; на фиг. 9 - пример реализации блока объединения; на фиг. 10 - пример реализации блока управления; на фиг. 11 - пример реализации преобразователя входных сигналов в блоке управления; на фиг. 12 - пример реализации выделителя старшего разряда в преобразователе входных сигналов в блоке управления; на фиг. 13 - пример алгоритма работы формирователя выходных сигналов в блоке управления;

на фиг. 14 - пример реализации формирователя выходных сигналов в блоке управления; на фиг. 15 - пример временных последовательностей тактовых импульсов, обеспечивающих синхронизацию работы отдельных блоков.

Заявленное устройство, представленное на фиг.1, состоит из блока управления (БУ) 1, блока преобразования параллельного кода в последовательный (БППП) 2, блока объединения (БО) 4, М блоков аналого- цифрового преобразования (БАЦП) 3, а также М групп блоков задержки из N подгрупп (более подробно представленных на фиг. 2), включающих основной блок задержки (ОБЗ) 5, (К-1) дополнительных блоков задержки (ДБЗ) 6 и (К-1) блоков коммутации (БК) 7, причем управляющие входы всех ОБЗ 5 подключены к соответствующим управляющим выходам БУ 1, а их информационные выходы - к соответствующим информационным входам БППП 2, сигнальные выходы всех ОБЗ 5 подключены к соответствующим сигнальным входам БУ 1, информационный вход каждого i-го ОБЗ 5, где i=1,2,.. , N, принадлежащего j-й группе блоков задержки, где j=1,2,..., М, подключен к соответствующему i-му выходу j-го БАЦП 3, управляющие входы всех ДБЗ 6 подключены к соответствующим дополнительным управляющим выходам БУ 1, а их информационные выходы - к соответствующим дополнительным входам БППП 2, сигнальные выходы всех ДБЗ 6 подключены к соответствующим дополнительным сигнальным входам БУ 1, информационный вход каждого z-го ДБЗ 6, входящего в i-ю подгруппу j-й группы блоков задержки, где z = 1,2,.., (К-1), подключен к выходу z-го БК 7, информационный вход каждого z-го БК 7, начиная с z=2, подключен к дополнительному информационному выходу (z-1)-го ДБЗ 6, информационный вход первого (z=1) БК 7 подключен к дополнительному информационному выходу соответствующего i-го ОБЗ 5, принадлежащего j-й группе блоков задержки, коммутирующие входы всех БК 7 подключены к соответствующим коммутирующим выходам БУ 1, сигнальный и информационный входы БО 4 подключены соответственно к сигнальному выходу БУ 1 и выходу БППП 2, выход БО 4 является выходом устройства, а входы БАЦП 3 являются входами устройства.

Структурная схема ОБЗ 5, показанная на фиг. 3, предназначена для запоминания и задержки на один цикл серии из S двоичных импульсов, поступающих с выхода БАЦП, обнаружения единичных отсчетов и коммутации задержанной серии на вход БППП 2. ОБЗ 5 состоит из коммутатора (Ком) 8, блока памяти (БП) 9 и блока анализа (БА) 10, причем информационный выход БА 10 подключен ко входу БП 9, выход которого подключен к информационному входу Ком 8 и одновременно является дополнительным информационным выходом ОБЗ 5, сигнальный выход и вход БА 10 являются соответственно сигнальным выходом и информационным входом ОБЗ 5, а выход и управляющий вход Ком 8 являются соответственно информационным выходом и управляющим входом ОБЗ 5.

Структурные схемы ДБЗ 6 показаны на фиг.4 и 5. ДБЗ 6z предназначен для запоминания и задержки на один цикл серии из S двоичных импульсов, поступающих через БК 7z с дополнительного информационного входа ОБЗ 5 (при z=1) или ДБЗ 6z-1 (при 1<z≤k-1), обнаружения единичных отсчетов и коммутации задержанной серии на вход БППП 2. ДБЗ 6 состоит из Ком 8, БП 9 и БА 10, причем информационный выход БА 10 подключен к входу БП 9, выход которого подключен к информационному входу Ком 8, управляющий вход и выход Ком 8 являются соответственно управляющим входом и информационным выходом ДБЗ 6, сигнальный выход и вход БА 10 являются соответственно сигнальным выходом и информационным входом ДБЗ 6, при этом в каждом z-ом ДБЗ 6 при z=1,2,.., (К-2) (см. фиг. 4), входящем в каждую из подгрупп блоков задержки, выход БП 9 одновременно является дополнительным информационным выходом ДБЗ 6.

Большинство блоков устройства по назначению и выполняемым функциям идентично одноименным блокам прототипа. С точностью до количества входных и выходных сигналов совпадают БАЦП 3, БО 4, Ком 8, БП 9, БА 10. Отличается количеством входных сигналов, но не отличается выполняемыми функциями БППП 2. Следовательно данные блоки могут быть реализованы так же, как аналогичные блоки прототипа [3].

Кроме того, пример возможной реализации БАЦП 3 приведен в [6,7]. Данный блок обеспечивает формирование дискретных отсчетов входного аналогового сигнала в виде N-разрядного двоичного кода. Отсчеты появляются на соответствующих N выходах блока с периодом τ .

Пример реализации на базе известных логических элементов [7] блоков Ком 8, БП 9, БА 10, а также дополнительно введенного в устройство блока БК 7 приведены на фиг.6.

Блок анализа 10 предназначен для передачи входной последовательности двоичных импульсов без преобразований и задержки на информационный выход и обнаружения появления хотя бы одного единичного импульса в каждой очередной серии из S импульсов, границы которой образуют цикл работы устройства и определяются тактовыми импульсами τo , следующими с периодом Ts= τ•S . После появления последнего импульса в серии уровень на сигнальном выходе соответствует логической "1", если в серии были единичные импульсы, и логическому "0" - в противном случае. На фиг. 6 показан пример реализации БА 10 на базе RS-триггера [7].

Блок памяти 9 предназначен для запоминания поступающей на его вход серии из S двоичных импульсов и формирования аналогичной серии на выходе с задержкой на один цикл из S тактов. На фиг. 6 показан пример реализации БП 9 на базе S-разрядного регистра сдвига [8].

Коммутатор 8 предназначен для коммутации двоичных импульсов с информационного входа блока на выход при наличии разрешающего уровня (логической "1") на управляющем входе. Кроме того, в зависимости от реализации взаимодействующих блоков Ком 8 может иметь дополнительные элементы согласования с ними. На фиг. 6 показан пример реализации Ком 8 на базе двух логических элементов "И" (8.1) и "ИЛИ" (8.2). При этом непосредственно коммутация осуществляется элементом "И", а элемент "ИЛИ" в данном случае служит для "информирования" блока, подключенного к выходу Ком 8 (в данном устройстве это БППП 2) о состоянии коммутатора перед считыванием очередной серии импульсов. В примере дополнительная функция Ком 8 обеспечивается пропусканием короткого тактового импульса τo, (появляющегося в интервале времени между считыванием последнего импульса предыдущей серии и первым импульсом следующей) на выход блока, если на управляющем входе будет присутствовать логическая "1", и непропусканием - в противном случае.

Блок коммутации 7 предназначен для выполнения функции коммутации, подобной основной функции Ком 8, т. е. для коммутации двоичных импульсов с информационного входа блока на выход при наличии разрешающего уровня (логической "1") на коммутирующем входе. На фиг. 6 показан пример реализации БК 7 на базе элемента "И" [7].

Блок преобразования параллельного кода в последовательный 2 предназначен для преобразования отдельных серий из S импульсов, поступающих одновременно на М•N•K входов блока, в одну последовательность импульсов на выходе БППП 2 сериями из S•G импульсов, причем C<M•N. При этом в выходную серию включаются только "помеченные" входные серии, что осуществляется согласованием работы с блоками, подключенными ко входам БППП 2 (в данном устройстве это Ком 8). На фиг. 7 показан пример реализации БППП 2 на базе известных цифровых элементов [6,7] : мультиплексоров (2.2), счетчика (2.3), дешифратора (2.4), элемента "И" (2.5), а также буферов (2.1), пример реализации которых из типовых элементов: параллельного регистра (2.1.1), элементов "И" (2.1.2, 2.1.3, 2.1.5), D-триггеров (2.1.4, 2.1.7) и регистра сдвига (2.1.6) - показан на фиг. 8. При поступлении тактовых импульсов τo, (появляющихся в интервале времени между считыванием последнего импульса предыдущей входной серии и первым импульсом следующей) на C-входы D-триггеров 2.1.7 всех буферов 2.1, данные триггеры устанавливаются в состояния, соответствующие сигналам, поступившим в этот же момент на D-входы, о состоянии подключенных к соответствующим входам БППП 2 внешних блоков (в данном устройстве - Ком 8). Одновременно с этим предыдущие входные серии считываются из регистров сдвига 2.1.6 в параллельные регистры 2.1.1, а состояние D-триггера 2.1.7 копируется в D-триггер 2.1.4. В интервале времени между тактовыми импульсами τo, все буферы последовательно (в соответствии с последовательностью соединения C-выходов и C-входов различных буферов) с периодом S•τвых2 опрашиваются на наличие входных серий, "помеченных" для" считывания в выходную серию. Моменты опроса определяются дешифратором 2.4 (реагирующем на появление на выходах счетчика 2.3 кодовой комбинации "0") и элементом "И" 2.5. Моменты опроса соответствуют промежуточным моментам между считыванием в выходную серию последнего импульса предыдущей считываемой серии и первого импульса следующей. За счет соответствующего соединения элементов "И" (2.1.2, 2.1.3, 2.1.5) в каждом буфере 2.1 формируется разрешающий считывание сигнал E, поступающий на соответствующий вход мультиплексора, подсоединенного к данному буферу, только при одновременном наличии разрешающих уровней "1" на C-входе данного буфера и на прямом выходе D-триггера 2.1.4. Последовательность считывания импульсов из разрядов параллельного регистра 2.1.1 (1,...,S) определяется последовательностью двоичных кодов (0,..., S-1) на выходе счетчика 2.3, управляющего мультиплексорами 2.2. После считывания данных из параллельного регистра 2.1.1 текущего буфера 2.1 через мультиплексор 2.2 на выход БППП 2 появляющийся на входах R разрешающий уровень "1" сбрасывает D-триггер в состояние "0", что обеспечивает прохождение разрешающего уровня "1" на C-вход следующего буфера. Если в следующем буфере D-триггер окажется в состоянии "0" ("не помеченная" серия), то разрешающий уровень пройдет дальше до первого попавшегося буфера, в котором D-триггер будет в состоянии "1" (" помеченная " серия).

Следует отметить, что рассмотренные примеры реализации БП 9, Ком 8 и БППП 2 предполагают последовательное считывание серий из БП 9 через Ком 8 в БППП 2, что приводит к дополнительной задержке на один цикл Ts= τ•S . Этой задержки можно избежать, если реализовать параллельное считывание данных из разрядов регистра сдвига БП 9 сразу в соответствующие разряды параллельного регистра 2.1.1 буферов 2.1 БППП 2, минуя регистр сдвига 2.1.6. При этом сигнал согласования Ком 8 и БППП 2 должен поступать, минуя D-триггер 2.1.7 сразу на вход D-триггера 2.1.4. В этом случае под каждой линией между Ком 8 и БППП 2 (см. фиг. 2) должны подразумеваться S+1 линии.

Блок объединения 4 предназначен для объединения последовательности импульсов, поступающих на сигнальный и информационный входы, и формирования выходного группового сигнала. В общем случае групповой сигнал может также включать различные служебные импульсы, в частности импульсы цикловой синхронизации [6] . На фиг. 9 приведен пример реализации БО 4 на базе известных цифровых элементов [6,7] : мультиплексора 4.1, счетчика 4.2 и кольцевого регистра 4.3. В данном варианте реализации БО 4 дополнительные служебные импульсы в количестве C формируются в самом БО 4. Их носителем является кольцевой регистр сдвига 4.3 на C тактов, из которого служебные импульсы считывается с помощью тактовых импульсов τвых3 , обеспечивающих их размещение на соответствующих временных позициях выходного сигнала. Мультиплексор 4.1, управляемый двоичным кодом, поступающим с выхода счетчика 4.2 (с тремя состояниями: 0,1,2), обеспечивает поочередное подключение к выходу сигналов, поступающих на сигнальный и информационный входы БО 4, а также сигналов с выхода кольцевого регистра 4.3.

Блок управления 1 является основным носителем используемого в устройстве известного алгоритма БИКМ [5], усовершенствованного в данном случае в части учета индивидуальных требований к допустимым искажениям и задержке передаваемых аналоговых сигналов. Назначением БУ 1 является анализ двоичных сигналов, поступающих на M•N•K сигнальных входов, и формирование в соответствии с результатами анализа двоичных сигналов на M•N•K управляющих и M•N•(K-1) коммутирующих выходах, а также формирование двоичной последовательности на сигнальном выходе.

Обязательным требованием, отражающим специфику алгоритма БИКМ, является ограничение количества "единичных" логических уровней на управляющих выходах величиной G<M•N, что и обеспечивает в итоге статистическое уплотнение путем формирования на выходе устройства последовательности (из значащих серий) информационных импульсов более короткой, чем суммарное количество двоичных импульсов, считываемых со всех выходов всех БАЦП 3. Значащими при этом являются те серии двоичных импульсов, в которых есть хотя бы один единичный импульс или серии, которые считываются с более младших разрядов БАЦП 3 по отношению к разрядам, на выходе которых есть единичные импульсы. Известным недостатком обычного алгоритма БИКМ является потеря младших разрядов практически во всех каналах при суммарном количестве значащих серий более допустимого количества G. В то же время при их количестве, меньшем, чем G, в выходной последовательности не все временные позиции, отведенные для информационной последовательности, будут заполнены. В предлагаемом устройстве это явление используется для передачи задержанных значащих серий, которые не уложились в допустимое число серий на предыдущих циклах. Учитывая, что предлагаемое устройство используется для передачи не только речевой информации, такая задержка может быть вполне допустима для ряда каналов. Кроме того, обычно при БИКМ серии считываются на выход в соответствии со следующим порядком: от старших разрядов всех каналов к младшим разрядам всех каналов. Это и является причиной потерь младших разрядов при перегрузках практически во всех каналах ("практически" означает, что иногда при небольших перегрузках потери могут быть и не во всех каналах, если количество лишних серий не превышает число каналов). Изменив последовательность считывания, можно обеспечить в отдельных каналах безыскаженную передачу при любых перегрузках.

Процесс функционирования БУ 1 определяется тремя группами исходных данных: общих, индивидуальных постоянных и индивидуальных временных.

Общими исходными данными являются:

M - число входов (M≥3);

N - разрядность АЦП (N≥ 4);

K - максимальное реализуемое количество циклов задержки (K≥1);

G - максимальное количество серий, считываемых на выход за один цикл (G≤M•N);

Индивидуальными постоянными исходными данными являются:

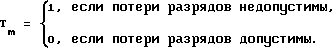

{ Tm} M - массив требований к допустимой степени искажений в каждом из каналов m=1,...,M, причем

{ Km}M - массив значений допустимого количества циклов задержки в каждом из каналов m=1,...,M, причем (1≤Km≤K).

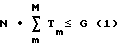

При этом требования {Tm}M должны удовлетворять условию реализуемости:

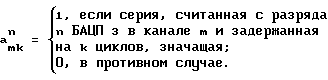

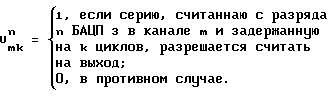

Индивидуальными временными исходными данными являются элементы трехмерного массива одноразрядных двоичных чисел  , поступающих на сигнальные входы БУ 1 с сигнальных выходов БА 10, о значащих сериях, записанных на предыдущем цикле в БП 9, т.е. готовых для передачи в следующем цикле, причем

, поступающих на сигнальные входы БУ 1 с сигнальных выходов БА 10, о значащих сериях, записанных на предыдущем цикле в БП 9, т.е. готовых для передачи в следующем цикле, причем

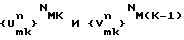

Результатом работы БУ 1 на каждом цикле являются элементы двух трехмерных массивов одноразрядных двоичных чисел  , формируемых соответственно на управляющих и коммутирующих выходах, причем

, формируемых соответственно на управляющих и коммутирующих выходах, причем

при этом для k < K V

Кроме того, БУ 1 подготавливает и передает на сигнальный выход в последовательном коде массив R-разрядных двоичных чисел {Wf}F, где  , соответствующих номерам старших разрядов БАЦП во всех каналах (в общем случае на всех циклах допустимой задержки), с которых считаны значащие серии, причем

, соответствующих номерам старших разрядов БАЦП во всех каналах (в общем случае на всех циклах допустимой задержки), с которых считаны значащие серии, причем

Учитывая предсказуемость состояния задержанных серий на основании данных о их считывании на предыдущих циклах, достаточно ограничиться величиной F=M, что позволит сохранить структуру выходного группового сигнала такой же, как в прототипе.

На фиг. 10 приведен пример реализации БУ 1 из трех основных блоков: преобразователя входных сигналов 1.1, формирователя выходных сигналов 1.2 и регистра сдвига 1.3. Последний блок является типовым и пример его реализации приведен в [8] , а примеры реализации первых двух блоков на базе типовых элементов [7,8] показаны на фиг. 11 и фиг. 14 соответственно.

Преобразователь входных сигналов 1.1 обеспечивает преобразование трехмерного массива одноразрядных двоичных сигналов  , поступающих на сигнальные входы БУ 1, в двумерный массив R-разрядных двоичных чисел {rmk}MK соответствующих номерам старших разрядов БАЦП (во всех каналах m=1,..., M и на всех циклах задержки k=1,..., K), с которых считаны и еще не переданы на выход значащие серии. На фиг. 11 показан пример реализации преобразователя входных сигналов 1.1 на базе выделителей старшего разряда 1.1.1, пример реализации которого из типовых логических элементов "И" показан на фиг. 12, и шифраторов 1.1.2, являющихся типовыми формирователями двоичного кода номера входного разряда, на котором присутствует логическая "1" [7,8].

, поступающих на сигнальные входы БУ 1, в двумерный массив R-разрядных двоичных чисел {rmk}MK соответствующих номерам старших разрядов БАЦП (во всех каналах m=1,..., M и на всех циклах задержки k=1,..., K), с которых считаны и еще не переданы на выход значащие серии. На фиг. 11 показан пример реализации преобразователя входных сигналов 1.1 на базе выделителей старшего разряда 1.1.1, пример реализации которого из типовых логических элементов "И" показан на фиг. 12, и шифраторов 1.1.2, являющихся типовыми формирователями двоичного кода номера входного разряда, на котором присутствует логическая "1" [7,8].

Формирователь выходных сигналов 1.2 является наиболее сложным блоком предлагаемого устройства и наиболее полно его функции может выполнить микропроцессорное вычислительное устройство [6,8] . Вариант алгоритма работы формирователя выходных сигналов 1.2 приведен в формализованном виде на фиг. 13. Ниже приводятся комментарии к функциям, выполняемым в блоках алгоритма:

1) Начало работы в момент  .

.

2) Считывание из ПЗУ общих и индивидуальных постоянных исходных данных.

3) Считывание из преобразователя входных сигналов 1.1 индивидуальных временных исходных данных, преобразованных в начальные номера старших разрядов значащих серий.

4) Начальная установка выходных управляющих и коммутирующих сигналов.

5) Установка начального значения счетчика управляющих сигналов, установленных в "1".

6) Установка начального значения счетчика остатка до последнего допустимого цикла задержки.

7) Установка начального значения учитываемого типа точности.

8,9,10) Инверсия типа точности для учета приоритетности последнего допустимого цикла задержки.

11) Установка начального значения номера анализируемого канала.

12) Установка начального значения признака необходимости повторного перебора каналов ("0"- не повторять, "1"- повторять).

13) Проверка типа точности (допустимой степени искажений) для анализируемого канала.

14) Вычисление номера анализируемого цикла задержки.

15) Проверка положительности номера анализируемого цикла задержки.

16) Проверка наличия значащих серий в анализируемом канале на анализируемом цикле задержки.

17) Установка управляющего и коммутирующего сигналов на выходах, соответствующих текущему разряду анализируемого канала на анализируемом цикле задержки.

18) Уменьшение номера текущего старшего (еще не считанного) разряда значащей серии.

19) Увеличение значения счетчика управляющих сигналов, установленных в "1".

20) Проверка допустимости количества управляющих сигналов, уже установленных в "1".

21,22) Уточнение признака необходимости повторного перебора каналов в зависимости от количества оставшихся значащих серий в анализируемом канале на анализируемом цикле задержки.

23,24,25) Проверка окончания перебора всех каналов.

26,27) Изменения учитываемого типа точности.

28,29) Проверка окончания перебора всех шагов задержки.

30) Считывание установленных значений управляющих и коммутирующих сигналов на соответствующие выходы БУ 1.

31) Окончание работы в момент  .

.

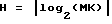

0писанный алгоритм в несколько видоизмененном виде можно также реализовать на базе типовых цифровых элементов без использования сложных вычислительных микропроцессорных устройств. Пример такой реализации показан на фиг. 14. Необходимая последовательность опроса наличия значащих серий и установки управляющих и коммутирующих сигналов в соответствии с индивидуальными постоянными исходными данными задается последовательностью H-разрядных двоичных кодов, где  , записанных поразрядно в кольцевые регистры сдвига (1.2.8) на M•N•K шагов. Подсчет количества оставшихся значащих серий в каждом канале на каждом цикле задержки обеспечивается инверсным счетчиком (1.2.1) совместно с логическими элементами "И" (1.2.5) и "ИЛИ" (1.2.6). Выделение на каждом такте τ1 номера выходных сигналов в соответствии с текущим кодом, считанным из кольцевых регистров сдвига, осуществляется дешифраторами (1.2.2, 1.2.9) и логическими элементами "И" (1.2.3, 1.2.7). Носителями выходных управляющих и коммутирующих сигналов являются соответственно прямые и инверсные выходы RS-триггеров (1.2.4). Подсчет количества управляющих выходов, на которых установлен уровень логической "1", осуществляется счетчиком 1.2.9 на основании сигналов на выходе логического элемента "ИЛИ", на входах которого на каждом такте появляется один единичный импульс, если текущая анализируемая серия значащая, и ни одного - если не значащая. При превышении допустимого количества G управляющих выходов, на которых установлен уровень логической "1", сигнал на выходе дешифратора 1.2.10 до конца работы на текущем цикле запирает элемент "И" 1.2.7, через который поступают тактовые импульсы сдвига инверсных счетчиков 1.2.1 и установки триггеров 1.2.4.

, записанных поразрядно в кольцевые регистры сдвига (1.2.8) на M•N•K шагов. Подсчет количества оставшихся значащих серий в каждом канале на каждом цикле задержки обеспечивается инверсным счетчиком (1.2.1) совместно с логическими элементами "И" (1.2.5) и "ИЛИ" (1.2.6). Выделение на каждом такте τ1 номера выходных сигналов в соответствии с текущим кодом, считанным из кольцевых регистров сдвига, осуществляется дешифраторами (1.2.2, 1.2.9) и логическими элементами "И" (1.2.3, 1.2.7). Носителями выходных управляющих и коммутирующих сигналов являются соответственно прямые и инверсные выходы RS-триггеров (1.2.4). Подсчет количества управляющих выходов, на которых установлен уровень логической "1", осуществляется счетчиком 1.2.9 на основании сигналов на выходе логического элемента "ИЛИ", на входах которого на каждом такте появляется один единичный импульс, если текущая анализируемая серия значащая, и ни одного - если не значащая. При превышении допустимого количества G управляющих выходов, на которых установлен уровень логической "1", сигнал на выходе дешифратора 1.2.10 до конца работы на текущем цикле запирает элемент "И" 1.2.7, через который поступают тактовые импульсы сдвига инверсных счетчиков 1.2.1 и установки триггеров 1.2.4.

На фиг. 15 приведен пример временных последовательностей тактовых импульсов, которые упоминались выше при описании примеров реализации основных блоков устройства и чьи обозначения использовались на фиг. 6-14.

Предлагаемое устройство в целом работает следующим образом. От M независимых источников информации на соответствующие входы устройства поступают аналоговые сигналы, которые преобразуются в БАЦП 3 в информационную последовательность N-разрядных двоичных отсчетов, появляющихся синхронно на N выходах всех M БАЦП 3 с периодом τ . Каждая из M•N информационных последовательностей двоичных отсчетов с информационных выходов соответствующих БАЦП 3 поступает сериями по S отсчетов (импульсов), где S=8...16 [5], с периодом длительности цикла TS, состоящим из S тактов длительностью τ , на информационные входы соответствующих ОБЗ 5. Внутри данных блоков информационная последовательность импульсов поступает на вход БА 10, на сигнальном выходе которого после поступления каждой серии появляется сигнал "1" при наличии в серии хотя бы одного ненулевого отсчета из S (признак значащей серии) или сигнал "0" в противном случае (признак незначащей серии). С информационного выхода БА 10 двоичные отсчеты поступают на вход БП 9, обеспечивающего запоминание всех S отсчетов одной серии и реализующего их задержку на время TS.

При поступлении на коммутирующий вход БК 71 с соответствующего коммутирующего выхода БУ 1 сигнала с уровнем логической "1", задержанная на S тактов серия из S отсчетов поступает с выхода БП 9 через БК 71, на информационный вход ДБЗ 61 и соответственно на вход БА 10 ДБЗ 61, а затем на вход БП 9 ДБЗ 61. В противном случае, т.е. при поступлении на коммутирующий вход ДБК 71 с соответствующего коммутирующего выхода БУ 1 сигнала с уровнем логического "0", БК 71 оказывается закрытым и на информационный вход ДБЗ 61 и соответственно на вход БА 10 ДБЗ 61, а затем на вход БП 9 ДБЗ 61 поступают нулевые отсчеты. После задержки еще на один цикл из S тактов в БП 9 ДБЗ 61 отсчеты с выхода данного блока через ДБК 72 поступают на информационный вход следующего ДБЗ 62 и т.д. до ДБЗ 6K-1.

Одновременно с поступлением с коммутирующих выходов БУ 1 коммутирующих сигналов, открывающих или закрывающих соответствующие БК 7, с управляющих выходов БУ 1 поступают управляющие сигналы, закрывающие или открывающие соответствующие Ком 8. В случае поступления из БУ 1 на управляющий вход некоторого Ком 8 открывающего сигнала с уровнем логической "1" с выхода БП 9, подключенного к информационному входу данного Ком 8, информация считывается через Ком 8 на соответствующий вход БППП 2. Суммарное количество управляющих сигналов g, имеющих значение "1", не превышает величину G < (MхN), соответствующую максимальному количеству серий из S двоичных отсчетов, помещающихся в цикле выходного группового сигнала на отрезке времени TS. Состав данных g≤G управляющих сигналов определяется в БУ 1 на основании сигналов, поступающих с сигнальных выходов всех БА 10, а также на основании заложенных в БУ 1 индивидуальных требований к допустимой степени искажений и задержке передачи сигналов от каждого из M источников информации с учетом их взаимной важности (приоритетности).

Поступившие в БППП 2 параллельно на M•N•K входов g≤G серий по S двоичных отсчетов преобразуются в последовательность из G•S отсчетов, которые поступают с выхода БППП 2 на информационный вход БО 4. На сигнальный вход БО 4 с сигнального выхода БУ 1 поступает последовательность из F•R двоичных символов, где  , являющихся кодом F≥M номеров старших разрядов на выходах БАЦП 3 всех каналов с ненулевыми двоичными отсчетами (в общем случае, на всех допустимых циклах задержки). В БО 4 осуществляется временное объединение G•S+F•R+C отсчетов, где C - количество дополнительных служебных импульсов, и формирование группового сигнала, поступающего с выхода БО 4 на выход устройства.

, являющихся кодом F≥M номеров старших разрядов на выходах БАЦП 3 всех каналов с ненулевыми двоичными отсчетами (в общем случае, на всех допустимых циклах задержки). В БО 4 осуществляется временное объединение G•S+F•R+C отсчетов, где C - количество дополнительных служебных импульсов, и формирование группового сигнала, поступающего с выхода БО 4 на выход устройства.

Положительный эффект от использования предлагаемого устройства продемонстрируем на следующем примере. Пусть количество каналов M=3, разрядность БАЦП N= 4, а допустимое количество считываемых серий G=8 (данные взяты из описания прототипа). В качестве тестового аналогового сигнала на входах всех БАЦП выберем гауссовский случайный процесс, прерываемый паузами в 40% времени. Будем полагать, что максимальный уровень на входе БАЦП на отрезке времени TS распределен по нормальному закону с параметрами, соответствующими (с учетом пауз) пикфактору П=3.3. Для упрощения расчетов будем также считать, что интервал корреляции входных сигналов не превышает длительности одного цикла TS В этом случае распределение вероятностей старших разрядов на каждом очередном цикле будет выглядеть следующим образом:

P =(P(0), P(1), P(2), P(3), P(4)}= =(0.442: 0.042; 0.082; 0.147; 0.288}

Рассчитаем вероятности потерь Pm отдельных разрядов при перегрузках в устройстве, работающем по алгоритму прототипа:

В первом канале:

P1(2) = P1(3) = P1(4) = 0

P1(1) = P(4){P(2)[P(3)+P(4)]+[P(3)+P(4)][P(2)+P(3)+P(4)]}= 0.075

Во втором канале:

P2(2) = P2(З) = P2(4) = 0

P2(1) = P(4){P(2)[P(3)+P(4)]+P(3)[P(2)+P(3)+P(4)]+ +P(4)[P(1)+P(2)+P(3)+P(4)]} = 0.078

В третьем канале:

P3(3) = P3(4) = О

P3(2) = P(4){P(3)[P(3)+P(4)]+P(4)[P(3)+P(4)]} = 0.054

P3(1) = P(4){P(1)P(4)+P(2)[P(3)+P(4)]+P(3)P(2) + P(4)[P(1)+P(2)]}+P(3){ P(3)[P(3)+P(4)] + P(4)[P(3)+P(4)]} = 0.055

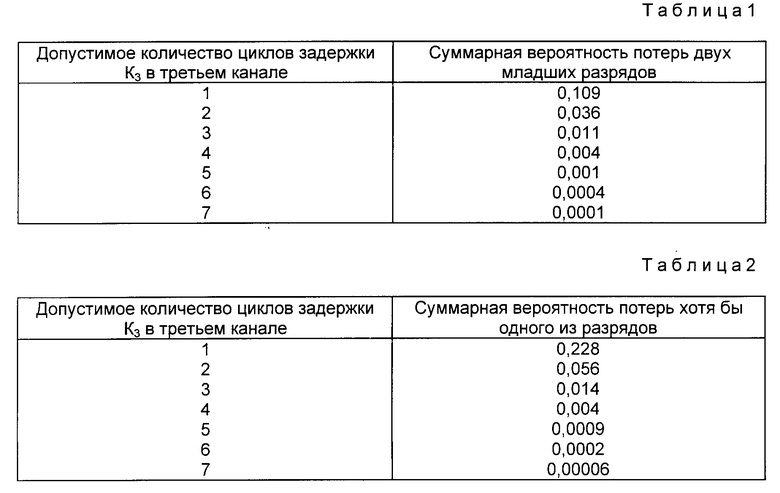

Как видно из приведенных результатов в первых двух каналах возможна потеря самых младших разрядов примерно с равными вероятностями 0.075 и 0.078, а в третьем канале возможна потеря двух разрядов с суммарной вероятностью 0.054 + 0.054 = 0.109, что объясняется используемым алгоритмом, дискриминирующим третий канал при считывании G=8 значащих серий из 9-12, появляющихся при перегрузках.

В предлагаемом устройстве можно задержать избыточные значащие серии двух младших разрядов 3-го канала и передать их при благоприятных условиях на следующих циклах. Функционирование устройства в данном случае может быть промоделировано марковской цепью, формулы расчета вероятностных характеристик которой являются довольно громоздкими и здесь не приводятся. В табл. 1 приведены количественные результаты расчетов.

Как видно из табл. 1, уже при задержке дополнительно на один шаг (K3=2) потери в третьем канале оказываются меньше, чем в первом и втором каналах, для которых в данном случае остаются допустимыми задержки K1=K2=1. С ростом допустимого количества циклов задержки потери в третьем канале снижаются до пренебрежимо малой величины.

Предлагаемое устройство позволяет, несмотря на жесткие требования к задержке в 1-м и 2-м каналах, исключить в них вообще потери при перегрузках. При этом задаются требования к точности T1=1, T2=1, T3=0. Как следует из формулы (1), такое сочетание требований реализуемо. При этом в третьем канале на отдельных циклах возможны потери всех разрядов. Однако за счет допустимости задержки в 3-м канале оказывается возможным существенно снизить потери в нем даже по сравнению с предыдущим случаем допустимости потерь в 1-м и 2-м каналах, что демонстрирует возможность улучшения в предлагаемом устройстве качества связи во всех каналах даже при дополнительной задержке только в одном из них. Результаты расчетов приведены в табл. 2.

При других статистических характеристиках входных аналоговых сигналов будут другие соотношения потерь, но в целом учет в предлагаемом устройстве индивидуальных требований к допустимой степени искажений и задержке в отдельных каналах всегда будет приводить к дополнительному выигрышу в качестве связи.

Литература

1. Авторское свидетельство N 520723. Устройство адаптивной импульсно-кодовой модуляции. / В. П. Кокошкин.

2. Авторское свидетельство N 1414922. Цифровая система передачи телефонных сигналов. / В. Р. Звонкович, В. П. Кокошкин, П. В. Сафонов, И. В. Ситняковский.

3. Авторское свидетельство N 575781. Устройство статистического уплотнения системы с временным разделением сигналов. / В. П. Кокошкин.

4. Банкет В.Л., Дорофеев В.М. Цифровые методы в спутниковой связи - М.: Радио и связь, 1988, - 240с.

5. Ситняковский И. В., Мейкшан В. И., Маглицкий Б. Н. Цифровая сельская связь./Под ред. М. Д. Бенедиктова. - М: Радио и связь, 1994, - 248 с.

6. Микросхемы памяти, ЦАП и АЦП: Справочник - 2-е изд., стереотип/О. Н. Лебедев, А. -Й. К. Марцинкявичюс, Э. -А. К. Багданскис и др.; - М.:КУбК-а, 1996, - 384 с.

7. Шило В.Л. Популярные цифровые микросхемы. Справочник, 2-е изд. испр. - Челябинск: Металлургия, Челябинское отд., 1989, - 352 с.

8. Алексенко А.Г., Шагурин И.И. Микросхемотехника: Учеб. пособие для вузов/Под ред. И. П. Степаненко. - М. : Радио и связь, 1982, -416 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР БЕЛОГО ШУМА (ВАРИАНТЫ) | 1997 |

|

RU2120179C1 |

| СПОСОБ И УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТОВ ДАННЫХ В КАНАЛЕ СВЯЗИ ОБЩЕГО ПОЛЬЗОВАНИЯ | 1997 |

|

RU2115246C1 |

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1997 |

|

RU2116004C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1996 |

|

RU2114501C1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1997 |

|

RU2115135C1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ РАДИОПЕРЕДАТЧИКА | 1995 |

|

RU2099872C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2144267C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА РАДИОСТАНЦИЙ | 1994 |

|

RU2099868C1 |

Использование: в технике электросвязи при построении многоканальных систем связи. Сущность изобретения: разработка устройства статистического уплотнения с временным разделением каналов, позволяющего уменьшить или полностью исключить искажения в отдельных каналах, а также расширить область применения за счет учета индивидуальных требований к допустимым искажениям и задержке различных аналоговых сигналов. Поставленная цель достигается тем, что в известное устройство, содержащее блоки управления 1, преобразования параллельного кода в последовательный 2, объединения 4, М блоков аналого-цифрового преобразования 3 и М групп по N в каждой из основных блоков задержки 5, где М ≥ 3, N ≥ 4, дополнительно введены M • N (К-1) блоков коммутации 7 и М • N (К-1) дополнительных блоков задержки 6, где К ≥ 2. Благодаря указанной совокупности признаков оказывается возможным уменьшить или полностью исключить потери при перегрузках избирательно в различных каналах за счет дополнительной задержки части разрядов цифровых отсчетов в каналах, допускающих такую задержку, и считывания отдельных разрядов в различных каналах в порядке снижения требуемой точности их восстановления. 1 з.п.ф-лы, 15 ил., 2 табл.

| SU, авторское свидетельство, 520723, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| SU, авторское свидетельство, 575781, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| SU, авторское свидетельство, 1418922, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| RU, авторское свидетельство, 2019043, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| US, патент, 4726020, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| GB, заявка, 2182588, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| GB, заявка, 1437959, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| GB, заявка, 1440443, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1998-05-10—Публикация

1997-01-23—Подача