VI 00 О

о о о

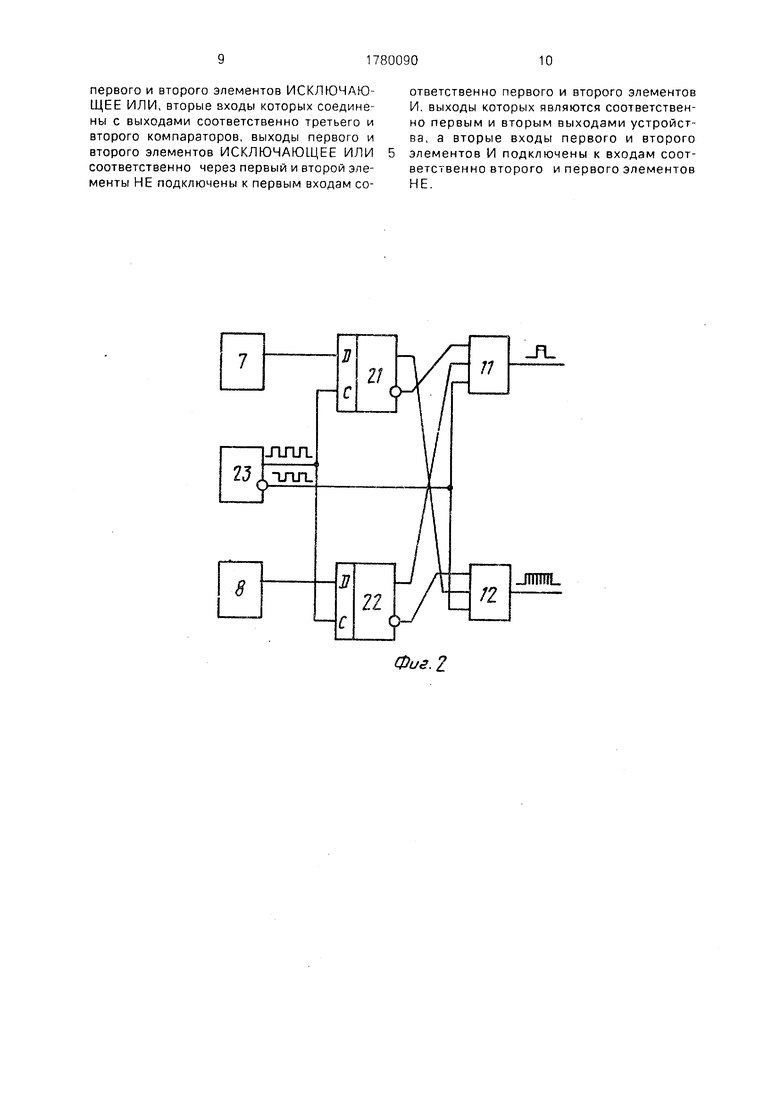

/i3o6peiei ;s/ie относится к аналоговой вычислительной технике и может быть использоБопО и качеств;-} блока перемножения, нагфимар, aHajiOroBbix и гибр щньХ 8ь Числительных машлках.

Известе -; ум - о; а О1Цмй широтно-имПуЯЬСМЫЙ ДСДУЛЯТОр (УШ1ЛГ Л) СОСТО;1 ИИЙ :/i3

псл:лрдог: атг;ль -:о соедутнанычх сум чиру К; це-п W ierpsToos и охваченно-о nij.io KHтельной обрзть о / связью первого ког.-гпараторз, йыхсд icoToporo подключен к перк;:-му входу cvMN-iMoyiouiero интегратооз, второго ;а,|Г.1Г араторз, к первому входу которого подключен сум гирую эго инrerpSTopa, а к второму входу - первый мнформгчйониый вход. Второй информиционн.1Й вход подключен к второму входу сумMwpyiOLU.arD и итег pa о Da через блок изг.1еиеиия ачакз, управляемый вь ходным (П гналсм второго компаратора, авыходной и.; 1роно-модул 1ровгнный сигна/i произведен- с; CHi. с з лхода пераоО компарзНадостат: ом является низкая то гюсть, обуспочле нна: наличием ком1луTupyHJiU-ix устройстп а целм входных сигнаНз1/ 1Л8 близкиг к пр5длэгаемог у с;х:-:ичес 0-4 peiiieHHKj яйг;яятсу: , ,У/;Я.Ц:/;| : |;0. .i ;О СОвДИНвг ИЬ 6

су имирующь-н лптегрзтор и охваченный по;10 ь veni;,-iow of pSTrHji- связью первый компаратср, йыхол ;oTOpi;f гшдключек к первому входу сум -1;/:ру О;цего интегратора ЕОрой Бход KCTOpoiD лвляе тя первым инЛириацио-НУм входом УШИМ, причем выхо,ц су.:- ирую.ла о ииеграторэ через парзь й .итйбный резистор подключен к rsepBOwy входу пторого KOMfiapoTops, второй м,;о,4 ; г:тс:рого -:срйЗ второй масштабный ре;н1С-ор соедлмен с вторым инфорг-шцион1 8 р Е Ы е в Ы в о А Ы

а ходом

третьего vi четвертого масштабкьзх резисторов гюд|(.лю1ень coo7B8TCHieh:MO к выходу cyMiviV:pyOL u,eio ингеграторз м второму информационному входу ViiJi/lM, а вторуо вь1зодь объединены и подк/иочень к пэрвому входу третьего компаратора, второй вход которого соединен с нулевого потенциалз- к выходам второго и третьего компар а т о р о в п о д к л ю ч е .ч ы у с т а и о в о ч и ы е, реагирующие ма фронт, R- и S-бходы Tpi-irгерного устройства, выход которого служит выходом УШИМ,

Известный модулятор более точен, чем описанное выше техническое решение, одна ко точность его остается низкой, поскольку длительность каждого из двух Информативных выходных интервалов УШ/lM зависит от моментов смены направления интегрирования, где велика нелинейность пилообразного напряжения на выходе интегратора, которая приво,дит к дополнительным погрешностям. Кроме того, на точность умножения оказывают значительное влияние задержки и фронты всех 1р8х компараторов схемы, которые приводят к появлению в выходном сигнале УШИМ ряде составляющих, определяющих дополнмтельные погрешкостм.

Целью изобретения яв/1яется повышение точности,

цель достигаетсй тем, что в УШИМ, содержащий последовательно соединенные

суммирующий интегратор и охваченный положительной обратной связью первый к.ом,паратор, выход которого подключен к первому входу суммирующего интегратора, второй вход которого является первым VIHформационным входом УШИМ, причем выход сум у1ирующего интегратора через первый масштабный резистор подключен к первому входу второго компаратора, второй вход ко орого через второй масштабнь:й резистор соединен с вторым информационным входом УШИМ, первые выводы третьего м четвертого масштабных резисто1 оа подключены соответственно к выходу оумгчир/ющего iHTarpaTops и второму информзцмокному входу УШИМ, а вторые выаодь объединень и подключены к первому входу третьего компаратора, второй вход которого соединен с шиной нулевого потенциглг;, введены первый и второй элементы

ИСКЛЮЧАЮиДИЕ И Л И, первый и второй элементы НЕ и первый и второй элементы И, при зтом первого компаратора подключен к первым входам первого и второго элементов ИСКЛЮЧАЮШ.ЕЕ ИЛИ, вторые входы которых соединены с выходами соответственно третьего и второго компараторов , выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соответственно через первый f второй элементы НЕ подключены к первым входам соответственно первого /1 второго элементов И, выходы которых являются соответственно первьм и вторым выходами УШИМ а вторь е входы первого и второго элементов И подхлючехв

к входам соответственно второго и первого элементов i-IE,

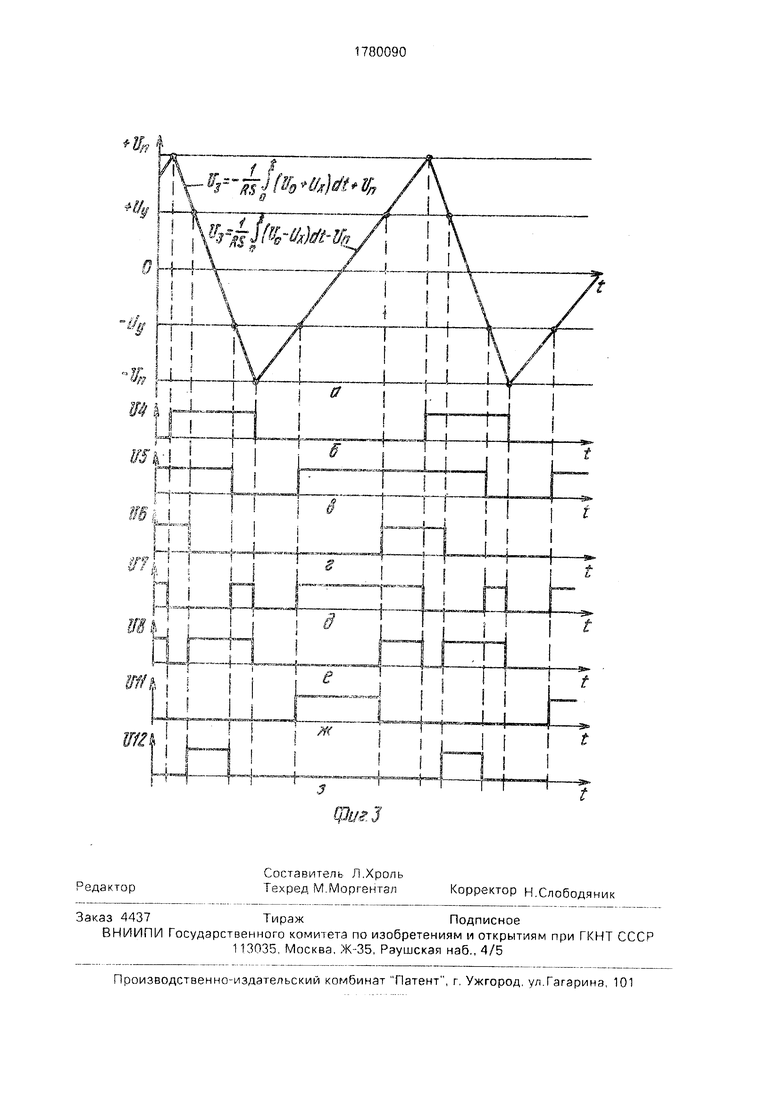

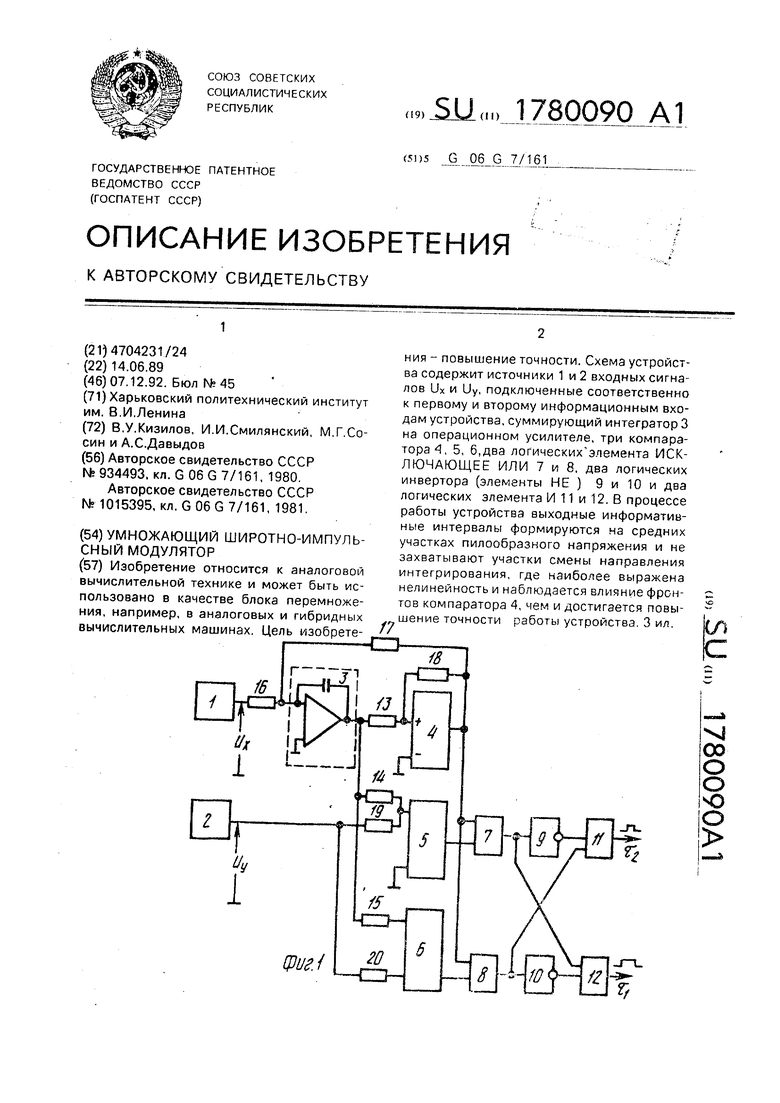

На фиг. 1 приведена схема УШИМ: на фиг, 2 показан фрагмент логической частк УШИМ при преобразовании про зведения

входных сигналов в цифровой код; на ф1/(Г, 3 показаны временные диаграммы работы УШИМ для положительных входных сигналов.

Схема УШИМ содержит источники 1 и 2 входных сигналов Ux Uy, подключенные

соответственно к первому и второму информационным входам УШИМ, суммирующий интегратор 3 на операционном усилителе, три компаратора 4, 5 и 6, два логических элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и 8, два логических инвертора (элементы НЕ) 9 и 10 и два логических элемента И 11 и 12. Выход компаратора 3 подключен через масштабные резисторы 13, 14 и 15 к неинвертирующим входам трех компараторов 4, 5 и 6. К инвертирующему входу интегратора 3 подключены через резисторы 16 и 17 источник 1 первого входного сигнала Ux и выход пераого компаратора 4, который подключен также к первым входам логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и 8 и через масщтабный резистор 18 к своему неинвертирующему входу. Вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и В подключены к выходам компараторов 5 и 6,а выходы этих элементов подключены через логические инверторы 9 и 10 соответственно к первым входам логических элементов И 11 и 12. Вторые входы элементов И 11 и 12 соединены непосредственно с выходами элементов ИКЛЮЧАЮЩЕЕ ИЛИ 8 и 7 соответственно. Источник 2 второго входного сигнала Uy через масштабные резисторы 19 и 20 подключен соответственно к неинвертирующему входу компаратора 5 и к инвертирующему входу компаратора 6.

На выходе элементов И 11 и 12 формируются положительные выходные импульсы УШИМ. При положительных входных сигналах Ux и Uy длительность импульса на выходе элемента И 12 больше, чем длительность импульса на выходе элемента И 11, поэтому выход элемента И 12 можно считать УСЛОВНО положительным, а выход элемента И 11 - отрицательным. При изменении полярности одного из входных сигналов длительность импульса на выходе элемента И 11 становится больще длительности импульса на выходе элемента И 12.

Схема работает следующим образом.

Интегратор 3 и компаратор 4 образуют автоколебательный широтно-импульсный модулятор. На выходе интегратора 3 формируется пилообразное напряжение, модулированное по скорости сигналом Ux. Скорость изменения напряжения на выходе интегратора 3 при отрицательном напряжеНИИ на выходе компаратора 4 и положительном входном сигнале Ux равна -Uo +Ux

a при положительном напряжении на выходе компаратора

-Uo +UN

где ± Uo - напряжение на выходе компаратора 4; TO постоянная времени интегратора 3. равная CR17 (принято, что R16 R17). Компаратор 4 переключается из одного состояния насыщения в другое, когда напряжение на его неинвертирующем входе меняет знак, например, с -I- на -. Потенциал неинвертирующего входа равен

Uc

Uv,

Ri3+R18,

р ±Ri3 + R18Ri3 +Ri8

где UM - напряжение на выходе интегратора. Приравняв нулю, определим значение напряжения на выходе интегратора, соответствующее порогу переключения компаRn

ратора 4 (см. фиг. 3 а, б) UK ± Us -5-

Компараторы 5 и 6 переключаются в моменты, когда напряжение на выходе интегратора 3 сравнится с уровнями ± Uy, как показано на фиг. 3 в, г.

Изменение выходного сигнала компараторов 5 и 6 описывается выражениями (при равенстве сопротивлений Rig) Z5 sign (ии + Uy); Z6 sign (UH - Uy),

что эквивалентно сравнению пилообразного напряжения Un на компараторе 5 с уровнем -Uy, а на компараторе Uy. На логических элементах ИСКЛЮЧАЮЩЕЕ ИЛИ формируются импульсы, когда напряжения на компараторе 4 и на компараторах 5 и 6 по знаку не совпадают (фиг. 3 д. е).

На выходах элементов И 11 и 12 формируются выходные импульсы УШИМ Г1ИГ2 (см. фиг. 3 ж. з), определяющие информативные интервалы. Длительность этих интервалов может быть определена из следующих соображений (см. фиг. 3 а, ж, з). Когда напряжение на выходе компаратора 4 отрицательно, интегратор интегрирует разность -Uo+Ux в положительном направлении от уровня UK до уровня +UK.

Интервалу г i соответствует изменение напряжения интегратора от -Uy до +Uy, т.е. на 2Uy со скоростью Vi. Откуда интервал времени ri может быть определен как отношение изменения напряжения (путь) к скорости:

2Uy 2Uy

vi -iJo-u; °Аналогично определяется 12. которому соответствует изменение напряжения интегратора от до -Uy при положительном напряжении на выходе компаратора 4,

2 V2 Uo + Ux Разность длительностей этих интервалов равна

UxUv

ri Г2 4ТоиГ

и

Длительность цикла преобразования определяется изменением напряжения интегратора на 2UK {от -UK до +UK со скороCTbioVi и от +UK до -UK со скоростью V2). Она может быть определена заменой в выражениях п и Т2 Uy на UK и суммированием полученных интервалов

2U« , 2U.

+ То

Uo -Ь Ux

Uo-Ux

UK Up

Относительная разность длительностей выходных ммпульсов равна

Г1 -га y.

Тц Uo UK

Как следует из описания работы УШИМ и временных диаграмм, выходные информативные интервалы формируются на средних участках пилообразного напряжения и не захватывают участки смены направления мн-аэгрировзимя, где наиболее выражена нелинейность и нзблюдается наибольшее влияние фронтов компаратора 4, что повышзетточность работы УШИМ. Наличие двух, г не четырех, как в устройствах-аналогах, информативных интервалов также способствует повышению точности его работы.

Можно показать, что на точность предлагаемого УШИМ значительно меньшее влияние оказывают и задержки компараторов, чем в устройстве-прототипе. Так, если предположить, что задержки всех компараторов при переключении в положительном и отрицательном направлениях равны, то задержки компараторов 5 и 6 вообще не влияют на точность преобразования, а задержки переключения компаратора 4 не вносят погрешности нелинейности, а вносят только небольшую мультипликативную погрешность.

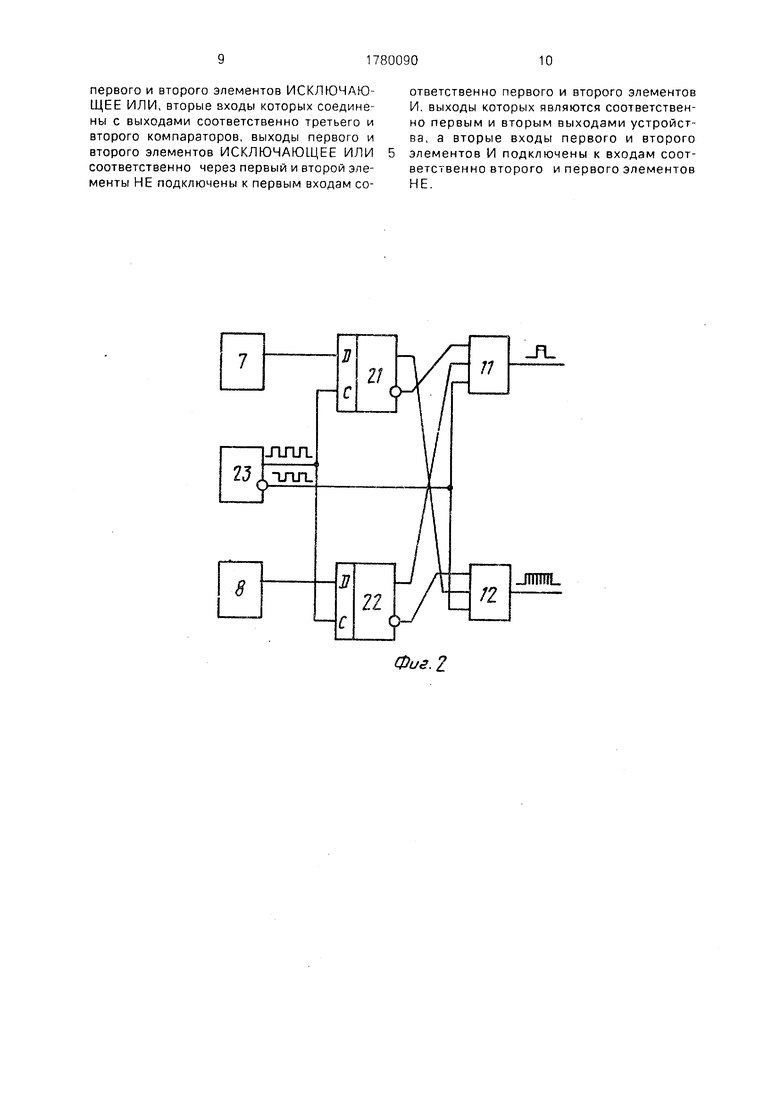

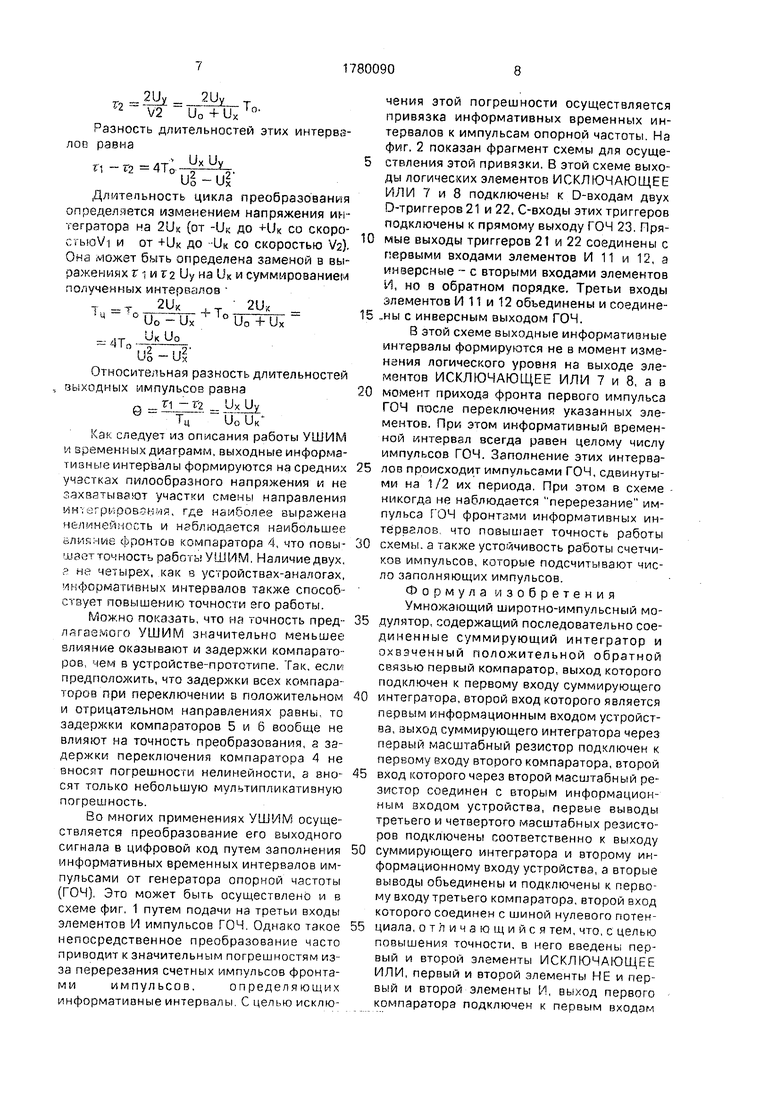

Во многих применениях УШИМ осуществляется преобразование его выходного сигнала в цифровой код путем заполнения информативных временных интервалов импульсами от генератора опорной частоты (ГОЧ), Это может быть осуществлено и в схеме фиг. 1 путем подачи на третьи входы элементов И импульсов ГОЧ. Однако такое непосредственное преобразование часто приводит к значительным погрешностям изза перерезания счетных импульсов фронтами импульсов. определяющих информативные интервалы. С целью исключения этой погрешности осуществляется привязка информативных временных интервалов к импульсам опорной частоты. На фиг. 2 показан фрагмент схемы для осуществления этой привязки. В этой схеме выходы логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и 8 подключены к D-входам двух D-триггеров 21 и 22, С-входы этих триггеров подключены к прямому выходу ГОЧ 23. Прямые выходы триггеров 21 и 22 соединены с первыми входами элементов И 11 и 12, а инверсные - с вторыми входами элементов И, но в обратном порядке. Третьи входы элементов И 11 и 12 обьединены и соедине5 .ны с инверсным выходом ГОЧ.

В этой схеме выходные информативные интервалы формируются не в момент изменения логического уровня на выходе элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и 8, а в

0 момент прихода фронта первого импульса ГОЧ после переключения указанных элементов. При этом информативный временной интервал всегда равен целому числу импульсов ГОЧ. Заполнение этих интервалов происходит импульсами ГОЧ, сдвинутыми на 1/2 их периода. При этом в схеме никогда не наблюдается перерезание импульса ГОЧ фронтами информативных интервалов, что повышает точность работы

0 схемы, а также устойчивость работы счетчиков импульсов, которые подсчитывают число заполняющих импульсов.

Формула изобретения Умножающий широтио-импульсный модулятор, содержащий последовательно соединенные суммирующий интегратор и охваченный положительной обратной связью первый компаратор, выход которого подключен к первому входу суммирующего

0 интегратора, второй вход которого является первым информационным входом устройства, выход суммирующего интегратора через первый масштабный резистор подключен к перво.му входу второго компаратора, второй

5 вход которого через второй масштабный резистор соединен с вторым информационным входом устройства, первые выводы третьего и четвертого масштабных резисторов подключены соответственно к выходу

0 суммирующего интегратора и второму информационному входу устройства, а вторые выводы обьединены и подключены к первому входу третьего компаратора, второй вход которого соединен с шиной нулевого потенциала. отличающийся тем, что. с цельно повышения точности, в него введены первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй элементы НЕ и первый и второй элементы И. выход первого компаратора подключен к первым входам

первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых соединены с выходами соответственно третьего и второго компараторов, выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соответственно через первый и второй элементы НЕ подключены к первым входам соответственно первого и второго элементов И, выходы которых являются соответственно первым и вторым выходами устройства, а вторые входы первого и второго элементов И подключены к входам соответственно второго и первого элементов НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1980 |

|

SU911560A1 |

| Преобразователь напряжения в интервал времени | 1989 |

|

SU1621177A2 |

| Интегрирующий аналого-цифровой преобразователь | 1988 |

|

SU1681384A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ АНАЛОГОВОГО СИГНАЛА ОПТИЧЕСКОГО ДАТЧИКА В ЦИФРОВОЙ КОД | 1995 |

|

RU2097915C1 |

| Измеритель скорости звука | 1990 |

|

SU1758561A2 |

| Преобразователь выходных сигналов параметрических датчиков в код | 1986 |

|

SU1336232A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1444950A1 |

| УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КОРНЯ КВАДРАТНОГО ИЗ ПРОИЗВЕДЕНИЯ ДВУХ ВЕЛИЧИН | 1992 |

|

RU2025774C1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1989 |

|

SU1695503A1 |

| Цифровой интегрирующий вольтметр | 1989 |

|

SU1698813A1 |

Изобретение относится к аналоговой вычислительной технике и может быть использовано в качестве блока перемножения, например, в аналоговых и гибридных вычислительных машинах. Цель изобрете-17ния - повышение точности. Схема устройства содержит источники 1 и 2 входных сигналов Ux и Uy, подключенные соответственно к первому и второму информационным входам устройства, суммирующий интегратор 3 на операционном усилителе, три компаратора -1, 5, 6,два логичесхих'элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и 8, два логических инвертора (элементы НЕ ) 9 и 10 и два логических элемента И 11 и 12. В процессе работы устройства выходные информативные интервалы формируются на средних участках пилообразного напряжения и не захватывают участки смены направления интегрирования, где наибо.'^ее выражена нелинейность и наблюдается влияние фронтов компаратора 4, чем и достигается повышение точности работы устройства. 3 ил.СПс

-Л.

Фиг. г

| Широтно-импульсное множительное устройство | 1980 |

|

SU934493A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-12-07—Публикация

1989-06-14—Подача