арифметический блок 8, Во втором цикле работы коммутаторы 2 и 3 подключают преобразуемое U и опорное }д напряжения таким образом, что напряжение на выходе интегратора 4 к концу первого такта становится пропорционально разности и - УО Во втором такте второго цикла осуществляется разряд интегратора опорным напряжением UQ до момента срабатывания компаратора 6. В арифметический блок 8 заносится код, пропорциональный Од - и, Результирующий код, накопленный в блоке 8 за два цикла преобразования пропорционален преобразуемому напряжению U и практически не зависит от напряжений смещения интегратора 4 и компаратора 6. Кроме того не предъявляется требовайий к точности резистора R и конденсатора С интегратора 4, что обеспечивает высокую точность преобразования. } з.п. ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Преобразователь сигналов датчиков переменного тока | 1986 |

|

SU1332531A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1984 |

|

SU1233283A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛЫ ВРЕМЕНИ | 2014 |

|

RU2552605C1 |

| Преобразователь напряжения в интервал времени | 1988 |

|

SU1649662A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Интегрирующий аналого-цифровой преобразователь | 1982 |

|

SU1202056A1 |

| Многофункциональный преобразователь | 1985 |

|

SU1267443A1 |

Изобретение относится к области измерительной техники и может быть использовано для создания высокоточных цифровых измерительных приборов. Устройство обеспечивает высокую точность прербразования за счет автоматической коррекции погрешности, обусловленной наличием напряжений смещения интегратора и компаратора, и исключения влияния точности резистора на результат преобразования; Достоинством аналого-цифрового преобразователя является также простота устройства. Результат преобразования определяется как сумма результатов за два цикла работы устройства. В первом такте первого цикла коммутаторы 2 и 3 подключают преобразуемое и и опорное Uj напряжения ко входам интегратора 4 таким образом, что выходной сигнал интегратора 4 пропорционален разности Ug - Uy, Затем осуществляется разряд интегратора Д опорным напряжением -U до момента срабатьшания компаратора 6. Логический блок 7 формирует интервал времени, пропорциональный разности U - - Uj(, который заполняется импульсами опорной частоты fg ОД заносится в ж

1

Изобретение относится к измерительной технике и может быть использовано для создания высокоточных цифровых измерительных приборов.

Цель изобретения - повьшение точности и упрощение устройства.

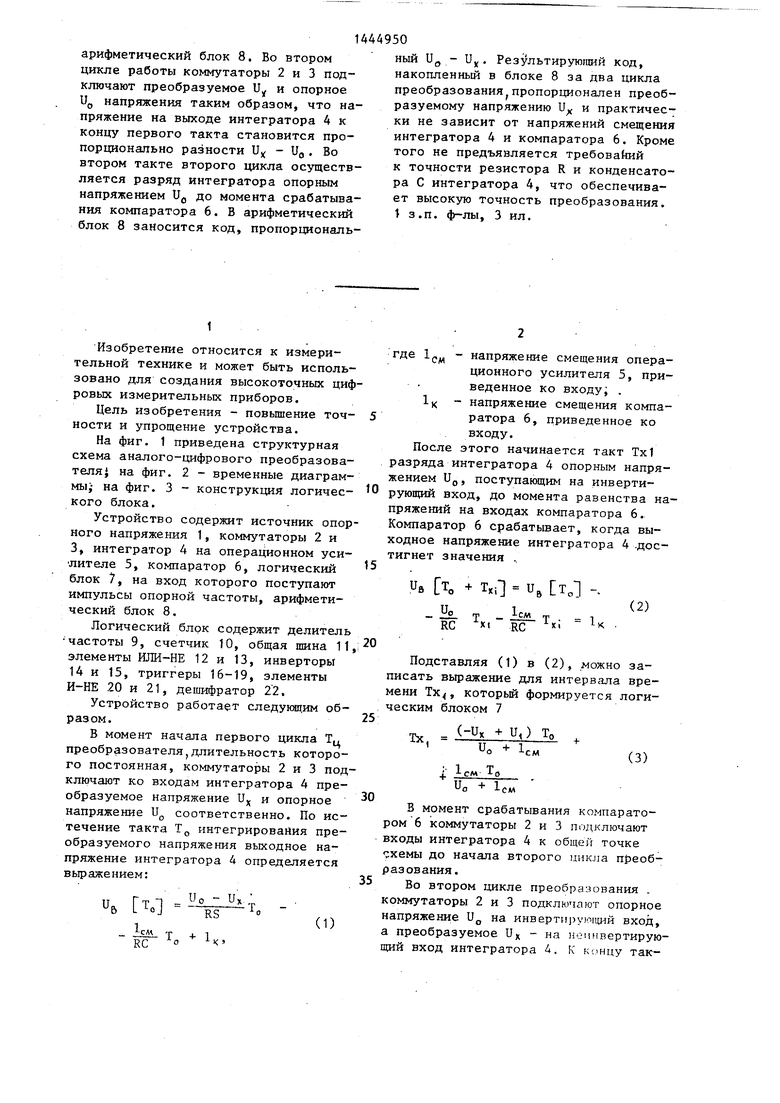

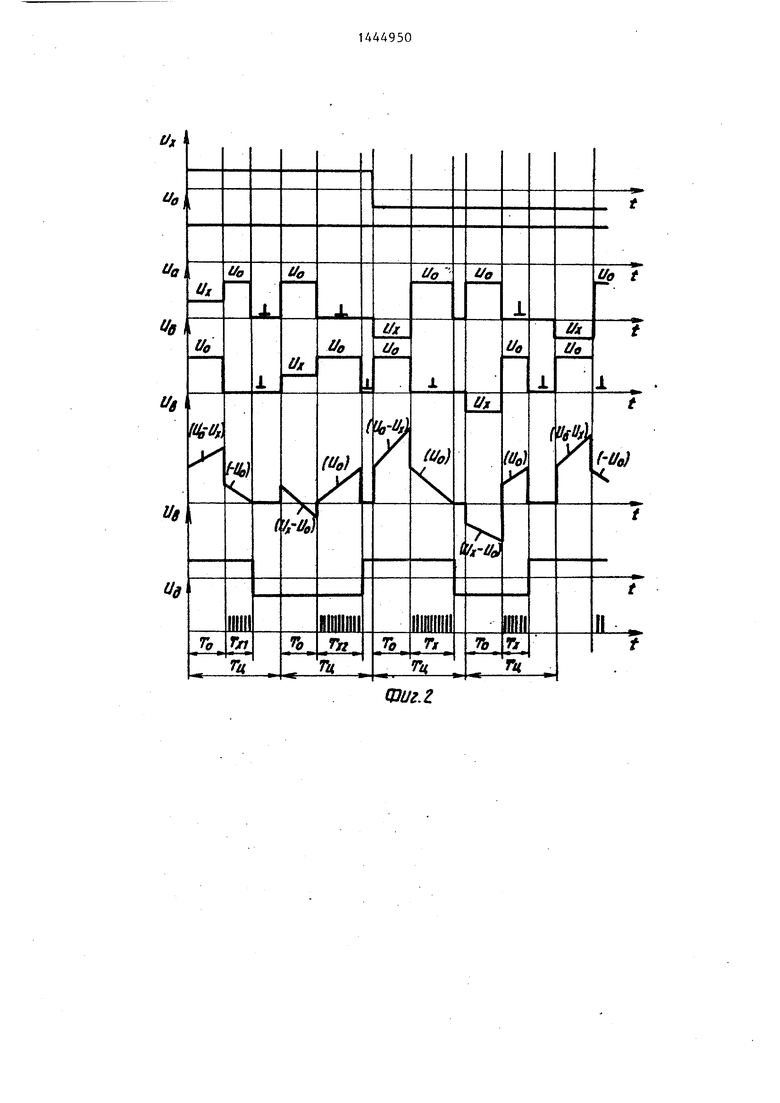

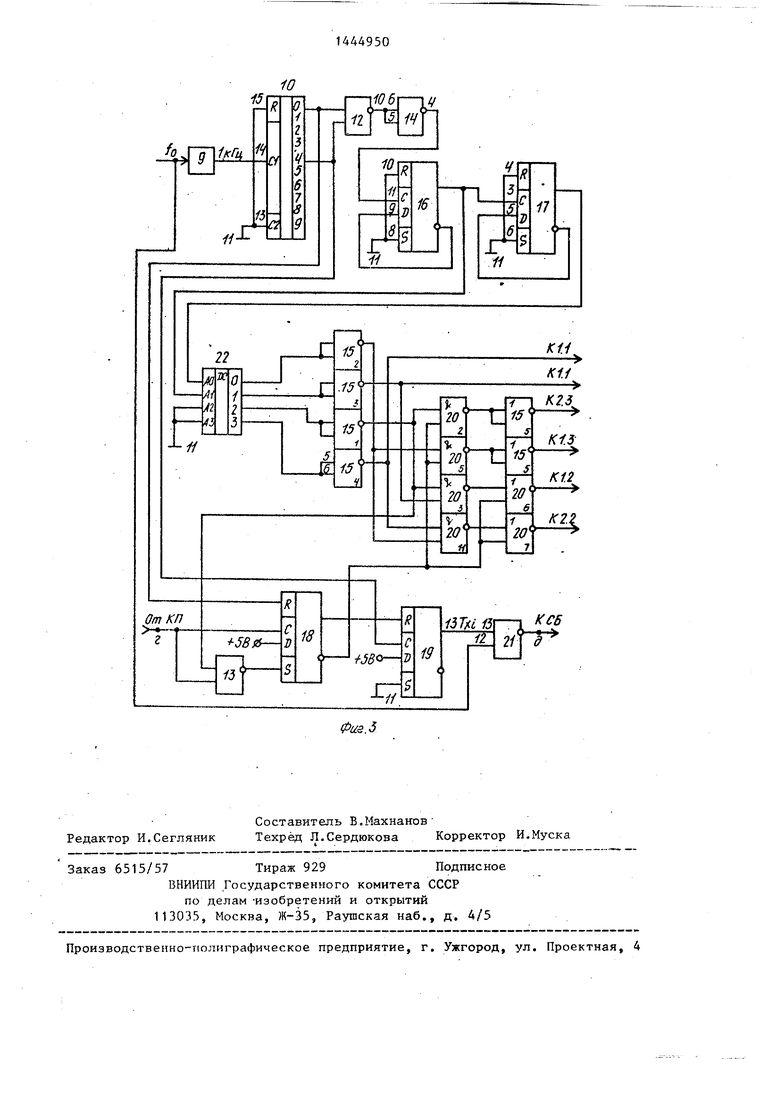

На фиг. 1 приведена структурная схема аналого-цифрового преобразователя} на фиг. 2 - временные диаграммы,- на фиг. 3 - конструкция логического блока.

Устройство содержит источник опорного напряжения 1, коммутаторы 2 и 3, интегратор 4 на операционном усилителе 5, компаратор 6, логический блок 7, на вход которого поступают импульсы опорной частоты, арифметический блок 8.

Логический блок содержит делитель -частоты 9, счетчик 10, общая шина 11 элементы РШИ-НЕ 12 и 13, инверторы 14 и 15, триггеры 16-19, элементы И-НЕ 20 и 21, дешифратор 22.

Устройство работает следунлцим образом.

В момент начала первого цикла Тц преобразователя,длительность которого постоянная, коммутаторы 2 и 3 под клк1чают ко входам интегратора 4 преобразуемое напряжение U и опорное напряжение U соответственно. По истечение такта TQ интегрирования преобразуемого напряжения выходное напряжение интегратора 4 определяется выражением:

p

т. 1

и о - и,

см

RC

RS + 1

Т„

(1)

к

где 1р - напряжение смещения операционного усилителя 5, приведенное ко входу; . 1ц - напряжение смещения компаратора 6, приведенное ко входу.

После этого начинается такт Тх1 разряда интегратора 4 опорным напряжением UQ, поступающим на инвертирующий вход, до момента равенства напряжений на входах компаратора 6. Компаратор 6 срабатьшает, когда выходное напряжение интегратора 4 .достигнет значения ..

UB Т„ + Txi и, Tj -.

- ° т СМ гр ,

RC XI RC

(2)

Подставляя (1) в (2), можно записать вьфажение для интервала времени Тх, которьй формируется логическим блоком 7

Тх,

(-UK + и,) То

и„ + 1

см

(3)

-см

и„ + 1

ем

В момент срабатывания компаратором 6 коммутаторы 2 и 3 подключают входы интегратора 4 к общей точке схемы до начала второго цикла преобразования.

Во втором цикле преобразования . коммутаторы 2 и 3 подключают опорное напряжение и„ на инверти))ую1ций вход, а преобразуемое Ux - на неиивертирую- щий вход интегратора 4. К кинцу так

напряжение на выходе интегра- будет определяться вьфаженнUe т;

UK - Ufl RC

0

-1 RC

Т« -ь 1,

Затем осуществляется разряд интегратора 4 опорным напряжением U, поступающим на неинвертирующий вход. В момент срабатывания компаратора 6 выходное напряжение интегратора 4 будет равно

+ т, - т,иДтц +

и. (1

+ ii.) RC

j-CM

RC

Т. «2

Ил + Iv

о .

Подставляя (4) в (5), получим выражение для интервала времени Т

(6

C-Ux.-f Ue) То -1емТ,

и„ - 1,

-

U« - 1,

-см в

арифметическом блоке 8 формирукод, пропорциональный сумме

(6

Схема преобразователя весьма проста и содержит в аналоговой части ре- зистор R и конденсатор С, точность которых не влияет на результат преобразования, а также операционный усилитель 5 и компаратор 6, напряжения смещения которых практически не вли- яют на точность преобразования. Так например, в соответствии с (7) напряжение смещения операционного усилителя 5, равно 5 мВ, при выборе опорного напряжения Uj,, равного 5В, вносит относйтель1пгю погрешность, не превьшакщую 1 Ь .

Алгоритм работы аналого-цифрового преобразователя достаточно ком- gQ пактен, не требует начальной установ- ход которого является шиной импуль- ки преобразователя перед циклом из- сов опорной частоты, а первая и мерения, а также введения цепи анало- вторая группы выходов соединены с говой автокоррекции, которая услож- управляющими входами первого и вто55

няет устройство и снижает его уйтой- чивость. Кроме того, данный-алгоритм позволяет снизить погрешность из-за абсорбции конденсатора С интегратора 4, поскольку среднее значение

рого коммутаторов соответственно, а третий выход подключен к входу ариф- метическбго блока, отличают щ и и с я тем, что, с целью.повышения точности и упрощения устройства.

ю

напряжения на конденсаторе С за цикл преобразования равно нулю.

При этом, логический блок 7 может быть реализован в соответствии с фиг. 3 при выбранных длительности цикла Тц 10 мс и длительности такта Тд 4 мс. Коэффициент деления делителя частоты 9 определяется значением опорной частоты fj,. Каждый четвертый и десятьЬ импульсы, поступающие на вход счетчика Ю записы- ваются в счетчик, собранньй на триггерах 16 и 17, выходной код которого 15 управляют дешифратором 22 (К561ИД1). С помощью триггеров 18 и 19 по выходному сигналу компаратора 6 формируются интервалы времени Т, которые заполняют импульсами опорной частоты

20

fд. Число импульсов подсчитывается

(7)

в арифметическом блоке 8, в качестве которого может быть использован двоичный суммирующий счетчик. Элеме нты ИЛИ-НЕ 12 и 13 и инверторы 14 и 15, (6) 25 а также элементы И-НЕ 20 служат для

формирования сигналов управления ключами, на которых собраны коммутаторы 2 и 3. Первая цифра в обозначении сигналов управления показывает 30 номер коммутатора, а вторая - номер ключа, который соответствует входам коммутаторов 2 и 3 сверху вниз, как показано на фиг. 1.

Формула изобретения

ход которого является шиной импуль- сов опорной частоты, а первая и вторая группы выходов соединены с управляющими входами первого и второго коммутаторов соответственно, а третий выход подключен к входу ариф- метическбго блока, отличают щ и и с я тем, что, с целью.повышения точности и упрощения устройства.

в нем второй вход компаратора объединен с вторым входом интегратора и подключен к выходу второго коммутатора.

2, Преобразователь по п.1, отличающийся тем, что логический блок выполнен на счетчике, триггерах, инверторах, дешифраторе, элементе ИЛИ-НЕ, И-НЕ и делителе частоты, вход которого является вторым входом блока, а выход соединен с первым счетным входом счетчика, первый выкод которого соединен с первым входом первого элемента w.. ИЛИ-НЕ и С-входом первого триггера, которого соединен с прямым выходом второго триггера, D-вход - с шиной питания, S-вход - с общей шиной, а выход подключен к первому входу первого элемента И-НЕ, выход которого является третьим выходом блока, а второй вход является вторым входом блока, второй- выход счетчика соединен с вторым входом первого элемента ИЛИ-НЕ и R-входом второго триггера, С-вход которого объединен с первым входом второго элемента ИЛИ-НЕ и является первым входом блока, D-вход соединен с шиной питания, а S-вход - с выходом второго элемента ИЛИ-НЕ, второй вход которого объединен с первыми входами вто- рого и третьего элементов И-НЕ и через первый инвертор подключен к первому выходу дешифратора, второй выход которого через второй инвертор соединен с первыми входами четвертого и пятого элементов И-НЕ, третий выход черед третий инвертор соединен

с вторым входом третьего элемента И-НЕ и является первым выходом второй группы вькодов блока, четвертый выход через четвертый инвертор соединен с вторым входом червертого элемента И-НЕ и является первым вькодом группы выходов блока, вторые входы второго и пятого элементов И-НЕ объединены с первыми входами шестого и седьмого элементов И-НЕ и подключены к инверсному выходу второго триггера, выходы второго и пятого элементов И-НЕ соединены соответственно с входами пятого и шестого инверторов, выходы которых являются вторыми выходами соответственно первой и второй групп выходов блока, а вторые входы шестого и седьмого

элементов И-НЕ соединены соответст- венно с выходами третьего и четвертого элементов И-НЕ, причем выходы шестЬго и седьмого элементов лвляют- ся третьими выходами первой и второй

групп выходов соответственно, а пер- вьй и второй входы дешифратора соединены соответственно с прямыми выходами третьего и четвертого триггеров, третий и четвертый вх;оды дешифратора подключены к общей шине, инверс- ньй выход третьего триггера соединен с его D-входом, С-вход подключен к прямому выходу четвертого триггера, инверсньй выход которого соединен с его D-входом, С-вход через седьмой инвертор подключен к выходу первого элемента ИЛИ-НЕ, а R- и S-входы третьего и четвертого триггеров подключены к общей шине, вход сброса и

второй счетньй вход счетчика соединен с общей шиной.

Ve

Фиг. г

к

| Измерение, контроль, автоматизация | |||

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Приборы и техника эксперимента | |||

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Пуговица | 0 |

|

SU83A1 |

Авторы

Даты

1988-12-15—Публикация

1987-07-22—Подача