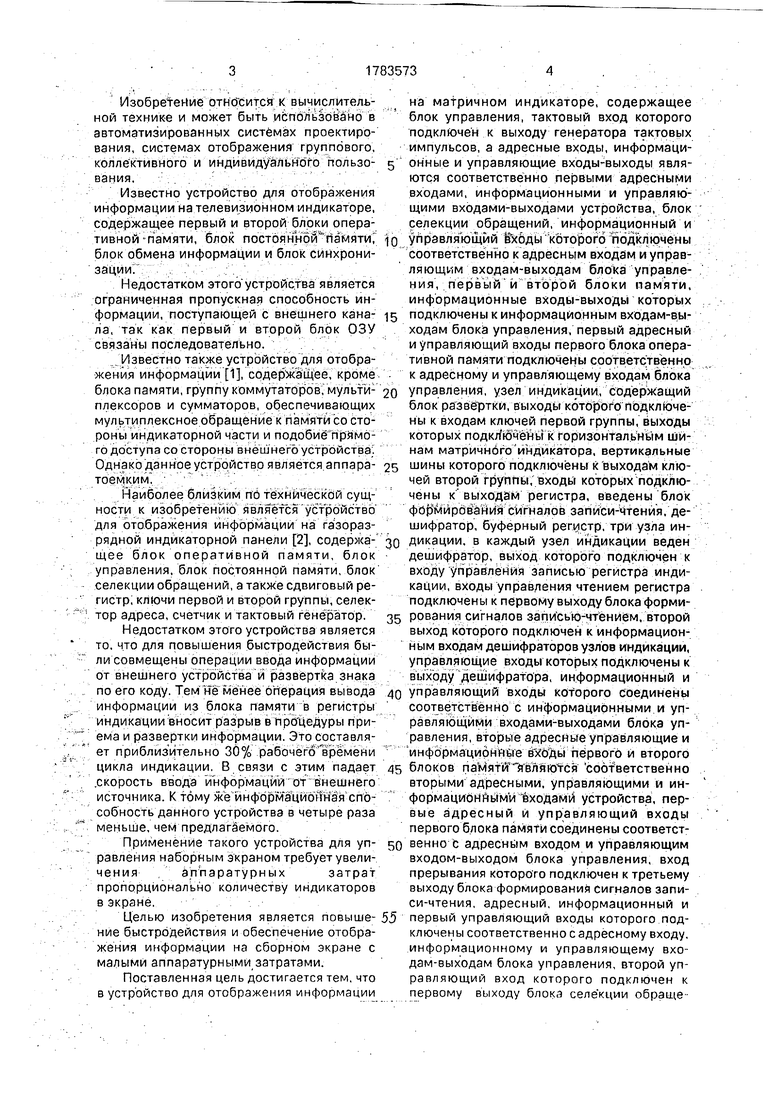

Фиг.1

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах проектирования, системах отображения группового, коллективного и индивидуального пользования.

Известно устройство для отображения информации на телевизионном индикаторе, содержащее первый и второй блоки оперативной-памяти, блок постоянной памяти, блок обмена информации и блок синхронизации.

Недостатком этого устройства является ограниченная пропускная способность информации, поступающей с внешнего канала, так как первый и второй блок ОЗУ связаны последовательно.

Известно также устройство для отображения информации 1, содержащее, кроме блока памяти, группу коммутаторов, мультиплексоров и сумматоров, обеспечивающих мультиплексное обращение к памяти со стороны индикаторной части и подобие прямого доступа со стороны внешнего устройства Однако данное устройство является аппара- тоемким.

Наиболее близким по технической сущности к изобретению является устройство для отображения информации на газоразрядной индикаторной панели 2, содержащее блок оперативной памяти, блок управления, блок постоянной памяти блок селекции обращений, а также сдвиговый регистр, ключи первой и второй группы, селектор адреса,счетчик и тактовый генератор.

Недостатком этого устройства является то. что для повышения быстродействия были совмещены операции ввода информации от внешнего устройства и развертка знака по его коду Тем не менее операция вывода информации из блока памяти в регистры индикации вносит разрыв в процедуры приема и развертки информации Это составляет приблизительно 30% рабочего времени цикла индикации В связи с этим падает скорость ввода информации от внешнего источника. К тому же информационная способность данного устройства в четыре раза меньше, чем предлагаемого

Применение такого устройства для управления наборным экраном требует увеличенияаппаратурныхзатратпропорционально количеству индикаторов в экране

Целью изобретения является повышение быстродействия и обеспечение отображения информации на сборном экране с малыми аппаратурными затратами.

Поставленная цель достигается тем что в устройство для отображения информации

на матричном индикаторе, содержащее блок управления, тактовый вход которого подключен к выходу генератора тактовых импульсов, а адресные входы, информационные и управляющие входы-выходы являются соответственно первыми адресными входами, информационными и управляющими входами-выходами устройства, блок селекции обращений, информационный и

0 управляющий &ходы которого подключены соответственно к адресным входам и управляющем входам-выходам блока управления, первый и второй блоки памяти, информационные входы-выходы которых

5 подключены к информационным входам-выходам блока управления, первый адресный и управляющий входы первого блока оперативной памяти подключены соответственно к адресному и управляющему входам блока

0 управления, узел индикации, содержащий блок развертки, выходы которого подключены к входам ключей первой группы, выходы которых подключены к горизонтальным шинам матричного индикатора, вертикальные

5 шины которого подключены к выходам ключей второй группы, входы которых подключены к выходам регистра, введены блок формирования сигналов записи-чтения, дешифратор, буферный регистр, три узла ин0 дикации, в каждый узел индикации веден дешифратор, выход которого подключен к входу управления записью регистра индикации, входы управления чтением регистра подключены к первому выходу блока форми5 рования сигналов записью-чтением, второй выход которого подключен к информационным входам дешифраторов узлов индикации, управляющие входы которых подключены к выходу дешифратора, информационный и

0 управляющий входы которого соединены соответственно с информационными и управляющими входами-выходами блока управления, вторые адресные управляющие и информационные ВУОДЫ первого и второго

5 блоков памят1/Г йвляются соответственно вторыми адресными, управляющими и информационными входами устройства, первые адресный и управляющий входы первого блока памяти соединены соответст- 50 венно с адресным входом и управляющим входом-выходом блока управления, вход прерывания которого подключен к третьему выходу блока формирования Сигналов записи-чтения адресный информационный и

5 первый управляющий входы которого подключены соответственно с адресному входу, информационному и управляющему входам-выходам блока управления, второй управляющий вход которого подключен к первому выходу блока селекции обраще

ний. второй и третий выходы которого подключены к входам выборки соответственно первого и второго блоков памяти, а четвертый выход подключен к первому управляющему входу генератора тактовых импульсов и является выходом Готовность устройства, второй управляющий вход генератора тактовых импульсов является третьим управляющим входом устройства, пятый выход блока селекции обращений подключен к управляющему входу буферного регистра, информационный вход которого соединен с информационными входами регистров узлов индикации, входы выборки которых под- ключены соответственно к шестому, седьмому, восьмому и девятому выходам блока селекции обращений, тактовые входы блоков развертки узлов индикации подключены к третьему выходу блока формирования сигналов записи-чтения.

Введение двух блоков памяти, блока формирования сигналов записи-чтения, состоящего из таймера, дешифратора и триггера, позволило совместить операции ввода информации и развертки изображения, увеличить информационную емкость индикатора (до размеров матрицы 128x128 элементов отображения), ввод информации проводить в режиме прямого доступа к памяти, что позволяет отображать информацию с частотой кадров, близкой к телевизионной.

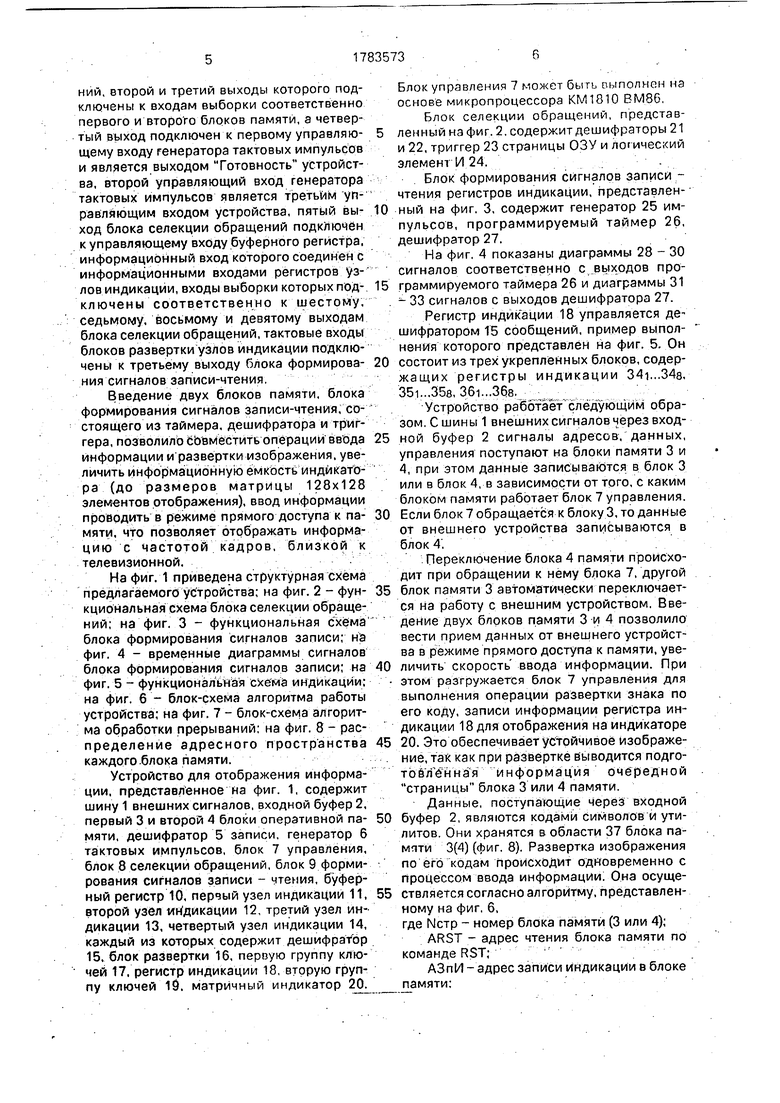

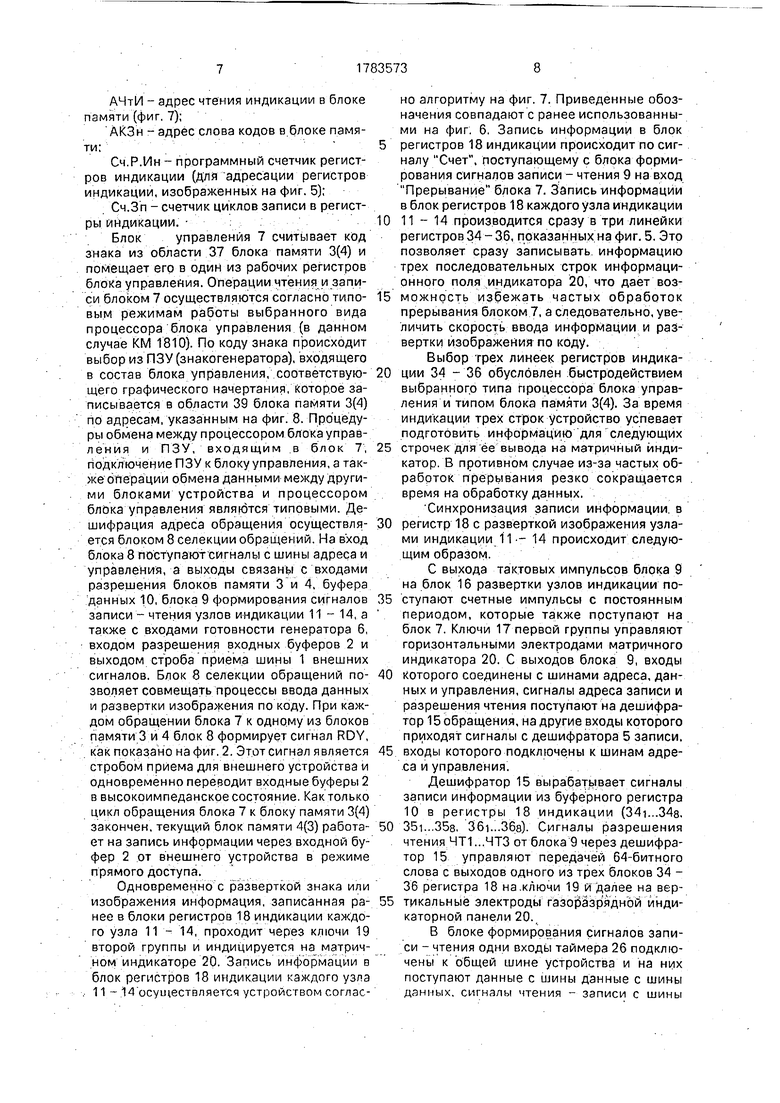

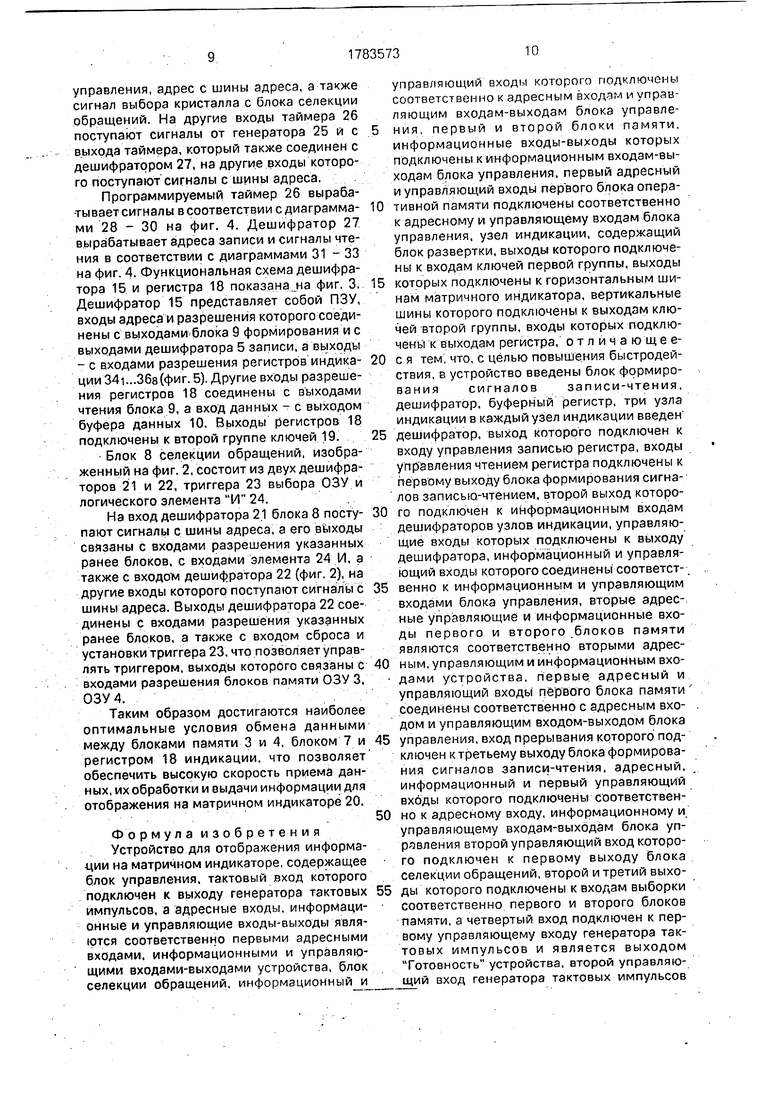

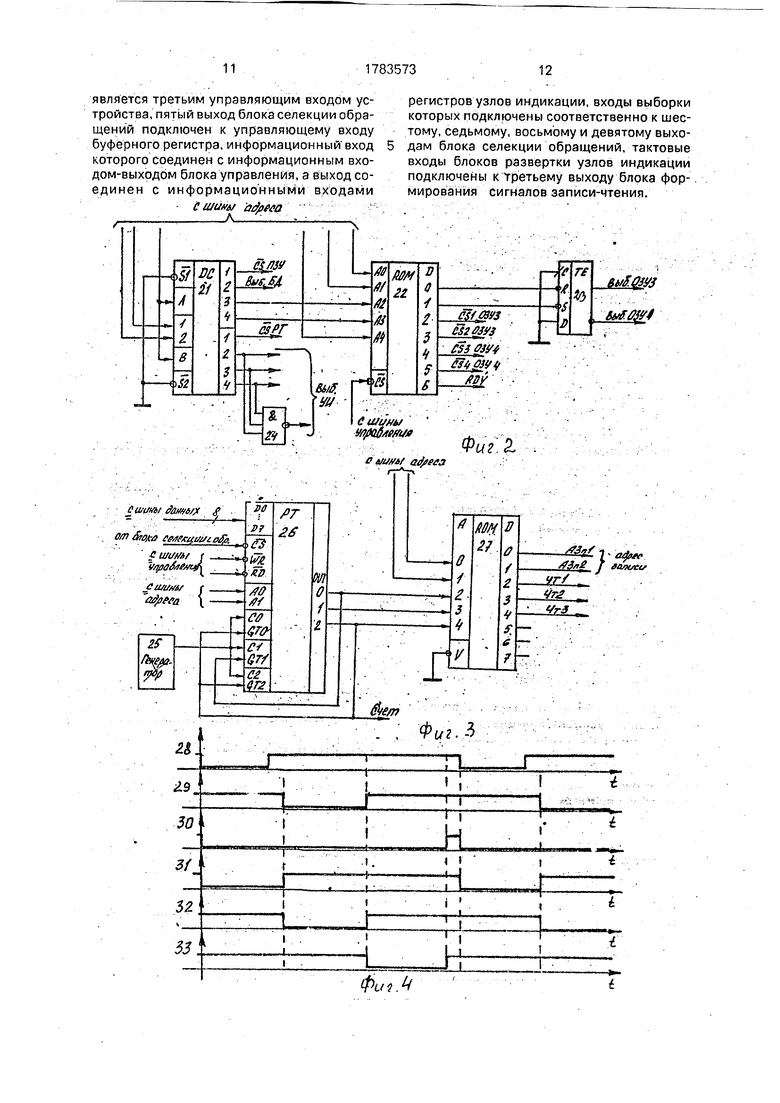

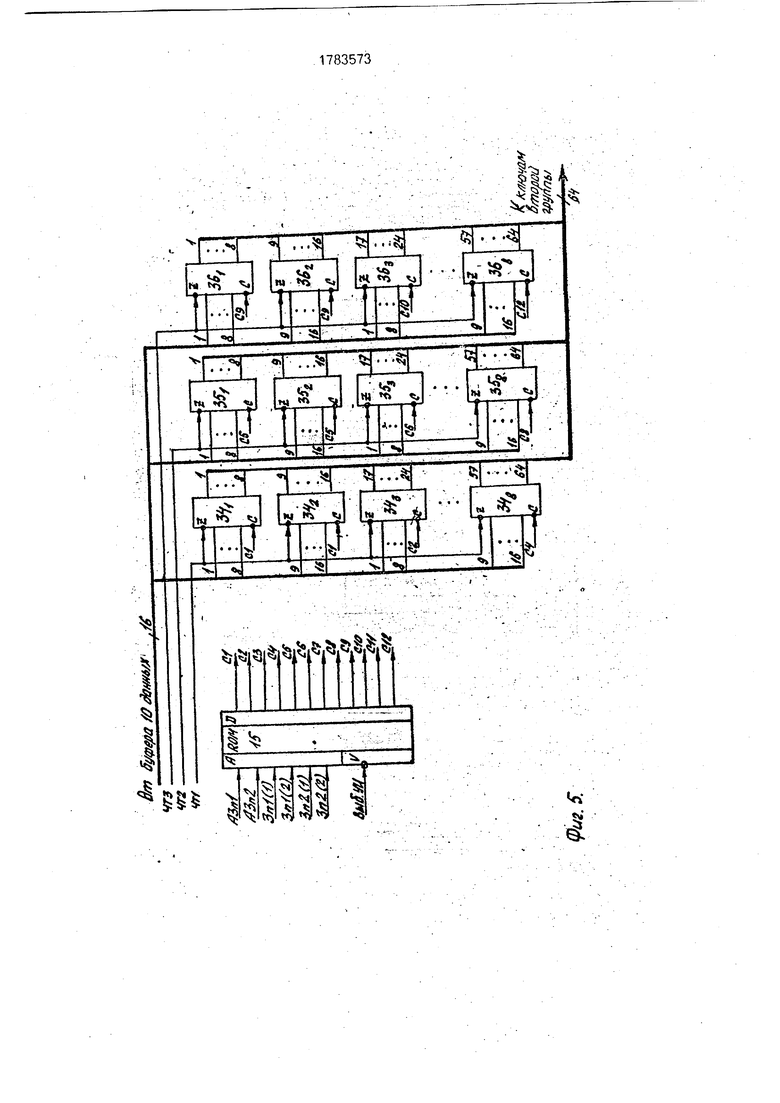

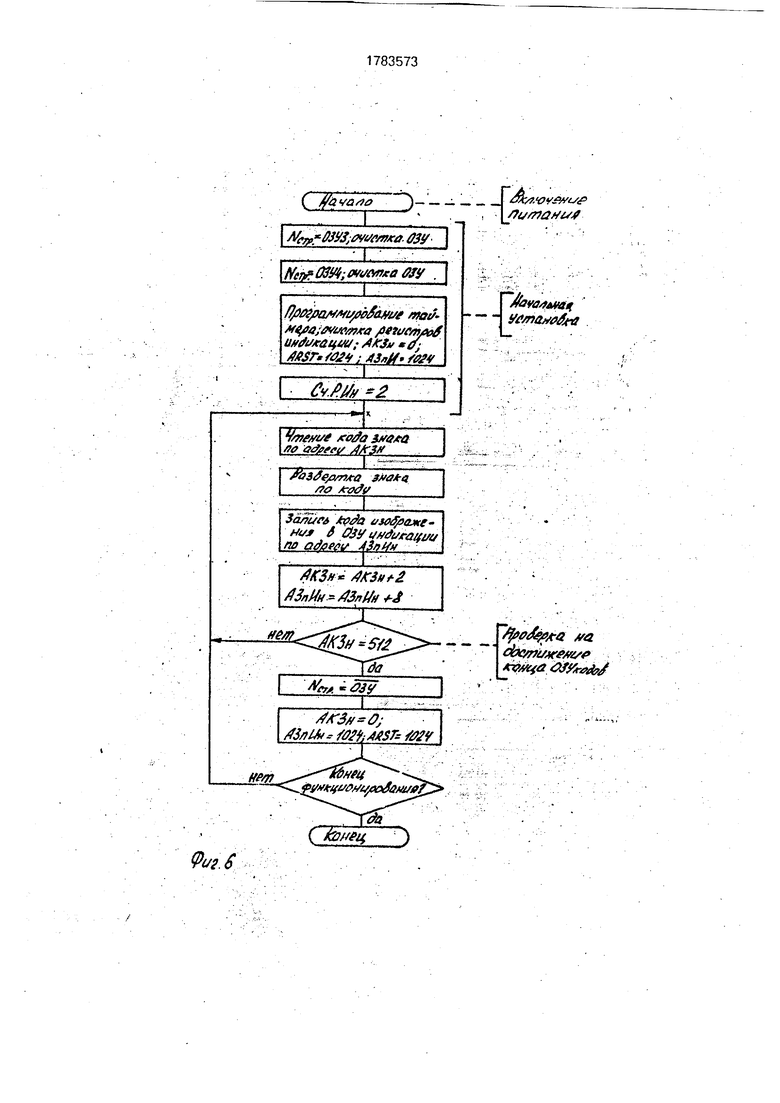

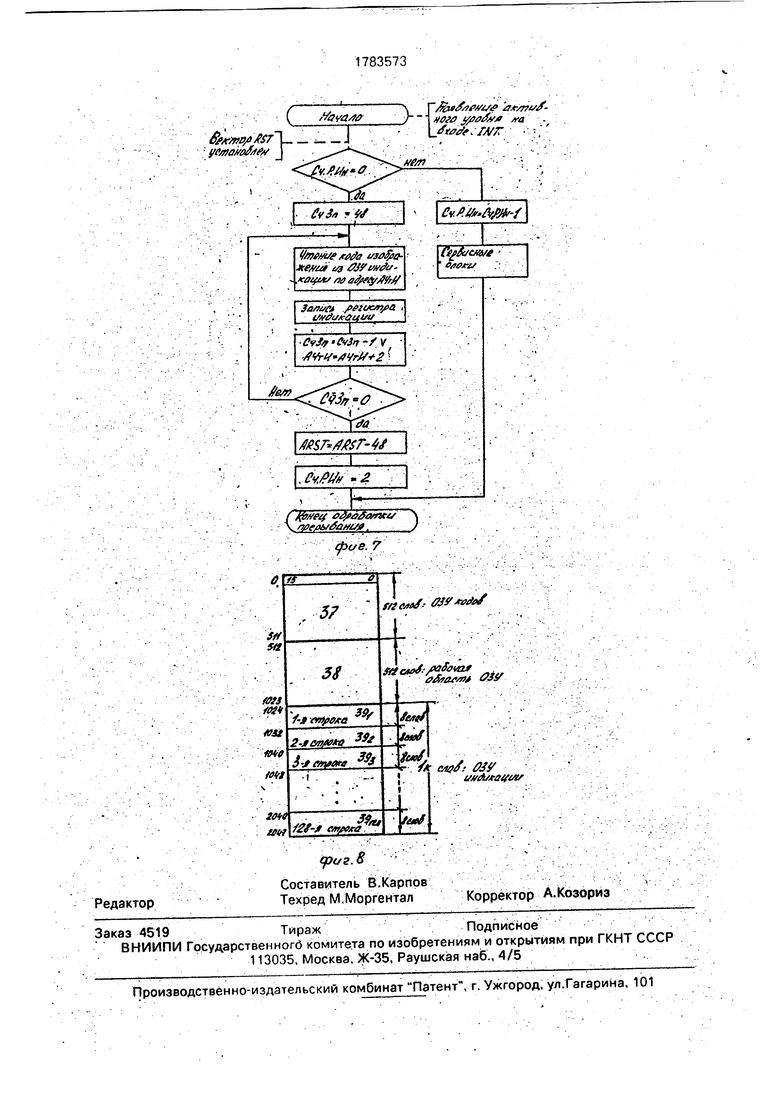

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока селекции обращений; на фиг. 3 - функциональная схема блока формирования сигналов записи; на фиг. 4 - временные диаграммы сигналов блока формирования сигналов записи; на фиг. 5 - функциональная схема индикации; на фиг. 6 - блок-схема алгоритма работы устройства; на фиг. 7 - блок-схема алгоритма обработки прерываний; на фиг. 8 - распределение адресного пространства каждого блока памяти.

Устройство для отображения информации, представленное на фиг. 1, содержит шину 1 внешних сигналов, входной буфер 2, первый 3 и второй 4 блоки оперативной памяти, дешифратор 5 записи, генератор 6 тактовых импульсов, блок 7 управления, блок 8 селекции обращений, блок 9 формирования сигналов записи - чтения, буферный регистр 10, перчый узел индикации 11, второй узел индикации 12, третий узел индикации 13, четвертый узел индикации 14, каждый из которых содержит дешифратор 15. блок развертки 16, первую группу ключей 17, регистр индикации 18, вторую группу ключей 19. матричный индикатор 20.

Блок управления 7 может быгь выполнен на основе микропроцессора КМ1810 BM8G

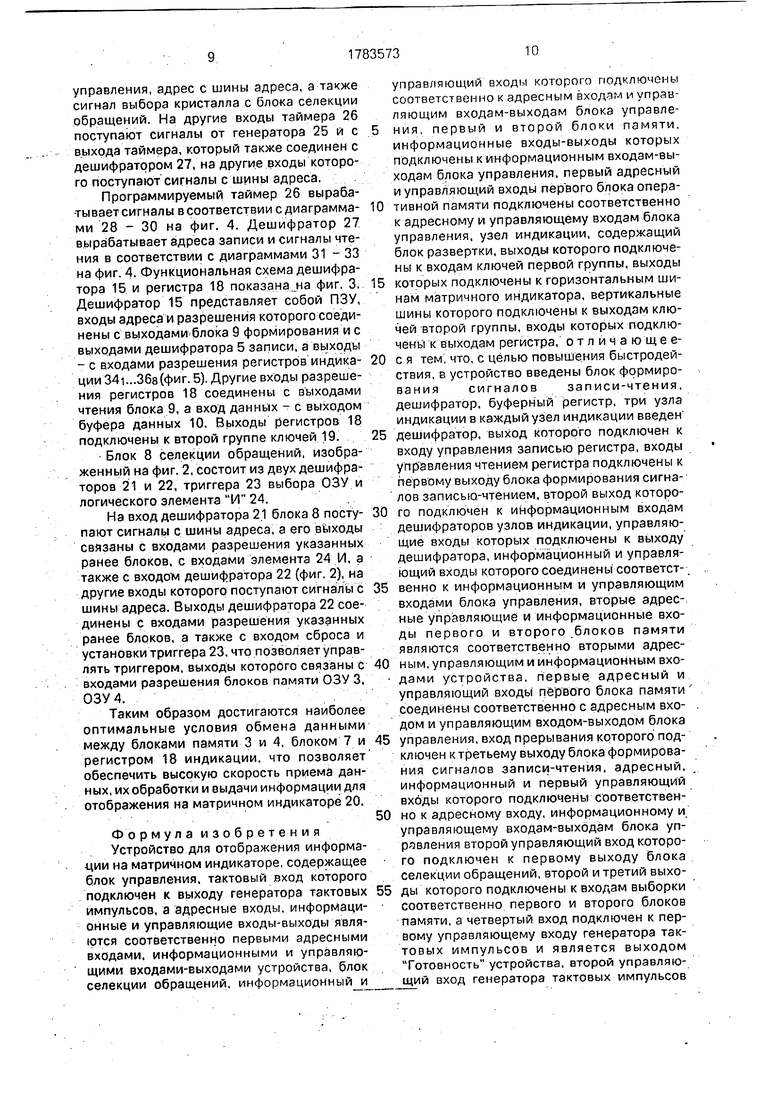

Блок селекции обращений, представ- 5 ленный на фиг. 2. содержит дешифраторы 21 и 22, триггер 23 страницы ОЗУ и логический элемент И 24.

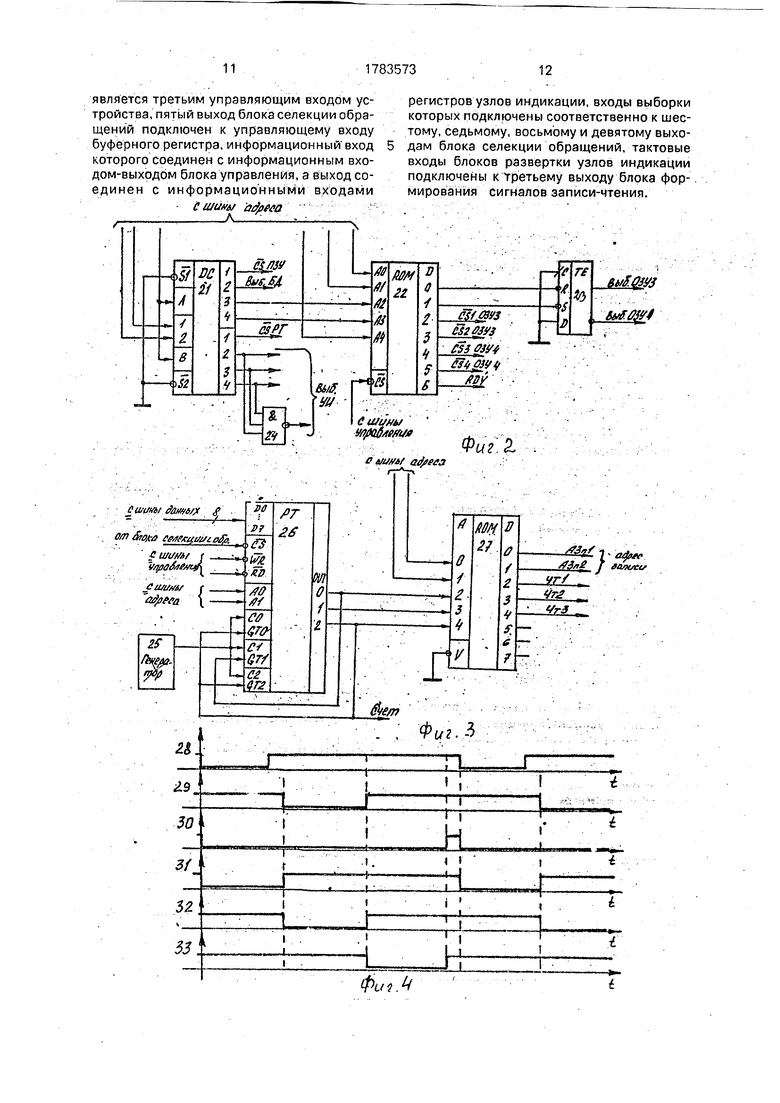

Блок формирования сигналов записи - чтения регистров индикации, представлен0 ный на фиг. 3, содержит генератор 25 импульсов, программируемый таймер 26, дешифратор 27.

На фиг. 4 показаны диаграммы 28 - 30 сигналов соответственно с выходов про5 граммируемого таймера 26 и диаграммы 31 - 33 сигналов с выходов дешифратора 27.

Регистр индикации 18 управляется дешифратором 15 сообщений, пример выполнения которого представлен на фиг. 5. Он

0 состоит из трех укрепленных блоков, содер- жащих регистры индикации 34i...34s, 35i...35e, 36i...36e.

Устройство работает следующим образом. С шины 1 внешних сигналов через вход5 ной буфер 2 сигналы адресов, данных, управления поступают на блоки памяти 3 и 4, при этом данные записываются в блок 3 или в блок 4, в зависимости от того, с каким блоком памяти работает блок 7 управления.

0 Если блок 7 обращается к блоку 3, то данные от внешнего устройства записываются в блок 4.

Переключение блока 4 памяти происходит при обращении к нему блока 7, другой

5 блок памяти 3 автоматически переключается на работу с внешним устройством. Введение двух блоков памяти 3 и 4 позволило вести прием данных от внешнего устройства в режиме прямого доступа к памяти, уве0 личить скорость ввода информации. При этом разгружается блок 7 управления для выполнения операции развертки знака по его коду, записи информации регистра индикации 18 для отображения на индикаторе

5 20. Это обеспечивает устойчивое изображение, так как при развертке выводится подго- то§лченная информация очередной страницы блока 3 или 4 памяти.

Данные, поступающие через входной

0 буфер 2, являются кодами символов и ути- литов. Они хранятся в области 37 блока па- мпти 3(4) (фиг. 8). Развертка изображения по его кодам происходит одновременно с процессом ввода информации. Она осуще5 ствляется согласно алгоритму, представленному на фиг. 6, где Метр - номер блока памяти (3 или 4);

ARST - адрес чтения блока памяти по команде RST;

АЗпИ - адрес записи индикации в блоке памяти;

АЧтИ - адрес чтения индикации в блоке памяти (фиг. 7);

АКЗн - адрес слова кодов в блоке памяти;

Сч Р.Ин - программный счетчик регистров индикации (для адресации регистров индикации, изображенных на фиг. 5);

Сч.Зп - счетчик циклов записи в регистры индикации.

Блок управления 7 считывает код знака из области 37 блока памяти 3(4) и помещает его в один из рабочих регистров блока управления. Операции чтения и записи блоком 7 осуществляются согласно типо- вым режимам работы выбранного вида процессора блока управления (в данном случае КМ 1810). По коду знака происходит выбор из ПЗУ (знакогенератора), входящего в состав блока управления, соответствую- щего графического начертания, которое записывается в области 39 блока памяти 3(4) по адресам, указанным на фиг. 8. Процедуры обмена между процессором блока управ- ления и ПЗУ, входящим в блок 7, подключение ПЗУ к блоку управления, а также операции обмена данными между другими блоками устройства и процессором блока управления являются типовыми. Дешифрация адреса обращения осуществля- ется блоком 8 селекции обращений. На вход блока 8 поступают сигналы с шины адреса и управления, а выходы связаны с входами разрешения блоков памяти 3 и 4, буфера данных 10, блока 9 формирования сигналов записи - чтения узлов индикации 11 - 14, а также с входами готовности генератора 6, входом разрешения входных буферов 2 и выходом строба приема шины 1 внешних сигналов. Блок 8 селекции обращений по- зволяет совмещать процессы ввода данных и развертки изображения по коду. При каждом обращении блока 7 к одному из блоков памяти 3 и 4 блок 8 формирует сигнал RDY, как показано на фиг. 2. Этот сигнал является стробом приема для внешнего устройства и одновременно переводит входные буферы 2 в высокоимпеданское состояние Как только цикл обращения блока 7 к блоку памяти 3{4) закончен, текущий блок памяти 4(3) работа- ет на запись информации через входной буфер 2 от внешнего устройства в режиме прямого доступа.

Одновременно с разверткой знака или изображения информация, записанная ра- нее в блоки регистров 18 индикации каждого узла 11 - 14, проходит через ключи 19 второй группы и индицируется на матричном индикаторе 20. Запись информации в блок регистров 18 индикации каждого узла 11-14 осуществляется устройством согласно алгоритму на фиг. 7. Приведенные обозначения совпадают с ранее использованными на фиг. 6. Запись информации в блок регистров 18 индикации происходит по сигналу Счет, поступающему с блока формирования сигналов записи - чтения 9 на вход Прерывание блока 7. Запись информации в блок регистров 18 каждого узла индикации 11-14 производится сразу в три линейки регистров 34 - 36, показанных на фиг. 5. Это позволяет сразу записывать информацию трех последовательных строк информационного поля индикатора 20, что дает возможность избежать частых обработок прерывания блоком 7, а следовательно, увеличить скорость ввода информации и развертки изображения по коду.

Выбор грех линеек регистров индикации 34 - 36 обусловлен быстродействием выбранного типа процессора блока управления и типом блока памяти 3(4). За время индикации трех строк устройство успевает подготовить информацию для следующих строчек для ее вывода на матричный индикатор В противном случае из-за частых обработок прерывания резко сокращается время на обработку данных.

Синхронизация записи информации в регистр 18с разверткой изображения узлами индикации 11-14 происходит следующим образом.

С выхода тактовых импульсов блока 9 на блок 16 развертки узлов индикации поступают счетные импульсы с постоянным периодом, которые также поступают на блок 7. Ключи 17 первой группы управляют горизонтальными электродами матричного индикатора 20. С выходов блока 9, входы которого соединены с шинами адреса, данных и управления, сигналы адреса записи и разрешения чтения поступают на дешифратор 15 обращения, на другие входы которого приходят сигналы с дешифратора 5 записи. входы которого подключены к шинам адреса и управления.

Дешифратор 15 вырабатывает сигналы записи информации из буферного регистра 10 в регистры 18 индикации (34ь .34в, 35i. 35s, 36i...36s). Сигналы разрешения чтения ЧТ1...ЧТЗ от блока 9 через дешифратор 15 управляют передачей 64-битного слова с выходов одного из трех блоков 34 - 36 регистра 18 на ключи 19 и далее на вертикальные электроды газоразрядной индикаторной панели 20.

В блоке формирования сигналов записи - чтения одни входы таймера 26 подключены к общей шине устройства и на них поступают данные с шины данные с шины данных, сигналы чтения - записи с шины

управления, адрес с шины адреса, а также сигнал выбора кристалла с блока селекции обращений. На другие входы таймера 26 поступают сигналы от генератора 25 и с выхода таймера, который также соединен с дешифратором 27, на другие входы которого поступают сигналы с шины адреса.

Программируемый таймер 26 вырабатывает сигналы в соответствии с диаграммами 28 - 30 на фиг. 4. Дешифратор 27 вырабатывает адреса записи и сигналы чтения в соответствии с диаграммами 31-33 на фиг. 4. Функциональная схема дешифратора 15 и регистра 18 показана .на фиг. 3. Дешифратор 15 представляет собой ПЗУ, входы адреса и разрешения которого соединены с выходами блока 9 формирования и с выходами дешифратора 5 записи, а выходы - с входами разрешения регистров индикации З41...36в(фиг. 5). Другие входы разрешения регистров 18 соединены с выходами чтения блока 9, а вход данных - с выходом буфера данных 10. Выходы регистров 18 подключены к второй группе ключей 19.

Блок 8 селекции обращений, изображенный на фиг. 2, состоит из двух дешифраторов 21 и 22, триггера 23 выбора ОЗУ и логического элемента И 24.

На вход дешифратора 21 блока 8 поступают сигналы с шины адреса, а его выходы связаны с входами разрешения указанных ранее блоков, с входами элемента 24 И, а также с входом дешифратора 22 (фиг, 2), на другие входы которого поступают сигналы с шины адреса. Выходы дешифратора 22 соединены с входами разрешения указанных ранее блоков, а также с входом сброса и установки триггера 23. что позволяет управлять триггером, выходы которого связаны с входами разрешения блоков памяти ОЗУ 3, ОЗУ 4.

Таким образом достигаются наиболее оптимальные условия обмена данными между блоками памяти 3 и 4, блоком 7 и регистром 18 индикации, что позволяет обеспечить высокую скорость приема данных, их обработки и выдачи информации для отображения на матричном индикаторе 20.

Формула изобретения Устройство для отображения информации на матричном индикаторе, содержащее блок управления, тактовый вход которого подключен к выходу генератора тактовых импульсов, а адресные входы, информационные и управляющие входы-выходы являются соответственно первыми адресными входами, информационными и управляющими входами-выходами устройства, блок селекции обращений, информационный и

управляющий входы которого подключены соответственно к адресным входам и управляющим входам-выходам блока управле- 5 ния, первый и второй блоки памяти, информационные входы-выходы которых подключены к информационным входам-выходам блока управления, первый адресный и управляющий входы первого блока опера0 тивной памяти подключены соответственно к адресному и управляющему входам блока управления, узел индикации, содержащий блок развертки, выходы которого подключены к входам ключей первой группы, выходы

5 которых подключены к горизонтальным шинам матричного индикатора, вертикальные шины которого подключены к выходам ключей второй группы, входы которых подключены к выходам регистра, отличающее0 с я тем, что, с целью повышения быстродействия, в устройство введены блок формиро- вания сигналов записи-чтения, дешифратор, буферный регистр, три узла индикации в каждый узел индикации введен

5 дешифратор, выход которого подключен к входу управления записью регистра, входы управления чтением регистра подключены к первому выходу блока формирования сигналов записью-чтением, второй выход которо0 го подключен к информационным входам дешифраторов узлов индикации, управляющие входы которых подключены к выходу дешифратора, информационный и управляющий входы которого соединены соответст-.

5 венно к информационным и управляющим входами блока управления, вторые адресные управляющие и информационные входы первого и второго блоков памяти являются соответственно вторыми адрес0 ным, управляющим и информационным вхо- дами устройства, первые адресный и управляющий входы первого блока памяти соединены соответственно с адресным входом и управляющим входом-выходом блока

5 управления, вход прерывания которого подключен к третьему выходу блока формирования сигналов записи-чтения, адресный, информационный и первый управляющий входы которого подключены соответствен0 но к адресному входу, информационному и управляющему входам-выходам блока управления второй управляющий вход которого подключен к первому выходу блока селекции обращений, второй и третий выхо5 ды которого подключены к входам выборки соответственно первого и второго блоков памяти, а четвертый вход подключен к первому управляющему входу генератора тактовых импульсов и является выходом Готовность устройства, второй управляющий вход генератора тактовых импульсов

является третьим управляющим входом устройства, пятый выход блока селекции обращений подключен к управляющему входу буферного регистра, информационный вход которого соединен с информационным входом-выходом блока управления, а выход соединен с информационными входами С шиш афыа

регистров узлов индикации, входы выборки которых подключены соответственно к шестому, седьмому, восьмому и девятому выходам блока селекции обращений, тактовые входы блоков развертки узлов индикации подключены к третьему выходу блока формирования сигналов записи-чтения.

Bt/ffgm Ј#f№/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на матричном индикаторе | 1990 |

|

SU1835555A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ГАЗОРАЗРЯДНОЙ ИНДИКАТОРНОЙ ПАНЕЛИ | 1993 |

|

RU2069018C1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для отображения информации | 1988 |

|

SU1566404A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ГАЗОРАЗРЯДНОЙ ИНДИКАТОРНОЙ ПАНЕЛИ | 1992 |

|

RU2042216C1 |

| Устройство для отображения информации | 1988 |

|

SU1603365A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1585830A1 |

| Устройство для отображения информации | 1986 |

|

SU1434423A1 |

Использование автоматика и вычислительная техника, система сбора и отображёния информации Сущность изобретения- устройство содержит входной буфер 2, два блока памяти 3 и 4, блок управления 7, генератор тактовых импульсов 6, блок 8 селекции обращении, дешифратор записи 5, блок формирования сигналов записи 9, буферный регистр 10, узлы 11-14 индикации, каждый из которых содержит две группы ключей 17, 19 индикаторную панель 20, блок 16 развертки, регистр 18 индикации дешифратор 15 обращений 2-3-7 8-9-11,2- 4-7, 8-5-11,5-12, 5-13, 5-14, 9-7. 8-6-68-2,8- 10, 8-14, 8-13 8-12,8-11,10-14,10-13 10-12 10-11, 15-18-19-20, 16-17-20, 7-9 8 ил

еи/ию/ tfowt/jr f

o/n &o#a tffitfttfta/iofo.

с шаш/ r Ъ/раАггмЖ

ЈlWtft/

atjafea

Cff 4W

C

ev

C2 $T2

с at/fft/ ad/еез

ЈЈv#

УГ/

eawcc/

VrЈ

Vr3

p

со f-- ю

со

СО

г /9Mtop0/ mtotftg u/ff

f /Уачал0

I

I

,0Щ0у&/ггх0 03У I.

fort OMi0MM e 0м .

ff/)&/ a#/w/x Јawt мфа;0лх / ха /} 9vf/nA j

U#Jt/AratfMe/; JX3 0; M$r Majf /&V

&Ш 2

хода iff a fa

ffff Q&ffiS d/C3#

1

JfosJe/vrJAra (r

Jbpdt vsafeajKfHVJ 6 Ctiy wdi/raift/t/ no adefw jSntttt

4f3nt2 43 HH 43nfa+J

/ttolk MM

Фиг 6

I &/t.Vv&VtJ P

Жгм4л#а4 J yt/na#0dtn

fy0tfy#& #& dxyne/AeffM/t хъмцб ЖЯпЖ/

. .( /л, „ r& Atfwt/f a /ni//.

. V ™ У4МГ}-- мм юаА, „а .

&W #/V- ---J- . . -.;; ife/rtawfjfs/ J

t/jafya- xwttf w 0jyiw v. /x aJ/wsfMrtf

Зали& .peiu&n/ o. t/#0c/#gutsi/

J.

Cf/fMrf/y AVrV-/tyrM+2

(tfweef etyajamtts . у/заг/ц/г&г/иь.}

(five.

| Устройство для отображения информации | 1984 |

|

SU1290402A1 |

| кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1992-12-23—Публикация

1989-11-04—Подача