VI Ю

OJ CJ 00

ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| ЧАСТОТНО-ФАЗОВОЕ РЕЛЕ | 2016 |

|

RU2641096C2 |

| ЧАСТОТНО-ФАЗОВОЕ РЕЛЕ | 2003 |

|

RU2239904C1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство для фазовой синхронизации | 1983 |

|

SU1149425A2 |

| Цифровой фазометр | 1989 |

|

SU1622834A1 |

| НИЗКОЧАСТОТНЫЙ ИЗМЕРИТЕЛЬ ФАЗОВОГО СДВИГА | 1992 |

|

RU2024028C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| Цифровой фазометр | 1983 |

|

SU1128187A1 |

| ЦИФРОВОЙ НИЗКОЧАСТОТНЫЙ ФАЗОМЕТР-ЧАСТОТОМЕР МГНОВЕННОГО ЗНАЧЕНИЯ | 1990 |

|

RU2024027C1 |

Фиг2

Изобретение относится к измерительной технике и может быть использовано для бесконтактного измерения фазы дисбаланса роторов, в том числе роторов мотор-подшипников, вращающихся в бесконтактном газомагнитном подвесе.

Наиболее близким из известных является цифровой фазометр с постоянным измерительным времен ем, содержащий два формирователя, входы которых являются входами фазометра, триггер с раздельными входами, подключенными к выходам формирователей, счетчик, вход которого через две схемы совпадения соединен с выходом триггера, генератор импульсов, выход которого соединен с управляющим входом первой схемы совпадения, времязадающий делитель частоты, входом соединенный с выходом задающего генератора, а выходом - с управляющим входом второй схемы совпадения. - --i: : ;

Недостатком известного цифрового фазометра является низкая надежность измерений при бесконтактном определении начального положения ротора оптоэлект- ронным датчиком с отражением оптического луча, обусловленная тем, что оптические неоднородности на поверхности ротора, (царапины, шероховатости, потертости, блики и т.п.) воспринимаются датчиком как ложные метки и искажают результаты измерений/

Целью изобретения является повышение надежности определения фазы дисбаланса ротора путем селекции сигналов в опорном канале.

Указанная цель достигается тем, что в цифровой фазометр, содержащий первый и второй формирователи, первый триггер, первый и второй логические элементы И, генератор импульсов, времязадающий делитель и первый двоичный счетчик, введены соединенный со входом первого формирователя оптоэлектронный датчик начального положения ротора, состоящий из диодного фотоприемника, соединенного через первый резистор с источником сигнала питания и диодного излучателя, соединенного через второй резистор с выходом генератора импульсов, блок компенсации фазового сдвига селектора и селектор сигналов, первый вход которого соединен с выходом первого формирователя, второй вход - с выходом генератора импульсов, а первый выход - с первым входом первого триггера, второй вход которого соединен с выходом блока компенсации фазового сдвига селектора, первый вход которого соединен с выходом второго формирователя, второй вход - с выходом генератора импульсов, третий, четвертый и пятый входы - соответственно с первым, вторым и третий входами селектора сигналов.

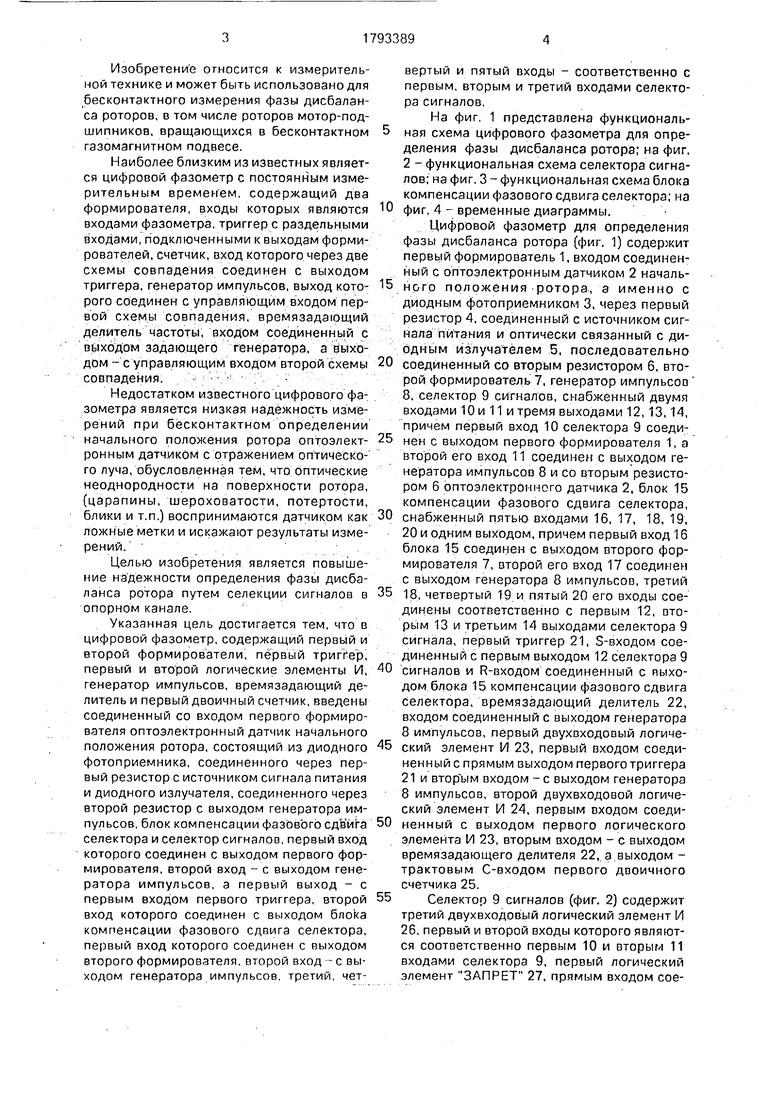

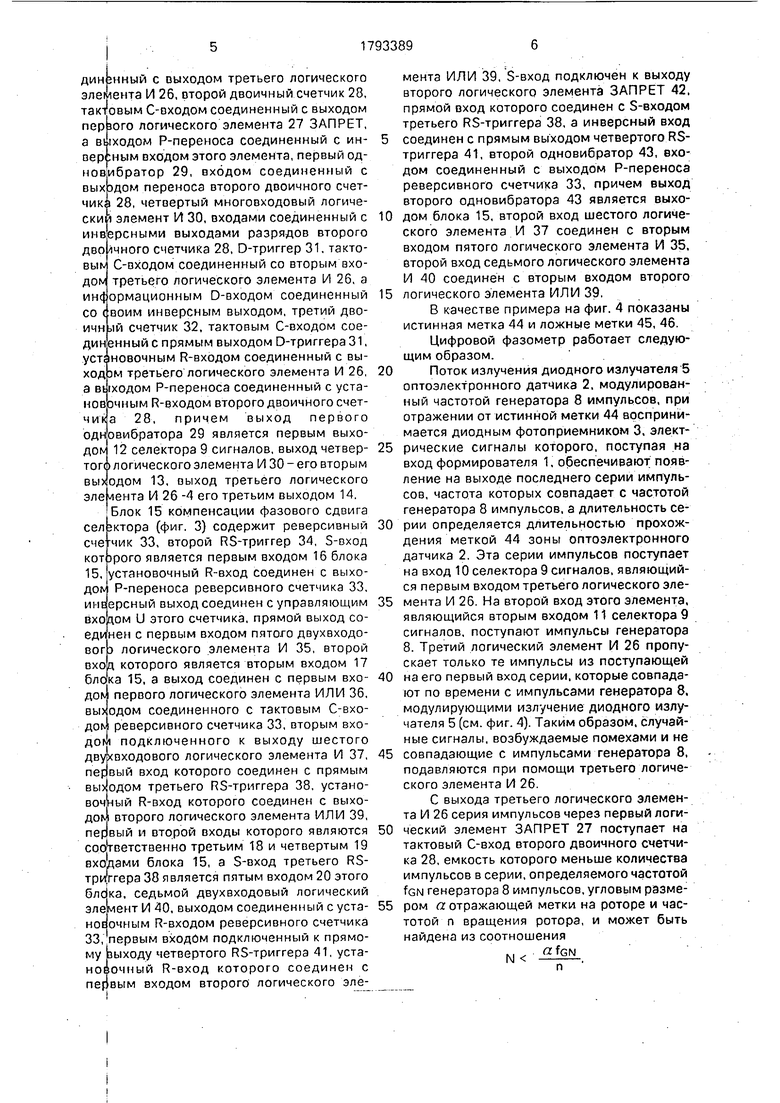

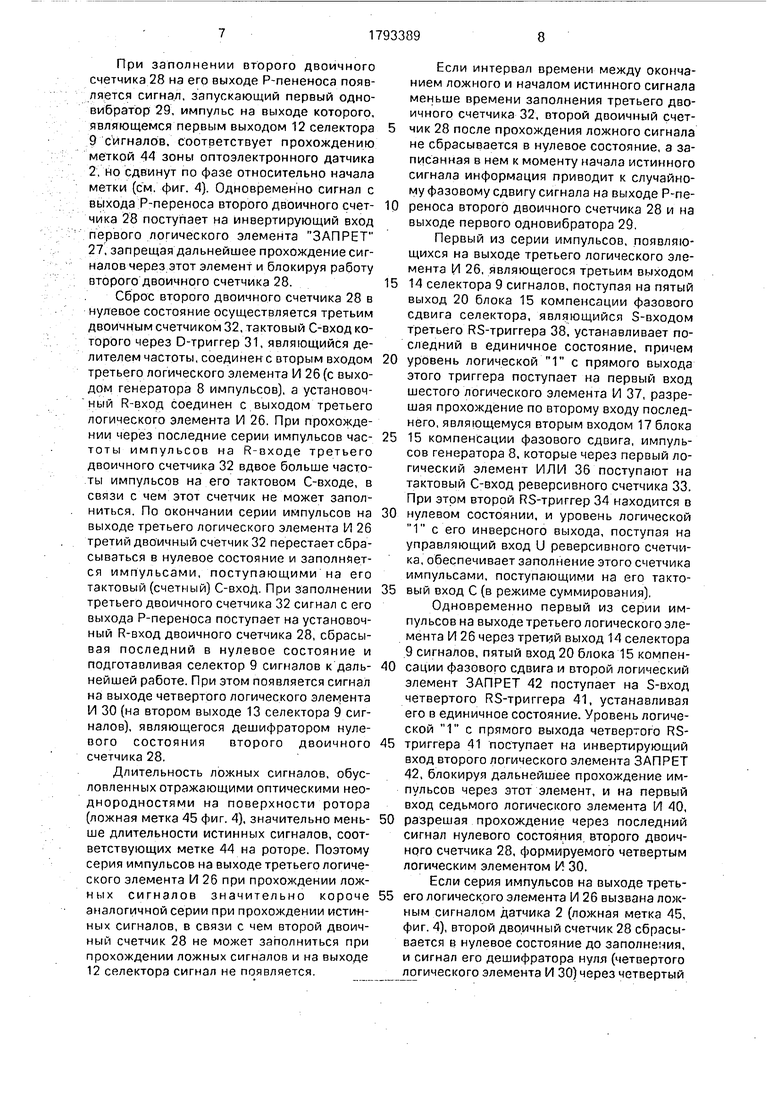

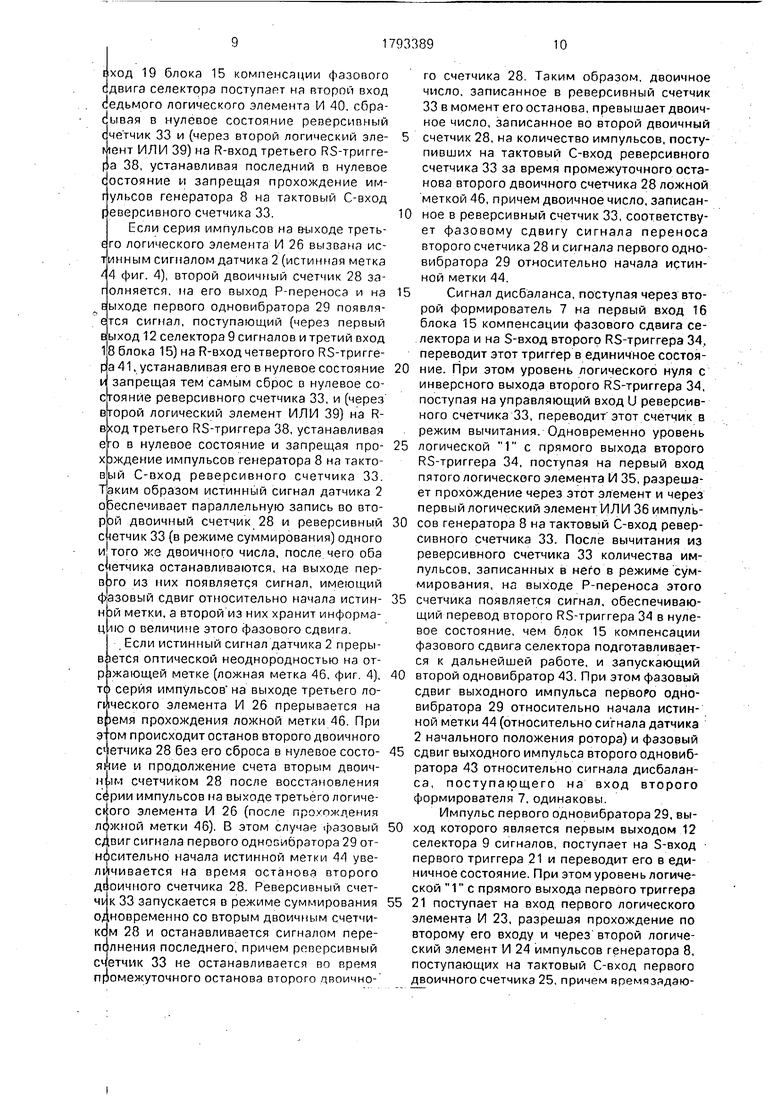

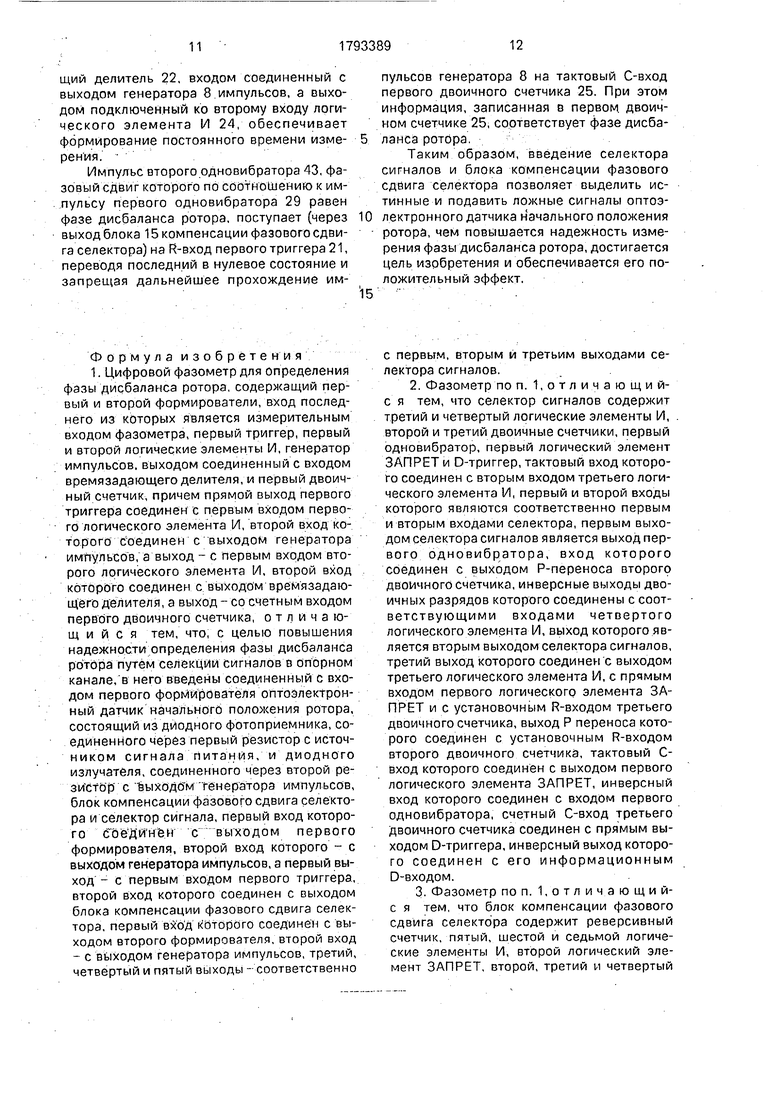

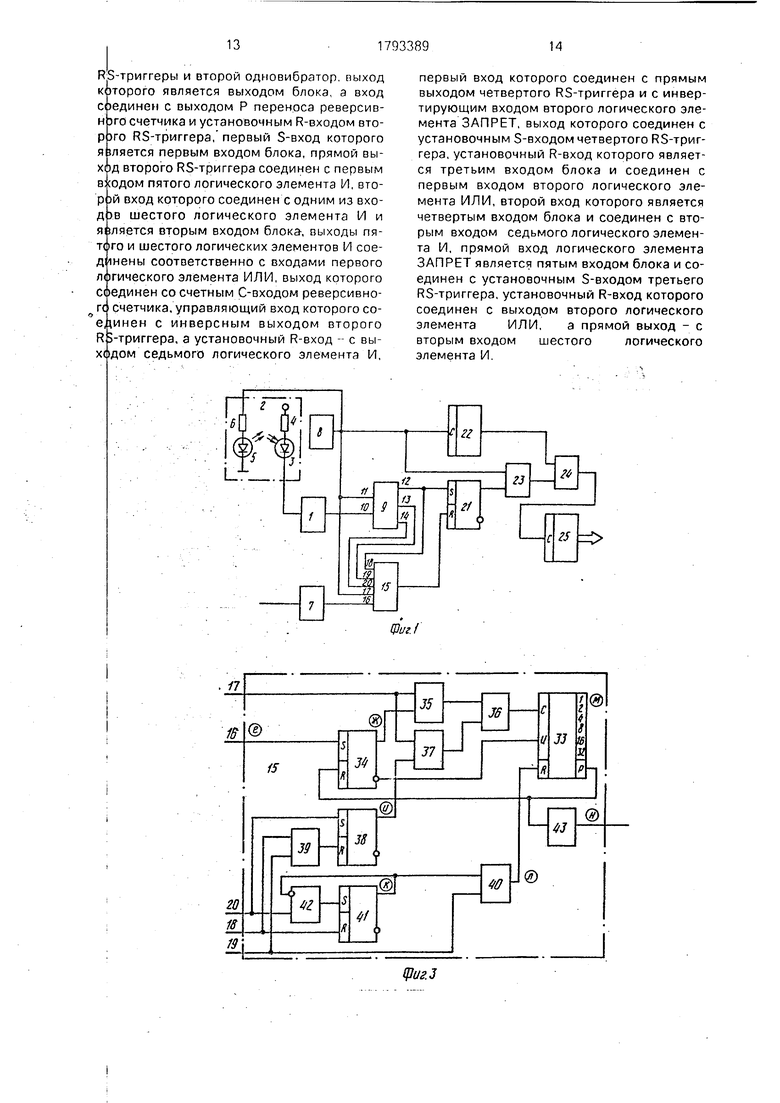

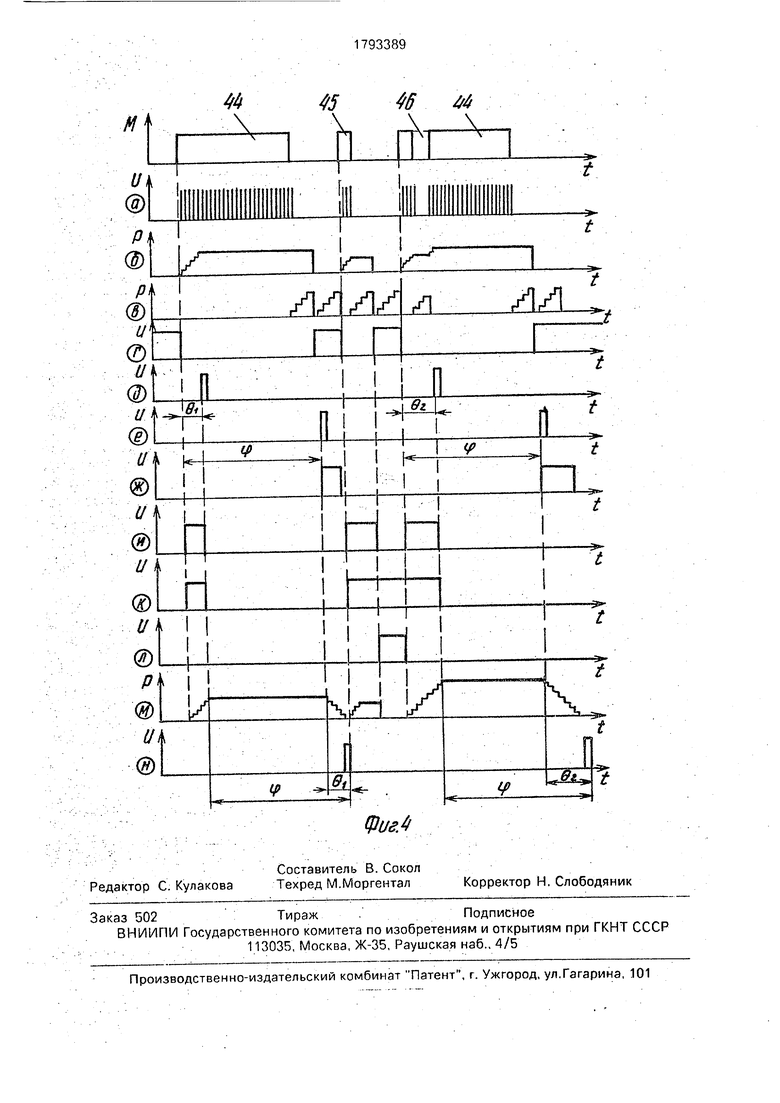

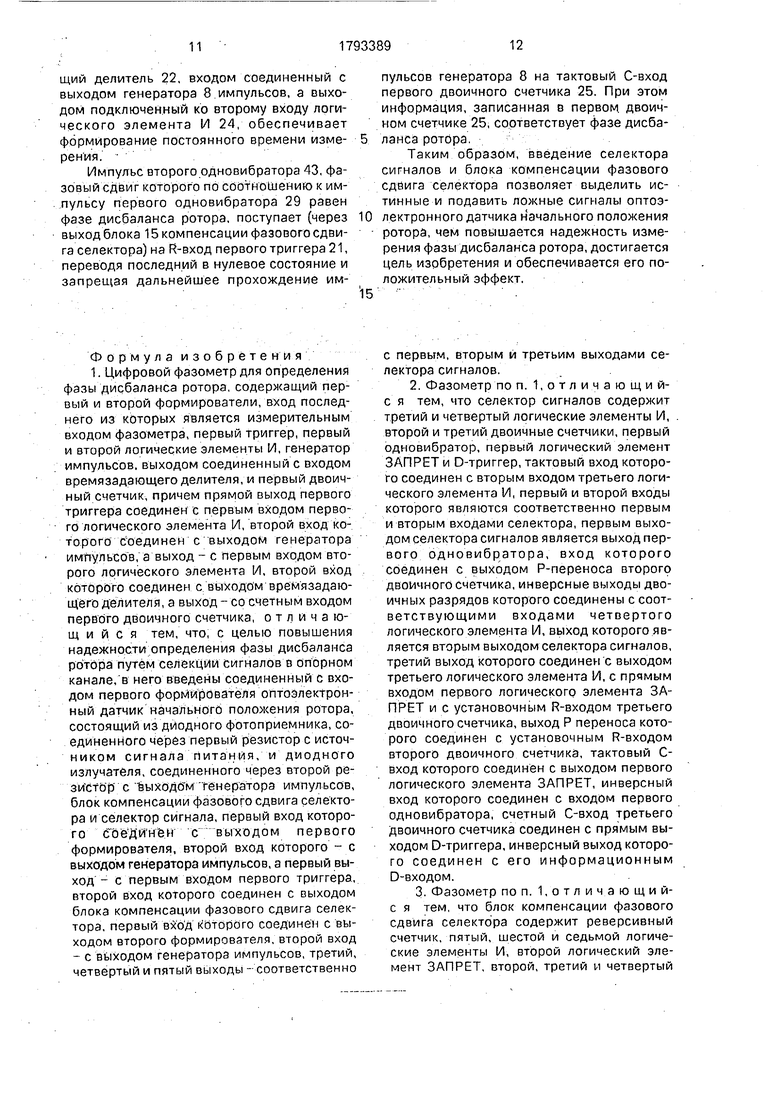

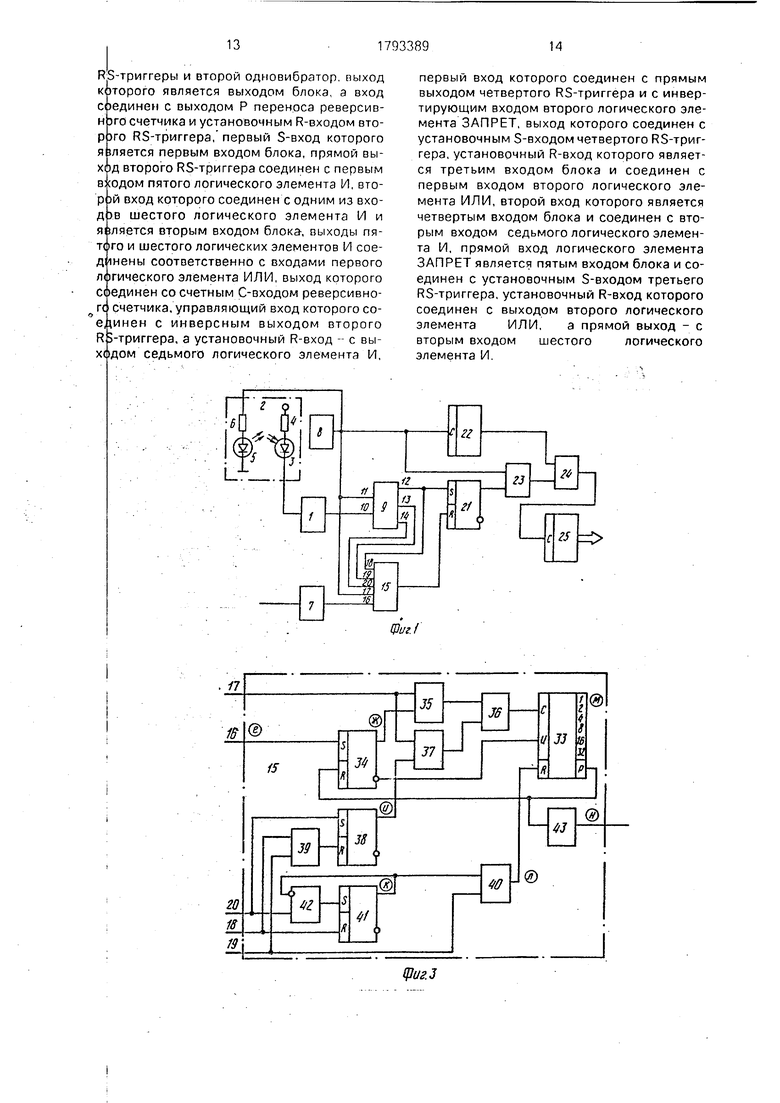

На фиг. 1 представлена функциональная схема цифрового фазометра для определения фазы дисбаланса ротора; на фиг, 2 - функциональная схема селектора сигналов; на фиг. 3 - функциональная схема блока компенсации фазового сдвига селектора; на

фиг, 4 - временные диаграммы.

Цифровой фазометр для определения фазы дисбаланса ротора (фиг. 1) содержит первый формирователь 1, входом соединенный с оптоэлектронным датчиком 2 началь5 него положения ротора, з именно с диодным фотоприемником 3, через первый резистор 4, соединенный с источником сигнала питания и оптически связанный с ди- Ьдным излучателем 5, последовательно

0 соединенный со вторым резистором 6, второй формирователь 7, генератор импульсов 8, селектор 9 сигналов, снабженный двумя входами 10 и 11 и тремя выходами 12,13,14, причем первый вход 10 селектора 9 соеди5 нен с выходом первого формирователя 1, а второй его вход 11 соединен с выходом генератора импульсов 8 и со вторым резистором 6 оптоэлектронного датчика 2. блок 15 компенсации фазового сдвига селектора,

0 снабженный пятью входами 16, 17, 18, 19, 20 и одним выходом, причем первый вход 16 блока 15 соединен с выходом второго формирователя 7, второй его вход 17 соединен с выходом генератора 8 импульсов, третий

5 18, четвертый 19 и пятый 20 его входы соединены соответственно с первым 12, вторым 13 и третьим 14 выходами селектора 9 сигнала, первый триггер 21, S-входом соединенный с первым выходом 12 селектора 9

0 сигналов и R-входом соединенный с выходом блока 15 компенсации фазового сдвига селектора, времязадающий делитель 22, входом соединенный с выходом генератора 8 импульсов, первый двухвходовый логиче5 ский элемент И 23, первый входом соединенный с прямым выходом первого триггера 21 и втор ым входом -с выходом генератора 8 импульсов, второй двухвходовой логический элемент И 24, первым входом соеди0 ценный с выходом первого логического элемента И 23, вторым входом - с выходом времязадающего делителя 22, а.выходом - трактовым С-входом первого двоичного счетчика 25.

5 Селектор 9 сигналов (фиг. 2) содержит третий двухвходовый логический элемент И 26, первый и второй входы которого являются соответственно первым 10 и вторым 11 входами селектора 9, первый логический элемент ЗАПРЕТ 27, прямым входом соедин

гнный с выходом третьего логического

элемента И 26, второй двоичный счетчик 28, тактовым С-входом соединенный с выходом перзого логического элемента 27 ЗАПРЕТ,

1ходом Р-переноса соединенный с ин- :ным входом этого элемента, первый ода в вер

новибратор 29, входом соединенный с выхэдом переноса второго двоичного счетчика 28, четвертый многовходовый логическиим в дво

BbIN

дом

) элемент И 30, входами соединенный с

ерсными выходами разрядов второго

4чного счетчика 28, D-триггер 31, тактоС-входом соединенный со вторым вхотретьего логического элемента И 26, а

инс| ормационным D-входом соединенный со (воим инверсным выходом, третий двоичной счетчик 32, тактовым С-входом соединенный с прямым выходом О-триггера31, установочным R-входом соединенный с выход DM третьего логического элемента И 26, а выходом Р-переноса соединенный с установочным R-входом второго двоичного счетчик а 28, причем выход первого одновибратора 29 является первым выхоДОГ

топ

12 селектора 9 сигналов, выход четвер- 25 логического элемента И 30 - его вторым

выходом 13, выход третьего логического эле иента И 26 -4 его третьим выходом 14.

Блок 15 компенсации фазового сдвига сел зктора (фиг. 3) содержит реверсивный сче чик 33, второй RS-триггер 34, S-вход кот Dporo является первым входом 16 блока 15, установочный R-вход соединен с выхо- flON Р-переноса реверсивного счетчика 33, ИИЕ ерсный выход соединен с управляющим входом U этого счетчика, прямой выход соединен с первым входом пятого двухвходо- вогэ логического элемента И 35, второй вхоц которого является вторым входом 17 блока 15, а выход соединен с первым вхо- flON первого логического элемента ИЛИ 36, выходом соединенного с тактовым С-входом реверсивного счетчика 33, вторым входом подключенного к выходу шестого двухвходового логического элемента И 37, первый вход которого соединен с прямым третьего RS-триггера 38, установочный R-вход которого соединен с выходом второго логического элемента ИЛИ 39, первый и второй входы которого являются соответственно третьим 18 и четвертым 19 входами блока 15, а S-вход третьего RS- трцггера 38 является пятым входом 20 этого блс|ка, седьмой двухвходовый логический элемент И 40, выходом соединенный с уста- НОЕ очным R-входом реверсивного счетчика 33, первым входим подключенный к прямому зыходу четвертого RS-триггера 41, установочный R-вход которого соединен с nef вым входом второго логического элемента ИЛИ 39, S-вход подключен к выходу второго логического элемента ЗАПРЕТ 42, прямой вход которого соединен с S-входом третьего RS-триггера 38, а инверсный вход соединен с прямым выходом четвертого RS- триггера 41, второй одновибратор 43, входом соединенный с выходом Р-переноса реверсивного счетчика 33, причем выход второго одновибратора 43 является выходом блока 15, второй вход шестого логического элемента И 37 соединен с вторым входом пятого логического элемента И 35, второй вход седьмого логического элемента И 40 соединен с вторым входом второго логического элемента ИЛИ 39,

В качестве примера на фиг. 4 показаны истинная метка 44 и ложные метки 45, 46.

Цифровой фазометр работает следующим образом.

Поток излучения диодного излучателя 5 оптоэлектронного датчика 2, модулированный частотой генератора 8 импульсов, при отражении от истинной метки 44 воспринимается диодным фотоприемником 3. электрические сигналы которого, поступая на вход формирователя 1, обеспечивают появление на выходе последнего серии импульсов, частота которых совпадает с частотой генератора 8 импульсов, а длительность серии определяется длительностью прохождения меткой 44 зоны оптоэлектронного датчика 2. Эта серии импульсов поступает на вход 10 селектора 9 сигналов, являющийся первым входом третьего логического элемента И 26. На второй вход этого элемента, являющийся вторым входом 11 селектора 9 сигналов, поступают импульсы генератора 8. Третий логический элемент И 26 пропускает только те импульсы из поступающей на его первый вход серии, которые совпадают по времени с импульсами генератора 8, модулирующими излучение диодного излучателя 5 (см. фиг. 4). Таким образом, случайные сигналы, возбуждаемые помехами и не совпадающие с импульсами генератора 8, подавляются при помощи третьего логического элемента И 26.

С выхода третьего логического элемента И 26 серия импульсов через первый логический элемент ЗАПРЕТ 27 поступает на тактовый С-вход второго двоичного счетчика 28, емкость которого меньше количества импульсов в серии, определяемого частотой TGN генератора 8 импульсов, угловым размером о. отражающей метки на роторе и частотой п вращения ротора, и может быть найдена из соотношения

М gfGN

При заполнении второго двоичного счетчика 28 на его выходе Р-пененоса появляется сигнал, запускающий первый одно- вибратор 29, импульс на выходе которого, являющемся первым выходом 12 селектора 9 сигналов, соответствует прохождению меткой 44 зоны оптоэлектронного датчика 2, но сдвинут по фазе относительно начала метки (см. фиг. 4). Одновременно сигнал с выхода Р-переноса второго двоичного счетчика 28 поступает на инвертирующий вход первого логического элемента ЗАПРЕТ 27, запрещая дальнейшее прохождение сигналов через этот элемент и блокируя работу второго двоичного счетчика 28.

Сброс второго двоичного счетчика 28 в нулевое состояние осуществляется третьим двоичным счетчиком 32, тактовый С-вход которого через D-триггер 31, являющийся делителем частоты, соединен с вторым входом третьего логического элемента И 26 (с выходом генератора 8 импульсов), а установоч- ный R-вход соединен с выходом третьего логического элемента И 26. При прохождении через последние серии импульсов частоты импульсов на R-входе третьего двоичного счетчика 32 вдвое больше частоты импульсов на его тактовом С-входе, в связи с чем этот счетчик не может заполниться. По окончании серии импульсов на выходе третьего логического элемента И 26 третий двоичный счетчик 32 перестает сбрасываться в нулевое состояние и заполняется импульсами, поступающими на его тактовый (счетный) С-вход. При заполнении третьего двоичного счетчика 32 сигнал с его выхода Р-переноса поступает на установочный R-вход двоичного счетчика 28, сбрасывая последний в нулевое состояние и подготавливая селектор 9 сигналов к дальнейшей работе. При этом появляется сигнал на выходе четвертого логического элемента И 30 (на втором выходе 13 селектора 9 сигналов), являющегося дешифратором нулевого состояния второго двоичного счетчика 28.

Длительность ложных сигналов, обусловленных отражающими оптическими нео- днородностями на поверхности ротора (ложная метка 45 фиг. 4), значительно меньше длительности истинных сигналов, соответствующих метке 44 на роторе. Поэтому серия импульсов на выходе третьего логического элемента И 26 при прохождении лож- ных сигналов значительно короче аналогичной серии при прохождении истинных сигналов, в связи с чем второй двоичный счетчик 28 не может заполниться при прохождении ложных сигналов и на выходе 12 селектора сигнал не появляется.

Если интервал времени между окончанием ложного и началом истинного сигнала меньше времени заполнения третьего двоичного счетчика 32, второй двоичный счетчик 28 после прохождения ложного сигнала не сбрасывается в нулевое состояние, а записанная в нем к моменту начала истинного сигнала информация приводит к случайному фазовому сдвигу сигнала на выходе Р-пе0 реноса второго двоичного счетчика 28 и на выходе первого одновибратора 29.

Первый из серии импульсов, появляющихся на выходе третьего логического элемента И 26, являющегося третьим выходом

5 14 селектора 9 сигналов, поступая на пятый выход 20 блока 15 компенсации фазового сдвига селектора, являющийся S-входом третьего RS-триггера 38, устанавливает последний в единичное состояние, причем

0 уровень логической 1 с прямого выхода этого триггера поступает на первый вход шестого логического элемента И 37, разрешая прохождение по второму входу последнего, являющемуся вторым входом 17 блока

5 15 компенсации фазового сдвига, импульсов генератора 8, которые через первый логический элемент ИЛИ 36 поступают на тактовый С-вход реверсивного счетчика 33. При этом второй RS-триггер 34 находится в

0 нулевом состоянии, и уровень логической 1 с его инверсного выхода, поступая на управляющий вход U реверсивного счетчика, обеспечивает заполнение этого счетчика импульсами, поступающими на его такто5 вый вход С (в режиме суммирования),

Одновременно первый из серии импульсов на выходе третьего логического элемента И 26 через третий выход 14 селектора 9 сигналов, пятый вход 20 блока 15 компен0 сации фазового сдвига и второй логический элемент ЗАПРЕТ 42 поступает на S-вход четвертого RS-триггера 41, устанавливая его в единичное состояние. Уровень логической 1 с прямого выхода четвертого RS5 триггера 41 поступает на инвертирующий вход второго логического элемента ЗАПРЕТ 42, блокируя дальнейшее прохождение импульсов через этот элемент, и на первый вход седьмого логического элемента И 40,

0 разрешал прохождение через последний сигнал нулевого состояния, второго двоичного счетчика 28, формируемого четвертым логическим элементом И 30.

Если серия импульсов на выходе треть5 его логического элемента И 26 вызвана ложным сигналом датчика 2 (ложная метка 45, фиг. 4), второй двоичный счетчик 28 сбрасывается в нулевое состояние до заполнения, и сигнал его дешифратора нуля (четвертого логического элемента И 30) через четвертый

ход 19 блока 15 компенсации фазового сдвига селектора поступает на второй вход Седьмого логического элемента И 40. сбра- сывая в нулевое состояние реверсивный счетчик 33 и (через второй логический элемент ИЛИ 39) на R-вход третьего RS-тригге- ра 38, устанавливая последний в нулевое состояние и запрещая прохождение им- гульсов генератора 8 на тактовый С-вход реверсивного счетчика 33.

Если серия импульсов на выходе третьего логического элемента И 26 вызвана истинным сигналом датчика 2 (истинная метка 44 фиг. 4), второй двоичный счетчик 28 за- голняется. на его выход Р-переноса и на выходе первого одновибратора 29 появляется сигнал, поступающий (через первый выход 12 селектора 9 сигналов и третий вход 18 блока 15) на R-вход четвертого RS-тригге- ра 41,устанавливая его в нулевое состояние V запрещая тем самым сброс в нулевое состояние реверсивного счетчика 33, и (через второй логический элемент ИЛИ 39) на R- вход третьего RS-триггера 38, устанавливая его в нулевое состояние и запрещая прохождение импульсов генератора 8 на тактовый С-вход реверсивного счетчика 33. Таким образом истинный сигнал датчика 2 оэеспечивает параллельную запись во второй двоичный счетчик 28 и реверсивный счетчик 33 (в режиме суммирования) одного и того же двоичного числа, после чего оба счетчика останавливаются, на выходе первого из них появляется сигнал, имеющий фазовый сдвиг относительно начала истин- н эй метки, а второй из них хранит информа- Ц ИО о величине этого фазового сдвига.

Если истинный сигнал датчика 2 прерывается оптической неоднородностью на от- рзжающей метке (ложная метка 46. фиг. 4), то серия импульсов на выходе третьего логического элемента И 26 прерывается на время прохождения ложной метки 46. При э ом происходит останов второго двоичного с1 етчика 28 без его сброса в нулевое состояние и продолжение счета вторым двоич- н .1м счетчиком 28 после восстановления импульсов на выходе третьего логиче- ct ого элемента И 26 (после прохождения ложной метки 46). В этом случае фазовый слвиг сигнала первого односибрэтора 29 относительно начала истинной метки 44 увеличивается на время останова второго

дс

оичного счетчика 28. Реверсивный счетчу к 33 запускается в режиме суммирования

ой

.повременно со вторым двоичным счетчиксм 28 и останавливается сигналом пере- пслнения последнего, причем реверсивный счетчик 33 не останавливается во время промежуточного останова второго двоичного счетчика 28. Таким образом, двоичное число, записанное в реверсивный счетчик 33 в момент его останова, превышает двоичное число, записанное во второй двоичный 5 счетчик 28, на количество импульсов, поступивших на тактовый Овход реверсивного счетчика 33 за время промежуточного останова второго двоичного счетчика 28 ложной меткой 46, причем двоичное число, записан- 10 ное в реверсивный счетчик 33, соответствует фазовому сдвигу сигнала переноса второго счетчика 28 и сигнала первого одно- вибратора 29 относительно начала истинной метки 44.

5 Сигнал дисбаланса, поступая через второй формирователь 7 на первый вход 16 блока 15 компенсации фазового сдвига селектора и на S-вход второго RS-триггера 34, переводит этот триггер в единичное состоя0 ние. При этом уровень логического нуля с инверсного выхода второго RS-триггера 34, поступая на управляющий вход U реверсивного счетчика 33, переводит этот счетчик в режим вычитания. Одновременно уровень

5 логической 1 с прямого выхода второго RS-триггера 34, поступая на первый вход пятого логического элемента И 35, разрешает прохождение через этот элемент и через первый логический элемент ИЛИ 36 импуль0 сов генератора 8 на тактовый С-вход реверсивного счетчика 33. После вычитания из реверсивного счетчика 33 количества импульсов, записанных в него в режиме суммирования, на выходе Р-переноса этого

5 счетчика появляется сигнал, обеспечивающий перевод второго RS-триггера 34 в нулевое состояние, чем блок 15 компенсации фазового сдвига селектора подготавливается к дальнейшей работе, и запускающий

0 второй одновибратор 43. При этом фазовый сдвиг выходного импульса первого одно- вибратора 29 относительно начала истинной метки 44 (относительно сигнала датчика 2 начального положения ротора) и фазовый

5 сдвиг выходного импульса второго одновибратора 43 относительно сигнала дисбаланса, поступающего на вход второго формирователя 7. одинаковы.

Импульс первого одновибратора 29, вы0 ход которого является первым выходом 12 селектора 9 сигналов, поступает на S-вход первого триггера 21 и переводит его в единичное состояние. При этом уровень логической 1 с прямого выхода первого триггера

5 21 поступает на вход первого логического элемента И 23, разрешая прохождение по второму его входу и через второй логический элемент И 24 импульсов генератора 8, поступающих на тактовый С-вход первого двоичного счетчика 25, причем времязадэющий делитель 22, входом соединенный с выходом генератора 8.импульсов, а выходом подключенный ко второму входу логического элемента И 24, обеспечивает формирование постоянного времени измерения.

Импульс второго одновибратора 43, фазовый сдвиг которого по соотношению к импульсу первого одновибратора 29 равен фазе дисбаланса ротора, поступает (через выход блока 15 компенсации фазового сдвига селектора) на R-вход первого триггера 21, переводя последний в нулевое состояние и запрещая дальнейшее прохождение имФормула изобретения 1. Цифровой фазометр для определения фазы дисбаланса ротора, содержащий первый и второй формирователи, вход последнего из которых является измерительным входом фазометра, первый триггер, первый и второй логические элементы И, генератор импульсов, выходом соединенный с входом времязадающего делителя, и первый двоичный счетчик, причем прямой выход первого триггера соединен с первым входом первого логического элемента И, второй вход которого соединен с выходом генератора импульсов, а выход - с первым входом второго логического элемента И, второй вход которого соединен с выходом времязадающего делителя, а выход - со счетным входом первого двоичного счетчика, отличающийся тем, что, с целью повышения надежности определения фазы дисбаланса ротора путём селекции сигналов в опорном канале, в него введены соединенный с входом первого формирователя оптоэлектрон- ный датчик начального положения ротора, состоящий из диодного фотоприемника, соединенного через первый резистор с источником сигнала питания, и диодного излучателя, соединенного через второй ре- зи ст бр с выходом генератора импульсов, блок компенсации фазового сдвига селектора и селектор сигнала, первый вход которого бое ди нен с выходом первого формирователя, второй вход которого -с выходом генератора импульсов, а первый выход - с первым входом первого триггера, второй вход которого соединен с выходом блока компенсации фазового сдвига селектора, первый вход которого соединён с выходом второго формирователя, второй вход - с выходом генератора импульсов, третий, четвертый и пятый выходы -соответственно

пульсов генератора 8 на тактовый С-вход первого двоичного счетчика 25. При этом информация, записанная в первом, двоичном счетчике 25, соответствует фазе дисбаланса ротора.

Таким образом, введение селектора сигналов и блока компенсации фазового сдвига селектора позволяет выделить истинные и подавить ложные сигналы оптоэлектронного датчика начального положения ротора, чем повышается надежность измерения фазы дисбаланса ротора, достигается цель изобретения и обеспечивается его положительный эффект.

....

с первым, вторым и третьим выходами селектора сигналов.

RS-триггеры и второй одновибратор. ЕШХОД которого является выходом блока, а вход соединен с выходом Р переноса реверсив- н эго счетчика и установочным R-входом вто- р )го RS-триггера, первый S-вход которого я )ляется первым входом блока, прямой выход второго RS-триггера соединен с первым

содом пятого логического элемента И, второй вход которого соединен с одним из вхо- д в шестого логического элемента И и является вторым входом блока, выходы пятого и шестого логических элементов И сое1нены соответственно с входами первого логического элемента ИЛИ, выход которого соединен со счетным С-входом реверсивно- t гс счетчика, управляющий вход которого соединен с инверсным выходом второго R 5-триггера, а установочный R-вход -- с выходом седьмого логического элемента И,

первый вход которого соединен с прямым выходом четвертого RS-триггера и с инвертирующим входом второго логического элемента ЗАПРЕТ, выход которого соединен с установочным S-входом четвертого RS-триггера, установочный R-вход которого является третьим входом блока и соединен с первым входом второго логического элемента ИЛИ, второй вход которого является четвертым входом блока и соединен с вторым входом седьмого логического элемента И, прямой вход логического элемента ЗАПРЕТ является пятым входом блока и соединен с установочным S-входом третьего RS-триггера, установочный R-вход которого соединен с выходом второго логического элемента ИЛИ, а прямой выход - с вторым входом шестого логического элемента И.

Авторы

Даты

1993-02-07—Публикация

1990-01-03—Подача