Фиг./

Изобретение относится к вычислительной технике и может быть использовано в аналоговых вычислительных машинах.

Цель изобретения - повышение точности устройства.

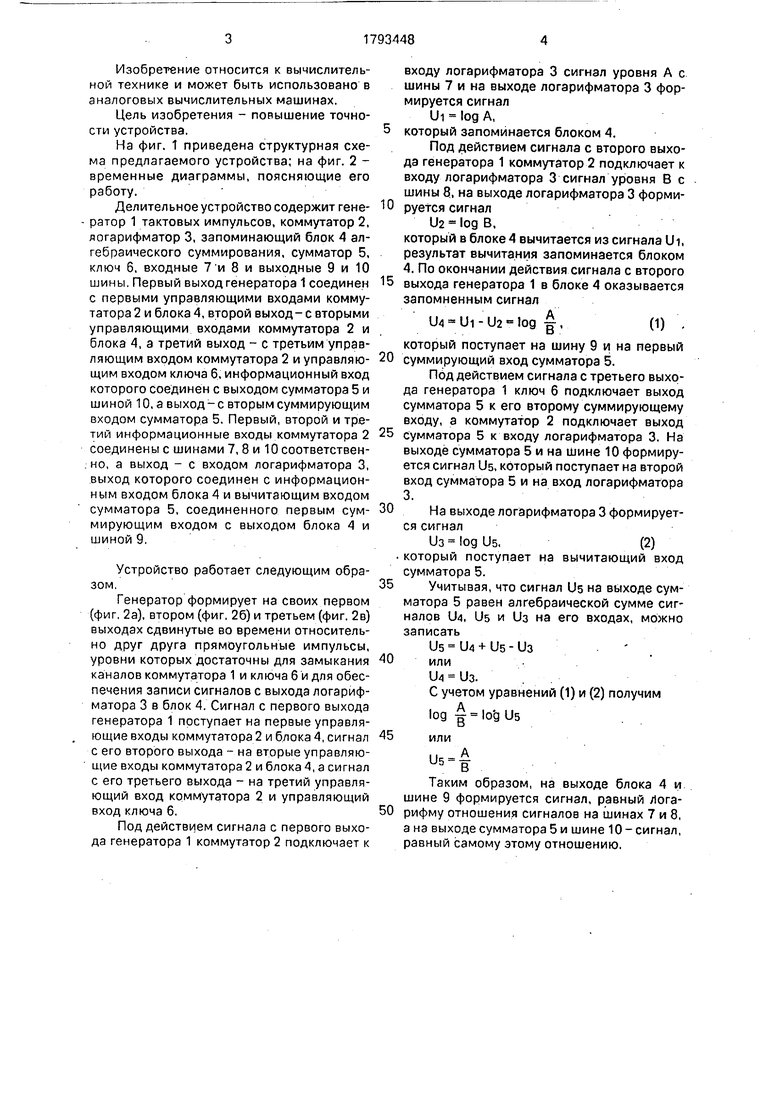

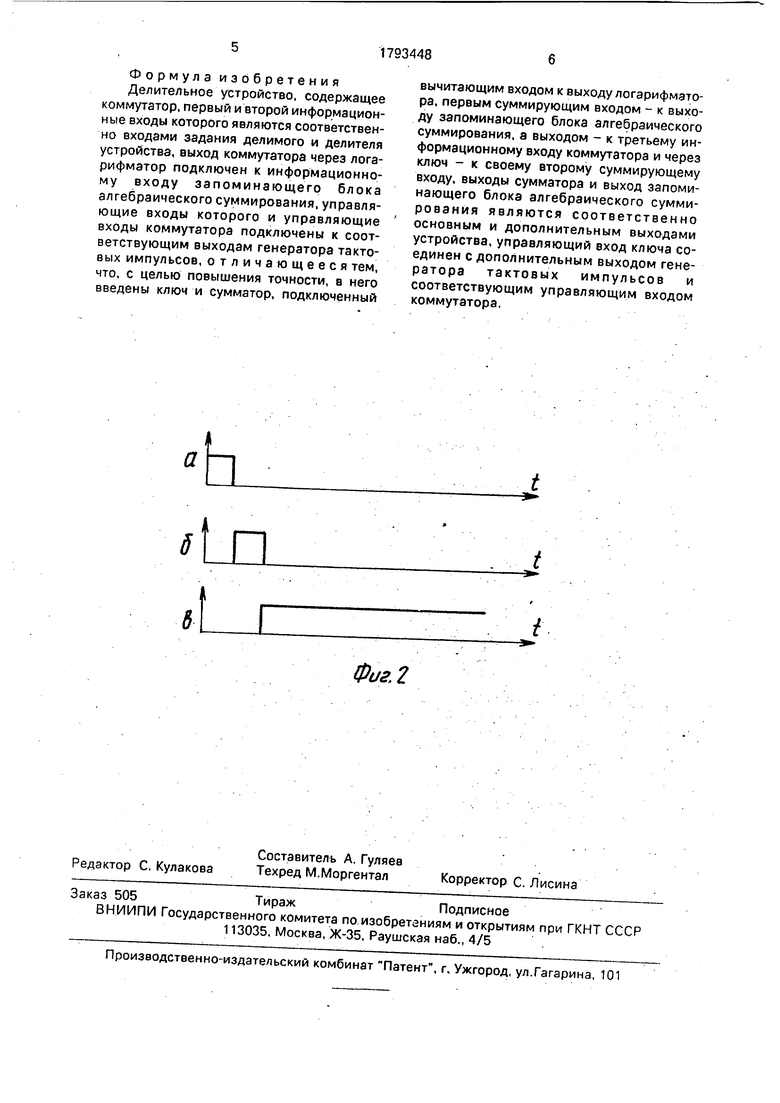

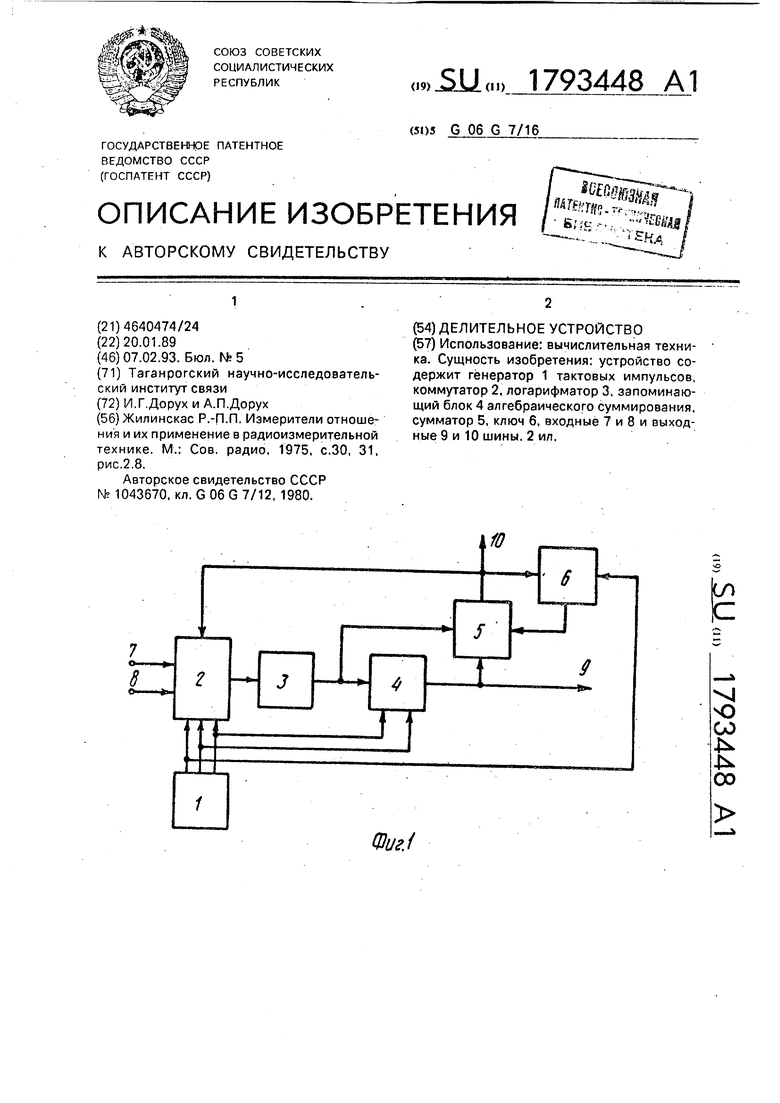

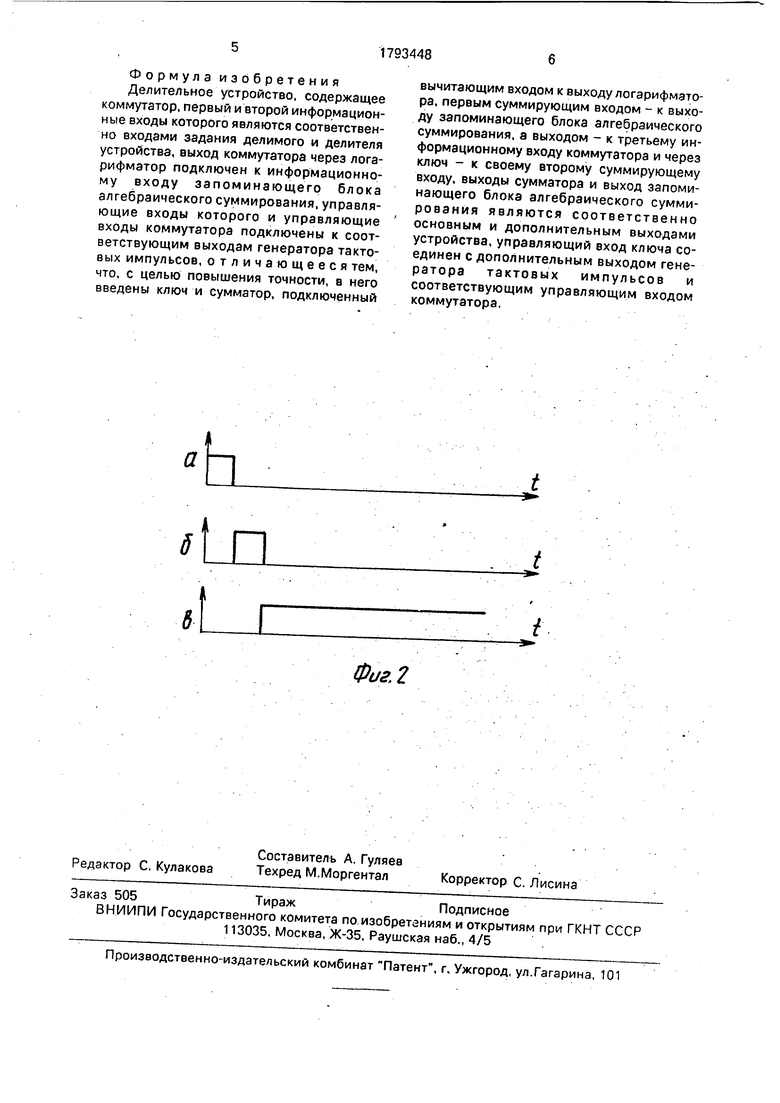

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие его работу.

Делительное устройство содержит генератор 1 тактовых импульсов, коммутатор 2, яогарифматор 3, запоминающий блок 4 алгебраического суммирования, сумматор 5, ключ 6, входные 7 и 8 и выходные 9 и 10 шины. Первый выход генератора 1 соединен с первыми управляющими входами коммутатора 2 и блока 4, второй выход- с вторыми управляющими входами коммутатора 2 и блока 4, а третий выход - с третьим управляющим входом коммутатора 2 и управляющим входом ключа 6, информационный вход которого соединен с выходом сумматора 5 и шиной 10, а выход-с вторым суммирующим входом сумматора 5. Первый, второй и третий информационные входы коммутатора 2 соединены с шинами 7, 8 и 10 соответствен- ; но, а выход - с входом логарифматора 3, выход которого соединен с информационным входом блока 4 и вычитающим входом сумматора 5, соединенного первым суммирующим входом с выходом блока 4 и шиной 9.

Устройство работает следующим образом.

Генератор формирует на своих первом (фиг. 2а), втором (фиг. 26) и третьем (фиг. 2в) выходах сдвинутые во времени относительно друг друга прямоугольные импульсы, уровни которых достаточны для замыкания каналов коммутатора 1 и ключа б и для обеспечения записи сигналов с выхода логарифматора 3 в блок 4. Сигнал с первого выхода генератора 1 поступает на первые управляющие входы коммутатора 2 и блока 4, сигнал с его второго выхода - на вторые управляющие входы коммутатора 2 и блока 4, а сигнал с его третьего выхода - на третий управляющий вход коммутатора 2 и управляющий вход ключа 6.

Под действием сигнала с первого выхода генератора 1 коммутатор 2 подключает к

входу логарифматора 3 сигнал уровня А с шины 7 и на выходе логарифматора 3 формируется сигнал Ui log A,

который запоминается блоком 4.

Под действием сигнала с второго выхода генератора 1 коммутатор 2 подключает к входу логарифматора 3 сигнал уровня В с шины 8, на выходе логарифматора 3 формируется сигнал U2 log В,

который в блоке 4 вычитается из сигнала Ui, результат вычитания запоминается блоком 4. По окончании действия сигнала с второго

выхода генератора 1 в блоке 4 оказывается запомненным сигнал

U4 - Ui - U2 - log -g,

О)

который поступает на шину 9 и на первый суммирующий вход сумматора 5.

Под действием сигнала с третьего выхода генератора 1 ключ б подключает выход сумматора 5 к его второму суммирующему входу, а коммутатор 2 подключает выход сумматора 5 к входу логарифматора 3. На выходе сумматора 5 и на шине 10 формируется сигнал Us, который поступает на второй вход сумматора 5 и на вход логарифматора 3.

На выходе логарифматора 3 формируется сигнал

Уз log Us,(2) который поступает на вычитающий вход сумматора 5.

Учитывая, что сигнал Us на выходе сумматора 5 равен алгебраической сумме сигналов U4, Us и Ua на его входах, можно записать

+ U5-U3 или

U из.

С учетом уравнений (1) и (2) получим

log -| log Us или

-$

Таким образом, на выходе блока 4 и шине 9 формируется сигнал, равный Лога- рифму отношения сигналов на шинах 7 и 8, а на выходе сумматора 5 и шине 10-сигнал, равный самому этому отношению.

Формула изобретения Делительное устройство, содержащее коммутатор, первый и второй информационные входы которого являются соответственно входами задания делимого и делителя устройства, выход коммутатора через лога- рифматор подключен к информационному входу запоминающего блока алгебраического суммирования, управляющие входы которого и управляющие входы коммутатора подключены к соответствующим выходам генератора тактовых импульсов, отличающееся тем, что, с целью повышения точности, в него введены ключ и сумматор, подключенный

вычитающим входом к выходу логарифмзто- ра, первым суммирующим входом - к выходу запоминающего блока алгебраического суммирования, а выходом - к третьему информационному входу коммутатора и через ключ - к своему второму суммирующему входу, выходы сумматора и выход запоминающего блока алгебраического суммирования являются соответственно основным и дополнительным выходами устройства, управляющий вход ключа соединен с дополнительным выходом генератора тактовых импульсов и соответствующим управляющим входом коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ПОСТОЯННОЕ | 1991 |

|

RU2024879C1 |

| Устройство для вычисления функции А - В / А + В | 1989 |

|

SU1674163A1 |

| Частотный детектор | 1990 |

|

SU1730738A1 |

| Дифференцирующее устройство | 1990 |

|

SU1749899A2 |

| Устройство для моделирования воспроизводства продукта в экономических системах | 1987 |

|

SU1430974A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2023302C1 |

| Преобразователь интервала времени в код | 1990 |

|

SU1830622A1 |

| Дифференцирующее устройство | 1990 |

|

SU1829044A1 |

| Устройство для определения вероятности нахождения сигнала в заданном амплитудном диапазоне | 1990 |

|

SU1758632A1 |

| Управляемый фазовращатель | 1990 |

|

SU1721536A1 |

Ь

t

n

8

t

t

t

Фиг. 2

Авторы

Даты

1993-02-07—Публикация

1989-01-20—Подача