Я(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1985 |

|

SU1285473A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1285474A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1317438A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1278848A1 |

| Многоканальное устройство приоритета | 1985 |

|

SU1283765A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Система для обмена информацией | 1980 |

|

SU980087A1 |

| Устройство для распределения заданий процессорам | 1990 |

|

SU1756889A1 |

| Устройство для сопряжения многопроцессорной вычислительной системы с внешними устройствами | 1984 |

|

SU1241245A2 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

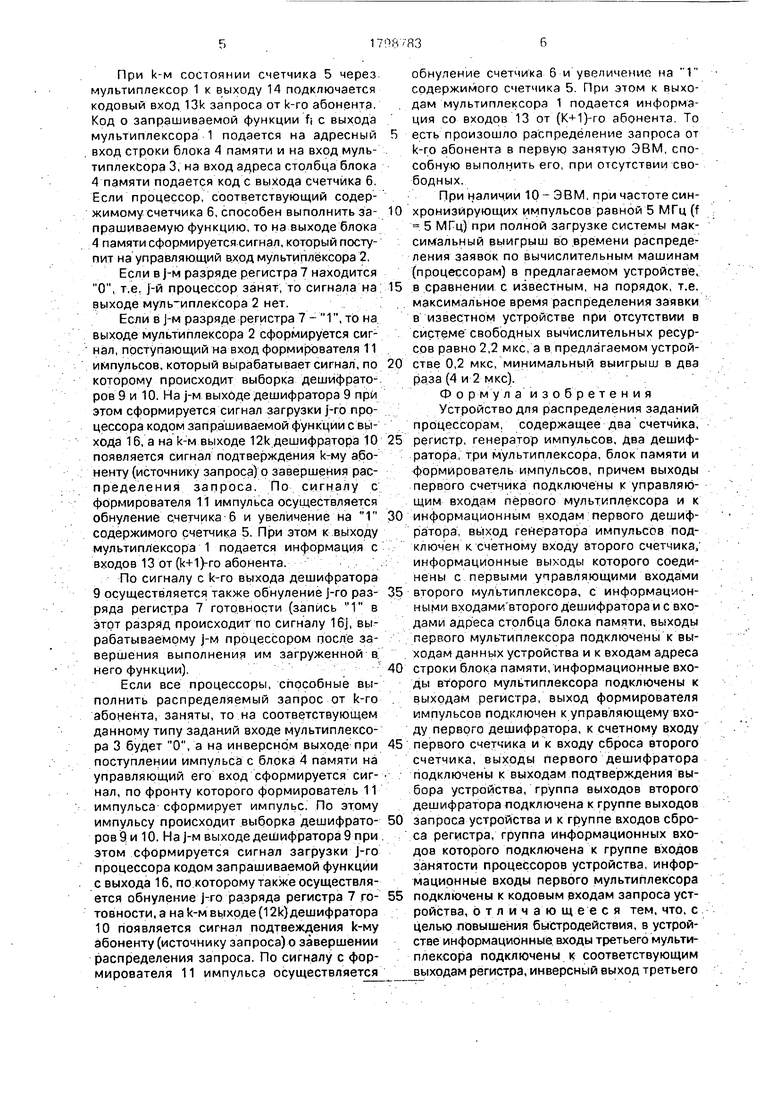

Изобретение относится к вычислительной технике, в частности к устройствам для распределения нагрузки в многомашинных и многопроцессорных системах. Целью изобретения является повышение быстродействия.Устройство содержит мультиплексоры 1, .2, 3, счетчики. 5, 6, блок памяти 4, дешифраторы 9, 10, регистр 7, формирователь импульсов 11. В устройстве возмржно, не производя перебора возможных незанятых вычислительных ресурсов при отгсутствии в системе процессоров, способных выполнить данный тип заданий, распределить задание на первую занятую ЭВМ и перейти к распределению запроса от следующего источника. 1 ил.

12

4 Ч 00 VI 00

со

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для распределения нагрузки в многомашинных и многопроцессорных системах.

Целью изобретения является повышение быстродействия,

На чертеже представлена структурная схема устройства.

Устройство содержит два мультиплексора 1,2, мультиплексоре инверсным выходом 3, блок 4 памяти, два счетчика 5 и 6, регистр 7, генератор 8 импульсов, два дешифратора 9 и 10, формирователь 11 импульсов, выходы 12 подтверждения выбора устройства, которые входы 13 запроса устройства, выходы 14 данных устройства, входы 15 занятости процессора устройства, выходы 16 запроса устройства, причем выходы счетчика 5 подключены к управляющим входам мультиплексора 1 и к информационным входам дешифратора 10, выход генератора 8 импульсов подключен к счетному входу Счетчика 6, информационные выходы которого соединены с первыми управляющими входами мультиплексора 2, с информационными входами первого дешифратора и со вторыми входами адреса блока 4 памяти, выходы мультиплексора 1 подключены к выходам 14 данных устройства, к первым входам адреса блока 4 памяти и к первым управляющим входам мультиплексора 3, выход блока 4 памяти подключен ко вторым управляющим входам мультиплексоров 2 и 3, информационные входы которых подключены к выходам регистра 7, выход мультиплексора 2 и инверсный выход мультиплексора 3,подключены к входу формирователя 11 импульсов, выход которого подключен к управляющим входам дешифраторов 9 и 10, к счетному входу счетчика 5 и входу сброса счетчика 6, выходы дешифратора 10 подключены к выходам 12 подтверждения выбора устройства, группа выходов дешифратора 9 подключена к груп- . пе выходов 16 запроса устройства и к первой группе информационных входов регистра 7, вторая группа информационных входов которого подключена к группе входов 15 занятости процессора устройства, информационные входы мультиплексора 1 подключены к кодовым входам 13 запроса устройства.

Введение мультиплексора с инверсным выходом позволяет повысить производительность и расширить функциональные возможности вычислительной системы за счет исключения опроса на занятость вычислительных ресурсов и распределения задания на первую занятую ЭВМ, способную выполнить его, при отсутствии в системе свободных процессоров, способных выполнить данный тип заданий.

в других технических решениях подобный подход к распределению заданий между процессорами в многопроцессорной вычислительной системе отсутствует, поэтому заявленный объект соответствует критерию Существенные отличия.

Наличие существенных отличий приводит к положительному эффекту, так как исключение любого элемента или связи не позволяет реализовать возможность исклю5 чения опроса на занятость вычислительных ресурсов и распределения задания на первую занятую ЭВМ при отсутствии в системе свободных процессоров, способных выполнить данный тип заданий.

0Устройство может быть применено для распределения функционально различных запросов при несовпадении функциональных ресурсов ЭВМ. В частности, устройство может быть применено в отказоустойчивых

5 многомашинных вычислительных системах с использованием в вычислительном процессе частично работоспособных состояний

.ЭВМ.. ; .. ; Устройство работает следующим обра0 зом.

При распределении запросов счетчиком 5 осуществляется циклическое подключение абонентов (источников запроса) к устройству через мультиплексор 1, а счетчиком

5 б поочередная проверка процессоров (от первого до т-го)на занятость и способность выполнить запрашиваемую функцию (программу). Особенность работы устройства заключается в том, что если все процессоры,

0 способные выполнить запрашиваемую от k- го абонента конкретного типа функцию, заняты, то опроса на занятость процессоров и блокировки распределения от .других абонентов не происходит, задание распределя5 ется в первую занятую ЭВМ, способную выполнить его и переходить к распределению здания от другого абонента.

Отображение занятости процессоров осуществляется в регистре 7, в j-м разряде

0 находится 1, если j-й процессор не занят,. в противном случае в этом разряде находится О. Отображение функциональных возможностей процессоров осуществляется в блоке 4 памяти, ячейка которого 4ij содер5 , если J-й процессор способен выполнить функцию fi, в противном случае в ней находится О.;

Рассмотрим более подробно процесс распределения запросов, выставляемых абонентами на соответствующие входы 13.

При k-м состоянии сметчика 5 через мультиплексор 1 к выходу 14 подключается кодовый вход 13k запроса от k-ro абонента. Код о запрашиваемой функции fj с выхода мультиплексора 1 подается на адресный вход строки блока А памяти и на вход мультиплексора 3, на вход адреса столбца блока 4 памяти подается код с выхода счетчика 6. Если процессор, соответствующий содержимому счетчика 6,способен выполнить запрашиваемую функцию, то на выходе блока 4 памяти сформируетсЯ:Сигнал, который поступит на управляющий вход мультиплексора 2.

Если в j-м разряде регистра 7 находится О, т.е. j-й процессор занят, то сигнала на: выходе муль иплексора 2 нет.

Если в j-м разряде регистра 7 - 1, то на. выходе мультиплексора 2 сформируется сигнал, поступающий на вход формирователя 11 импульсов, который вырабатывает сигнал, по которому происходит выборка дешифрато-. ров 9 и 10. Н.а j-м выходе дешифратора 9 при этом сформируется сигнал загрузки j-ro процессора кодом запрашиваемой функции с выхода 16, а на k:M выходе 12k дешифратора 10 появляется сигнал подтверждения k-му абоненту (источнику запроса) о завершения распределения запроса. По сигналу с формирователя 1.1 импульса осуществляется обнуление счетчика б и увеличение на 1 содержимого счетчика 5. При этом к выходу мультиплексора 1 подается информация с входов 13 от (k+1)-ro абонента.. .

По сигналу с k-ro выхода дешифратора

9 осуществляется также обнуление j-ro разряда регистра 7 готовности (запись Т в этот разряд происходит по сигналу 16, вырабатываемому j-м процессором после завершения выполнения им загруженной в. него функции).

Если все процессоры, способные выполнить распределяемый запрос от k-ro абонента, заняты, то на соответствующем данному типу заданий входе мультиплексора 3 будет О, а на инверсном выходе при поступлении импульса с блока 4 памяти на управляющий его вход сформируется сигнал, по фронту которого формирователь 11 импульса сформирует импульс. По этому импульсу происходит выборка дешифраторов 9: и 10, На j-м выходе дешифратора 9 при этом сформируется сигнал загрузки j-ro процессора кодом запрашиваемой функции с выхода 16, по которому также осуществляется обнуление j-ro разряда регистра 7 готовности, а на k-м выходе (12k) дешифратора

10 появляется сигнал подтвеждения k-му абоненту (источнику запроса) о завершении распределения запроса. По сигналу с формирователя 11 импульса осуществляется

обнуление счетчика 6 и увеличение на 1 содержимого счетчика 5. При этом к выходам мультиплексора 1 подается информация со входов 13 от (К+1)-го абонента. То 5 есть произошло распределение запроса от k-ro абонента в первую занятую ЭВМ, способную выполнить его, при отсутствии свободных.

При наличии 10 - ЭВМ, при частоте син0 хронизирующих импульсов равной 5 МГц (f 5 МГц) при полной загрузке системы максимальный выигрыш во времени распределения заявок по вычислительным машинам (процессорам) в предлагаемом устройстве,/

5 в сравнении с известным, на порядок, т.е. максимальное время распределения заявки в известном устройстве при отсутствии в системе свободных вычислительных ресурсов равно 2,2 мкс, а в предлагаемом устрой0 стве 0,2 мкс, минимальный выигрыш в два раза (4 и 2 мкс).

Ф о р м у л а и з о б р е т е н и я Устройство для распределения заданий процессорам, содержащее два счетчика,

5 регистр, генератор импульсов, два дешифратора, три мультиплексора, блок памяти и формирователь импульсов, причем выходы первого счетчика подключены к управляющим входам первого мультиплексора и к

0 информационным входам: первого дешифратора, выход генератора импульсов подключен к счетному входу второго счетчика;

информационные выходы которого соединены с первыми управляющими входами

.5 второго мультиплексора, с информационными входами второго дешифратора и с входами адреса столбца блока памяти, выходы первого мультиплексора подключены к выходам данных устройства и к входам адреса

0 строки блока памяти, информационные входы второго мультиплексора подключены к выходам регистра, выход формирователя импульсов подключен к управляющему входу первого дешифратора, к счетному входу

5 первого счетчика и к входу сброса второго счетчика, выходы первого дешифратора подключены к выходам подтверждения выбора устройства, группа выходов второго дешифратора подключена к группе выходов

0 запроса устройства и к группе входов сброса регистра, группа информационных входов которого подключена к группе входов занятости процессоров устройства, информационные входы первого мультиплексора

5 подключены к кодовым входам запроса устройства, 6 т л и чаю щ е е с я тем, что, с целью повышения быстродействия, в устройстве информационные входы третьего мультиплексора подключены к соответствующим выходам регистра, инверсный выход третьего

мультиплексора подключен к первому входущий вход - к выходу блока памяти к второму

формирователя импульсов, адресные входыи управляющему входу второго мультиплектретьего мультиплексора подключены к вы-сора, выход которого соединен с вторым

ходам первого мультиплексора, а управляю-входом формирователя импульсов.

| Устройство для распределения заданий процессорам | 1985 |

|

SU1285473A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-02-28—Публикация

1990-05-07—Подача