изобретение относится к вычислительной технике и может быть использовано в многомашинных и мультипроцессорных вьмислительных системах для распределения нагрузки между про цессорами.

Цель изобретения - упроп1ение устройства.

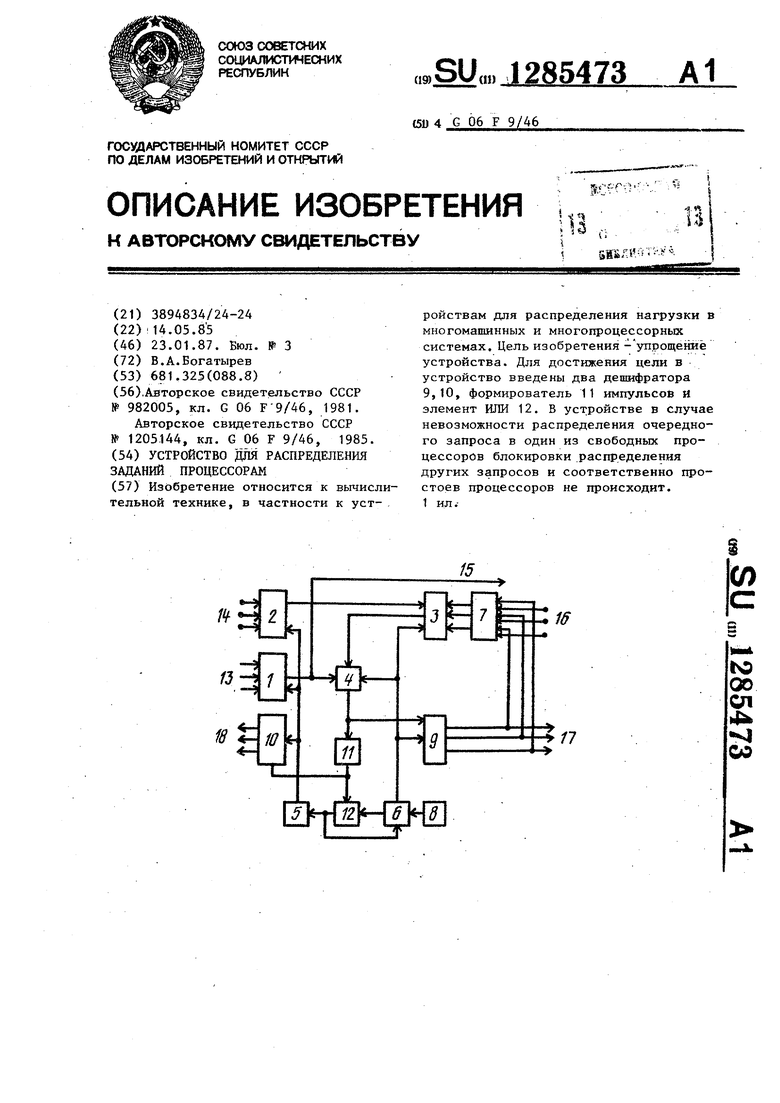

На чертеже представлена структурная схема устройства.

Устройство содержит три мультиплексора 1-3, блок 4 памяти, два счетчика 5 и 6, регистр 7, генератор 8 импульсов, два дешифратора 9 и 10, формирователь 11 импульсов и элемент ИЛИ 12,-Кодовые входы 13 запроса устройства, входы 14 подтверждения запроса устройства-, выход 15 данных устройства, входы 16 занятости процессора устройства, Ёыходы 17 запро- сов устройства, выходы 18 подтверж- дения выбора устройства.

Устройство работает следующим образом.

При распределении запросов счетчиком 5 осуществляется циклическое подключение абонентов (источников запросов) к устройству через мультиплексоры 1 и 2, а счетчиком 6 поочередная проверка процессоров (от первого до т-го) на незанятость и способность выполнить запрашиваемую функцию (прорамму) , Особенность работы устройства заключается в том, что если все процессоры, способные выполнить зап- рашиваемую от k-ro абонента функцию, заняты, to блокировки распределения запросов от других абонентов не происходит, а после завершения цикла подключения к устройству всех абонен тов повторяется попытка распределени запроси от k-ro абонента.

Отображение занятости процессоров осуществляется в регистре 7, в j-м разряде которого находится 1, если j-й процессор не занят, в противном случае в этом разряде находится О. Отображение функциональных возможностей процессоров осуществляется в блоке 4 памяти, ячейка которого 4;; содержит 1 если j-й процессор способен выполнить функцию f;, в противном случае в ней находится О.

Рассмотрим более подробно процесс распределения запросов, выставляемых абонентами на соответствующие входы 13 и сопровождаемые сигналами на соответствующих входах 14.

5

5

О

-5

5

0

„

При k-M состоянии счетчика 5 через мультиплексор 1 к выходу 15 подключа- ется кодовый вход 13,,. запроса от k-ro абонента, а через мультиплексор 2 к входу выборки мультиплексора 3 вход 14, на котором содержится сигнал при наличии запроса от k-ro абонента. Код запрашиваемой функции f; с выхода мультиплексора 1 подается на адресный вход строки блока 4 памяти, на вход адреса столбца которого подается код с выхода счетчика 6. На вход выборки блока 4 памяти через мультиплексор 3 подается содержимое j-ro разряда регистра 7 (j задается счетчиком 6 и меняется от О до m числа, определяемого количеством процессоров) .

Если в J-M разряде регистра 7 находится О, т.е. j-й процессор занят, то сигнала на выходе мультиплексора 3 нет, выборки блока 4 памяти не происходит и на его выходе сигнал не формируется. В таком состоянии устройство находится до прихода очередного импульса с генератора 8, по которому содержимое счетчика 6 увеличивается на 1 и к выходу мультиплексора 3 подключается выход (j+1)-ro разряда регистра 7 и т.д., до момента нахождения в выбранном разряде регистра 7 1. При считьюании через мультиплексор 3 1 на вход выборки блока 4 памяти поступает сигнал, по которому происходит чтение ячейки 4 ;j блока 4 памяти (адрес строки подается с выхода мультиплексора 1, а адрес столбца с выхода счетчика 6).

Если в ячейке 4;: содержится О (j-й процессор не может вьтолнять запрашиваемую функцию), то на выходе блока 4 памяти сигнал не формируется. Такое состояние устройства сохраняется до прихода очередного импульса с генератора 8.

Если в выбранной ячейке 4j: содержится 1 (j-й процессор способен выполнить запрашиваемую функцию fj), то на выходе блока 4 памяти формируется сигнал, по которо1-гу осуществляется выборка дешифратора 9. На j-м выходе дешифратора 9 при этом формируется сигнал загрузки j-ro процессора кодом запрашиваемой функции с выхода 15. По сигналу с JTTO выхода дешифратора 9 осуществляется также обнуление j-ro разряда регистра 7 готовности (запись 1 в этот разряд

происходит по сигналу , вырабатываемому J-M процессором после завершения выполнения им загруженной в него функции). После обнуления j-ro разряда регистра 7 сигнал на выходе мультиплексора 3 пропадает, в результате чего сигнал на выходе блока 4 памяти также пропадает: по заднему фронту этого сигнала на формирователе 11 импульса вьфабатывается короткий импульс, поступающий на вход выборки дешифратора 10. При этом на k-M выходе 18k появляется сигнал подтверждения k-му абоненту (источнику запросов) о завершении распределения запроса. По сигналу с формирователя 11 импульса через элемент ИЛИ 12 после выдачи сигнала подтверждения абоненту осуществляется обнуление счетчика 6 и увеличение на 1 содержимого счетчика 5. При этом к выходам мультиплексоров 1 и 2 подается информация с входов 13 и 14 от ()-гo абонента.

Если при изменении состояний счет чика 6 от О до т на выходе блока 4 памяти сигнала не формируется, что происходит, если все процессоры, способные выполнить распределяемый запрос от k-ro абонента, заняты, то по сигналу переноса со счетчика 6 содержимое счетчика 5 увеличивается и начинается распределение от (k + + 1)-го абонента. Таким образом, на рассматриваемом цикле распределения запорос от k-ro абонента остается не распределенным, при этом, k-й абонент запроса не снимает. Попытка распределения запроса от k-ro абонента циклически повторяется калздый раз, когда в счетчике 5 формируется адрес этого абонента (номер абонента - k). Если через мультиплексор 1 и 2 к устройству подключается абонент, не выставивший запроса (на соответствующем входе 14 устройства - О), то на выходе мультиплексора 2 сигнал не (формируется, выборки мультиплексора 3 и блока 4 памят и не происходит и соответственно распределение не осуществляется. При этом опрос следующего по очереди абонента происходит при увеличении содержимого счетчика 5 сигналом переноса с счетчика 6.

ВНИШШ Заказ 7526/51

Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Формула изобретения Устройство для распределения заданий процессорам, содержащее три мультиплексора, блок памяти, два счетчи

ходы первого счетчика подключены к управляющим входам первого и второго мультиплексоров, выход генератора импульсов подключен к счетному входу второго счетчика, информационные выходы которого соединены с первыми уп равляющими входами третьего мультиплексора, отличающееся тем, что, с целью упрощения, в него введены два дешифратора, формирователь импульсов и элемент ИЛИ, причем выходы первого мультиплексора подключены к выходу данных устройства и к первым входам адреса блока памяти, вход выборки блока памяти подключен к выходу третьего мультиплексора, вы- ;годы второго счетчика подключены к вторым входам адреса блока памяти, к информационным входам первого де- шифратора, выход блока памяти подключен к входу формирователя импульса и к управляющему входу первого дешифратора, выход формирователя импульса подключен к первому входу элемента ИЛИ и к управляющему входу второго дешифратора, выходы второго дешифратора подключены к выходам подтверждения выбора устройства,.выход переноса второго счетчика подключен к второму входу элемента ИЛИ, выход которого подключен к счетному входу первого счетчика и к входу сброса второподключены к информационным входам второго дешифратора, выход второго мультиплексора подключен к второму управляющему входу третьего мультиплексора, информационные входы которого подключены к выходам регистра, группа выходов первого дешифратора подключена к группе выходов запроса устройства и к первой группе информационных входов регистра, вторая группа информационных входов которого подключена к группе входов занятости процессора устройства, информационный входы первого мультиплексора подключены к кодовым входам запроса устройства, информационные входы второго мультиплексора подключены к входам подтверждения запроса устройства.

.Тираж 670

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1985 |

|

SU1285474A1 |

| Устройство для распределения заданий процессорам | 1990 |

|

SU1798783A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1317438A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1278848A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

Изобретение относится к вычислительной технике, в частности к уст- , ройствам для распределения нагрузки в многомашинных и многопроцессорных системах. Цель изобретения - упрощение устройства. Для достижения цели в устройство введены два депшфратора 9,10, формирователь 11 импульсов я элемент ИЛИ 12. В устройстве в случае невозможности распределения очередного запроса в один из свободных процессоров блокировки .распределения других запросов и соответственно простоев процессоров не происходит. 1 ил.(П /7 ю 00 сл 4 ч1 со

| Устройство для распределения задач между процессорами | 1981 |

|

SU982005A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1205144A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-23—Публикация

1985-05-14—Подача