Изобретение относится к импульсной технике и предназначено для использования во входных логических цепях широкополосных времяимпульсных преобразователей и измерительных приборов-частотомеров, фазометров, а также обнаружителей сигналов на фоне широкополосных помех.

Цель изобретения - повышение помехоустойчивости при ограниченной скорости изменения.частоты входного сигнала.

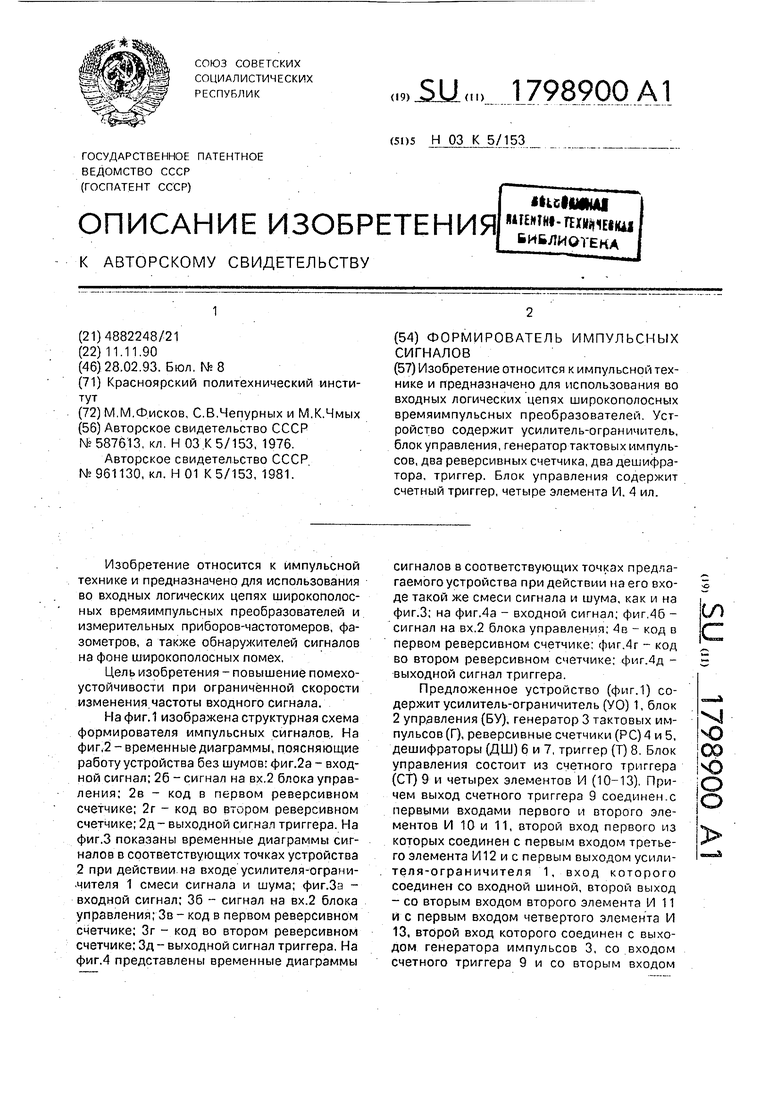

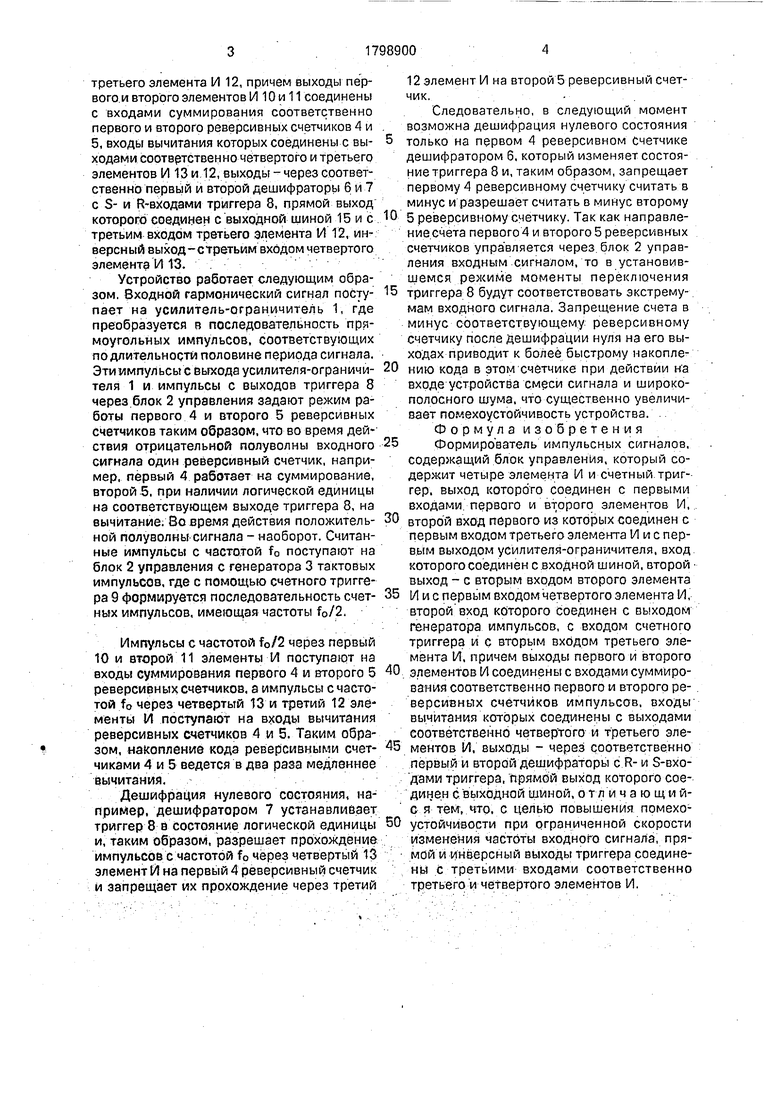

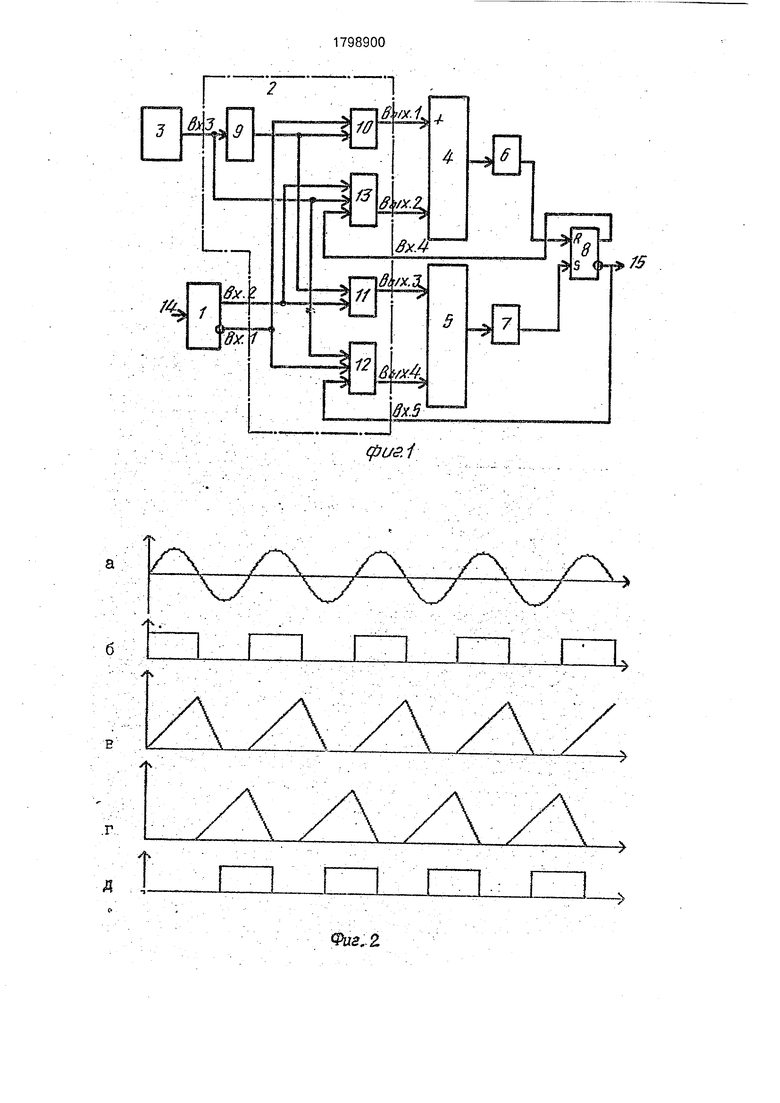

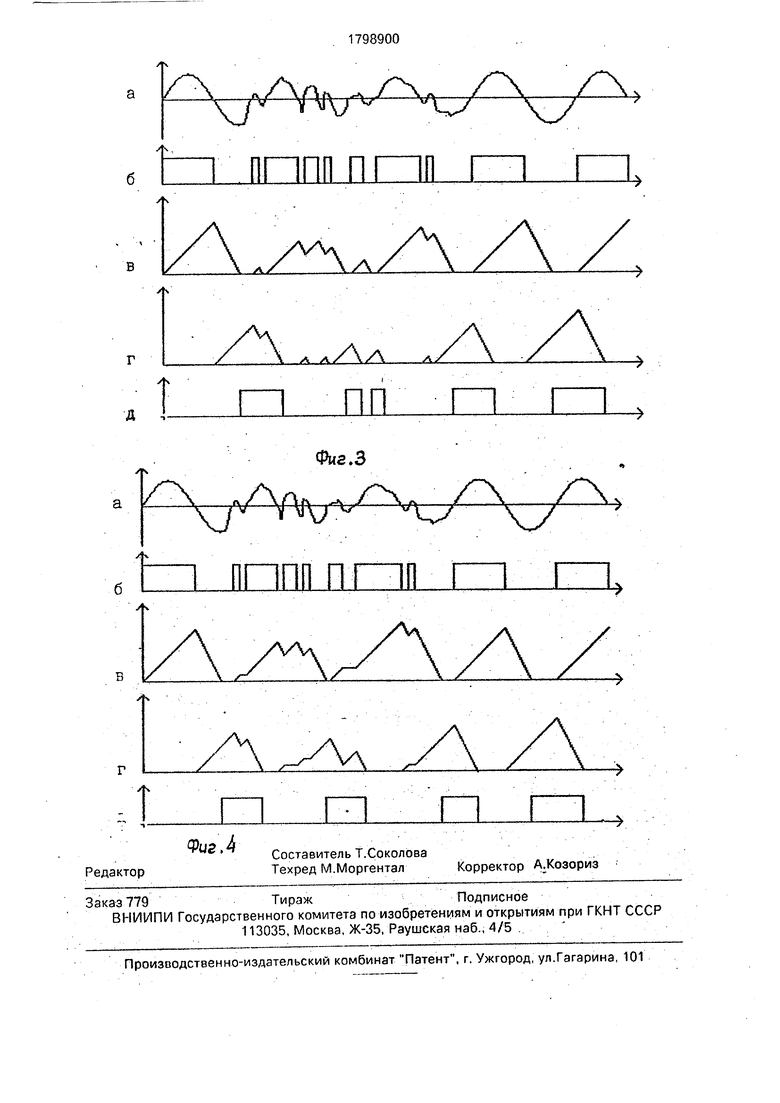

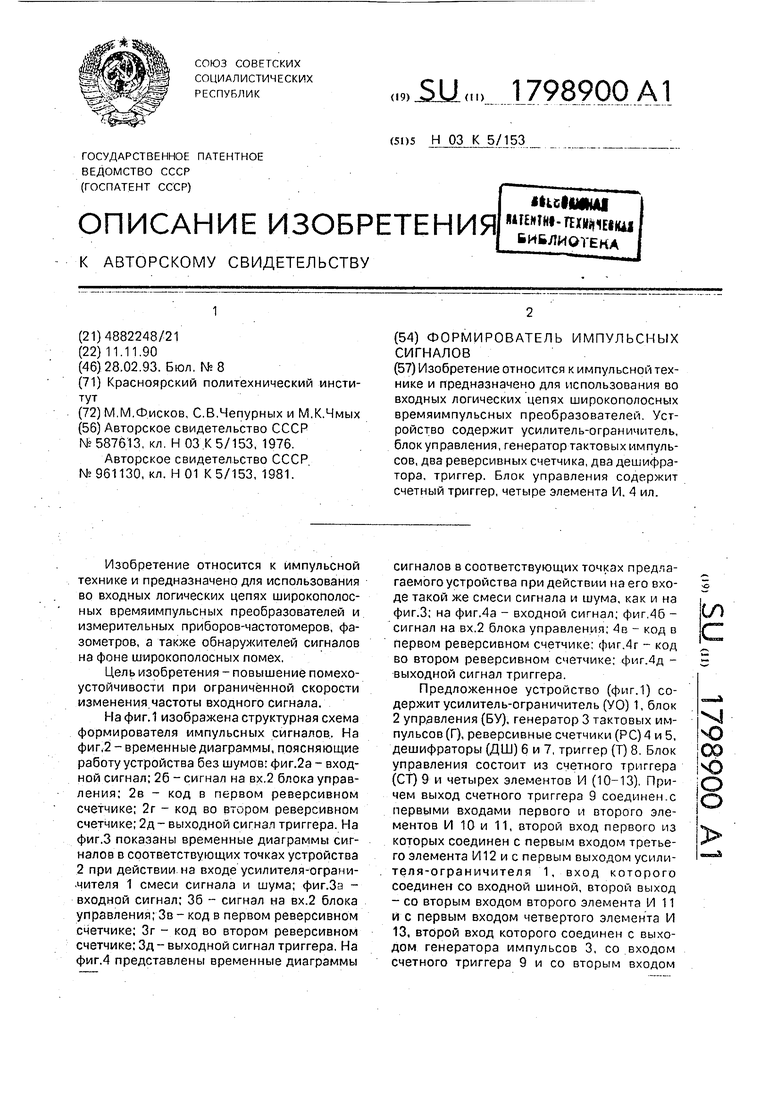

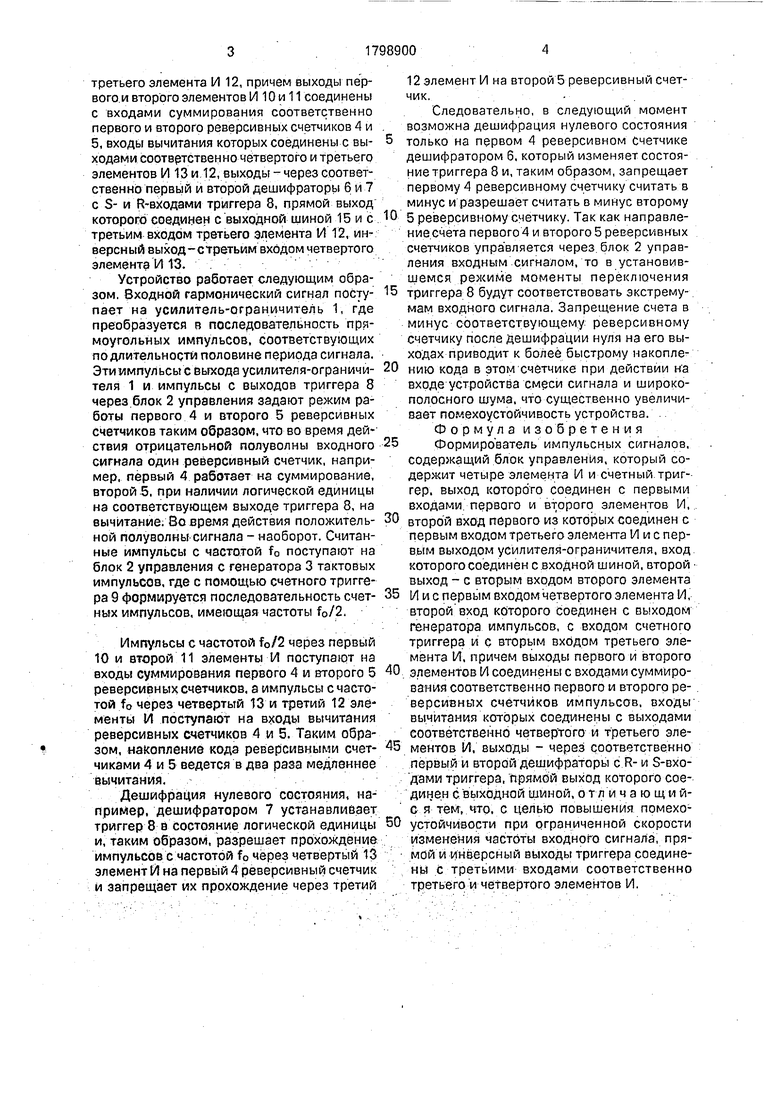

На фиг.1 изображена структурная схема формирователя импульсных сигналов.. На фиг,2-временные диаграммы, поясняющие работу устройства без шумов: фиг.2а - входной сигнал; 26 - сигнал на вх.2 блока управления; 2в - код в первом реверсивном счетчике; 2г - код во втором реверсивном счетчике; 2д - выходной сигнал триггера. На фиг.З показаны временные диаграммы сигналов в соответствующих точках устройства 2 при действии на входе усилителя-ограни- чителя 1 смеси сигнала и шума; фиг.Зз - входной сигнал; 36 - сигнал на вх.2 блока управления;Зв - код в первом реверсивном счетчике; Зг - код во втором реверсивном счетчике; Зд - выходной сигнал триггера. На фиг.4 представлены временные диаграммы

сигналов в соответствующих точках предлагаемого устройства при действии на его входе такой же смеси сигнала и шума, как и на фиг.З; на фиг.4а - входной сигнал; фиг.46 - сигнал на вх.2 блока управления; 4в - код в первом реверсивном счетчике; фиг.4г - код во втором реверсивном счетчике; фиг.4д - выходной сигнал триггера.

Предложенное устройство (фиг.1) содержит усилитель-ограничитель (УО) 1, блок 2 управления (БУ), генератор 3 тактовых импульсов (Г), реверсивные счетчики (PC) 4 и 5, дешифраторы (ДШ) 6 и 7, триггер (Т) 8. Блок управления состоит из счетного триггера (СТ) 9 и четырех элементов И (10-13). Причем выход счетного триггера 9 соединен.с первыми входами первого и второго элементов И 10 и 11, второй вход первого из которых соединен с первым входом третьего элемента И12 и с первым выходом усилителя-ограничителя 1, вход которого соединен со входной шиной, второй выход - со вторым входом второго элемента И 11 и с первым входом четвертого элемента И 13, второй вход которого соединен с выходом генератора импульсов 3, со входом счетного триггера 9 и со вторым входом

ел

С

ч

00 Ю О

третьего элемента И 12, причем выходы пер- вого.и второго элементов И 10 и 11 соединены с входами суммирования соответственно первого и второго реверсивных счетчиков 4 и 5, входы вычитания которых соединены с выходами соответственно четвертого и третьего элементов И 13 и 12, выходы - через соответственно первый и второй дешифраторы 6 и 7 с S- и R-входами триггера 8, прямой выход которого соединен с выходной шиной 15 и с третьим входом третьего элемента И 12, инверсный выход-стретьим входом четвертого элемента И 13.

Устройство работает следующим образом, входной гармонический сигнал поступает на усилитель-ограничитель 1, где преобразуется в последовательность прямоугольных импульсов, соответствующих по длительности половине периода сигнала. Эти импульсы с выхода усилителя-ограничителя 1 и импульсы с выходов триггера 8 через блок 2 управления задают режим работы первого 4 и второго 5 реверсивных счетчиков таким образом, что во время действия отрицательной полуволны входного сигнала один реверсивный счетчик, например, первый 4 работает на суммирование, второй 5, при наличии логической единицы на соответствующем выходе триггера 8, на вычитание; Во время действия положительной полуволны сигнала - наоборот. Считанные импульсы с частотой f0 поступают на блок 2 управления с генератора 3 тактовых импульсов, где с помощью счетного триггера 9 формируется последовательность счетных импульсов, имеющая частоты f0/2.

Импульсы с частотой W2 через первый 10 и второй 11 элементы И поступают на входы суммирования первого 4 и второго 5 реверсивных счетчиков, а импульсы с частотой f0 через четвертый 13 и третий 12 эле менты И поступают на входы вычитания реверсивных счетчиков 4 и 5. Таким образом, накопление кода реверсивными счетчиками 4 и 5 ведется в два раза медленнее вычитания.

Дешифрация нулевого состояния, например, дешифратором 7 устанавливает триггер 8 в состояние логической единицы и, таким образом, разрешает прохождение импульсов с частотой f0 через четвертый 13 элемент И на первый 4 реверсивный счетчик и запрещает их прохождение через третий

12 элемент И на второй 5 реверсивный счетчик.

Следовательно, в следующий момент возможна дешифрация нулевого состояния

только на первом 4 реверсивном счетчике дешифратором б, который изменяет состояние триггера 8 и, таким образом, запрещает первому 4 реверсивному счетчику считать в минус и разрешает считать в минус второму

5 реверсивному счетчику. Так как направле- ние.счета первого 4 и второго 5 реверсивных счетчиков управляется через, блок 2 управления входным сигналом, то в установившемся, режиме моменты переключения

триггера 8 будут соответствовать экстремумам входного сигнала. Запрещение счета в минус соответствующему реверсивному счетчику после дешифрации нуля на его выходах приводит к более быстрому накоплению кода в этом счетчике при действии на входе устройства смеси сигнала и широкополосного шума, что существенно увеличивает помехоустойчивость устройства. . Формула изобретения

Формирователь импульсных сигналов, содержащий блок управления, который содержит четыре элемента И и счетный триггер, выход которого соединен с первыми входами, первого и второго элементов И,

второй вход первого из которых соединен с первым входом третьего элемента И и с первым выходом усилителя-ограничителя, вход которого соединен с.входной шиной, второй выход - с вторым входом второго элемента

И и с первым входом четвертого элемента И, второй вход которого соединен с выходом генератора импульсов, с входом счетного триггера и с вторым входом третьего элемента l/l, причем выходы первого и второго

элементов И соединены с входами суммирования соответственно первого и второго реверсивных счётчиков импульсов, входы вычитания которых соединены с выходами соответственно четвертого и третьего элементов И, выходы - через соответственно первый и второй дешифраторы с R- и S-вхо- дами триггера, (прямой выход которого соединен с выходной шиной, о т л и чающий- с я тем, что, с целью повышения помехоустойчивости при ограниченной скорости изменения частоты входного сигнала, прямой и инверсный выходы триггера соединены с третьими входами соответственно третьего и четвертого элементов И.

(fJU& 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсных сигналов | 1981 |

|

SU961130A1 |

| Формирователь импульсных сигналов | 1988 |

|

SU1635254A2 |

| Коррелятор | 1981 |

|

SU1024933A1 |

| Цифровой измеритель магнитной индукции | 1989 |

|

SU1709257A1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2003 |

|

RU2241273C1 |

| Цифровой фазометр | 1981 |

|

SU1273831A1 |

| Формирователь импульсных сигналов | 1984 |

|

SU1181126A1 |

| Устройство для контроля внеполосных спектров излучения радиопередатчиков | 1989 |

|

SU1674389A1 |

| Цифровой умножитель частоты | 1977 |

|

SU691853A1 |

| Способ измерения фазового сдвига между двумя гармоническими сигналами и устройство для его осуществления | 1988 |

|

SU1596272A1 |

Изобретение относится к импульсной технике и предназначено для использования во входных логических цепях широкополосных времяимпульсных преобразователей. Устройство содержит усилитель-ограничитель, блок управления, генератор тактовых импульсов, два реверсивных счетчика, два дешифратора, триггер. Блок управления содержит счетный триггер, четыре элемента И. 4 ил.

Т

Д IФигг2

я I ГП ПП

Фиг.З

| Устройство для фиксации моментов времени,соответствующих фазе синусоидального сигнала | 1976 |

|

SU587613A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР | |||

| Формирователь импульсных сигналов | 1981 |

|

SU961130A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-02-28—Публикация

1990-11-11—Подача