I

Изобретение относится к области автоматики и вычислительной техники, в частности, к устройствам для умножения низких и иифранизких частот.

Известно устройства для умножения частоты, содержащее генератор импульсов, два управляемых делителя частоты, элемент задержки, счетчик, группу элементов И и.регистр памяти 11

Известно также устройство для умножения частоты, содержащее формирователь, блок управления, элементы И и ИЛИ, генератор тактовьк импульсов, триггер, делитель частоты, счетчик импульсов, реверсивный счетчик, группы элементов И и наборное поле 12.

Общим недостатком известных устройств является понюке}шая точность умножения частоты при высоких требованиях по быстродействию.

Наиболее близким по техническо11 сущности к предложенному является Щ1фровой зп 1ножитель частоты, содержащий усилитель-ограничитель, .соединённый входом с входом цифрового умножителя частоты и подключенный выходами к входам амплитудных дискримина

тОров, триггеры, выход первого из которых соединен с выходом цифрового умножителя частоты, а выход второго триггера подключен к первому входу основного элемента И, соединенного выходом со счетным входом основного счетчика, вькоды которого подключены к цифровым входам управляемого делителя частоты, соединенного счетным входом с выходом генератора импульсов и подключенного вь1ходом к входу формирователя импульсов : ввода 3.

; Данный цифровой умножитель имеет быстродействие, равное полупериоду .входной частоты, к практически не имеет погрещности несимметрии ограничения. Недостатками прототипа являются наличие погрещности умножителя, обусловленной отклонением входной частоты от оптимальной, и наличие погрешности умножения, обусловленной ошибками выполнения время-импульсного преобразования.

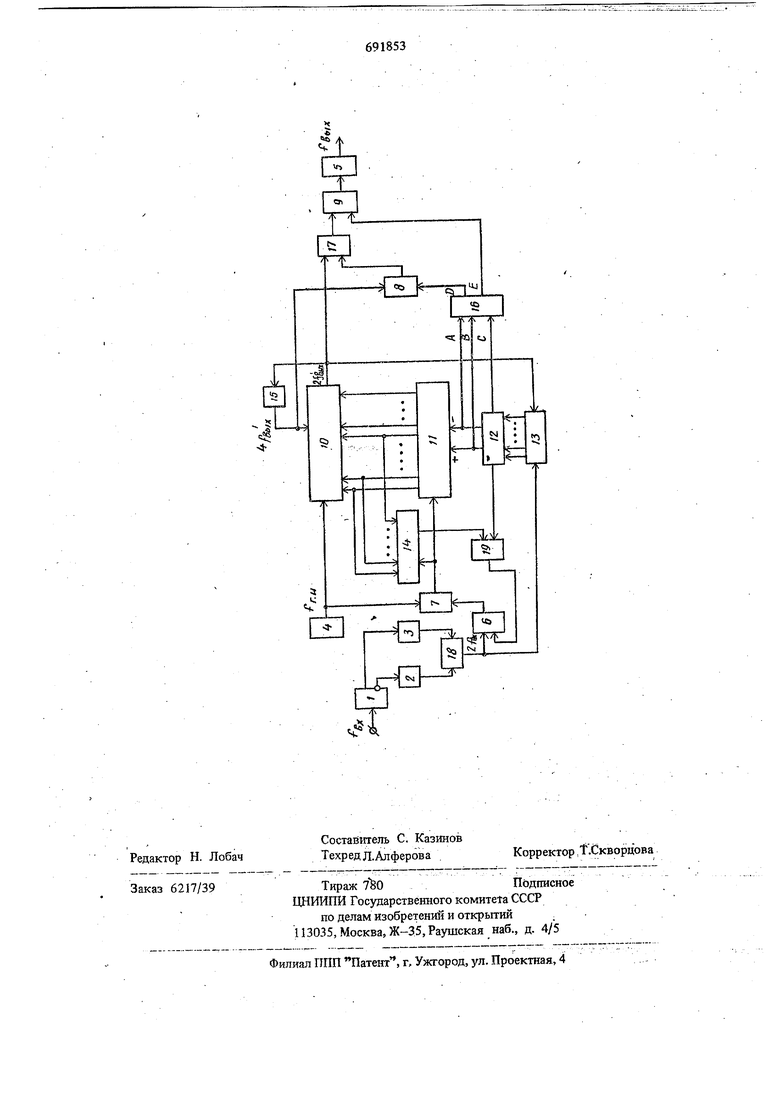

Целью настоящего изобретения является (повышение точности умножения в широком диапазоне частот. 36 Поставленная цель достигается тем, что в цифровой умножитель частоты дополнительно введены счетчики, элементы И и ИЛИ, дешиф ратор коррекции и основной дешифратор, под ключенный входами к выходам первого дополнительного счетчика, соединенного первым входом с первым входом первого элемента ИЛИ и выходом управляемого делителя Частоты и подключенного вторым входом к |В,ыходу второго элемента ИЛИ, входы которого соединены с выходами амплитудных дискриминаторов, и к первому входу второго триггера, соединенного вторым входом с выходом третьего элемента ИЛИ, первый вход которого подключен к первому выходу основного дешифратора, а второй вход соединен с ВЫХОДОМ второго дополнительного счетчика, подключенного счетным входом к выходу основного элемента И, соединенного вторым вхо дом с выходом генератора импульсов, причем поразрядные входы второго дополнительного счетчика подключены к соответствующим выходам основного счетчика, соединенного суммирующим и вычитающим входами соответственно со вторым и третьим выходами основ ного дешифратора, подключенного вторым, третьим и четвертым выходами к входам дешифратора коррекции, выходы которого соединены с первыми входами первого и второго дополнительных элементов И, причем выход первого дополнительного элемента И, соединен ного вторым входом с выходом формирователя импульсов ввода и управляющим входом управляемого делителя частоты, соедйнен со вторым входом первого элемента ИЛИ, подключе1шого выходом ко второму входу второго дополнительного элемента И, выход кото рого соединен с входом первого триггера. Существо изобретения поясняется чертежом, на котором изображена блок-схема умножителя. Цифровой умножитель частоты содержит усилитель-ограничитель 1, амплитудные дискри минаторы 2 и 3, генератор 4 импульсов, первый и второй триггеры 5 и 6, основной элемент И 7, первый и второй дополнительные элементы И 8 и 9, управляемый делитель 10 ча стоты, основной счетчик 11, основной дешиф ратор 12, первый и второй дополнительные счетчики 13 и 14, формирователь 15 импульсов ввода, дешифратор 16 коррекции, первый второй и третий элементы ИЛИ 17, 18 и 19. Выходы усилителя I соедйненьГчер соответствующие дискриминаторы 2 и 3 со входами элемента ИЛИ 18, подключенного выходом к первому входу триггера 6 и второму входу счётчика 13, первый вход которого соединен с выходом управляемого делителя 10 частоты. ВХОДОМ формирователя 15 и первым входом элемента ИЛИ 17. Выход триггера 6, подключенного вторым входом к выходу элемента ИЛИ 19, соединен с первым входом элемента И 7, второй вход которого подключен к выходу генератора 4 импульсов и счетному входу управляемого делителя 10 частоты, а выход элемента И 7 соединен со счетными входами счетчиков 11 и 14. Входы элемента ИЛИ 19 подключены к первому выходу основного дешифратора 12 и выходу счетчика 14, соединенного поразрядными входами с соответствующими выходами счетчика 11, суммирующий и вычитающий входы которого подключены к второму и третьему выходам основного дешифратора 12. Управляющий вход управляемого делителя 10 частоты, соединенного цифрОвь1ми входами с выходами счетчика ll, подключен к выходу формирователя 15 и второму входу элемента И 8, выход которого соединен с вторым входом элемента ИЛИ 17. Выходы дешифратора 16 коррекции, подключенного входами к второму, третьему и четвертому выходам Основного дешифратора 12, соединены с первыми входами элементов И 8 и 9. Выход элемента И 9, подключенного вторым входом к выходу элемента ИЛИ 17, соединен через триггер 5 с выходом устройства. Цифровой умножитель частоты работает следующим образом. При синусоидальном входном сигнале входное воздействие подается на вход усилителяограничителя 1, где ограничивается. Затем выходные противофазные напряжения усилителя 1 дискриминируются двумя идентичными дискриминаторами 2 и 3 (их моменты срабатывания могут быть совмещены с положительными нульпереходами сигнала). Импульсные сигналы через элемент ИЛИ 18 с двойной частотой 2fBx поступают на первый вход триггера 6, устанавливая его каждым импульсом в единичное состояние и давая разрешение на прохождение импульсов высокой частоты fj-H с выхода генератора 4 через элемент I И 7 на счетные входы счетчиков II и 14. Счетчик 11 выполнен реверсивным, изменение его состояния в сторону увеличения или уменьшения выходного кода М достигается сигналами с выходов основного дешифратора 12. Переключение на сложение или вычитание определяется знаком рассогласования по частот;е. Так, если febix (где п - коэффициент умножения умножителя), то сигнал рассогласования А О, и сигналом с первого выхода основного дешифратора 12 триггер 6 через элемент ИЛИ 19 сбрасывается, запрещая .прохождение импульсов с генератора 4 на счетные входы счетчиков Пи 14. Выходной код счетчика 11 имеет в установившемся режиме постоянное зиачение, равюе М и определяющее коэффициент деления q управляемого делителя 10 q 2-M, где k - разрядност дейителя 10 частотЫ;. Требуемое изменение выходной частоты ум- ножителя достигается изменением козффипиента q с Помощью счетчика 11 по результатам подсчета в счетчике 13 суммы Д п импульсов частоты 2 fsbix с выхода делителя 10 частоты за период входной частоты fax умножителя. Для обеспечения режима слежения за изменением входной частоты в широком частотном диапазоне, изменение Л q коэффициента деления делителя 10 частоты формируется не толь ко в виде функции вышеуказанного рассогласования Д п, но и в виде функции входной частоты, причем выполняется соотношение Л - const Для вьшолпения данного соотношения используется счетчик 14, включенный в контур внутренней обратной связи управления воздействием счетчика 11 на делитель 10 частоты. При этом, на сравнительно низких входных частотах управляющее воздействие М изменяется на большую величину, позволяющую более эффективно компенсировать ошибку умно жения. При более высокой входной частоте управляющее воздействие изменяется на меньшую величину, чем достигается меиьщая динамическая ошибка. Для обеспечения нормального характера протекания переходных процес сов, поразрядные входы счетчика 14 подключаются только к выходам старших разрядов счетчика 11. Время, в течение которого происходит коррекция воздействия М путем соответствующего суммирования или вычитания импульсов с выхода генератора 4 в счетчике 11, регулируется сбросом триггера 6 через элемент ИЛИ 19 сигналом с первого выхо;ла основного дешифратора 12 или сигналом с выхода счетчика 14. Для нормального функционирования без режима автоколебаний ъ установившемся состоянии в умножителе с помощью основного дешифратора 12 искусственно создается зона нечувствительности, которой .соответствует сигнал на первом выходе дешифратора 12. - Выходные импульсы 2 с выхода управляемого делителя 10, возникающие вследствие периодического переполнения счетчика делителя 10, поступают на первый вход элемента ИЛИ 17 и на вход формирователя 15 импульсов. С помощью формирователя 15 осуществляется ввод в делитель 10 кода М с удвоенной частотой по отношению к частоте 2 fBbix что позволяет улучшить динамические характеристики устройстэа. Для устранения ошибки по фазе, обуслов енной дискретностью изменения коэффициен-, та деления управляемого делителя 10, используется фазовая коррекция, реализова1шая на элементах И 8 и 9, дешифраторе 16 коррек1ЩИ и элементе ИЛИ 17. Фазовая коррекщм осуществляется за счет добавления или вычитания из выходной последовательности требуемого количества импульсов. Дешифратор 16 коррекции (выполненный, например, на триггерах и элементах И), управляет отпиранием элементов И 8 и 9 в соответствии с таблицей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты | 1977 |

|

SU693373A1 |

| Преобразователь перемещений в код | 1978 |

|

SU746652A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1012431A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928352A1 |

| Следящий умножитель частоты | 1979 |

|

SU832556A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928353A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Умножитель частоты | 1988 |

|

SU1614096A1 |

| Устройство для измерения показателя тепловой инерции частотных термодатчиков | 1982 |

|

SU1075090A1 |

| Интегратор азимутных импульсов | 1977 |

|

SU691877A2 |

ОО1

01О

100

На вход С поступает сигнал с четвертого выхода дешифратора 12, т.е. сигнал, соответ- ствующий отсутствию рассогласования (без зоны нечувствительности, так как в данном случае оно не влияет на возникновение режима автоколебаний). В этом случае фазовая коррекция не производится.

1 1 О

О 1 О

При поступлении сигнала на вход В (со второго выхода дешифратора 12), коррекция /эсуществляется добавлением импульсов с частотой 4 fBbix к выходной, последовательности 2 fflbix через элемент И 8.

При постуЫении сигнала на втод А, коррекция осуществляется путем подавления импульсов частоты 2 fsbix за счет запирания эле мента И 9 на требуемое время. Количество суммируемых или вычитаемых (подавляемых) дополнительных импульсов определяется сигналами рассогласования с выхода дешифратора 12 и может регулироваться дешифратором 16. Практически происходит добавление или вычитание 1-3-х импульсов , что позволяет приблизительно в 2 раза уменьшить время переходного процесса. Для получения формы сигнала умноженной частоты типа меандр - вькодной сигнал с эле мента И 9 делится на два триггером 5. Таким образом, данное устройство по сравнению с прототипом имеет улучшенные статичёские и динамические Характеристики в широ ком диапазоне частот, Повьп11ение точности умножения достигается за счет использования отрицательной обратной связи по частоте в сочетании с корректирующим воздействием, позволяющим стабилизировать относительный шаг коррекции в широком диапазоне частот, . соответствующего выбора диапазона частот и . зоны нечувствительности, а также использования фазовой коррекции. При правильно выбранных схемных элементах устройство позво.ляет в широком диапазоне частот снизить погрешность время-импульсного преобразования в Кд раз, где Кд коэффициент деления депителя частоты п рото1ипа.;; Формула изобретения Цифровой умножитель частоты, содержащий усилитель-ограничитель, Соединенный входом с входом цифрового умножителя частоть, а выходами - с входами амплитудных дискриминаторов, триггеры, выход первого из которых соединен с выходом цифрового умножителя частоты, а выхся второго триггера подключен к первому входу основного элемента И, соединенного выходом со счетным входом основного счетчика, выходы которого подключены к цифровым входам управляемого делителя Частоты, соединенного счетным входом с выходом генератора импульсов и подключенного выходом к входу формирователя импульсов 6 8 ввода, отличающийся тем, что, с целью повышения точности умножения в широком диапазоне частот, в цифровой умножитель частоты дополнительно введены счетчики, элементы И и ИЛИ, дешифратор коррекции и основной дешифратор, подключенный входами к выходам первого дополнительного счетчика, соединенного первым входом с первым входом первого элемента ИЛИ и выходом управляемого делителя частоты и подключенного вторым входом к выходу второго элемен- та ИЛИ, входы которого соединены с выходами амплитудных дискриминаторов, и к первому входу второго триггера, соединенного вторым входом с выходом третьего элемента ИЛИ, первый вход которого подкгаочен к первому выходу основного дешифратора, а второй вход соединен с выходом второго дополнительного счетчика, подключенного счетitbiM входом к выходу основного элемента И, соедш енного вторым входом с выходом генератора импульсов, причем поразрядные входы второго дополнительного счетчика подключе.ны к соответствующим вьродам основного счетчика, соединенного суммирующим и вычитающим входами соответственно со вторым и третьим выходами основного дещифратора, подключенного вторым, третьим и четвертым выходами к входам деишфратора коррекции, выходы которого соединены с первыми входами первого и второго дополнительных элементов И, причем вь1ход первого дополнительного элемента И, подключенного вторым входом к выходу формирователя импульсов ввода и управляющему входу управляемого делителя частоты, соединен CQ вторым входом первого элемента ИЛИ, подключенного выходом к второму входу второго дополнительного элемента И, выход которого соединен с входом первого триггера, Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 580555, кл. G 06 F 7/52, 1976. 2.Авторское свидетельство СССР № 479805, кл. G 06 F 7/39, 1972. 3. Техника средств связи , серия Радиоизмерительная техника, М., вып. 6, 1976, с. 96.

Авторы

Даты

1979-10-15—Публикация

1977-07-25—Подача