Изобретение относится к вычислительной технике и может быть использовано для построения высоконадежных электронных вычислительных машин, комплексов и систем управления объектами или технологическими процессами.

Целью изобретения является повышение надежности вычислительной системы за счет увеличения гибкости резервирования узлов и повышения достоверности при приеме, обработке и передаче информации.

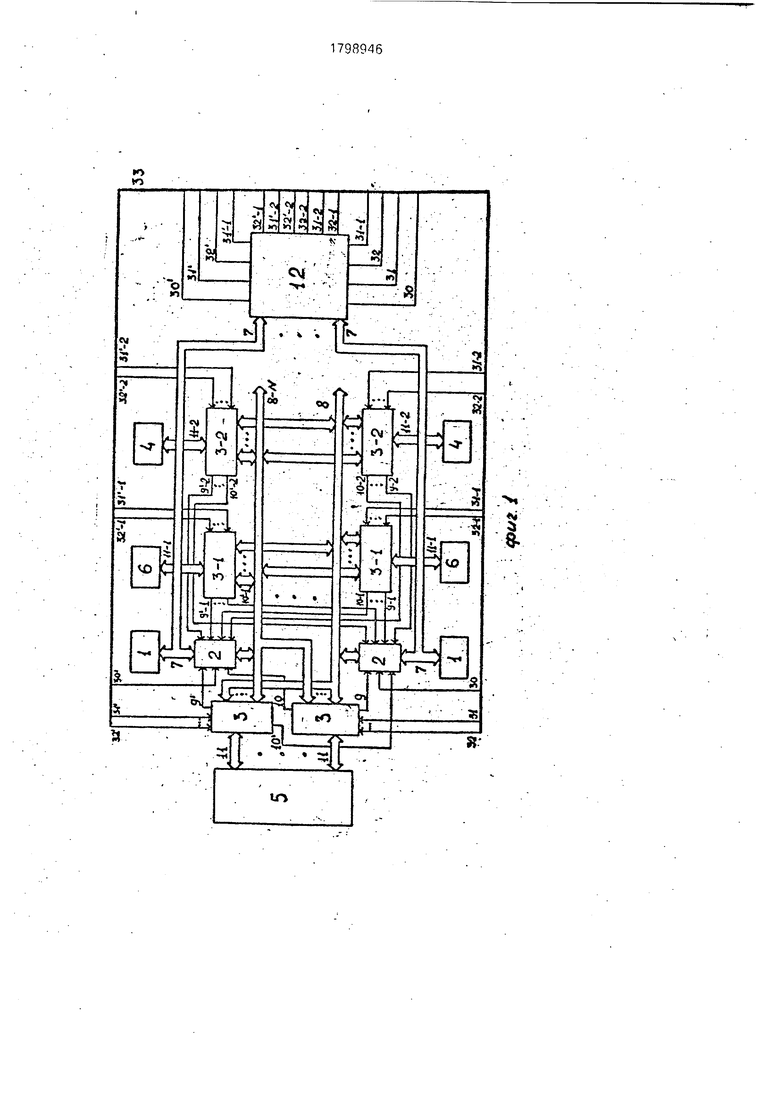

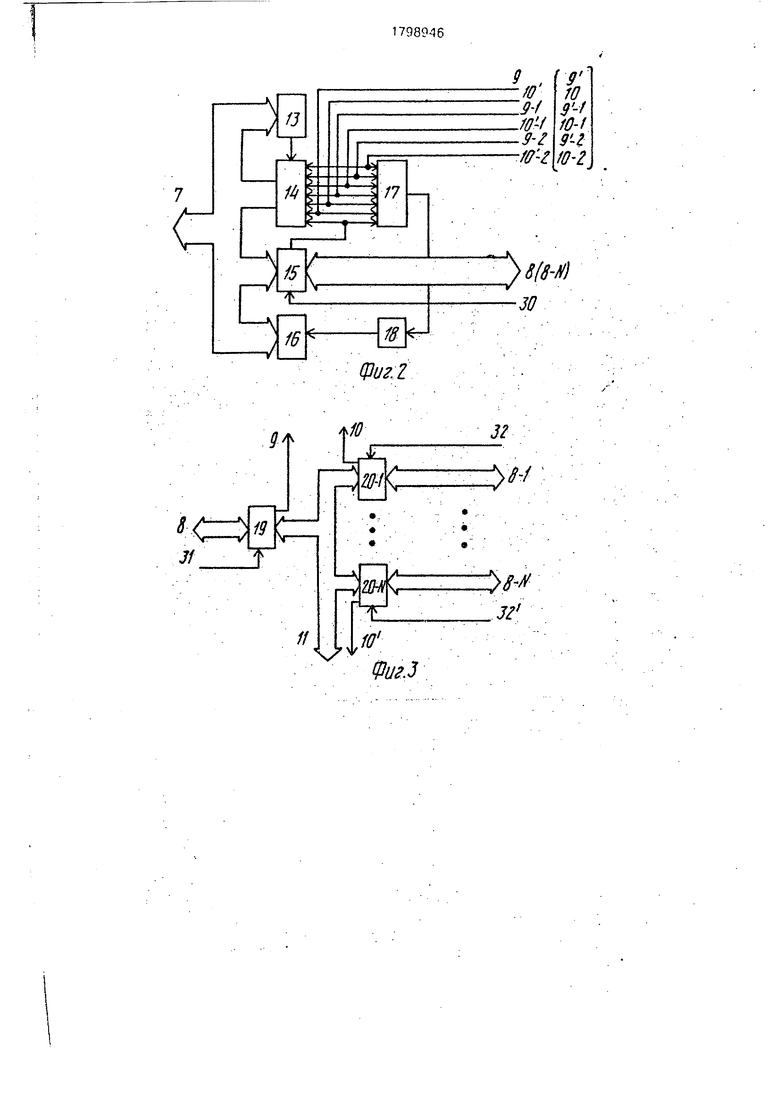

На фиг.1 представлена структурная схема предлагаемой системы; на фиг.2 - функциональная схема блока контроля; на фиг.З - функциональная схема коммутатора; на фиг.4 - функциональная схема блока управления резервированием; на фиг.5 - функци- ональная схема узла управления реконфигурацией; на фиг.6 - функциональная схема узла прерывания.

Резервированная вычислительная система содержит блок 12 управления резервированием, модуль 5 памяти и группу резервируемых каналов, каждый из которых содержит процессор 1 модуль 6 локальной памяти, блок 2 контроля, коммутатор 3 обмена, группу 3-1; 3-2 коммутаторов, блок 4 ввода-вывода, причем N процессорных .1 блоков своими внутренними шинами соединены с соответствующими шинами блока 12 управления резервированием. Через блоки 2 контроля внутренние, шины 7 процессорных 1 блоков соединены с магистралями 8 соответствующих N каналов. Коммутаторы 3 обмена и группа 3-1, 3-2 коммутаторов с одной стороны соединены с магистралями 8 всех N каналов, а с другой стороны - с соответствующими шинами 11 N-входового мо- дуля 5 памяти, с шинами 11-1 соответствующих модулей 6 локальной памяти и с шинами 11-2 блоков ввода-вывода. Управляющие выходы 9, 10 готовности коммутаторов 3,3-1, 3-2 каждого канала соединены с соответствующими управляющими

СП

С

VI

Ю 00 Ю

J

QS

входами блоков 2 контроля всех каналов. Управляющие выходы 30-32 блока 12 управления резервированием соединены с соответствующими входами коммутаторов 3, 3-4, 3-2 и блоков 2 контроля всех каналов.

Блок 2 контроля (фиг.2) содержит: селектор 13 адреса, регистр 14 состояния, магистральные ;15 гфием.опередатчики. блок 16 прерывания, элемент ИЛИ 17, одновмб- ратор 18.

Коммутаторы 3, 3-1, 3-2 (фиг.З) содержат магистральные 19, 2.0 приемопередатчики.

Блок 12 управления резервированием (фиг„4) содержит селектор 21 адреса, регистр 22 управления, регистр 23 реконфигурации, узел 24 сравнения, таймер 25, элементы ИЛИ 26, 28, узел 27 управления, узел 29 прерывания..

Узел 27 управления реконфигурацией (фиг,5), входящий в блок 12 управления резервированием, содержит входные 39, 40 регистры, постоянные 41, 44 запоминающие устройства, выходные 45, 46 регистры, генератор 42, элемент 43 задержки, шифра тор47.

Узел 29 прерывания (фиг.б), входящий в блок 12 управления резервированием,содержит: элемент И 48, элементы НЕ 49; 49- N, триггеры 50, 50-N формирователи сигналов ОТВ(СИП), триггеры 51; 51-М-фор- мирователи сигналов ТПР, регистр 52 адреса вектора прерывания,.магистральные 53. 53-N приемопередатчики, элементы 59, 59- N развязки. .,,.

Система работает следующим образом. В исходном состоянии на управляющих 30-32 выходах блока 12 управления резервированием устанавливаются сигналы, открывающие магистральные 15 приемопередатчики всех блоков2 контроля, Кроме того, в коммутаторах 3. 3-1, 3-2 открываются магистральные 19 приемопередатчики, подключающие выходные 11 шины боков 3, 3-1. 3-2 к магистрали 8 собственного канала. Магистральные 20 приемопередатчики, подключающие выходные 11 шины коммутаторов 3. 3-1, 3-2 к магистралям резервных каналов, блокируются. При работе системы в нормальном режиме каждый процессорный 1 блок через определенные, заданные интервалы времени осуществляет тестовый самоконтроль, результаты которого записываются в узел 24 сравнения каждого канала блока 12 управления резервированием. Интервал времени самотестирования в каждом канале определяется таймером 25. В момент записи результатов самотестирования в узел 24 сравнения таймер 25 устанавливается в исходное состояние. В случае записи неправильного кода самотестирования на выходе узла 24 сравнения появляется сигнал, поступающий на один из входов элемента ИЛИ

5 26. На второй вход этого элемента ИЛИ 26 поступает сигнал с выхода таймера 25, что свидетельствует о полном выходе из. строя процессорного 1 блока. Сигнал с выхода элемента ИЛИ 26 поступает на соответству0 (ощий вход узла 27 управления реконфигурацией и через элемент ИЛИ 28 на запускающий вход узла 29 прерывания. На . управляющих 30-32 выходах узла 27 управления реконфигурацией формируются сиг5 налы, блокирующие .магистральные

приемопередатчики блока 2 контроля и ком:мутаторов 3, 3-1, 3-2 в канале отказавшего

процессорного 1 блока. Узел 29.прерывания

организует :режим прерывания программы

0 во всех резервируемьгх каналах, .В режиме прерывания программы все исправные про- цессорные блоки читают содержимое регистра 22 управления каждого канала. Информация в. регистр 22 управления всех

5 каналов поступает из узла 27 управления реконфигурацией.и. определяет номер процессорного 1 блока:, который берет на себя .функции в ы шедшего из стрб -я.. В канале не- .исправного процессорного 1 блока магиет0 ральные 20 приемопередатчики коммутаторов 3, 3-1, 3-2, соединенные с каналом процессорного 1 блока, взявшего на.себя функции вышедшего из строя, разг блокируются. Таким образом осуществляет5 ся доступ к ресурсам канала вышедшего из строя процессорного Т блока. :

В случае исправной работы процессорного 1 блока его доступ к ресурсам канала осуществляется через блок 2 контроля и

0 коммутаторы. 3, 3-1, 3-2.

Прохождение информации в блоке 1 контроля ив коммутаторах 3, 3-1, 3-2 осуществляется через магистральные 15, 19, 20 приемопередатчики, которые осуществляют

5 контроль информации по биту четкости. В случае нарушения информации при прохождении через магистральные 15, 29, 20 приемопередатчики - они формируют сигналы ошибка, которые поступают в блок 2 кон0 троля от коммутаторов по цепям 9,10 готовности. В бл:оке 2 контроля сигналы ошибка от магистральных 15, 19. 20 приемопередатчиков поступают на информационные входы регистра 14 состояния и на

5 входы элемента ИЛИ 17. С выхода элемента ИЛИ 17 сигнал ошибки запускает одновиб- ратор 18, импульс которого вкпючает.блок 16 прерывания. Процессорный 1 блок переходит на подпрограмму обработки прерывания, в которой, читая содпр пмо; оопистрл

14 состояния, определяет участок, на котором произошло нарушение в процессе при- емопередэчи информации. Процессорный 1 блок осуществляет повторную приемопере- дачу информации. Если при трех попытках приемопередачи ошибка повторяется, то участок считается вышедшим из строя. 8 этом случае процессорный блок по шине 7 записывает в регистр 23 реконфигурации блока 12 управления резервирования код реконфигурации. В соответствии с этим кодом узел 27 управления реконфигурацией формирует на своих управляющих выходах сигналы, в соответствии с которыми неисправный участок приемопередачи информа- ции. исключается путе.м блокировки магистральных приемопередатчиков, коммутаторов, а доступ к общему ресурсу, осу- ществляется через блоки коммутации резервных каналов. . .

Режйм нарушения прохождения инфор- мациичерез магистральные 15 приемопередатчики блока 2 контроля соответствует режиму выхода из строя процессорного 1 блока.. .

Узел 27 управления реконфигурацией (фиг.5) предназначен для формирования уп- равляющих сигналов в соответствии с информацией, характеризующей исправность отдельных узлов системы. Информация, оп- ределяющая исправность процессорных 1 блоков, входящих в систему, поступает на входы узла 27 управления реконфигурацией по шинам 35-1: 35-N. Информация, определяющая конфигурацию системы, поступает на.входы узла 27 управления реконфигурацией по щинам 36-1: 36-N. Входная информация записывается во входные 39; 40 регистры узла 27 управления реконфигура.- цией и далее поступает на адресные входы постоянных 41. 44 запоминающих у.ст- . ройств Запись информации во входные 39, 40 регистры осуществляется по стробу с вы- хода генератора 42. С выхода постоянных. 41, 44 запоминающих устройств управля-ю- щая информация записывается в выходные 45, 46 регистры и далее поступает в систему на управляющие входы магистральных Т5, 19, 20 приемопередатчиков коммутаторов 3 и блоков 2 контроля. Элемент 43 задержки предназначен- для задержки импульса, стробирующего запись управляющей информации з выходные 45, 46 регистры. Задержка определяется временем переходного процесса ПЗУ. В постоянных 41, 44 запоминающих устройствах прошиты коды управляющей информации.

Зависимость выходных кодов от входных для постоянного 41 запоминающего устромстЕзя дублированной сиогрмы показана в табл. I..

В табл.2 показана аналогичная зависимость для постоянного 44 .запоминающего устройства.

Наличие низкого уровня (О) на входных шинах определяет отказавший бл.ок.

В.таблице 2 X - безразличное состояние. .

Узел 29 прерывания (фиг.6) предназначен для -организации режима прерывания программы одновременно во всех каналах резервированной вычислительной системы. Работа блока полностью соответствует стандартному алгоритму организации режима прерывания программ.

Сигнал с.выхода элемента ИЛИ 28 по- . ступает, по цепи 38 на тактовые входы триггеров .5.1: 51-М-формировэтелей сигналов ТПР. С выходов триггеров 51; 51-N сигналы ТПР поступают в каналы 7 процессорных 1 блоков. Процессорные Т блоки удовлетворяют ТПР, вырабатывая сигналы Ввод и ППР..

В узле 29 прерывания сигналы Ввод всех каналов (активный уровень О) поступают на элемент И. 48.. Сигналом с выхода элемента И..48 открывается регистр 52 адреса вектора прерывания и информация с его выходов поступает на входы магистральных 53;. 53-N приемопередатчиков: Сигналы ПЛ.Р всех каналов поступают в узел 29 прерывания по цепям 55; 55-N на входы установки триггеров 50; 50-М-формироватёлей сигналов ОТВ(СИП) всех каналов, на разрешающие входы магистральных 53; 53-N приемопередатчиков и на входы установки триггеррв-51; 51-N,

Таким образом, по сигналам ППР адрес вектора прерывания через магистральные 53; 53-N приемопередатчики поступает на ..шины, данных каналов 7 процессорных 1 блоков. Триггеры 51; 51-N устанавливаются в.исходное состояние, снимая сигналы ТПР, На входах триггеров 50; 50-N формируются сигналы ), которые через развязывающие 59; 59-N элементы поступают по цепям 54; 54-N в каналы 7 процессорных 1 блоков. Процессорные 1 блоки принимают адрес вектора и снимают сигналы Ввод и ППР. Узел 29 прерывания запрещает передачу адреса вектора прерывания и снимает сигналы ОТВ(СИП). Процессорные 1 блоки переходят на подпрограмму обслуживания прерывания.

Формула изобретения

1. Резервированная вычислительная система, содержащая блок управления резервированием, модуль памяти и группу резервируемых каналов, каждый из которых содержит процессор, модуль локальной памяти, блок контроля, коммутатор обмена и блок ввода-вывода, причем групповой выход управления коммутацией блока управления резервированием подключен к управляющим входам коммутатора обмена всех резервируемых каналов группы, информационные входы-выходы которых подключены к групповому входу-выходу модуля памяти, отличающаяся тем, что, с целью повышения надежности вычисли- тельной системы/в каждый резервируемый канал группы .введены группа коммутаторов, управляющие входы которых подключены к групповому выходу управления коммутацией блока управления резервиро- ванием, к шинам данных каждого резервируемого канала подключены вход-выход данных блока контроля своего резервируемого канала, а шины данных всех резервируемых каналов группы подключены к групповым информационным входам-выходам коммутаторов обмена и коммутаторов группы всех резервируемых каналов, при- чем в каждом резервируемом канале выходы готовности коммутаторов группы и коммутаторов обмена подключены к соответствующим входам группового входа готовности блока контроля своего резервируемого канала, а каждый М-выход группы выходов готовности коммутаторов обмена и коммутаторов группы каждого резервируемого канала подключён к М-вхо- дам групповых входов готовности блоков контроля остальных резервируемых каналов, а группа выходов управления контро- лем блока управления резервированием подключена к входам управления контролем блоков контроля соответствующих резервируемых каналов, в которых информационные входы-выходы блоков контроля и модулей локальной памяти соединены с выходами-входами соответствующих коммутаторов группы, а-информационные входы-выходы процессоров всех резервируемых каналов подключейы к информацией- ным выходам-входам блоков контроля своего резервируемого канала и соответствующим информационным выходам-входам блока управления резервированием.

2. Система по п. 1.отличающаяся тем, что блок управления резервированием содержит группу магистральных приемопередатчиков, узел прерывания, элемент ИЛИ и узел управления реконфигурацией, группа выходов управления контролем и групповой выход управления коммутацией которого являются одноименными выходами блока управления резервированием, информационные входы-выходы магистральных приемопередатчиков группы подключены к соответствующему информационному. входу-выходу блока управления резервированием и узла прерывания, управляющий вход которого подключен к выходу элемента ИЛИ, причем каждый магистральный приемопередатчик группы содержит регистр реконфигурации, селектор адреса и узел сравнения, информационные входы которых подключены к входу информационного входа-выхода магистрального приемопередатчика, .регистр управления, выход которого соединен с выходом информационного входа-выхода магистрального приемопередатчика, э также таймер и магистральный элемент ИЛИ, выход которого подключен к соответствующему управляющему входу узла управления реконфигурацией и соответствующему входу элемента ИЛИ блока управления резервированием, в каждом магистральном приемопередатчике, группы первый/выход селектора адреса подключён к управляющему входу .таймера и блока сравнения, выходы которых подключены к входам магистрального элемента ИЛИ, второй выход селектора адреса подключен к входу синхронизации регистра управления, информационный вход которого соединен с информационным выходом узла управления реконфигурацией, а третий выход селектора адреса подключен, к входу синхронизации регистра реконфигурации, выход которого соединен с соответствующим входом группы информационных входов узла управления реконфигурацией,

Т а б л.и ц а 1

ю «ч- о/ ее о г-

УЭ

оэ

СС

.Сь со

feJ

фиг. 6

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Мажоритарно-резервированная магистральная модульная вычислительная система | 1986 |

|

SU1457643A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ТЕЛЕФОННЫМИ ЛИНИЯМИ СВЯЗИ | 1992 |

|

RU2006927C1 |

| Устройство для управления реконфигурацией резервированного вычислительного комплекса | 1983 |

|

SU1149449A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Многоканальная система обмена для управления электропитанием вычислительного комплекса | 1988 |

|

SU1654830A1 |

| АВТОМАТИЗИРОВАННАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА УПРАВЛЕНИЯ ЗАПРАВКОЙ КРИОГЕННОГО РАЗГОННОГО БЛОКА | 1995 |

|

RU2084011C1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1605242A1 |

| Резервированная вычислительная система | 1990 |

|

SU1755400A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения высоконадежных ЭВМ, комплексов и систем управления объектами и технологическими процессами. С целью повышения надежности системы и повышения достоверности при приеме, обработке и передаче информации, в состав резервированной системы, содержащей блок управления резервированием, модуль памяти и группу резервируемых каналов, каждый из которых содержит процессор, модуль локальной памяти, блок контроля, коммутатор обмена и блок ввода-вывода, введены в каждый резервируемый канал группы коммутаторов с соответствующими связями. 1 з.п.ф, 6 ил. 2 табл.

| Авторское свидетельство СССР Ne 1371302, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР № 1621747, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1993-02-28—Публикация

1989-11-09—Подача