Изобретение относится к вычислительной технике и может быть использовано в высоконадежных системах управления, обмена и обработки данных.

Известна адаптивная система обработки, содержащая память заявок и однотипные процессоры, каждый из которых содержит операционный блок, блок опроса, первый и второй элементы ИЛИ, блок переключения режима, первый, второй и третий элементы И.

Недостатком данного устройства является низкая надежность функционирования.

Наиболее близкой по технической сущности к предлагаемой является адаптивная система обработки данных, содержащая блок памяти заявок, N блоков выбора каналов, N блоков обработки, каждый из которых содержит первый и второй процессоры и блок захвата магистрали, причем выходы разрешения адреса и данных блока памяти

через одноименные шины входной магистрали подключены к входам разрешения, адреса и данных всех блоков выбора каналов, выход разрешения i-го ( ...N) блока выбора каналов подключен к одноименному входу блока захвата магистрали i-ro блока обработки, выход строба блока захвата магистрали i-ro блока обработки подключен к одноименному входу первого процессора i-ro блока обработки и входу строба i-ro блока выбора канала, выходы адреса и данных которого через одноименные шины локальной магистрали подключены к входам адреса и данных первого и второго процессоров i-ro блока обработки. В каждом блоке обработки выход Разрешение первого процессора подключен к одноименному входу второго процессора, выход Запрос второго процессора подключен к входу Запрос первого процессора. Выход Запрос первого процессора через входную шину подключен к входу Запрос блока памяти заявок. Входы-выходы данных, адреса, сигналов выдачи, сигналов приема первого процессора через одноименные шины локальной магистрали подключены к одно- именным входам-выходам второго процессора. Выход Захват блока захвата магистрали подключен к одноименному входу первого процессора, выход Ответ которого подключен к входу Захват второго процессора. Выход Запрос и вход-выход занятости первого и второго процессоров через одноименные шины локальной магистрали подключены к входам Запрос и Занято соответственно блока захвата магистрали. Входы задания режима первого и второго процессоров являются одноименными входами системы, Входы- выходы занятости, приема, выдачи адреса и данных каждого из процессоров всех блоков обработки через одноименные шины системной магистрали соединены между собой. Выходы Запрос каждого из процессоров всех блоков обработки через одноименные шины системной магистрали соединены между собой, выход Запрос каждого из процессоров всех блоков обработки через одноименную шину системной магистрали подключен к входу Захват первого процессора первого блока обработки. В каждом блоке обработки выход Ответ первого процессора подключен к входу Захват второго процессора, выход Ответ второго процессора i-ro блока обработки подключен к входу Запрос первого процессора i-ro блока обработки. Процессор содержит первый и второй блоки буфер- ной памяти, первый и второй приемопередатчики, первый и второй блоки

обмена, дешифратор адреса и блок выполнения операций, входы Разрешение, Запрос, Задание режима и выходы Разрешение и Запрос которого являются соответственно одноименными входами и выходами процессора, выходы Пуск, Адрес, Данные первого блока буферной памяти подключены соответственно к одноименным первым входам блока выполнения

0 операций, первый выход считывания которого подключен к одноименному входу первого блока буферной памяти, выход Подтверждение записи которого подключен к одноименным входам первого блока

5 обмена и первого приемопередатчика и является первым выходом приема процессора. Выход Заполнение первого блока буферной памяти подключен к одноименному входу первого блока обмена и является

0 первым выходом занятости процессора. Первые информационные входы-выходы первого приемопередатчика соединены с одноименными входами первого блока буферной памяти и являются первыми входа5 ми-выходами адреса и данных процессора, Первый вход-выход выдачи процессора является одноименным входом-выходом первого приемопередатчика, вход Захват, выход Ответ и выход Запрос первого

0 блока обмена являются одноименными первыми входами и выходами процессора.

Выход Разрешение захвата первого блока обмена подключен к одноименному первому входу блока выполнения операций,

5 первый выход запроса захвата которого подключен к одноименному входу первого блока обмена. Первый выход Управление включением блока выполнения операций подключен к одноименному входу первого

0 приемопередатчика, информационные входы-выходы, входы-выходы выдачи и приема которого подключены соответственно к одноименным входам-выходам второго приемопередатчика и входам-выходам блока

5 выполнения операций, выход управления направлением передачи которого подключен к одноименным входам первого и второго приемопередатчиков, вход Управление включением которого подключен к одно0 именному второму выходу блока выполнения операций, второй выход запроса захвата которого подключен к одноименному входу второго блока обмена. Выход Разрешение захвата последнего подключен к

5 одноименному второму входу блока выполнения операций, вторые выходы считывания и записи которого подключены к одноименным входаги второго блока буферной памяти, выходы Заполнен, Пуск, Адрес, Данные которого подключены к

одноименным вторым входам блока выполнения операций соответственно. Входы-выходы адреса и данных второго приемопередатчика подключены к одноименным входам второго блока буферной памяти и являются одноименными вторыми входами-выходами процессора. Вход-выход выдачи второго приемопередатчика яв- ляется одноименными вторыми входами-выходами процессора. Вход-выход выдачи второго приемопередатчика является одноименным входом-выходом процессора, Вход-выход приема второго приемопередатчика соединен с одноименным выходом второго блока буферной памяти, входом второго блока обмена, является вторым входом-выходом приема процессора. Вход Захват, выходы Ответ, Запрос и занятости второго блока обмена являются одноименными вторыми входами и выходами процессора.

Недостатком данной системы является низкая надежность функционирования, которая обусловлена следующим. В этой системе каждый резервируемый канал содержит два процессора, которые производят параллельно обработку одной и той же информации. Однако в одном из процессоров может отказать блок выполнения операций, а в другом канале - один из блоков памяти, В результате этого оба процессора окажутся в неработоспособном состоянии, хотя в одном из них есть исправный блок выполнения операций, а в другом - исправный блок памяти.

Таким образом, при появлении отказов разноименных блоков в каждом из двух процессоров блока обработки канал находится в режиме отказа, что существенно снижает надежность функционирования системы в целом.

Цель изобретения - повышение надежности системы.

Сущность изобретения состоит в повышении надежности функционирования системы за счет возможности двусторонней коммутации шин данных и адресных шин с выходов одного канала на входы другого, а также за счет разделения функций контроля и управления системой между блоками контроля каждого из каналов.

В случае отказа устройства обработки данных одного из каналов устройство обработки данных другого канала работает на свой узел оперативной памяти и на узел оперативной памяти канала, в котором отказало устройство обработки данных. Тогда при отказе узла оперативной памяти любого из каналов сохраняется работоспособная структура системы. При отказе одного из

узлов оперативной памяти устройство обработки данных обоих каналов работает с одним узлом оперативной памяти, причем запись информации в этот узел производит

только устройство обработки данных этого канала. Тем самым устройство обработки данных из канала, в котором отказал узел оперативной памяти, находится в горячем резерве и при отказе другого устройства

0 обработки данных сразу же включается в работу, образуя работоспособную конфигурацию устройств обработки данных одного канала, память - другого. По сути дела в системе реализуется адаптация структуры к

5 возникающим отказам. До тех пор, пока оба канала исправны, используется резервирование, при котором любой канал принимает на себя основную работу в случае отказа другого. При этом исправные блоки отказав0 шего канала переключаются на резервирование аналогичных блоков исправного канала,

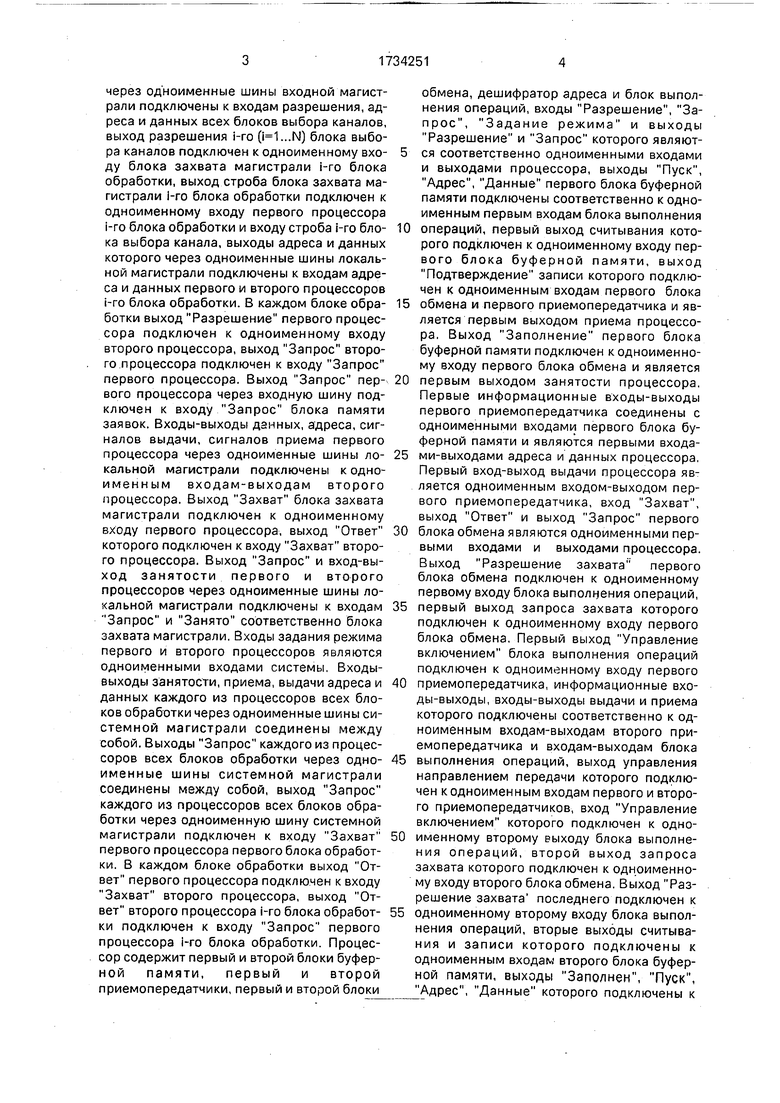

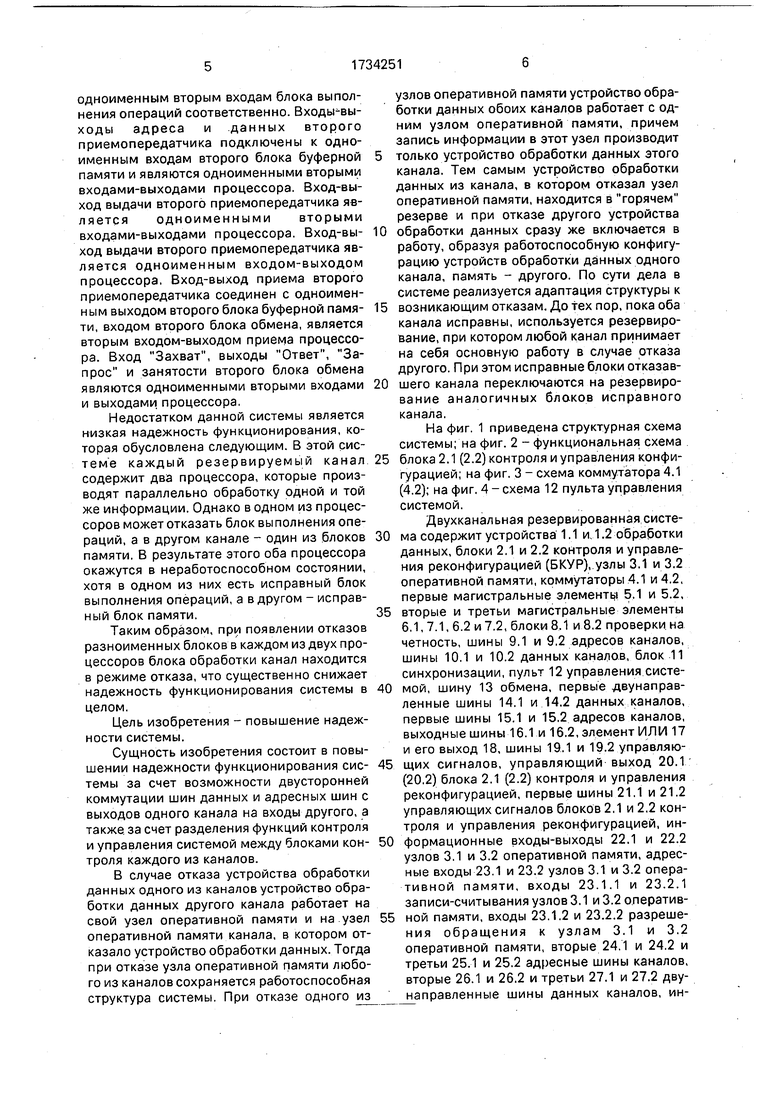

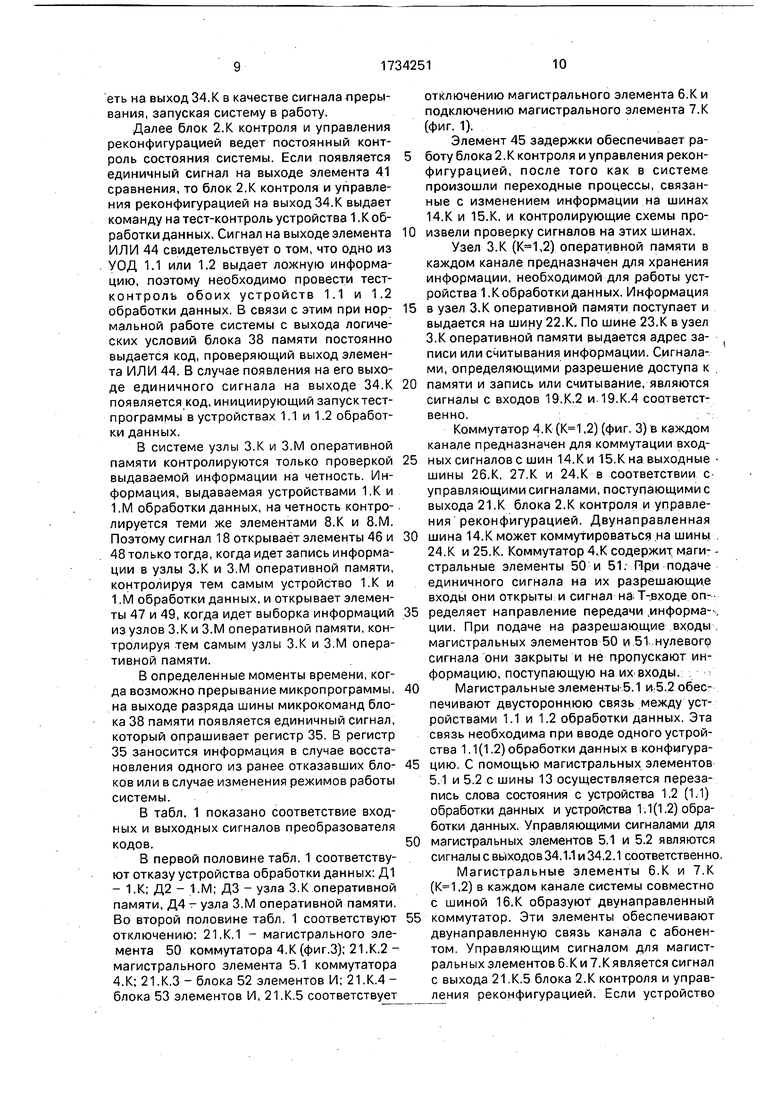

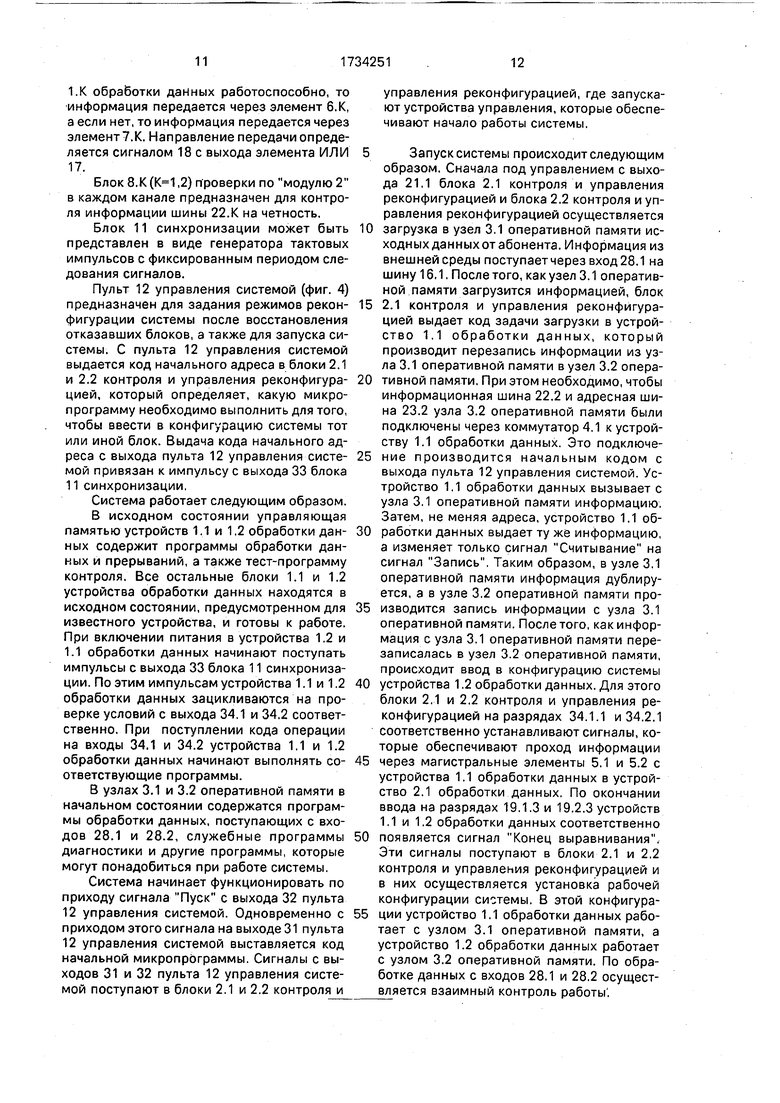

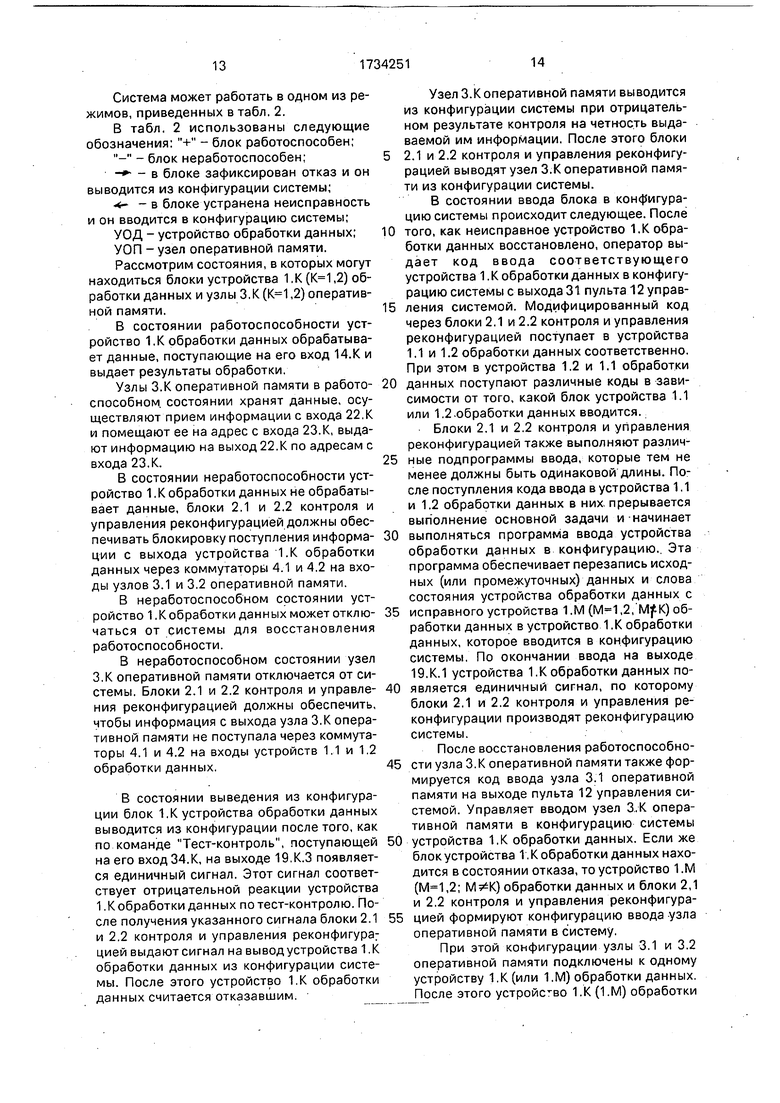

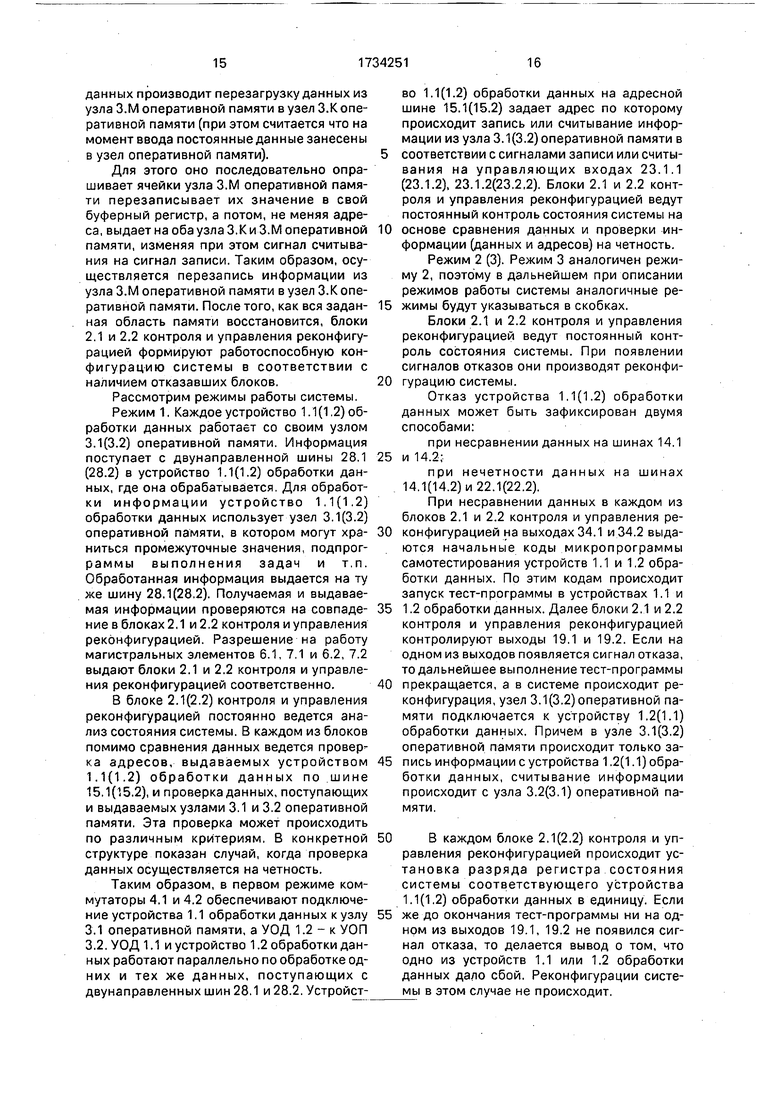

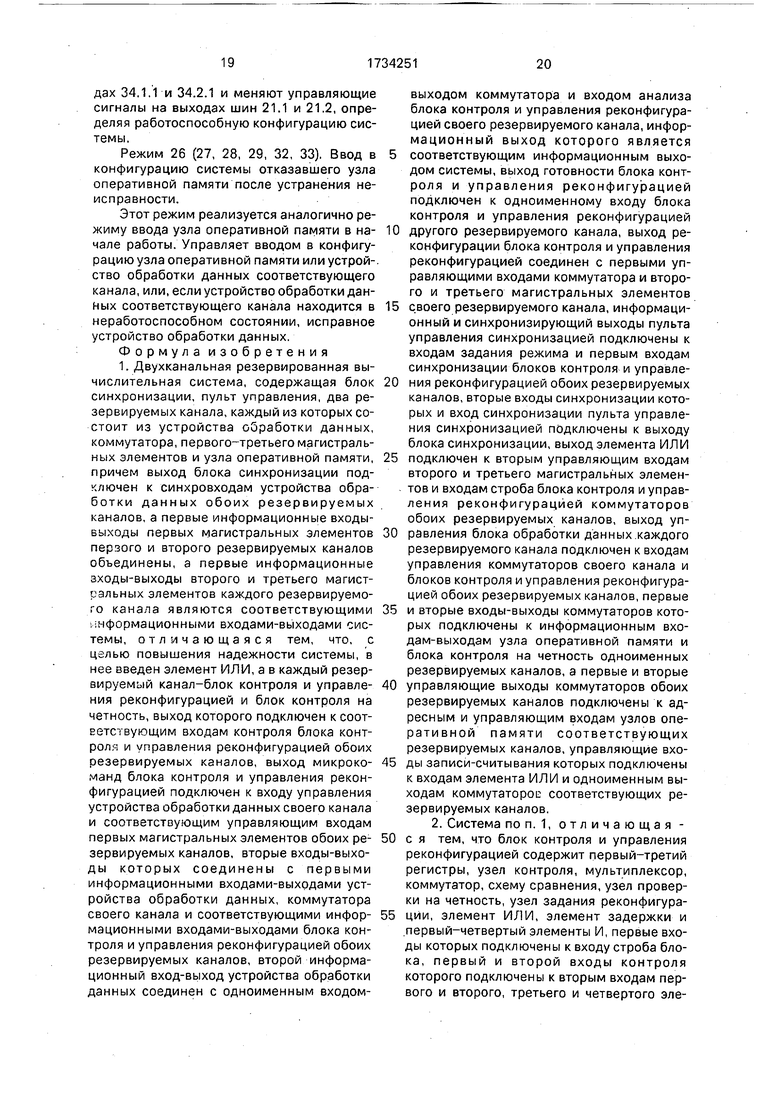

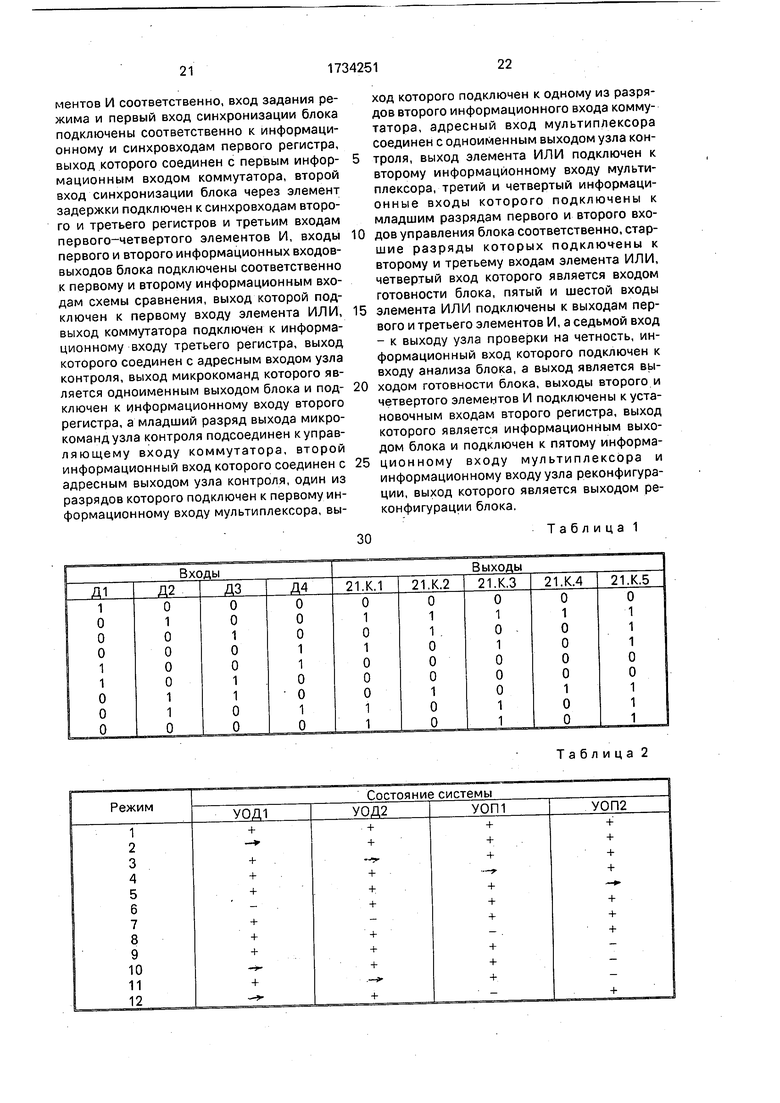

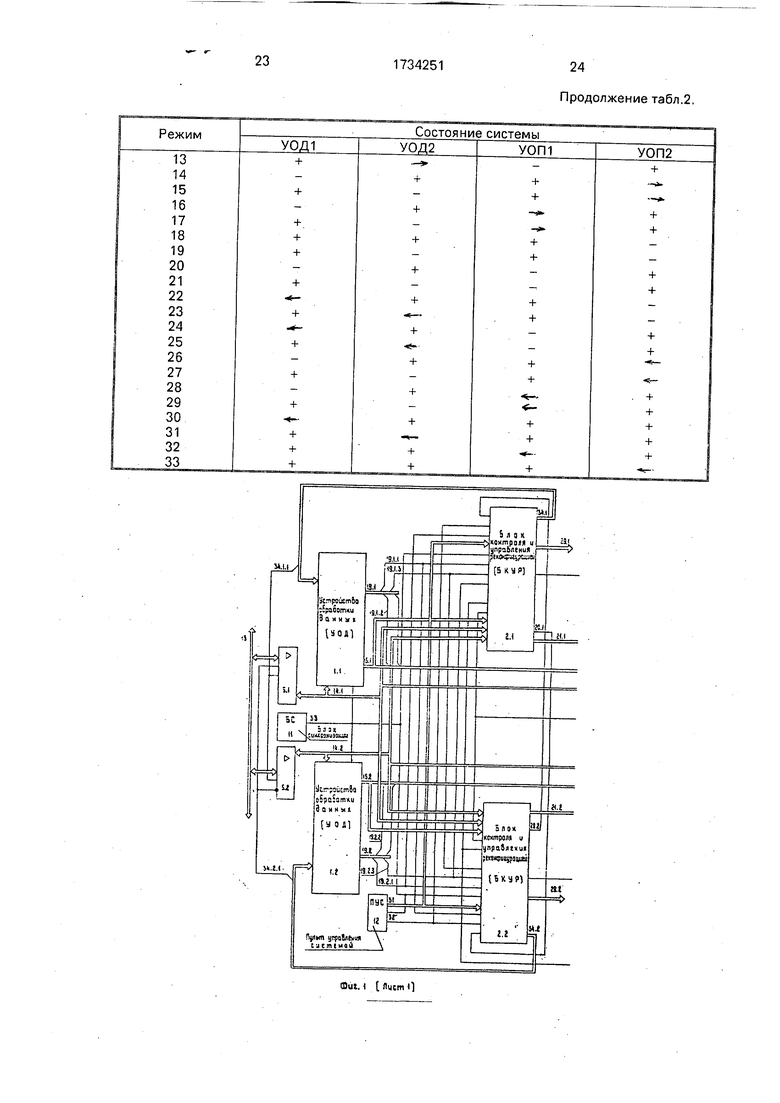

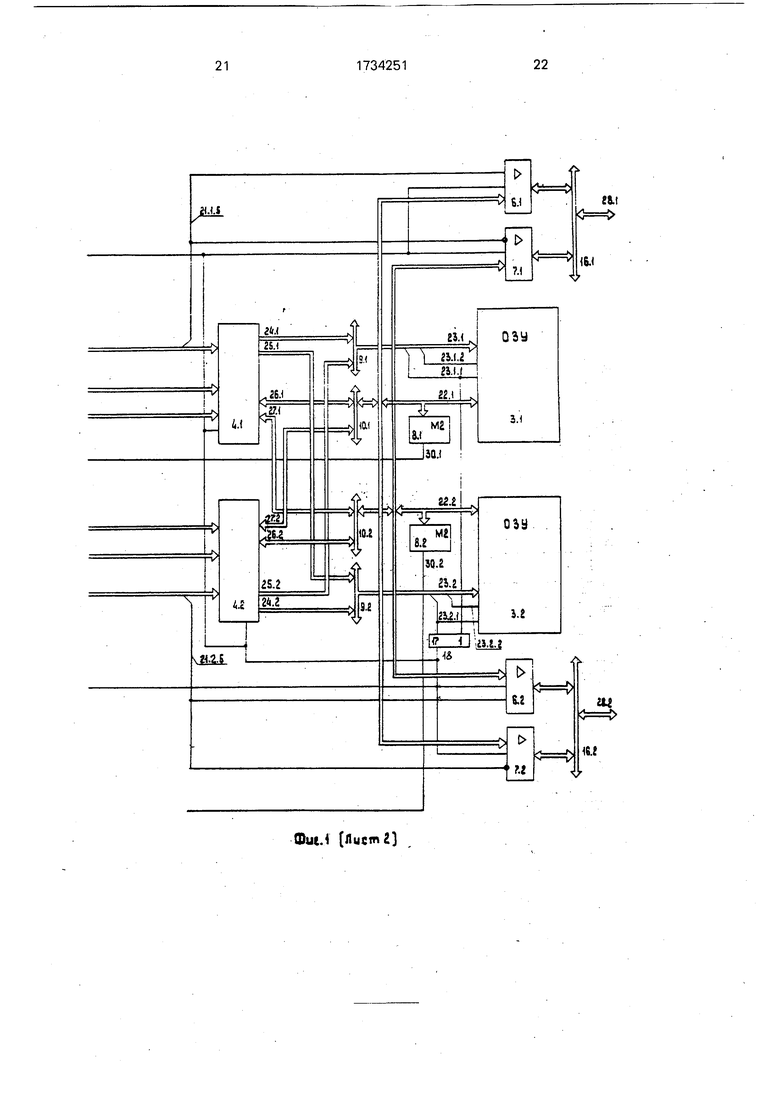

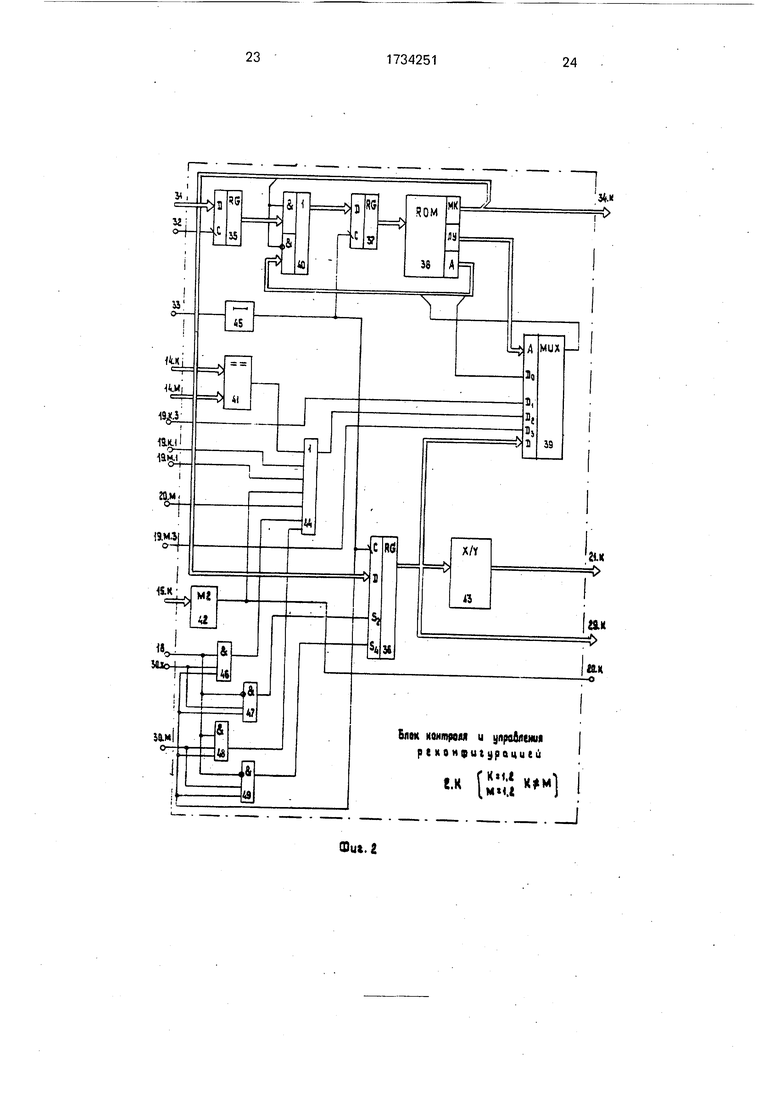

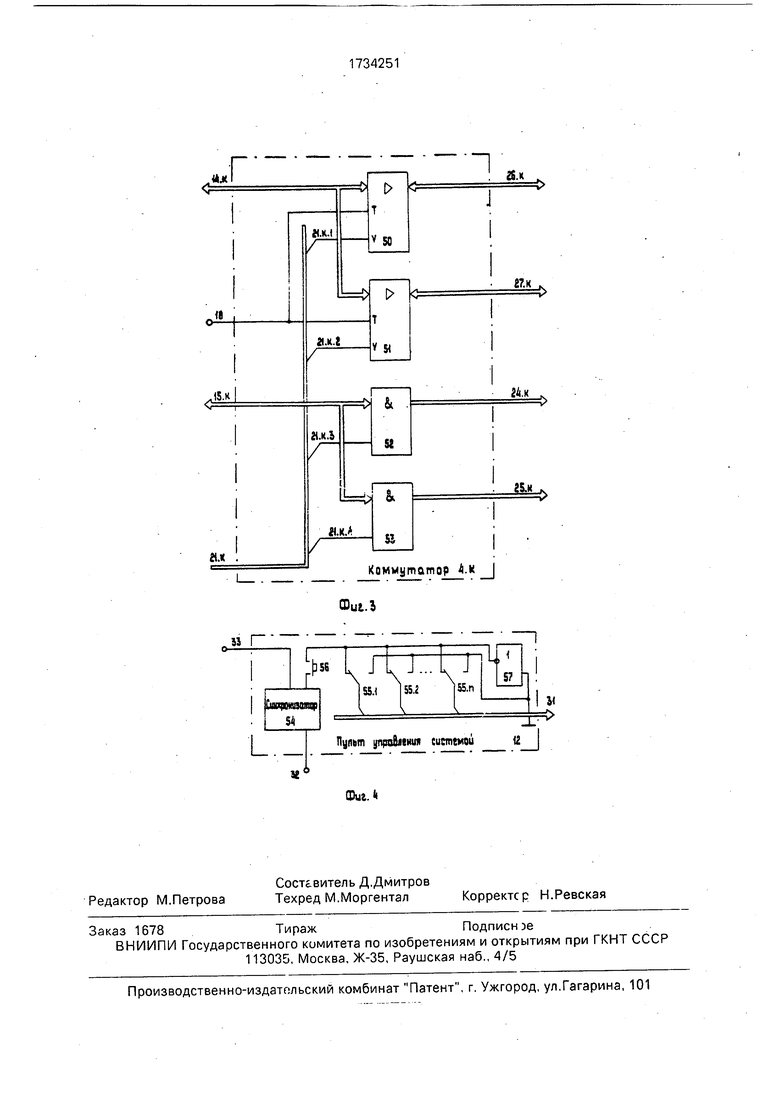

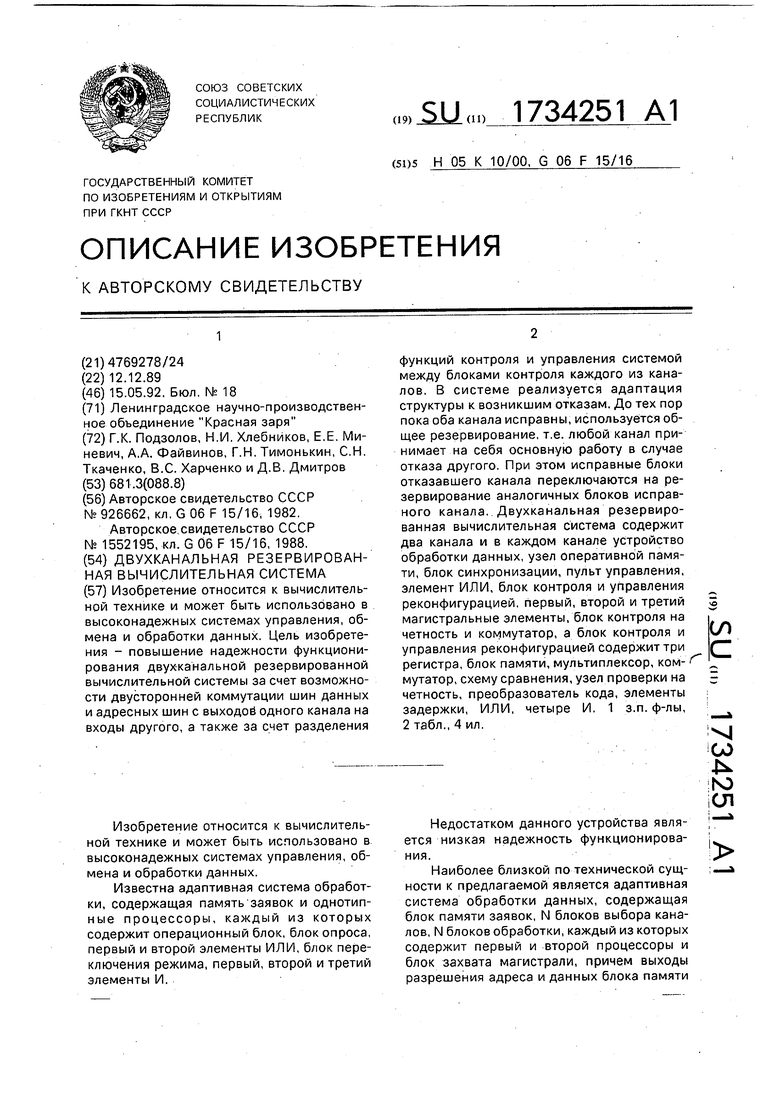

На фиг. 1 приведена структурная схема системы; на фиг. 2 - функциональная схема

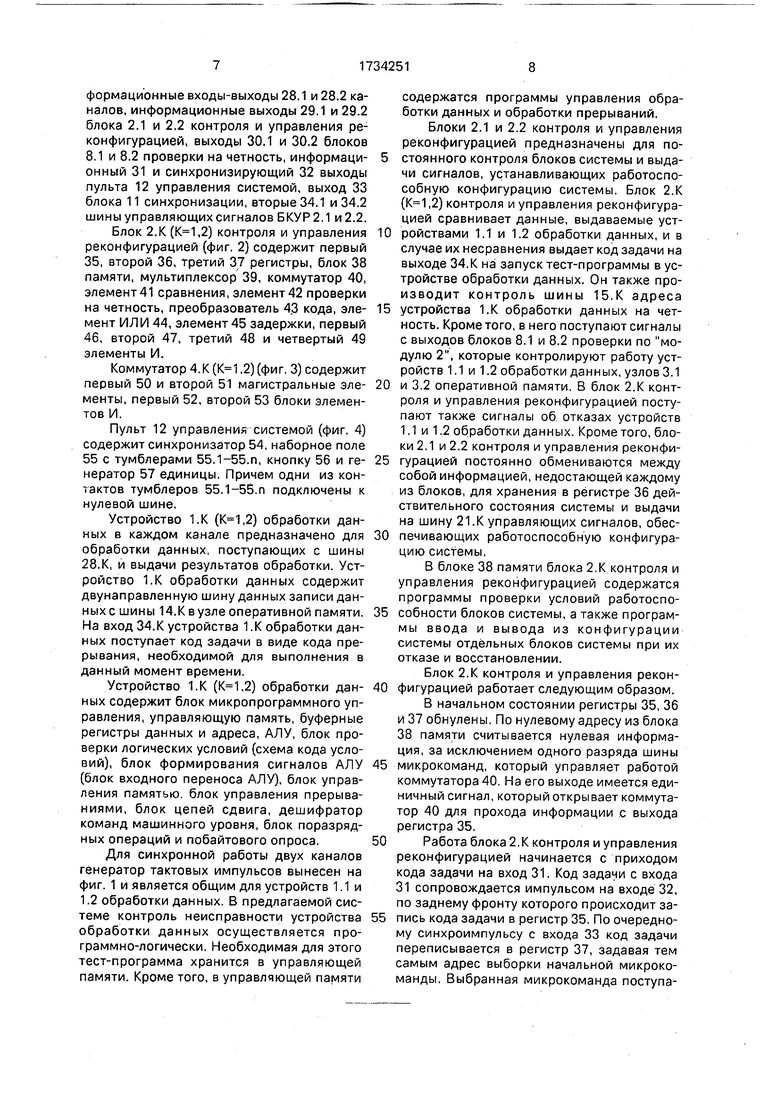

5 блока 2.1 (2.2) контроля и управления конфигурацией; на фиг. 3 - схема коммутатора 4.1 (4.2); на фиг. 4 - схема 12 пульта управления системой.

Двухканальная резервированная систе0 ма содержит устройства 1.1 и 1.2 обработки данных, блоки 2.1 и 2.2 контроля и управления реконфигурацией (БКУР), узлы 3,1 и 3.2 оперативной памяти, коммутаторы 4.1 и 4.2, первые магистральные элементы 5.1 и 5.2,

5 вторые и третьи магистральные элементы 6,1, 7.1, 6.2 и 7.2, блоки 8.1 и 8.2 проверки на четность, шины 9.1 и 9.2 адресов каналов, шины 10.1 и 10.2 данных каналов, блок 11 синхронизации, пульт 12 управления систе0 мой, шину 13 обмена, первые двунаправленные шины 14.1 и 14.2 данных каналов, первые шины 15.1 и 15,2 адресов каналов, выходные шины 16.1 и 16.2, элемент ИЛИ 17 и его выход 18, шины 19.1 и 19.2 управляю5 щих сигналов, управляющий выход 20.1 (20.2) блока 2.1 (2.2) контроля и управления реконфигурацией, первые шины 21.1 и 21.2 управляющих сигналов блоков 2.1 и 2,2 контроля и управления реконфигурацией, ин0 формационные входы-выходы 22.1 и 22.2 узлов 3.1 и 3,2 оперативной памяти, адресные входы 23.1 и 23.2 узлов 3.1 и 3.2 оперативной памяти, входы 23.1.1 и 23.2.1 записи-считывания узлов 3.1 и 3.2 оператив5 ной памяти, входы 23.1.2 и 23.2.2 разрешения обращения к узлам 3.1 и 3.2 оперативной памяти, вторые 24.1 и 24.2 и третьи 25.1 и 25.2 адресные шины каналов, вторые 26.1 и 26.2 и третьи 27.1 и 27.2 двунаправленные шины данных каналов, информационные входы-выходы 28.1 и 28.2 каналов, информационные выходы 29.1 и 29.2 блока 2.1 и 2.2 контроля и управления реконфигурацией, выходы 30.1 и 30,2 блоков

8.1и 8.2 проверки на четность, информационный 31 и синхронизирующий 32 выходы пульта 12 управления системой, выход 33 блока 11 синхронизации, вторые 34.1 и 34.2 шины управляющих сигналов Б КУР 2.1 и 2.2.

Блок 2.К (,2) контроля и управления реконфигурацией (фиг. 2) содержит первый 35, второй 36, третий 37 регистры, блок 38 памяти, мультиплексор 39, коммутатор 40, элемент41 сравнения, элемент42 проверки на четность, преобразователь 43 кода, элемент ИЛ И 44, элемент 45 задержки, первый 46, второй 47, третий 48 и четвертый 49 элементы И.

Коммутатор 4. К (,2) (фиг. 3) содержит первый 50 и второй 51 магистральные элементы, первый 52, второй 53 блоки элементов И.

Пульт 12 управления системой (фиг. 4) содержит синхронизатор 54, наборное поле 55 с тумблерами 55.1-55.П, кнопку 56 и генератор 57 единицы. Причем одни из контактов тумблеров 55.1-55.п подключены к нулевой шине.

Устройство 1.К (,2) обработки данных в каждом канале предназначено для обработки данных, поступающих с шины 28.К, и выдачи результатов обработки. Устройство 1.К обработки данных содержит двунаправленную шину данных записи данных с шины 14.К в узле оперативной памяти. На вход 34.К устройства 1.К обработки данных поступает код задачи в виде кода прерывания, необходимой для выполнения в данный момент времени.

Устройство 1.К (,2) обработки данных содержит блок микропрограммного управления, управляющую память, буферные регистры данных и адреса, АЛУ, блок проверки логических условий (схема кода условий), блок формирования сигналов АЛУ (блок входного переноса АЛУ), блок управления памятью, блок управления прерываниями, блок цепей сдвига, дешифратор команд машинного уровня, блок поразрядных операций и побайтового опроса.

Для синхронной работы двух каналов генератор тактовых импульсов вынесен на фиг. 1 и является общим для устройств 1.1 и

1.2обработки данных. В предлагаемой системе контроль неисправности устройства обработки данных осуществляется программно-логически. Необходимая для этого тест-программа хранится в управляющей памяти. Кроме того, в управляющей памяти

содержатся программы управления обработки данных и обработки прерываний.

Блоки 2.1 и 2.2 контроля и управления реконфигурацией предназначены для постоянного контроля блоков системы и выдачи сигналов, устанавливающих работоспособную конфигурацию системы. Блок 2.К (,2) контроля и управления реконфигурацией сравнивает данные, выдаваемые устройствами 1.1 и 1.2 обработки данных, и в случае их несравнения выдает код задачи на выходе 34,К на запуск тест-программы в устройстве обработки данных. Он также производит контроль шины 15.К адреса

устройства 1.К обработки данных на четность. Кроме того, в него поступают сигналы с выходов блоков 8.1 и 8.2 проверки по модулю 2, которые контролируют работу устройств 1.1 и 1.2 обработки данных, узлов 3.1

и 3.2 оперативной памяти. В блок 2.К контроля и управления реконфигурацией поступают также сигналы об отказах устройств 1.1 и 1.2 обработки данных. Кроме того, блоки 2.1 и 2.2 контроля и управления реконфигурацией постоянно обмениваются между собой информацией, недостающей каждому из блоков, для хранения в регистре 36 действительного состояния системы и выдачи на шину 21.К управляющих сигналов, обеспечивающих работоспособную конфигурацию системы,

В блоке 38 памяти блока 2,К контроля и управления реконфигурацией содержатся программы проверки условий работоспособности блоков системы, а также программы ввода и вывода из конфигурации системы отдельных блоков системы при их отказе и восстановлении.

Блок 2.К контроля и управления реконфигурацией работает следующим образом. В начальном состоянии регистры 35, 36 и 37 обнулены. По нулевому адресу из блока 38 памяти считывается нулевая информация, за исключением одного разряда шины

микрокоманд, который управляет работой коммутатора 40. На его выходе имеется единичный сигнал, который открывает коммутатор 40 для прохода информации с выхода регистра 35.

Работа блока 2.К контроля и управления реконфигурацией начинается с приходом кода задачи на вход 31. Код задачи с входа 31 сопровождается импульсом на входе 32, по заднему фронту которого происходит запись кода задачи в регистр 35. По очередному синхроимпульсу с входа 33 код задачи переписывается в регистр 37, задавая тем самым адрес выборки начальной микрокоманды. Выбранная микрокоманда поступаеть на выход 34.К в качестве сигнала прерывания, запуская систему в работу.

Далее блок 2.К контроля и управления реконфигурацией ведет постоянный контроль состояния системы. Если появляется единичный сигнал на выходе элемента 41 сравнения, то блок 2.К контроля и управления реконфигурацией на выход 34.К выдает команду на тест-контроль устройства Т.Коб- работки данных. Сигнал на выходе элемента ИЛИ 44 свидетельствует о том, что одно из УОД 1.1 или 1.2 выдает ложную информацию, поэтому необходимо провести тест- контролъ обоих устройств 1.1 и 1.2 обработки данных. В связи с этим при нормальной работе системы с выхода логических условий блока 38 памяти постоянно выдается код, проверяющий выход элемента ИЛИ 44. В случае появления на его выходе единичного сигнала на выходе 34.К появляется код, инициирующий запусктест- программы в устройствах 1.1 и 1.2 обработки данных.

В системе узлы З.К и З.М оперативной памяти контролируются только проверкой выдаваемой информации на четность. Информация, выдаваемая устройствами 1.К и 1.М обработки данных, на четность контролируется теми же элементами 8.К и 8.М. Поэтому сигнал 18 открывает элементы 46 и 48 только тогда, когда идет запись информации в узлы З.К и З.М оперативной памяти, контролируя тем самым устройство 1.К и 1 ,М обработки данных, и открывает элементы 47 и 49, когда идет выборка информации из узлов З.К и З.М оперативной памяти, контролируя тем самым узлы З.К и З.М оперативной памяти.

В определенные моменты времени, когда возможно прерывание микропрограммы, на выходе разряда шины микрокоманд блока 38 памяти появляется единичный сигнал, который опрашивает регистр 35. В регистр 35 заносится информация в случае восстановления одного из ранее отказавших блоков или в случае изменения режимов работы системы.

В табл. 1 показано соответствие входных и выходных сигналов преобразователя кодов.

В первой половине табл. 1 соответствуют отказу устройства обработки данных: Д1 - 1.К; Д2 - 1.М; ДЗ - узла З.К оперативной памяти, Д4 - узла З.М оперативной памяти. Во второй половине табл. 1 соответствуют отключению: 21.К.1 - магистрального элемента 50 коммутатора 4,К(фиг.З); 21.К.2- магистрального элемента 5.1 коммутатора 4.К; 21.К.З - блока 52 элементов И; 21.К.4 - блока 53 элементов И, 21.К.5 соответствует

отключению магистрального элемента 6.К и подключению магистрального элемента 7.К (фиг. 1).

Элемент 45 задержки обеспечивает работу блока 2.К контроля и управления реконфигурацией, после того как в системе произошли переходные процессы, связанные с изменением информации на шинах 14.К и 15.К, и контролирующие схемы про0 извели проверку сигналов на этих шинах.

Узел З.К (,2) оперативной памяти в каждом канале предназначен для хранения информации, необходимой для работы устройства 1, К обработки данных. Информация

5 в узел З.К оперативной памяти поступает и выдается на шину 22.К. По шине 23.К в узел З.К оперативной памяти выдается адрес записи или считывания информации. Сигналами, определяющими разрешение доступа к

0 памяти и запись или считывание, являются сигналы с входов 19.К.2 и 19.К.4 соответственно.

Коммутатор 4.К (,2) (фиг. 3) в каждом канале предназначен для коммутации вход5 ных сигналов с шин 14.К и 15.К на выходные шины 26.К, 27.К и 24.К в соответствии с управляющими сигналами, поступающими с выхода 21.К блока 2.К контроля и управления реконфигурацией. Двунаправленная

0 шина 14.К может коммутироваться на шины 24.К и 25.К. Коммутатор 4.К содержит маги- - стральные элементы 50 и 51: При подаче единичного сигнала на их разрешающие входы они открыты и сигнал на Т-входе оп5 ределяет направление передачи ,информа- ции. При подаче на разрешающие входы магистральных элементов 50 и 51 нулевого сигнала они закрыты и не пропускают информацию, поступающую на их входы.

0 Магистральные элементы 5.1 и 5.2 обеспечивают двустороннюю связь между устройствами 1.1 и 1.2 обработки данных. Эта связь необходима при вводе одного устройства 1.1 (1.2) обработки данных в конфигура5 цию. С помощью магистральных элементов 5.1 и 5.2 с шины 13 осуществляется перезапись слова состояния с устройства 1.2 (1,1) обработки данных и устройства 1.1(1.2) обработки данных. Управляющими сигналами для

0 магистральных элементов 5.1 и 5.2 являются сигналы с выходов34.1.1и34.2.1 соответственно.

Магистральные элементы 6.К и 7.К (,2) в каждом канале системы совместно с шиной 16.К образуют двунаправленный

5 коммутатор. Эти элементы обеспечивают двунаправленную связь канала с абонентом. Управляющим сигналом для магистральных элементов 6.К и 7.К является сигнал с выхода 21.К.5 блока 2.К контроля и управления реконфигурацией. Если устройство

1.К обработки данных работоспособно, то информация передается через элемент 6.К, а если нет, то информация передается через элемент 7.К. Направление передачи определяется сигналом 18с выхода элемента ИЛИ 17.

Блок 8.К (,2) проверки по модулю 2 в каждом канале предназначен для контроля информации шины 22.К на четность.

Блок 11 синхронизации может быть представлен в виде генератора тактовых импульсов с фиксированным периодом следования сигналов.

Пульт 12 управления системой (фиг. 4) предназначен для задания режимов рекон- фигурации системы после восстановления отказавших блоков, а также для запуска системы. С пульта 12 управления системой выдается код начального адреса в блоки 2.1 и 2.2 контроля и управления реконфигура- цией, который определяет, какую микропрограмму необходимо выполнить для того, чтобы ввести в конфигурацию системы тот или иной блок. Выдача кода начального адреса с выхода пульта 12 управления систе- мой привязан к импульсу с выхода 33 блока

11синхронизации,

Система работает следующим образом.

В исходном состоянии управляющая памятью устройств 1.1 и 1,2 обработки дан- ных содержит программы обработки данных и прерываний, а также тест-программу контроля. Все остальные блоки 1.1 и 1.2 устройства обработки данных находятся в исходном состоянии, предусмотренном для известного устройства, и готовы к работе. При включении питания в устройства 1.2 и 1.1 обработки данных начинают поступать импульсы с выхода 33 блока 11 синхронизации. По этим импульсам устройства 1.1 и 1.2 обработки данных зацикливаются на проверке условий с выхода 34.1 и 34.2 соответственно. При поступлении кода операции на входы 34.1 и 34.2 устройства 1.1 и 1.2 обработки данных начинают выполнять со- ответствующие программы.

В узлах 3.1 и 3.2 оперативной памяти в начальном состоянии содержатся программы обработки данных, поступающих с входов 28.1 и 28.2, служебные программы диагностики и другие программы, которые могут понадобиться при работе системы.

Система начинает функционировать по приходу сигнала Пуск с выхода 32 пульта

12управления системой. Одновременно с приходом этого сигнала на выходе 31 пульта

12 управления системой выставляется код начальной микропрограммы. Сигналы с выходов 31 и 32 пульта 12 управления системой поступают в блоки 2.1 и 2.2 контроля и

управления реконфигурацией, где запускают устройства управления, которые обеспечивают начало работы системы.

Запуск системы происходит следующим образом. Сначала под управлением с выхода 21.1 блока 2.1 контроля и управления реконфигурацией и блока 2.2 контроля и управления реконфигурацией осуществляется загрузка в узел 3.1 оперативной памяти исходных данных от абонента. Информация из внешней среды поступает через вход 28.1 на шину 16,1. После того, как узел 3.1 оперативной памяти загрузится информацией, блок 2.1 контроля и управления реконфигурацией выдает код задачи загрузки в устройство 1.1 обработки данных, который производит перезапись информации из узла 3.1 оперативной памяти в узел 3.2 оперативной памяти. При этом необходимо, чтобы информационная шина 22.2 и адресная шина 23.2 узла 3.2 оперативной памяти были подключены через коммутатор 4.1 к устройству 1.1 обработки данных. Это подключение производится начальным кодом с выхода пульта 12 управления системой. Устройство 1.1 обработки данных вызывает с узла 3.1 оперативной памяти информацию. Затем, не меняя адреса, устройство 1.1 обработки данных выдает ту же информацию, а изменяет только сигнал Считывание на сигнал Запись. Таким образом, в узле 3.1 оперативной памяти информация дублируется, а в узле 3.2 оперативной памяти производится запись информации с узла 3.1 оперативной памяти. После того, как информация с узла 3.1 оперативной памяти перезаписалась в узел 3.2 оперативной памяти, происходит ввод в конфигурацию системы устройства 1.2 обработки данных. Для этого блоки 2.1 и 2.2 контроля и управления реконфигурацией на разрядах 34.1.1 и 34.2.1 соответственно устанавливают сигналы, которые обеспечивают проход информации через магистральные элементы 5.1 и 5.2 с устройства 1.1 обработки данных в устройство 2.1 обработки данных. По окончании ввода на разрядах 19.1.3 и 19.2.3 устройств 1.1 и 1.2 обработки данных соответственно появляется сигнал Конец выравнивания. Эти сигналы поступают в блоки 2.1 и 2,2 контроля и управления реконфигурацией и в них осуществляется установка рабочей конфигурации системы. В этой конфигурации устройство 1.1 обработки данных работает с узлом 3.1 оперативной памяти, а устройство 1.2 обработки данных работает с узлом 3.2 оперативной памяти. По обработке данных с входов 28.1 и 28.2 осуществляется взаимный контроль работы .

Система может работать в одном из режимов, приведенных в табл. 2.

В табл. 2 использованы следующие обозначения: + - блок работоспособен;

- - блок неработоспособен;

- в блоке зафиксирован отказ и он выводится из конфигурации системы;

4- - в блоке устранена неисправность и он вводится в конфигурацию системы;

УОД - устройство обработки данных;

УОП - узел оперативной памяти.

Рассмотрим состояния, в которых могут находиться блоки устройства 1 .К (,2) обработки данных и узлы 3,К (,2) оперативной памяти.

В состоянии работоспособности устройство 1.К обработки данных обрабатывает данные, поступающие на его вход 14.К и выдает результаты обработки.

Узлы З.К оперативной памяти в работоспособном, состоянии хранят данные, осуществляют прием информации с входа 22.К и помещают ее на адрес с входа 23.К, выдают информацию на выход 22.К по адресам с входа 23.К.

В состоянии неработоспособности устройство 1.К обработки данных не обрабатывает данные, блоки 2.1 и 2.2 контроля и управления реконфигурацией должны обеспечивать блокировку поступления информации с выхода устройства 1.К обработки данных через коммутаторы 4.1 и 4.2 на входы узлов 3.1 и 3.2 оперативной памяти.

В неработоспособном состоянии устройство 1 .Кобработки данных может отключаться от системы для восстановления работоспособности.

В неработоспособном состоянии узел З.К оперативной памяти отключается от системы. Блоки 2.1 и 2.2 контроля и управления реконфигурацией должны обеспечить, чтобы информация с выхода узла З.К оперативной памяти не поступала через коммутаторы 4.1 и 4.2 на входы устройств 1.1 и 1.2 обработки данных.

В состоянии выведения из конфигурации блок 1.К устройства обработки данных выводится из конфигурации после того, как по команде Тест-контроль, поступающей на его вход 34.К, на выходе 19.К.З появляется единичный сигнал. Этот сигнал соответствует отрицательной реакции устройства 1.Кобработки данных по тест-контролю. После получения указанного сигнала блоки 2.1 и 2.2 контроля и управления реконфигура; цией выдают сигнал на вывод устройства 1,К обработки данных из конфигурации системы. После этого устройство 1.К обработки данных считается отказавшим.

Узел З.К оперативной памяти выводится из конфигурации системы при отрицательном результате контроля на четность выдаваемой им информации, После этого блоки

2.1 и 2.2 контроля и управления реконфигурацией выводят узел З.К оперативной памяти из конфигурации системы.

В состоянии ввода блока в конфигурацию системы происходит следующее. После

0 того, как неисправное устройство 1.К обработки данных восстановлено, оператор выдает код ввода соответствующего устройства 1 .К обработки данных в конфигурацию системы с выхода 31 пульта12управ5 ления системой. Модифицированный код через блоки 2.1 и 2.2 контроля и управления реконфигурацией поступает в устройства 1.1 и 1.2 обработки данных соответственно. При этом в устройства 1.2 и 1.1 обработки

0 данных поступают различные коды в зависимости от того, какой блок устройства 1.1 или 1.2.обработки данных вводится.

Блоки 2.1 и 2.2 контроля и управления реконфигурацией также выполняют различ5 ные подпрограммы ввода, которые тем не менее должны быть одинаковой длины. После поступления кода ввода в устройства 1.1 и 1.2 обработки данных в них прерывается выполнение основной задачи и-начинает

0 выполняться программа ввода устройства обработки данных в конфигурацию. Эта программа обеспечивает перезапись исходных (или промежуточных) данных и слова состояния устройства обработки данных с

5 исправного устройства 1 .М (,2,) обработки данных в устройство 1 .К обработки данных, которое вводится в конфигурацию системы. По окончании ввода на выходе 19.К.1 устройства 1.К обработки данных по0 является единичный сигнал, по которому блоки 2,1 и 2.2 контроля и управления реконфигурации производят реконфигурацию системы.

После восстановления работоспособно5 сти узла З.К оперативной памяти также формируется код ввода узла 3.1 оперативной памяти на выходе пульта 12 управления системой. Управляет вводом узел З.К оперативной памяти в конфигурацию системы

0 устройства 1.К обработки данных. Если же блок устройства 1. К обработки дан ных находится в состоянии отказа, то устройство 1 .М (,2; ) обработки данных и блоки 2,1 и 2.2 контроля и управления реконфигура5 цией формируют конфигурацию ввода узла оперативной памяти в систему.

При этой конфигурации узлы 3.1 и 3.2 оперативной памяти подключены к одному устройству 1,К(или 1.М) обработки данных. После этого устройство 1.К (1.М) обработки

данных производит перезагрузку данных из узла З.М оперативной памяти в узел 3.К оперативной памяти (при этом считается что на момент ввода постоянные данные занесены в узел оперативной памяти).

Для этого оно последовательно опрашивает ячейки узла З.М оперативной памяти перезаписывает их значение в свой буферный регистр, а потом, не меняя адреса, выдает на оба узла 3.К и З.М оперативной памяти, изменяя при этом сигнал считывания на сигнал записи. Таким образом, осуществляется перезапись информации из узла З.М оперативной памяти в узел 3.К оперативной памяти. После того, как вся заданная область памяти восстановится, блоки 2.1 и 2.2 контроля и управления реконфигурацией формируют работоспособную конфигурацию системы в соответствии с наличием отказавших блоков.

Рассмотрим режимы работы системы.

Режим 1, Каждое устройство 1.1 (1.2) обработки данных работает со своим узлом 3.1(3.2) оперативной памяти. Информация поступает с двунаправленной шины 28.1 (28.2) в устройство 1.1(1.2) обработки данных, где она обрабатывается. Для обработки информации устройство 1.1(1.2) обработки данных использует узел 3.1(3.2) оперативной памяти, в котором могут храниться промежуточные значения, подпрограммы выполнения задач и т.п. Обработанная информация выдается на ту же шину 28.1(28.2). Получаемая и выдаваемая информации проверяются на совпадение в блоках 2.1 и 2.2 контроля и управления реконфигурацией. Разрешение на работу магистральных элементов 6.1, 7.1 и 6.2, 7.2 выдают блоки 2.1 и 2,2 контроля и управления реконфигурацией соответственно.

В блоке 2.1(2.2) контроля и управления реконфигурацией постоянно ведется анализ состояния системы. В каждом из блоков помимо сравнения данных ведется проверка адресов, выдаваемых устройством 1.1(1.2) обработки данных по шине 15.1(15.2), и проверка данных, поступающих и выдаваемых узлами 3.1 и 3.2 оперативной памяти, Эта проверка может происходить по различным критериям. В конкретной структуре показан случай, когда проверка данных осуществляется на четность.

Таким образом, в первом режиме коммутаторы 4.1 и 4.2 обеспечивают подключение устройства 1.1 обработки данных к узлу 3.1 оперативной памяти, а УОД 1.2 - к УОП 3.2. УОД 1.1 и устройство 1.2 обработки данных работают параллельно по обработке одних и тех же данных, поступающих с двунаправленных шин 28.1 и 28.2. Устройство 1.1(1.2) обработки данных на адресной шине 15.1(15.2) задает адрес по которому происходит запись или считывание информации из узла 3.1(3.2) оперативной памяти в

соответствии с сигналами записи или считы- вания на управляющих входах 23.1.1 (23.1.2), 23.1.2(23.2,2). Блоки 2.1 и 2.2 контроля и управления реконфигурацией ведут постоянный контроль состояния системы на

основе сравнения данных и проверки информации (данных и адресов) на четность.

Режим 2 (3). Режим 3 аналогичен режиму 2, поэтому в дальнейшем при описании режимов работы системы аналогичные режимы будут указываться в скобках.

Блоки 2.1 и 2.2 контроля и управления реконфигурацией ведут постоянный контроль состояния системы. При появлении сигналов отказов они производят реконфигурацию системы.

Отказ устройства 1.1(1.2) обработки данных может быть зафиксирован двумя способами:

при несравнении данных на шинах 14.1

и 14.2;

при нечетности данных на шинах 14.1(14.2) и 22.1(22.2).

При несравнении данных в каждом из блоков 2.1 и 2.2 контроля и управления реконфигурацией на выходах 34.1 и 34.2 выдаются начальные коды микропрограммы самотестирования устройств 1.1 и 1,2 обработки данных. По этим кодам происходит запуск тест-программы в устройствах 1.1 и

1.2 обработки данных. Далее блоки 2,1 и 2.2 контроля и управления реконфигурацией контролируют выходы 19.1 и 19.2. Если на одном из выходов появляется сигнал отказа, то дальнейшее выполнение тест-программы

прекращается, а в системе происходит реконфигурация, узел 3.1(3.2) оперативной памяти подключается к устройству 1.2(1.1) обработки данных. Причем в узле 3.1(3.2) оперативной памяти происходит только запись информации с устройства 1.2(1. обработки данных, считывание информации происходит с узла 3.2(3.1) оперативной памяти.

В каждом блоке 2,1(2.2) контроля и управления реконфигурацией происходит установка разряда регистра состояния системы соответствующего устройства 1.1(1.2) обработки данных в единицу. Если

же до окончания тест-программы ни на одном из выходов 19.1, 19.2 не появился сигнал отказа, то делается вывод о том, что одно из устройств 1.1 или 1.2 обработки данных дало сбой. Реконфигурации системы в этом случае не происходит.

При нечетности аналогично описанному происходит запуск тест-программы, чтобы определить сбой или отказ произошел в устройстве обработки данных.

Режим 4 (5). Проверка узла 3.1(3.2) one- ративной памяти осуществляется на четность блоком 2.1(2,2) контроля и управления реконфигурацией в моменты времени, когда происходит считывание информации, о чем свидетельствует единичный сигнал на входе 19.1.2(19.2.2) блока 2.1(2.2) контроля и управления реконфигурацией. При появлении сигнала нечетности, который соответствует отказу узла 3.1(3.2) оперативной памяти, в блоке 2.1(2.2) контроля и управления рекон- фигурацией формируются соответствующие коды запросов на прерывание на выходах 34.1 и 34.2 соответственно. Эти коды поступают в устройства 1.1 и 1.2 обработки данных, инициируя в них начало обработки прерывания. Одновременно с этим блок 2.1(2.2) контроля и управления реконфигурацией подключает устройство 1.1(1.2) обработки данных к узлу 3.2(3,1) оперативной памяти только для считывания информации. Запись информации в узел 3.2(3.1) оперативной памяти производит устройство 1.2(1.1) обработки данных.

Режим 6 (7). В этих режимах система функционирует без одного устройства 1.1(1.2), 1.2(1.1) обработки данных и узел 3.2(3.1) оперативной памяти работает с ним совместно, а в узел 3.1(3.2) оперативной памяти производится запись текущей информации из устройства 1.2(1.1) обработки данных. Это позволяет в случае отказа узла 3.1(3.2) оперативной памяти перекоммутировать устройство 1.2(1.1) обработки данных на работу с узлом 3.1(3.2) оперативной памяти, сохраняя тем самым работоспособ- ную структуру системы.

Режим 8 (9). В этих режимах система функционирует без одного узла 3.1(3.2) оперативной памяти, устройство 1.2(1.1) обработки данных в этом случае только считывает информацию с узла 3.2(3.1) оперативной памяти.

Режим 10(11,12,13). В системе зафиксирован отказ одного из устройств 1.1 (или 1.2) обработки данных в то время, когда узел 3,1 или 3.2 оперативной памяти находится в неработоспособном состоянии. Происходит вывод неисправного устройства 1.1(1.2) обработки данных из конфигурации системы, так как это описано в режиме 2 (3).

Режим 14 (15, 16, 17). Фиксируется отказ одного из узлов 3.1 (или 3.2) оперативной памяти тогда, когда в системе в отказавшем состоянии находится одно из устройств 1.1 (1.2) обработки данных. В этих

режимах выводится из конфигурации системы отказавший узел 3.1(3.2) оперативной памяти. В исправное устройство 1.2(1.обработки данных выдается код, по которому прерывается и начинается решение задачи с полученных последних промежуточных результатов.

Режим 18(19, 20, 21), В системе имеется одно неработоспособное устройство 1.1(1.2) обработки данных и один работоспособный узел 3.1(3.2) оперативной памяти. С помощью блоков 2.1 и 2.2 контроля и управления реконфигурацией устанавливается работоспособная конфигурация системы, при которой исправное устройство обработки данных работает с исправным узлом оперативной памяти.

Режим 22 (23, 24, 25, 30, 31). Ввод в конфигурацию системы отказавшего устройства 1.1 (1.2) обработки данных после устранения неисправности.

С пульта 12 управления системой выдается адрес команды восстановления соответствующего устройства 1.1(1.2) обработки данных. Этот адрес поступает в блоки 2.1 и 2.2 контроля и управления реконфигурацией, которые в свою очередь формируют начальные адреса режима ввода устройств 1.1 и 1.2 обработки данных соответственно.

Блок 2.1 или 2.2 контроля и управления реконфигурацией управляет процессом восстановления, подавая управляющие сигналы на магистральные элементы 5.1, 5.2.

Блок 2.1 контроля и управления реконфигурацией подает единичный сигнал на разрешающие входы магистральных элементов 5.1 и 5.2, разрешая тем самым их работу, а блок 2.2 контроля и управления реконфигурацией подает либо единичный сигнал, либо нулевой сигнал, устанавливая направление передачи информации, в зависимости от того, какое устройство 1.1(1.2) обработки данных вводится в конфигурацию.

Например, если необходимо восстановить устройство 1.2 обработки данных, устанавливается связь с выхода 19.1 устройства

1.1обработки данных через магистральный элемент 5.1, шину 13 и магистральный элемент 5.2 на вход 19.2, устройства 1.2, 1.1 и

1.2обработки данных начинают обмен информацией. С устройства 1.1 обработки данных переписывается значение слова состояния в устройство 1.2 обработки данных. По окончании этого процесса на выходе 19.2.1 устройства 1.2 обработки данных появляется сигнал Окончание выравнивания, по которому блоки 2.1 и 2.2 контроля и управления реконфигурацией прекращают выдачу управляющих сигналов на выходах 34,1.1 и 34.2.1 и меняют управляющие сигналы на выходах шин 21.1 и 21.2, определяя работоспособную конфигурацию системы.

Режим 26 (27, 28, 29, 32, 33). Ввод в конфигурацию системы отказавшего узла оперативной памяти после устранения неисправности.

Этот режим реализуется аналогично режиму ввода узла оперативной памяти в на- чале работы. Управляет вводом в конфигурацию узла оперативной памяти или устройство обработки данных соответствующего канала, или, если устройство обработки данных соответствующего канала находится в неработоспособном состоянии, исправное устройство обработки данных.

Формула изобретения

1. Двухканальная резервированная вычислительная система, содержащая блок синхронизации, пульт управления, два резервируемых канала, каждый из которых состоит из устройства обработки данных, коммутатора, первого-третьего магистральных элементов и узла оперативной памяти, причем выход блока синхронизации подключен к синхровходам устройства обработки данных обоих резервируемых каналов, а первые информационные входы- выходы первых магистральных элементов перзого и второго резервируемых каналов объединены, а первые информационные зходы-выходы второго и третьего магистральных элементов каждого резервируемого канала являются соответствующими информационными входами-выходами системы, отличающаяся тем, что, с целью повышения надежности системы, в нее введен элемент ИЛИ, а в каждый резервируемый канал-блок контроля и управле- ния реконфигурацией и блок контроля на четность, выход которого подключен к соответствующим входам контроля блока контроля и управления реконфигурацией обоих резервируемых каналов, выход микроко- манд блока контроля и управления реконфигурацией подключен к входу управления устройства обработки данных своего канала и соответствующим управляющим входам первых магистральных элементов обоих ре- зервируемых каналов, вторые входы-выходы которых соединены с первыми информационными входами-выходами устройства обработки данных, коммутатора своего канала и соответствующими инфор- мационными входами-выходами блока контроля и управления реконфигурацией обоих резервируемых каналов, второй информационный вход-выход устройства обработки данных соединен с одноименным входомвыходом коммутатора и входом анализа блока контроля и управления реконфигурацией своего резервируемого канала, инфор- мационный выход которого является соответствующим информационным выходом системы, выход готовности блока контроля и управления реконфигурацией подключен к одноименному входу блока контроля и управления реконфигурацией другого резервируемого канала, выход реконфигурации блока контроля и управления реконфигурацией соединен с первыми управляющими входами коммутатора и второго и третьего магистральных элементов своего резервируемого канала, информационный и синхронизирующий выходы пульта управления синхронизацией подключены к входам задания режима и первым входам синхронизации блоков контроля и управления реконфигурацией обоих резервируемых каналов, вторые входы синхронизации которых и вход синхронизации пульта управления синхронизацией подключены к выходу блока синхронизации, выход элемента ИЛИ подключен к вторым управляющим входам второго и третьего магистральных элементов и входам строба блока контроля и управления реконфигурацией коммутаторов обоих резервируемых каналов, выход управления блока обработки данных каждого резервируемого канала подключен к входам управления коммутаторов своего канала и блоков контроля и управления реконфигурацией обоих резервируемых каналов, первые и вторые входы-выходы коммутаторов которых подключены к информационным входам-выходам узла оперативной памяти и блока контроля на четность одноименных резервируемых каналов, а первые и вторые управляющие выходы коммутаторов обоих резервируемых каналов подключены к адресным и управляющим входам узлов оперативной памяти соответствующих резервируемых каналов, управляющие входы записи-считывания которых подключены к входам элемента ИЛИ и одноименным выходам коммутаторов соответствующих резервируемых каналов.

2. Система поп.1, отличающая - с я тем, что блок контроля и управления реконфигурацией содержит первый-третий регистры, узел контроля, мультиплексор, коммутатор, схему сравнения, узел проверки на четность, узел задания реконфигурации, элемент ИЛИ, элемент задержки и первый-четвертый элементы И, первые входы которых подключены к входу строба блока, первый и второй входы контроля которого подключены к вторым входам первого и второго, третьего и четвертого элементов И соответственно, вход задания режима и первый вход синхронизации блока подключены соответственно к информационному и синхровходам первого регистра, выход которого соединен с первым информационным входом коммутатора, второй вход синхронизации блока через элемент задержки подключен к синхровходам второго и третьего регистров и третьим входам первого-четвертого элементов И, входы первого и второго информационных входов- выходов блока подключены соответственно к первому и второму информационным входам схемы сравнения, выход которой подключен к первому входу элемента ИЛИ, выход коммутатора подключен к информационному входу третьего регистра, выход которого соединен с адресным входом узла контроля, выход микрокоманд которого является одноименным выходом блока и подключен к информационному входу второго регистра, а младший разряд выхода микрокоманд узла контроля подсоединен к управляющему входу коммутатора, второй информационный вход которого соединен с адресным выходом узла контроля, один из разрядов которого подключен к первому информационному входу мультиплексора, выход которого подключен к одному из разрядов второго информационного входа коммутатора, адресный вход мультиплексора соединен с одноименным выходом узла контроля, выход элемента ИЛИ подключен к второму информационному входу мультиплексора, третий и четвертый информационные входы которого подключены к младшим разрядам первого и второго входов управления блока соответственно, старшие разряды которых подключены к второму и третьему входам элемента ИЛИ, четвертый вход которого является входом готовности блока, пятый и шестой входы

элемента ИЛИ подключены к выходам первого и третьего элементов И, а седьмой вход - к выходу узла проверки на четность, информационный вход которого подключен к входу анализа блока, а выход является выходом готовности блока, выходы второго и четвертого элементов И подключены к установочным входам второго регистра, выход которого является информационным выходом блока и подключен к пятому информационному входу мультиплексора и информационному входу узла реконфигурации, выход которого является выходом реконфигурации блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГИБРИДНАЯ ЯЧЕЙКА ОПТОЭЛЕКТРОННОГО НЕЙРОПРОЦЕССОРА | 1992 |

|

RU2057363C1 |

| Устройство приоритетного доступа к магистрали | 1990 |

|

SU1839249A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И РЕЗЕРВИРОВАНИЯ ИНФОРМАЦИОННОЙ СИСТЕМЫ | 2010 |

|

RU2453079C2 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1989 |

|

RU1819116C |

| Мажоритарное устройство | 1984 |

|

SU1399905A1 |

| СПОСОБ И ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА ОТКАЗОУСТОЙЧИВОЙ ОБРАБОТКИ ИНФОРМАЦИИ КРИТИЧЕСКИХ ФУНКЦИЙ ЛЕТАТЕЛЬНЫХ АППАРАТОВ | 2008 |

|

RU2413975C2 |

| Оперативное запоминающее устройство с блокировкой неисправных элементов памяти | 1976 |

|

SU622173A1 |

| Устройство для мажоритарного выбора сигналов | 1991 |

|

SU1833876A1 |

| Микропроцессорная система для программного управления технологическими процессами | 1987 |

|

SU1418653A1 |

| Переключатель линий | 1981 |

|

SU974585A1 |

Изобретение относится к вычислительной технике и может быть использовано в высоконадежных системах управления, обмена и обработки данных. Цель изобретения - повышение надежности функционирования двухканальной резервированной вычислительной системы за счет возможности двусторонней коммутации шин данных и адресных шин с выходоё одного канала на входы другого, а также за счет разделения функций контроля и управления системой между блоками контроля каждого из каналов. В системе реализуется адаптация структуры к возникшим отказам. До тех пор пока оба канала исправны, используется общее резервирование, т.е. любой канал принимает на себя основную работу в случае отказа другого. При этом исправные блоки отказавшего канала переключаются на резервирование аналогичных блоков исправного канала. Двухканальная резервированная вычислительная система содержит два канала и в каждом канале устройство обработки данных, узел оперативной памяти, блок синхронизации, пульт управления, элемент ИЛИ, блок контроля и управления реконфигурацией, первый, второй и третий магистральные элементы, блок контроля на четность и коммутатор, а блок контроля и управления реконфигурацией содержит три регистра, блок памяти, мультиплексор, ком- f мутатор, схему сравнения, узел проверки на четность, преобразователь кода, элементы задержки, ИЛИ, четыре И. 1 з.п. ф-лы, 2 табл., 4 ил. СП с VI со to ,сл

30

Таблица 1

Таблица 2

Продолжение табл.2,

fflut. Лист О

fflut.i (Лист О

Блок контроля и управления реконфигурацией

и (« .И

J

.J

L П J...L J

IПульт jfnpaBiiwffl системой 2

J...L J

U

57

I X F

| Адаптивная система обработки данных | 1980 |

|

SU926662A1 |

| Адаптивная система обработки данных | 1988 |

|

SU1552195A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-05-15—Публикация

1989-12-12—Подача