Изобретение относится к вычислительной технике и может быть использовано при построении отказоустойчивых многопроцессорных вычислительных систем (ВС).

Известна резервированная ВС, содержащая первый и второй резервируемые процессоры, первый и второй коммутаторы вывода инфс рмации, первый и второй модули памяти, устройство управления, первый и второй входы устройства управления, первый и второй коммутаторы ввода информации, первый - четвертый входы устройства управления, третий резервируемый процессор, третий коммутатор вывода информации и третий коммутатор ввода информации, пятый выход и третий вход устройства управления, четвертый коммутатор вывода информации, шестой выход устройства управления, блок сравнения, седьмой выход устройства управления В такой В С имеющийся резерв времени разделяется на такты. В каждом такте параллельно работает пара процессоров, что позволяет путем сравнения результатов их работы выявить наличие отказа одного из этих других процессоров Номер отказавшего процессора оп- ределяется в следующем такте путем анализа параллельной работы следующей пары процессоров. Если снова результаты насовпали, то отказал тот процессор, который работал в предыдущей паре и текущей паре.

Недостатком данной ВС является ограниченная область применения по количеству одновременно решаемых задач, она содержит лишь два модуля памяти и три процессора.

Известна резервированная ВС, содержащая т+1 резервируемых процессоров, т коммутаторов вывода информации, m модуХ|

СП СП Јь О О

пей памяти, устройство управления, группа входов которого подключена к контрольным выходам т+1 резервируемых процессоров, т коммутаторов ввода информации, первый и второй входы которых соединены соответственно с выходами первого и второго, и

третьегоm-1-ro и т-го, т-го и первого

модуля памяти, информационные входы второго, третьего, ..... т-го. т+1-го процессоров соединены с выходами соответственно первого, второго m-1-ro и т-го

коммутаторов ввода информации, а информационный вход первого процессора соединен непосредственно с выходом первого модуля памяти, информационные выходы второго, третьегоm-ro, m+1-ro резервируемых процессоров соединены соответственно с входами первого, второго

m-1-ro, m-ro коммутаторов вывода информации, первый и второй выходы которых соединены соответственно с входами первого

и второго, второго и третьего m-1-ro и

т-го, т-го и первого модулей памяти, а информационный выход первого процессора соединен непосредственно с входами первого модуля памяти, управляющие входы резервируемых процессоров подключены к первой группе выходов устройства управления, вторая группа выходов которого подключена к управляющим входам коммутатора ввода и вывода информации, коммутатор сравнения, информационные входы которого соединены с информационными выходами процессоров, управляющий вход - с выходом устройства управления, блок сравнения, выходы которого подключены к выходам коммутатора сравнения, а выход блока сравнения соединен с входом устройства управления.

В данной системе отказ резервируемых процессоров фиксируется внешним контролем, а также встроенным контролем, если он позволяет обнаружить этот отказ. Внешний контроль правильности функционирования процессоров осуществляется посредством устройства управления путем реконфигурации ВС в каждом такте контроля. Устройство управления обеспечивает назначения пары проверяемых процессоров на очередной такт контроля. В результате реконфигурации В С эти процессоры подключаются к одному модулю памяти и параллельно обрабатывают данные задачи этого модуля. В конце такта контроля результаты работы процессоров сравниваются в блок сравнения, В следующем такте назначается новая пара проверяемых процессоров. Если в двух тактах подряд произошло несравнение результатов работы пары проверяемых процессоров, то принимается решение о неисправности процессора, который контролировался в обеих парах. При обнаружении неисправного процессора внешний контроль прекращается, неисправный процессор восстанавливается, а исправные mпроцессоров на это время подключаются только к соответствующим m модулям памяти.

Недостатком ВС является низкая достоверность контроля, так как в случае отказа процессора в момент назначения его в пару контролируемых время обнаружения его отказа составит 2 или (т+1) тактов.

Целью изобретения является повышение надежности функционирования резервированной ВС путем обеспечения перекрестной коммутации резервируемых процессоров и модулей памяти.

Поставленная цель достигается тем, что

в резервированную вычислительную систему, содержащую группу резервируемых процессоров, группу коммутаторов ввода- вывода, группу модулей памяти, коммутатор сравнения, блок сравнения и блок управления резерви ровайием, вход сравнения которого подключен к выходу блока сравнения, первый и второй информационные входы которого соединены с одноименными выходами коммутатора сравнения, вход управления которого соединен с выходом адреса сравнения блока управления резервированием группа входов готовности процессоров которого подключена соответтсвенно к первым выходам готовности резервируемых процессоров группы, а группа выходов управления коммутацией которого подключена к входам управления соответствующих коммутаторов ввода-вывода группы, первые информационные входы-выходы которых

соединены с информационными входами- выходами соответствующих модулей памяти группы, дополнительно содержит группу шинных формирователей, первые информационные входы-выходы которых соединены

с информационными входами-выходами соответствующих резервируемых процессоров группы, вторые информационные входы-выходы шинных формирователей группы соединены с одноименными выходами-входами соответствующих коммутаторов ввода-вывода группы, входы строба которых соединены с одноименными входами соответствующих шинных формирователей группы и подключены к вторым выходам

готовности соответствующих резервируемых процессоров группы, выходы информационных входов-выходов которых подключены к соответствующим информационным входам коммутатора сравнения, а

выходы строба резервируемых процессоров

группы подключены к выходу строба блока управления резервированием, выход синхронизации контроля которого подключен к входу синхронизации блска сравнения, а выход состояния процессоров - к входам разрешения соответствующих шинных формирователей группы, информационный выход каждого К коммутатора ввода-вывода группы соединен с информационным входом К+1-го коммутатора ввода-вывода труппы, информационный выход последнего из которых подключен к информационному входу первого коммутатора ввода-вывода группы, а выход готовности блока управления резервированием является одноимен- ным выходом системы

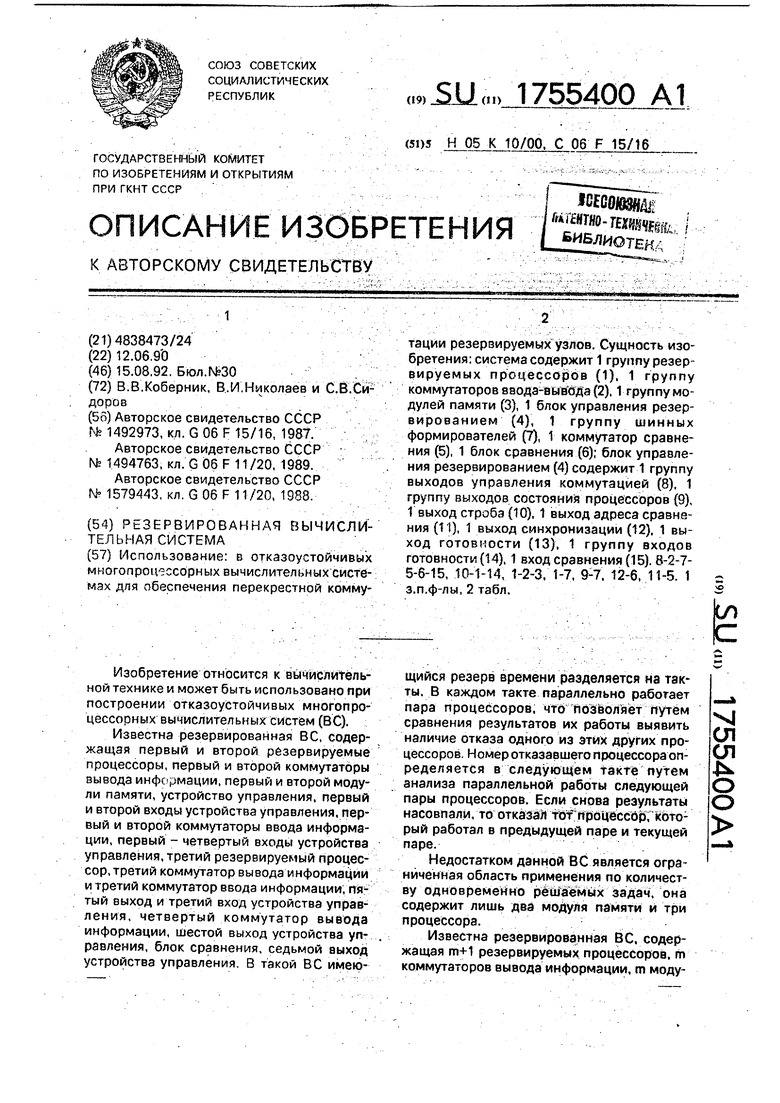

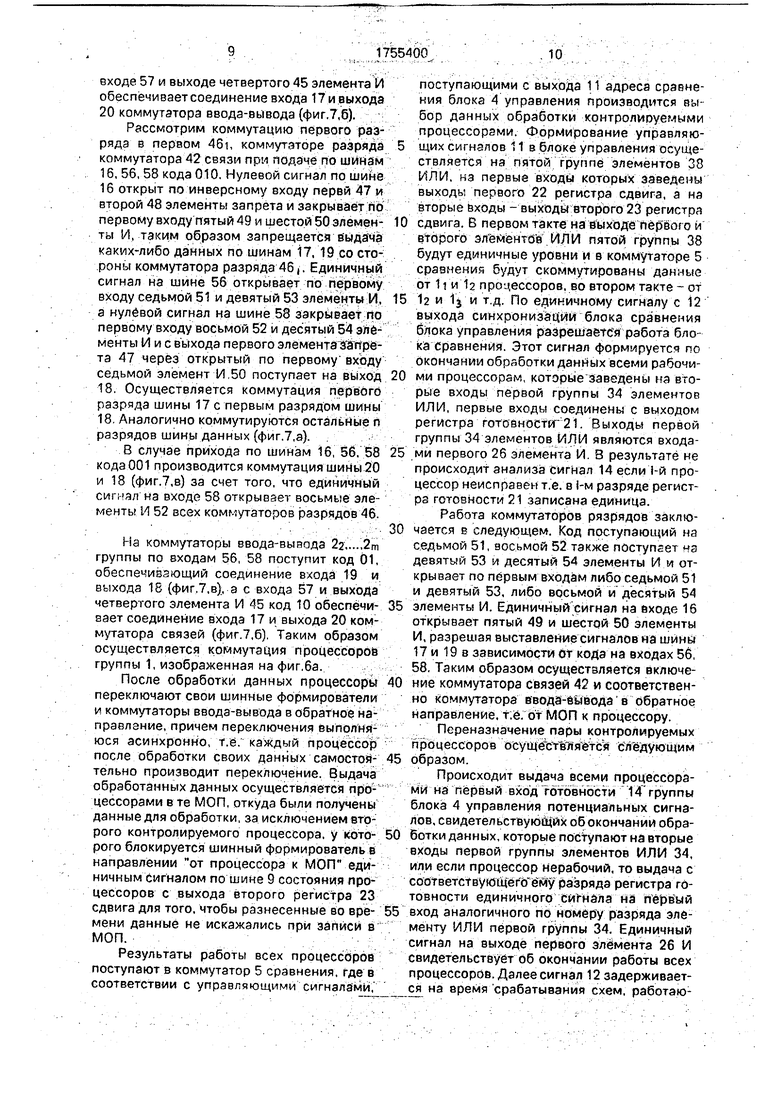

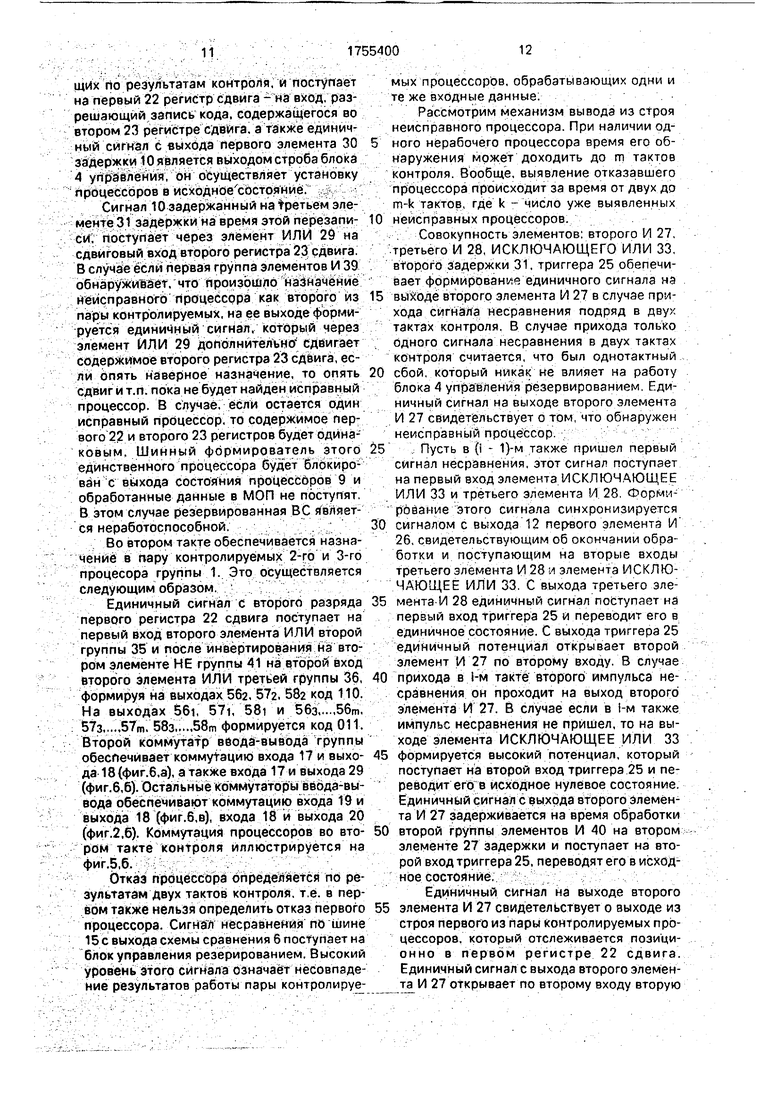

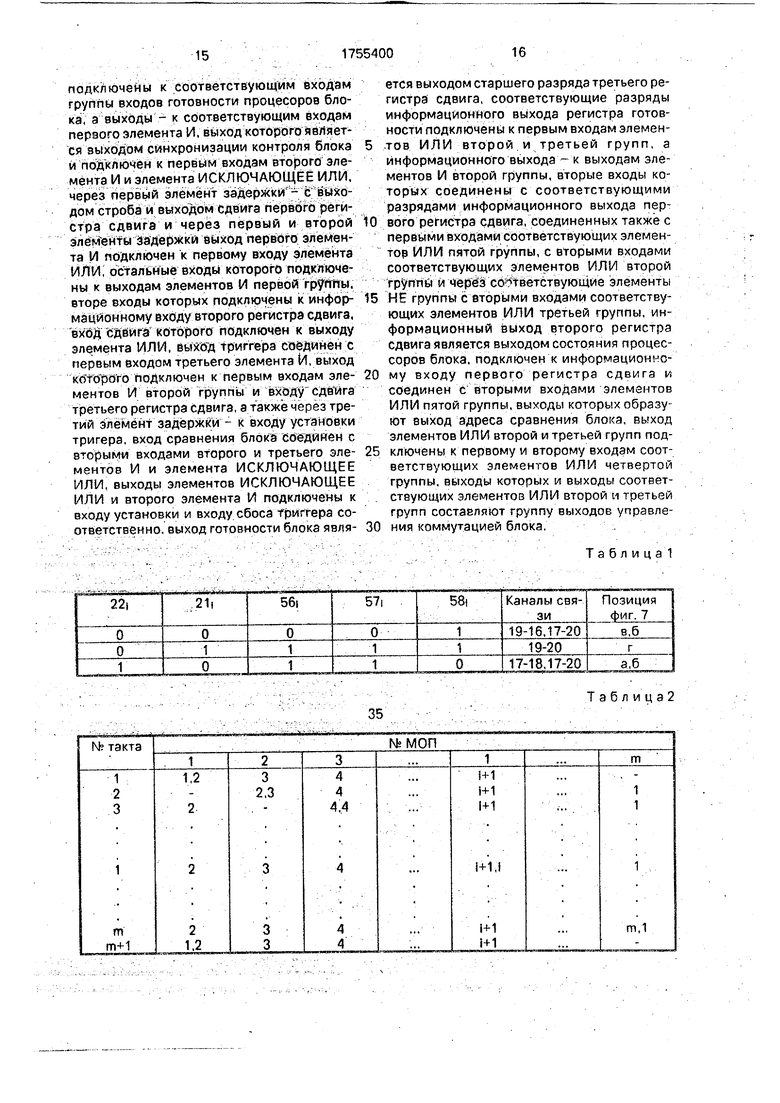

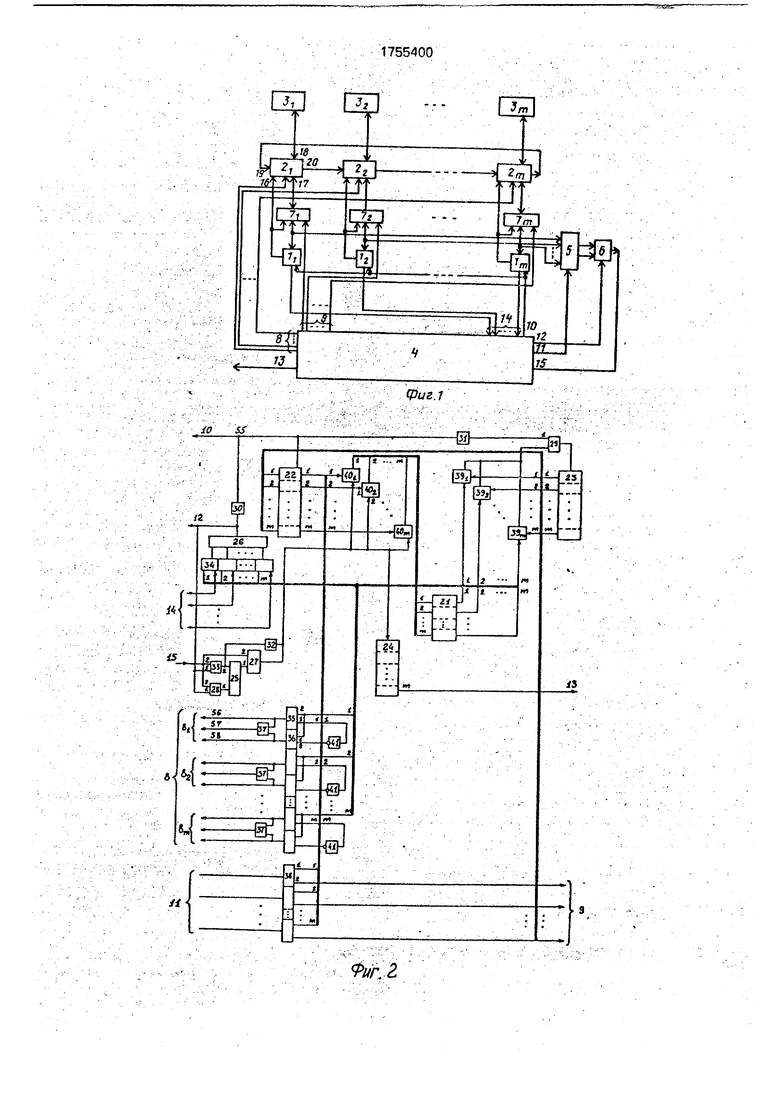

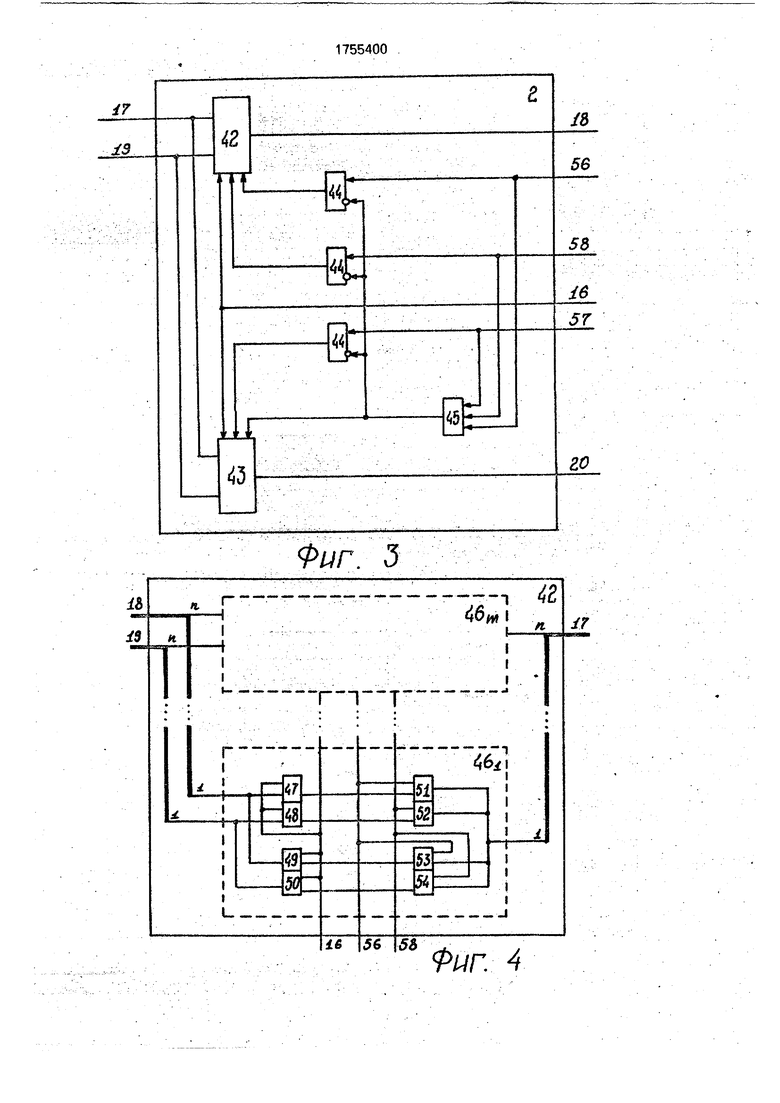

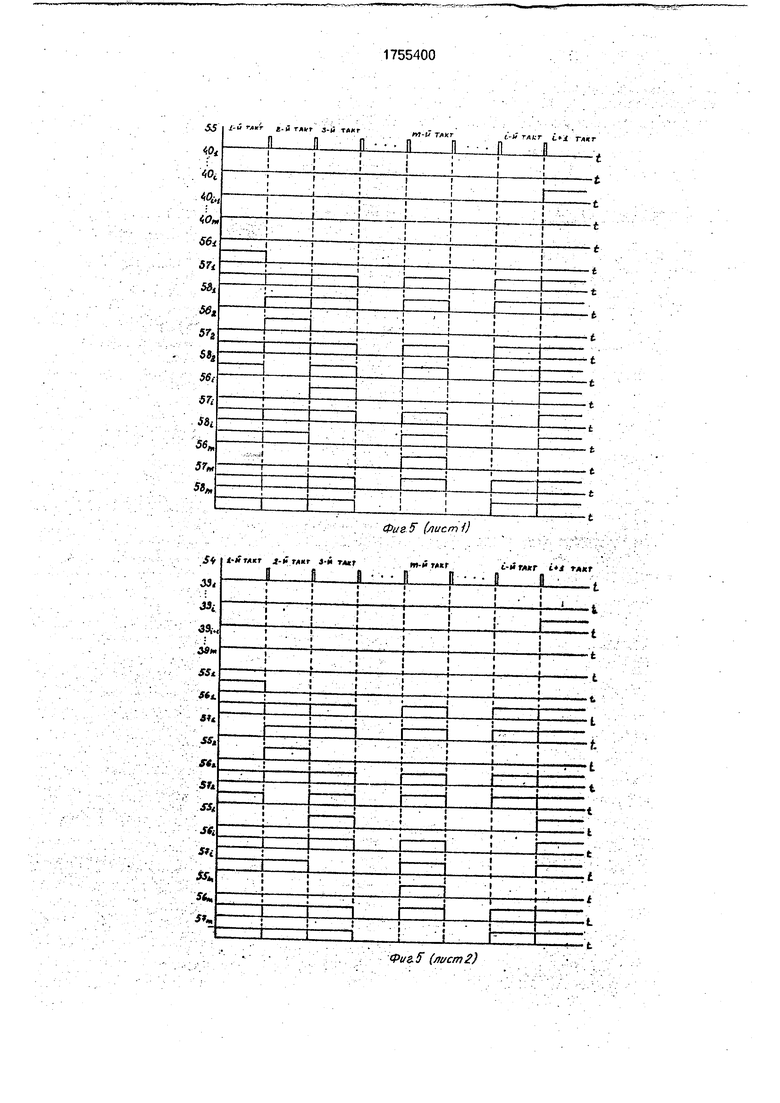

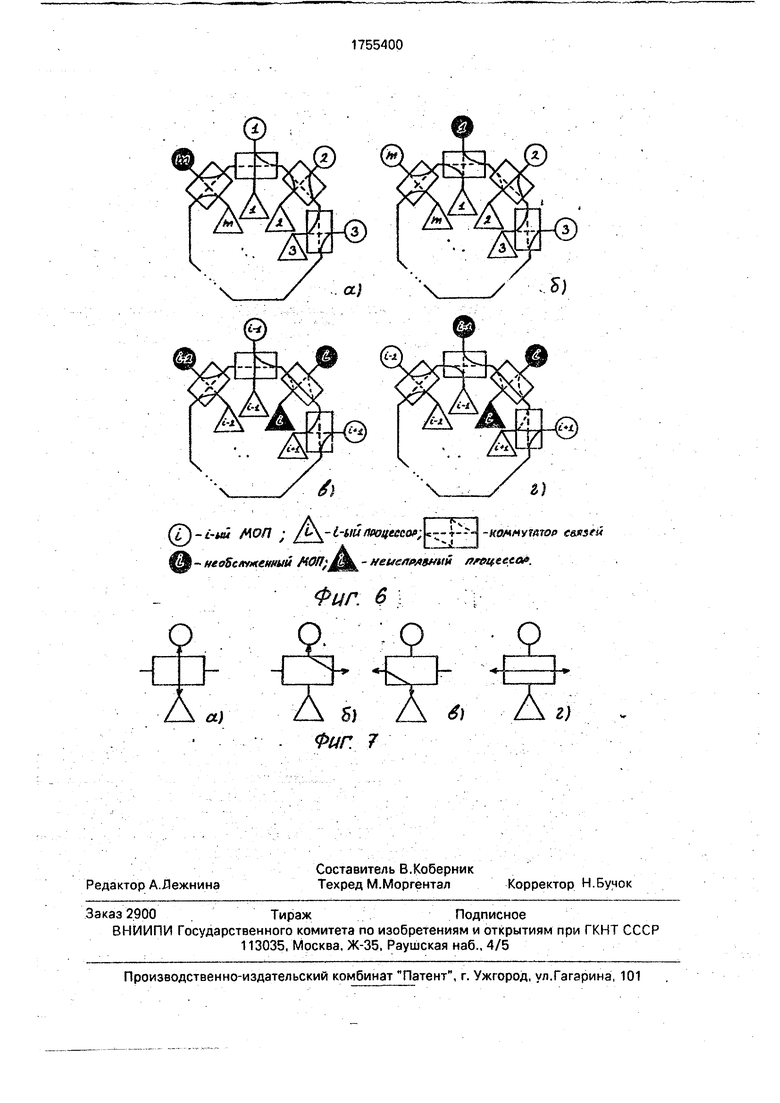

На фиг.1 представлена схема резервированной вычислительной системы; на фиг.2 - структурная схема блока управления резервированием; на фиг 3 - коммутатор ввода-вывода; на фиг 4 - коммутатор связей, на фиг.5 - временные диаграммы работы устройства; на фиг 6 - организация возможных каналов связи между процессорами и модулями памяти ВС, на фиг.7 - возможные направления коммутации коммутатора ввода-вывода

Резервированная вычислительная система (иг 1) содержит группу резервируемых процессоров 1. коммутаторов 2 ввода-вывода, модулей 3 памяти, блок 4 управления резервированием, коммутатор 5 сравнения, блок б сравнения, группу шинных формирователей 7 Блок управления резервированием содержит группу выходов 8 управления коммутациями, группу выходов 9 состояния процессоров, выход 10 строба блока управления резервированием, выход 11 адреса сравнения блока управления резервированием, выход 12 синхронизации блока сравнения, выход 13 готовности блока управления резервированием, первую группу 14 входов готовности блока управления, вход 15 сравнения Группа выходов 8 управления коммутацией подключена к од- поименным управляющим входам коммутаторов ввода-вывода группы 2, которые содержат также вход строба 16 первый 17 и второй 18 информационные входы-выхо- ды, информационный вход 19 и выход 20.

Блок управления (фиг,2) содержит регистр 21 готовности, первый - третий регистры 22, 23 и 24 сдвига, триггер 25, первый 26, второй 27 и третий 28 элементы И, эле- мент ИЛ И 29, первый 30, второй 31 и третий 32 элементы задержки, элемент 33 ИСКЛЮЧАЮЩЕЕ ИЛИ, первую 34, вторую 35, третью 36, четвертую 37 и пятую 38 группы элементов ИЛИ, первую 39 и вторую 40

группы элементов И и группу элементов НЕ 41

Коммутатор в вода-вывода (фиг 3)содео жит первый 42 и второй 43 коммутатор1 связей, группу элементов запрета 44, четвертый элемент И 45

Коммутатор связей (фиг.4) содержит п одинаковых коммутаторов 46 разрядов - по числу разрядов шины данных, каждый ит которых содержит первый 47, второй 48 элементы запрета, пятый 49, шестой 50, седьмой 51, восьмой 52, девятый 53 и десятый 54 элементы И.

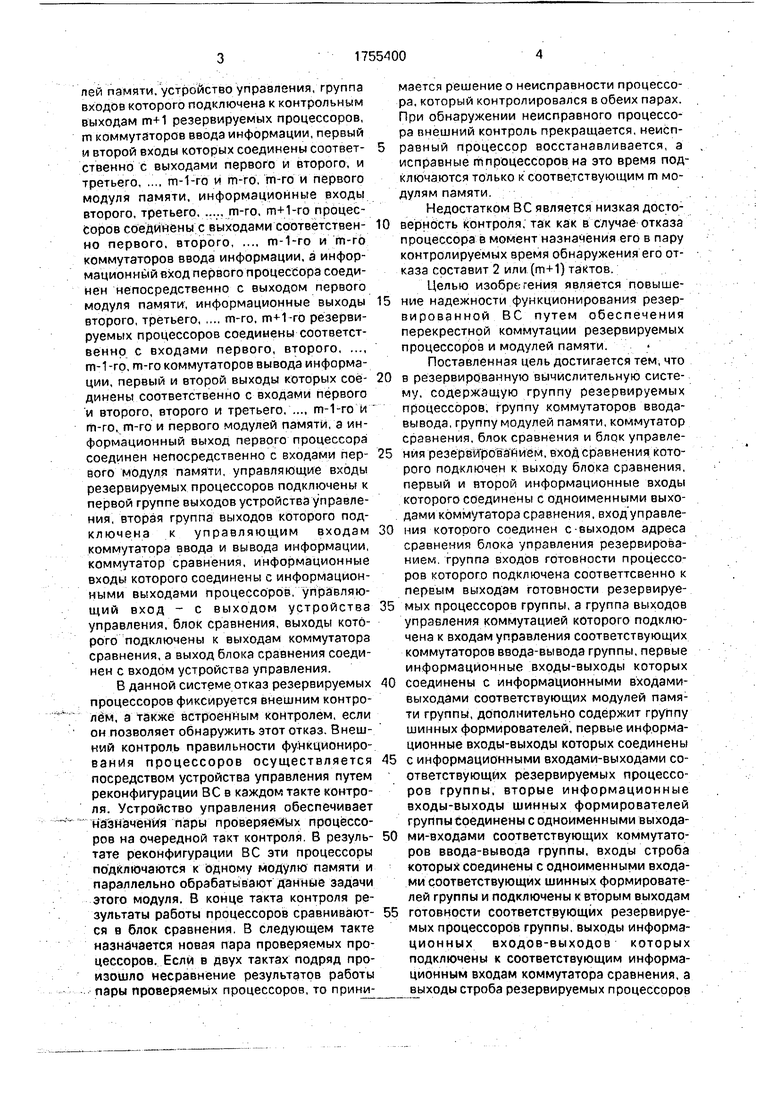

На временных диаграммах (фиг.5) обозначены1 55 - сигнал на выходе первого эле мента 30 задержки; 21i,..,21m - состояние регистра готоВнбетТГгТрЪцессо роё1; 56Ь 57| 58i - сигналы управлния коммутаторами ввода-вывода с управления коммутацией группы блока 4 управления

Регистр 21 готовности процессоров содержит информацию о состоянии процессо- ров (исправен или неисправен), что определяется состоянием )4bf регистра 2 если 1-й разряд в нулевом состоянии 1-1 процессор исправен, если в единичном - неисправен

Первый 22 второй 30 регистры сдвига показывают местоположение первого и второго контролируемых процессоров, работающих в паре с одним МОП. Единичное состояние 1-го разряда первого 22 (второго 30) регистра сдвига указывает на то, что 1-й процессор в данном такте является первым (вторым) в паре параллельно работающих процессоров

Первая группа элементов И 39 предназначена для обнаружения ситуации назначения неисправного процеёсора как второго для пары контролируемых. Вторая группа 40 элементов И позволяет выводить в ремонт неисправные процессоры, т.е переводить в единичное состояние разряды регистра 21 готовности процессоров

Регистр 21 сдвига предназначен для выявления момента прекращения работы ВС Это произойдет когда останется один исправный процессор

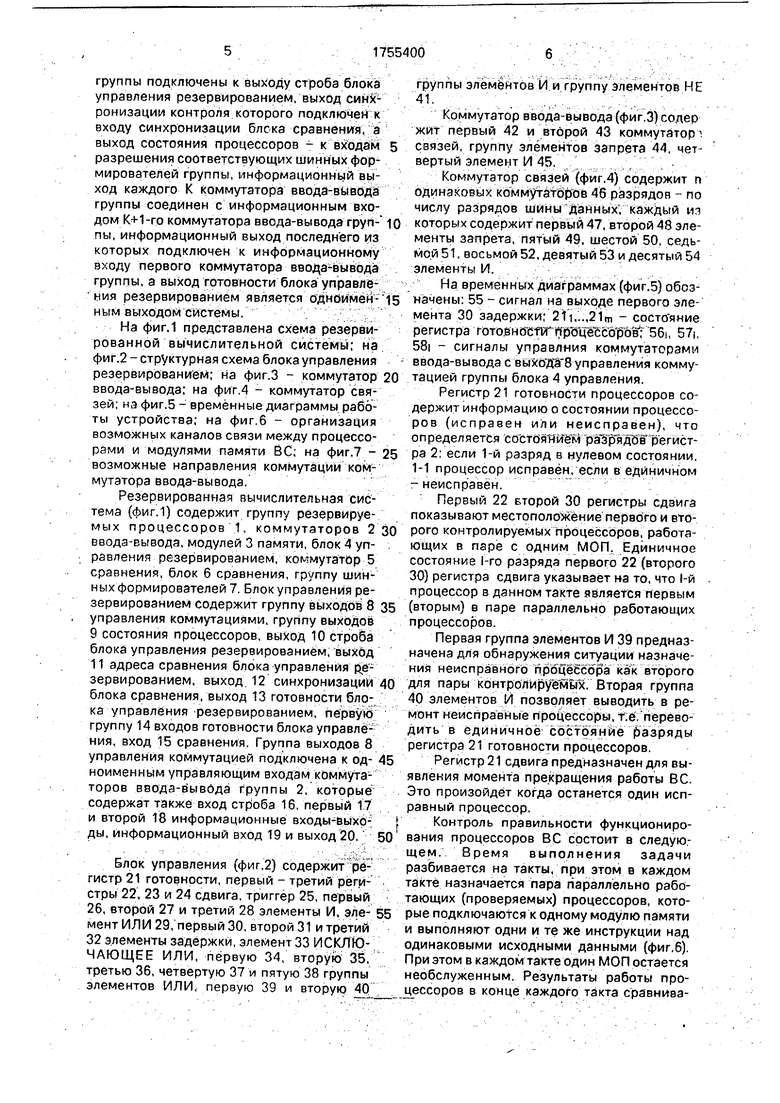

Контроль правильности функционирования процессоров ВС состоит в следующем Время выполнения задачи разбивается на такты, при этом в каждом такте назначается пара параллельно работающих (проверяемых) процессоров, которые подключаются к одному модулю памяти и выполняют одни и те же инструкции над одинаковыми исходными данными (фиг.6) При этом в каждом такте один МОП остается необслуженным Результаты работы процессоров в конце каждого такта сравниваются На следующий такт назначается новая пара проверяемых процессоров Отказавший процессор определяется по результатам его работы в двух смежных тактах Если при работе в двух тактах подряд произошло иесравнение результатов, то процессор учавствовавший в работе в двух тактах подряд считается неисправным и выводится в ремонтную конфигурацию, а соответствующий ему по номеру МОП в дальнейшем остается необслуженным Если было несравнение в первой паре, а во второй результаты работы совпали то это значит, что имен место однотактный сбой либо отказал первый из проверяемых процессоров группы который будет выявлен в следующем цикле контроля Резервированная ВС остается работоспособной пока имеется два исправных процессора

Подключение процессоров к соответствующим модулям памяти осуществляется с помощью группы коммутаторов 2 ввода-вывода управление которыми осуществляется сигналами с блока 4 управления в соответствии с содержимым регистра 22 сдвига и регистра 21 состояния процессоров

Возможные каналы связи между процессорами и МОП показаны на фиг бив табл 1

Резервированная ВС работает следующим образом

В исходном состоянии группа 1 процессоров исправна, в МОП группы 3 находятся даные, необходимые для обработки, во всех разрядах регистра 21 готовности записаны нули, в первом 22 и третьем 24 регистрах сдвига записан код 10...00, во втором регистре сдвига - код 01 00 В этом состоянии будут контролироваться процессоры 1i, 12 (фиг.б.а). Это осуществляется путем коммутации этих процессоров к первому 3i модулю памяти группы Через шинные формирователи 7з ,7m i группы процессоры 1з,...,1т-1 группы будут подключены соответственно к 32 ,3m i МОП группы Шинные формирователи группы 7 управляются процессорами В исходном состоянии они обеспечивают передачу даных для обработки из МОП в процессоры После обработ- ки данных процессорами, последние переводит шинные формирователи в состояние, обеспечивающее передачу обработанных данных из процессора в МОП Как только все обработанные даные будут выданы, шинные формирователи будут переведены процессорами в исходное состояние Таким образом осуществляется связь между процессорами и МОП.

Порядок подключения процессоров к модулям показан в табл 2

Такая коммутация процессоров осуще- ствляется следующим образом и она поясняется с помощью временных диаграмм (фиг 4) выдачи управляющих сигналов на

коммутаторы 2 ввода-вывода группы

В первом такте контроля контролируются 11 и 12 процессоры группы С выхода первого регистра 22 сдвига единичный сигнал поступает на первый вход первого эле0 мента ИЛИ 35 второй группы а также через первый элемент НЕ группы 41 - на второй вход первого элемента ИЛИ 35 второй группы В результате на выходе 56 первого элемента ИЛИ второй группы 35 формируется

5 единичный сигнал который поступает на первый вход первого элемента ИЛИ четвертой 37 группы, создавая на его выходе 57 высокий потенциал На вторые входы первых элементов ИЛИ второй группы 35 и пер0 вые входы первых элементов ИЛИ пятой группы 38 поступает сигнал с первого разряда регистра 21 готовности процессоров Так как в исходном состоянии все процессоры исправны то во всех разрядах регистра

5 21 готовности будут записаны нули На выходе 58i первого элемента ИЛИ 36 четвертой группы будет сформирован нулевой сигнал На первый коммутатор 2i ввода- вывода группы по входам 56ч, 57i 58( ши0 ны 8 поступит код 110 С выходов 2, m первого регистра 22 сдвига нулевые сигналы поступят на первые входы элементов 352 35т второй группы ИЛИ и проинвер- тированные на элементах НЕ 412, .,42т

5 групплы поступят на элементы 362, ..,3бт третьей группы ИЛИ. В результате на выходах элементов 352, ,35т ИЛИ, 582 58m и соответственно на выходах 572, ,57т элементов 372, ,37т четвертой группы ИЛИ

0 сформируются единичный потенциалы, на выходах 562 .. ,56т - нулевые потенциалы. На коммутаторы 2а, . ,1т группы по входам 56. 57 и 58 шины 8 поступает код 011.

На коммутаторы ввода-вывода по вто5 рым управляющим входам 16 с процессоров поступают нулевые сигналы, свидетельствующие о готовности процессоров принять данные Так как на выходах 56, 57, 58 не все единицы, то на выходе четвертого элемента

0 И 45 нулевой потенциал, который открывает по запрещающему входу элементы группы запрета 44, разрешая прохождение управляющих сигналов 56 на первый коммутатор 42 связей, 57 - на второй коммутатора 43

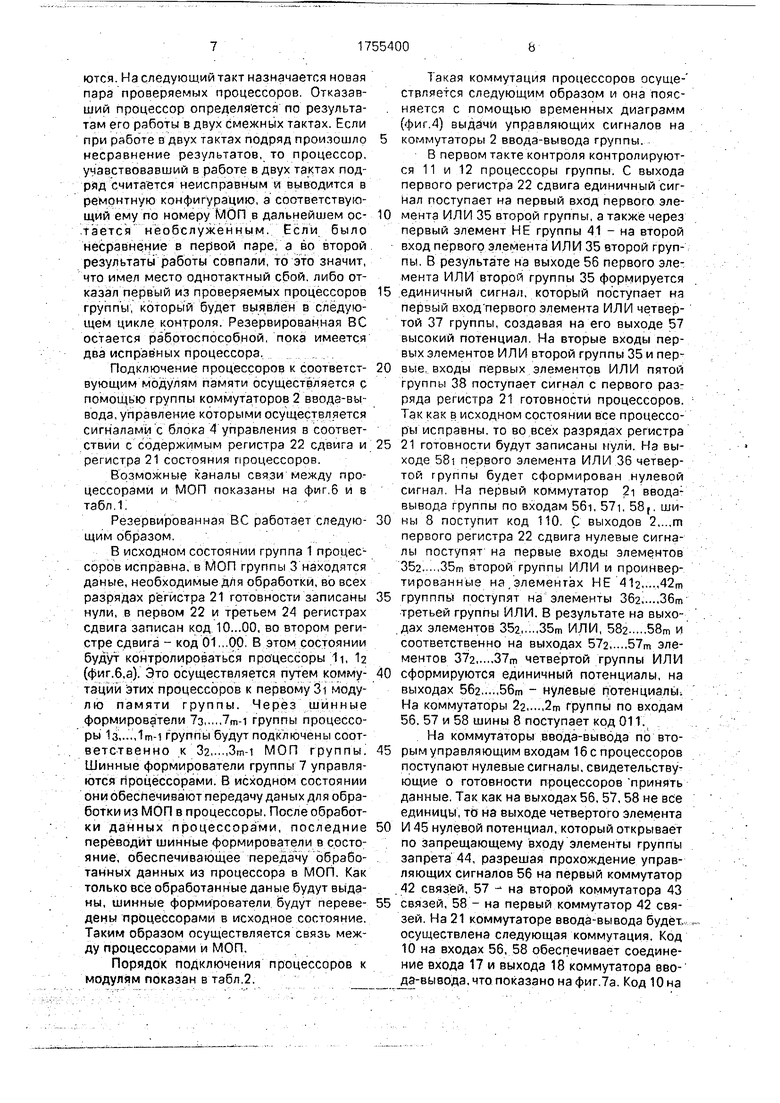

5 связей, 58 - на первый коммутатор 42 связей На 21 коммутаторе ввода-вывода будет осуществлена следующая коммутация. Код 10 на входах 56, 58 обеспечивает соединение входа 17 и выхода 18 коммутатора ввода-вывода, что показано на фиг 7а Код Юна

входе 57 и выходе четвертого 45 элемента И обеспечивает соединение входа 17 и выхода 20 коммутатора ввода-вывода (фиг.7,6).

Рассмотрим коммутацию первого разряда в первом 461, коммутаторе разряда коммутатора 42 связи прм подаче по шинам 16, 56, 58 кода 010, Нулевой сигнал по шине 16 открыт по инверсному входу первй 47 и второй 48 элементы запрета и закрывает по первому входу пятый 49 и шестой 50 элементы И, таким образом запрещается выдача каких-либо данных по шинам 17, 19 со стороны коммутатора разряда 46 (. Единичный сигнал на шине 56 открывает по первому входу седьмой 51 и девятый 53 элементы И, а нулевой сигнал на шине 58 закрывает rto первому входу восьмой 52 и десятый 54 элементы И и с выхода первого элемента запрета 47 через открытый по первому входу седьмой элемент И 50 поступает на выход 18 Осуществляется коммутация первого разряда шины 17 с первым разрядом шины 18 Аналогично коммутируются остальные п разрядов шины данных (фиг 7,а)

В случае прихода по шинам 16, 56, 58 кода 001 производится коммутация шины 20 и 18 (фиг.7,в) за счет того, что единичный сигнал на входе 58 открывает восьмые элементы И 52 всех коммутаторов разрядов 46

На коммутаторы ввода-вывода 22,...,2гп группы по входам 56, 58 поступит код 01, обеспечивающий соединение входа 19 и выхода 18 (фиг 7,в), а с входа 57 и выхода четвертого элемента И 45 код 10 обеспечивает соединение входа 17 и выхода 20 коммутатора связей (фиг 7,6) Таким образом осуществляется коммутация процессоров группы 1, изображенная на фиг 6а.

После обработки данных процессоры переключают свои шинные формирователи и коммутаторы ввода-вывода в обратное направление, причем переключения выполня- юся асинхронно, т.е каждый процессор после обработки своих данных самостоятельно производит переключение Выдача обработанных данных осуществляется процессорами в те МОП, откуда были получены данные для обработки за исключением второго контролируемого процессора, у которого блокируется шинный формирователь в направлении от процессора к МОП единичным сигналом по шине 9 состояния процессоров с выхода второго регистра 23 сдвига для того, чтобы разнесенные во времени данные не искажались при записи в МОП.

Результаты работы всех процессоров поступают в коммутатор 5 сравнения, где в соответствии с управляющими сигналами,

поступающими с выхода 11 адреса сравнения блока 4 управления производится выбор данных обработки контролируемыми процессорами Формирование управляющих сигналов 11 в блоке управления осуществляется на пятой группе элементов 38 ИЛИ, ьз первые входы которых заведены выходь1 первого 22 регистра сдвига, а на вторые входы - выходы второго 23 регистра

0 сдвига. В первом такте на выходе первого и второго элементов ИЛИ пятой группы 38 будут единичные уровни и в коммутаторе 5 сравнения будут скоммутированы данные от 11 и 12 прочессоров, во втором такте - от

5 12 и 13 и тд По единичному сигналу с 12 выхода синхронизации блока сравнения блока управления разрешается работа блока сравнения Этот сигнал формируете по окончании обработки данных всеми рабочи0 ми процессорам котэрые заведены на вторые входы первой группы 34 элементов ИЛИ, первые входы соединены с выходом регистра готовности 21 Выходы первой группы 34 элементов ИЛИ являются входа5 ми первого 26 элемента И 8 результате не происходит анализа сигнал 14 если i-й процессор неисправен т е. в i-м разряде регистра готовности 1 записана единица.

Работа коммутаторов рязрядов заклю0 чается в следующем. Код поступающий на седьмой 51, аосьмой 52 также поступает чз девятый 53 и десятый 54 элементы И и открывает по первым входам либо седьмой 51 и девятый 53, либо восьмой и десятый 54

5 элементы И. Единичный сигнал на входе 16 открывает пятый 49 и шестой 50 элементы И, разрешая выставление сигналов на шины 17 и 19 в зависимости от кода на входах 56 58 Таким образом осуществляется включе0 ние коммутатора связей 42 и соответственно коммутатора ввода-вывода в обратное направление, т.е. от МОП к процессору

Переназначение пары контролируемых процессоров осуществляется следующим

5 образом

Происходит выдача всеми процессорами на первый вход готовности 14 группы блока 4 управления потенциальных сигналов, свидетельствующих об окончании обра0 ботки данных, которые поступают на вторые входы первой группы элементов ИЛИ 34, или если процессор нерабочий, то выдача с соответетвукЭщего ейу разряда регистра готовности единичного сигнала на первый

5 вход аналогичного по номеру разряда элементу ИЛИ первой группы 34. Единичный сигнал на выходе первого элемента 26 И свидетельствует об окончании работы всех процессоров. Далее сигнал 12 задерживается на время срабатывания схем, работающйх по результатам контроля, и поступает на первый 22 регистр сдвига - на вход, разрешающий запись кода, содержащегося во втором 23 регистре сдвига, а также единичный сигнал с выхода первого элемента 30 задержки 10 является выходом строба блока 4 управления, он осуществляет установку процессоров в исходное состояние.

Сигнал 10 задержанный на третьем элементе 31 задержки на время этой перезаписи, поступает через элемент ИЛИ 29 на сдвиговый вход второго регистра 23 сдвига. В случае если первая группа элементов И 39 обнаруживает, что произошло назначение неисправного процессора как второго из пары контролируемых, на ее выходе формируется единичный сигнал, который через элемент ИЛИ 29 дополнительно сдвигает содержимое второго регистра 23 сдвига, если опять наверное назначение, то опять сдвиг и т.п. пока не будет найден исправный процессор. В случае, если остается один исправный процессор, то содержимое первого 22 и второго 23 регистров будет одинаковым, Шинный формирователь этого единственного процессора будет блокирован с выхода состояния процессоров 9 и обработанные данные в МОП не поступят, В этом случае резервированная ВС Является неработоспособной.

Во втором такте обеспечивается назначение в пару контролируемых 2-го и 3-го процесора группы 1. Это осуществляется следующим образом.

Единичный сигнал с второго разряда первого регистра 22 сдвига поступает на первый вход второго элемента ИЛИ второй группы 35 и после инвертирования на втором элементе НЕ группы 41 на второй вход второго элемента ИЛИ третьей группы 36, формируя на выходах 562, 572, 582 код 110.

На выходах 56i, 57i, 58i и 56з56m.

57з57щ. 58з58m формируется код 011.

Второй коммутатр ввода-вывода группы обеспечивает коммутацию входа 17 и выхода 18{фиг.6,а), а также входа 17 и выхода 29 (фиг.6,6). Остальные коммутаторы ввода-вывода обеспечивают коммутацию входа 19 и выхода 18 (фиг.б,в), входа 18 и выхода 20 (фиг.2,6). Коммутация процессоров во втором такте контроля иллюстрируется на фиг.5,6.

Отказ процессора определяется по результатам двух тактов контроля, т е. в первом также нельзя определить отказ первого процессора. Сигнап несравнения по шине 15 с выхода схемы сравнения 6 поступает на блок управления резерированием. Высокий уровень этого сигнала означает несовпадение результатов работы пары контролируемых процессоров, обрабатывающих одни и те же входные данные.

Рассмотрим механизм вывода из строя неисправного процессора. При наличии одного нерабочего процессора время его обнаружения может доходить до m тактов контроля. Вообще, выявление отказавшего процессора происходит за время от двух до m-k тактов, где k - число уже выявленных

0 неисправных процессоров.

Совокупность элементов: второго Л 27, третьего И 28, ИСКЛЮЧАЮЩЕГО ИЛИ 33, второго задержки 31, триггера 25 обепечи- вает формирование единичного сигнала на

5 выходе второго элемента И 27 в случае прихода сигнала несравнения подряд в двух тактах контроля. В случае прихода только одного сигнала несравнения в двух тактах контроля считается, что был однотактный

0 сбой, который никак не влияет на работу блока 4 управления резервированием Единичный сигнал на выходе второго элемента И 27 свидетельствует о том, что обнаружен неисправный процессор

5 Пусть в (i - 1)-м также пришел первый сигнал несравнения, этот сигнал поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 33 и третьего элемента И 28 Формирование этого сигнала синхронизируется

0 сигналом с выхода 12 первого элемента И 26, свидетельствующим об окончании обработки и поступающим на вторые входы третьего элемента И 28 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 33 С выхода третьего эле5 мента И 28 единичный сигнал поступает на первый вход триггера 25 и переводит его в единичное состояние. С выхода триггера 25 единичный потенциал открывает второй элемент И 27 по второму входу. В случае

0 прихода в 1-м такте второго импульса несравнения он проходит на выход второго элемента И 27. В случае если в 1-м также импульс несравнения не пришел, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 33

5 формируется высокий потенциал, который поступает на второй вход триггера 25 и переводит его в исходное нулевое состояние. Единичный сигнал с выхода второго элемента И 27 задерживается на время обработки

0 второй группы элементов И 40 на втором элементе 27 задержки и поступает на второй вход триггера 25, переводят его в исходное состояние.

Единичный сигнал на выходе второго

5 элемента И 27 свидетельствует о выходе из строя первого из пары контролируемых процессоров, который отслеживается позици- онно в первом регистре 22 сдвига. Единичный сигнал с выхода второго элемен- 27 открывает по второму входу вторую

группу элементов И 40 и разрешает запись единицы с 1-го разряда первого регистра 22 сдвига в i-й разряд регистра 21 готовности процессоров. Теперь i-й процессор считается неисправным. Коммутация i-ro коммутатора ввода-вывода изменяется следующим образом., ;

Как только появляется единичный уровень на выходе 1-го разряда регистра готовности он поступает на вторые входы 1-х элементов ИЛИ второй 35 и третьей 36 группы, формируя на их выходах 56i, 681 и соответственно на выходе 57i i-ro элемента ИЛИ четвертой группы 37 высокие уровни, т.е. на 1-й коммутатор ввода-вывода по входам 56ь 57,, 58i поступит код 111. Он сформирует единичный уровень на выходе четвертого элемента И 45, который закроет по запрещающему входу элементы запрета группы 44, а также осуществляют коммутацию второго коммутатора 43 связей, соединяя вход 19 и выход 20 (фиг б,г), коммутация первого коммутатора 42 не происходит. Коммутация процессоров в m+(i - 1) и m+i тактах изображена на фиг 6 в,г, а также поясняется временной диаграммой фиг.5. Коммутация неисравного процессора не происходит и его МОП остае ся необслужепным

Отказ резервированной ВС наступает в случае, если остается один рабочий процессор, об этом сигнализирует единичный сигнал на чевсртом выходе 13 готовности блока 4 управления резервированием.-Он формируется на гл-м разряде регистра 24 сдвига, сдвиговый вход которого соединен с выходом второго элемента И 27. После прихода m -1 таких сигналов на гл-м разряде регистра сдвига появляется единица, резервированная ВС неработоспособна. Таким образом, в предлагаемой В С осуществляется последовательный контроль работоспособности всех процессоров, пока в конфигурации ВС не останется один исправный процессор, что обеспечивает повышение надежности ВС по сравнению с прототипом.

Формула изобретения

1. Резервированная вычислительная система, содержащая группу резервируемых процессоров, группу коммутаторов вво- да-в-ывода, группу модулей памяти, коммутатор сравнения, блок сравнения и блок управления резервированием, вход сравнения которого подключен к выходу блока сравнения, первый и второй информационные входы которого соединены с одноименными выходами коммутатор сравнения, вход управления которого соединен с выходом адреса сравнения блока

управления резервированием, группа вхо дов готовности процессоров которого подключена соответственно к первым выходим готовности резервируемых процесссорсп

группы, а группа выходов управления коммутацией которого подключена к входам управления соответствующих коммутаторов ввода-вывода группы, первые информзци онные входы-выходы которых соединены с

0 информациоными входами выходами соответствующих модулей памяти группы, отличающаяся тем что, с целью повышения надежности устройства путем обеспечения перекрестной коммутаций резервируемых

5 процессов и модупей памяти, в систему вве дена группа шинных формирователей, первые информационные входы-выходы которых соединены с информационными входами-выходами соовтетствующйх резср0 вируемых процессоров группы, вторые информационные входы-выходы шинных формирователей группы соединены с одноименными выходами-входами соответствующих коммутаторов ввода-вывода группы

5 входы стробз которых соединены с одноименными входами соответствующих шинных формирователей группы и подключены к вторым выходам готовности соответстау- ющих резервируемых процессоров группы,

0 выходы информационных входов-выходов которых подключены к соответствующим информационным входам коммутатора сравнения, а выходы строба резервируемых процессоров группы подключены к выходу

5 строба блока управления резервированием, выход синхронизации контроля которого подключен к входу синхронизации блока сравнения, а выходы состояния процессоров - к входам разрешения соответствую0 щих шинных формирователей группы, информационный выход каждого К коммутатора ввода-вывода группы соединен с ин формационным входом К+1-го коммутатора ввода-вывода группы, информационный вы5 ход последнего из которых подключен к информационному входу первого коммутатора ввода-вывода группы, а выход готовности блока управления резервированием является одноименным выходом системны.

0 2. Система по п. 1,отличающаяся тем, что блок управления резервированием содержит регистр гбтбв йости, первый - третий регистры сдвига, триггер, три элемента И, элемент ИЛИ, три элемента задержки,

5 элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. пять групп элементов ИЛИ, две группы элементов И и группу элементов НЕ, причем выход регистра готовности подключен к первым входам элементов И первой группы и элементов ИЛИ первой группы, вторые входы которых

подключены к соответствующим входам группы входов готовности процесоров блока, а выходы - к соответствующим входам первого элемента И, выход которого является выходом синхронизации контроля блока и подключен к первым входам второго элемента И и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, через первый элемент задержки - с выходом строба и выходом сдвига первого регистра сдвига и через первый и второй элементы задержки выход первого элемента И подключен к первому входу элемента ИЛИ, остальные входы которого подключены к выходам элементов И первой гругГпы. вторе входы которых подключены к инфор- мацйонному входу второго регистра сдвига, вход сдвига которого подключен к выходу элемента ИЛИ, выхбд триггера соединен с первым входом третьего элемента И, выход кбторого подключен к первым входам эле- ментов И второй группы и входу сдв ига третьего регистра сдвига, а также через третий элемент задержки - к входу установки тригера, вход сравнения блока соединен с вторыми входами второго и третьего эле- ментов И и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и второго элемента И подключены к входу установки и входу сбоса триггера соответственно, выход готовности блока явля-

ется выходом старшего разряда третьего регистра сдвига, соответствующие разряды информационного выхода регистра готовности подключены к первым входам элементов ИЛИ второй и третьей групп, а информационного выхода - к выходам элементов И второй группы, вторые входы которых соединены с соответствующими разрядами информационного выхода первого регистра сдвига, соединенных также с первыми входами соответствующих элементов ИЛИ пятой группы, с вторыми входами соответствующих элементов ИЛИ второй группы и через соответствующие элементы НЕ группы с вторыми входами соответствующих элементов ИЛИ третьей группы, информационный выход второго регистра сдвига является выходом состояния процессоров блока, подключен к информационному входу первого регистра сдвига и соединен с вторыми входами элементов ИЛИ пятой группы, выходы которых образуют выход адреса сравнения блока, выход элементов ИЛИ второй и третьей групп подключены к первому и второму входам соответствующих элементов ИЛИ четвертой группы, выходы которых и выходы соответствующих элементов ИЛИ второй и третьей групп составляют группу выходов управления коммутацией блока,

Таблица1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления реконфигурацией резервированной вычислительной систем | 1989 |

|

SU1718398A1 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Резервированная вычислительная система | 1989 |

|

SU1798946A1 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Резервированная система | 1982 |

|

SU1084802A1 |

| Устройство для управления резервированной вычислительной системой | 1989 |

|

SU1755399A1 |

| Устройство для управления реконфигурацией резервированного вычислительного комплекса | 1983 |

|

SU1149449A1 |

| Устройство для централизованного управления вычислительной системой | 1985 |

|

SU1259261A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

Использование: в отказоустойчивых многопроцессорных вычислительных системах для обеспечения перекрестной коммутации резервируемых узлов. Сущность изобретения: система содержит 1 группу резервируемых процессоров (1). 1 группу коммутаторов ввода-вывода (2), 1 группу модулей памяти (3), 1 блок управления резервированием (4), 1 группу шинных формирователей (7), 1 коммутатор сравнения (5), 1 блок сравнения (6); блок управления резервированием (4) содержит 1 группу выходов управления коммутацией (8), 1 группу выходов состояния процессоров (9), 1 выход строба (10), 1 выход адреса сравнения (11), 1 выход синхронизации (12). 1 выход готовности (13), 1 группу входов готовности (14), 1 вход сравнения (15). 8-2-7- 5-6-15, 10-1-14, 1-2-3. 1-7, 9-7, 12-6, 11-5. 1 з.п.ф-лы, 2 табл. ь Ё

35

Таблицз2

v

f

s

Ljr

№:)

)

;

tf

.iu/ f

« j

3J«3

,Г IJL I e

Т /У 1 ---

ТШ / /Ытff Of

47

У5

tt

«

Фиг. 3

/s

56

58

16

57

го

Риг. А

Фиг 5 (лист /У

сри&5 (па cm 2)

T)-i-uu МОП ; /l -t-tiun 0itescoi - нео5ея емий Wfyjfj - неиеамвни /rr&teeeat.

-КОММУТ

О

Фиг. б

Q -О

а)

As, A

S) ФиГ. 7

1}

-КОММУТАТОР e&fsfn

9

6)

г)

| Авторское свидетельство СССР № 1492973,кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1494763, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1579443, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-08-15—Публикация

1990-06-12—Подача