Изобретение относится к вычислительной технике и может быть использовано для сопряжения вычислительных модулей (электронных вычислительных машин) в многомашинных вычислительных комплексах, информационно - измерительных, автоматизированных системах управления.

Известно устройство RDMA - адаптер [1], разработанное под управлением RDMA Consortium, куда входят многие гранды индустрии, такие как IBM, Cisco, NetApp, EMC, HP, Intel, Microsoft, общим числом около 50.

Использование сетевых адаптеров RDMA основано на реализации функции SMB Multichannel, которая является частью сетевого протокола SMB3.0. SMB Multichannel отвечает за обнаружение поддержки RDMA сетевого адаптера.

При построении систем управления применение технологии RDMA базируется на использовании высокоскоростной коммутируемой последовательной шины Infmiband, применяющейся как для внутренних (внутрисистемных), так и для межсистемных соединений.

Очевидно, что использование технологии RDMA Consortium для построения систем управления требует создания сетевых структур и соответственно дополнительных временных издержек на реализацию TCP/IP - протоколов для организации каналов и режима работы RDMA.

Известно устройство RapidIO (SRIO) [2] - интерфейс «быстрого ввода-вывода», содержащий блок DMA, блок сообщений, регистр конфигурации, блок адаптера - SerDes - преобразователь параллельного кода в последовательный и обратно.

Недостатком указанного устройства является то, что организация обмена данными посредством дуплексного звена SRIO не позволяет реализовать метод конвейерной передачи, что определено организацией логического уровня интерфейса SRIO. Кроме того, применение устройства SRIO требует создания сетевых структур и соответственно дополнительных временных издержек на реализацию сетевых протоколов.

Наиболее близким к предлагаемому, по технической сущности, является устройство [3] для сопряжения ЭВМ с магистралью, содержащее селектор адреса, регистр состояния, формирователь сигнала занятости магистрали, блок прерывания, группу регистров адресов, регистр передаваемого массива, регистр режима работы, блок формирователя интерфейсных сигналов, два триггера, два регистра приема, два регистра передачи, два блока магистральных передатчиков, блок дешифрации адресов, элементы И, ИЛИ.

Целью изобретения является расширение функциональных возможностей, а именно, - применение межмашинного прямого доступа к памяти при построение больших распределенных вычислительных систем, в которых вычислительные устройства расположены на значительном расстояние друг от друга; повышение производительности вычислительных систем за счет сокращения времени информационного обмена между вычислительными устройствами систем; повышение информационно-функциональной безопасности вычислительных систем.

Поставленная цель достигается тем, что в устройство содержащее селектор адреса, регистр состояния, блок магистральных приемопередатчиков, регистры адресов, регистр массива, регистр режима, регистры приема, регистры передачи, соединенные с внутренней магистралью вычислительного модуля, выходы регистра режима, входы блока дешифратора режима работы, входы - выходы магистральных приемопередатчиков, регистры приема, регистры передачи соединены с внутренним каналом устройства, выходы селектора адреса соединены с регистрами адреса, регистром массива, регистром режима, магистральными приемопередатчиками, регистром состояния, формирователем сигнала занятости устройства, блок прерывания соединен с внутренней магистралью вычислительного модуля, с входами регистра состояния, с выходом формирователя интерфейсных сигналов, с внутренним каналом устройства, выход триггера требования прямого доступа и выход триггера подтверждения выбора соединены с внутренней магистралью вычислительного модуля, вход триггера требования прямого доступа соединен с выходом первого элементом ИЛИ первый вход, которого соединен с выходом регистра режима, а второй вход с выходом дешифратора режима работы, второй вход триггера требования прямого доступа соединен с выходом триггера подтверждения выбора, первый вход, которого соединен с внутренней магистралью вычислительного модуля, а второй вход соединен с выходом второго элемента ИЛИ, первый вход, которого соединен с выходом блока прерывания, второй вход второго элемента ИЛИ соединен с выходом второго элемента И, входы которого соединены с соответствующими выходами формирователя интерфейсных сигналов и регистра счетчика массива, первый вход первого элемента И соединен с выходом триггера подтверждение выбора, выход третьего элемента И соединен с внутренним каналом устройства, первый вход третьего элемента И соединен с выходом дешифратора режима работы, второй вход третьего элемента И соединен с магистралью вычислительного модуля, выход третьего элемента И соединен с внутренним каналом устройства, введены:

коммутатор высокоскоростных каналов передачи информации (КВКПИ), группа двухвходовых элементов ИЛИ, один многовходовой элемент ИЛИ, группа выходных магистральных приемопередатчиков, группа входных магистральных приемопередатчиков, группа высокоскоростных каналов передачи информации (ВКПИ), регистр команд, причем информационные входы выходных магистральных приемопередатчиков соединены с внутренним каналом устройства, информационные выходы выходных приемопередатчиков соединены с входами высокоскоростного канала передачи информации, информационные выходы высокоскоростного канала передачи информации соединены с информационными входами входных магистральных приемопередатчиков, информационные выходы которых соединены с внутренним каналом устройства, управляющие выходы коммутатора высокоскоростных каналов передачи информации соединены с первыми входами группы двухвходовых элементов ИЛИ, вторые входы группы двухвходовых элементов ИЛИ соединены с соответствующими выходами дешифратора режима работы устройства, входы многовходового элемента ИЛИ соединены с соответствующими выходами подтверждения выбора абонента входных магистральных приемопередатчиков, входы подтверждения выбора абонента входных магистральных приемопередатчиков соединены с соответствующими выходами высокоскоростных каналов передачи информации, выход занятости устройства объединен по монтажному ИЛИ с выходом занятости абонента и соединен с соответствующими входами высокоскоростных каналов передачи информации, информационные входы регистра команд соединены с соответствующими выходами блока дешифратора режима, управляющий выход которого соединен с соответствующим входом блока прерывания и стробирующим входом регистра команд, вход управления регистра команд соединен с соответствующим выходом селектора адреса, информационные выходы регистра команд соединены с информационными шинами магистрали вычислительного модуля. Выход ППД - предоставление прямого доступа регистра команд объединен по монтажному ИЛИ с соответствующей шиной внутренней магистрали вычислительного устройства.

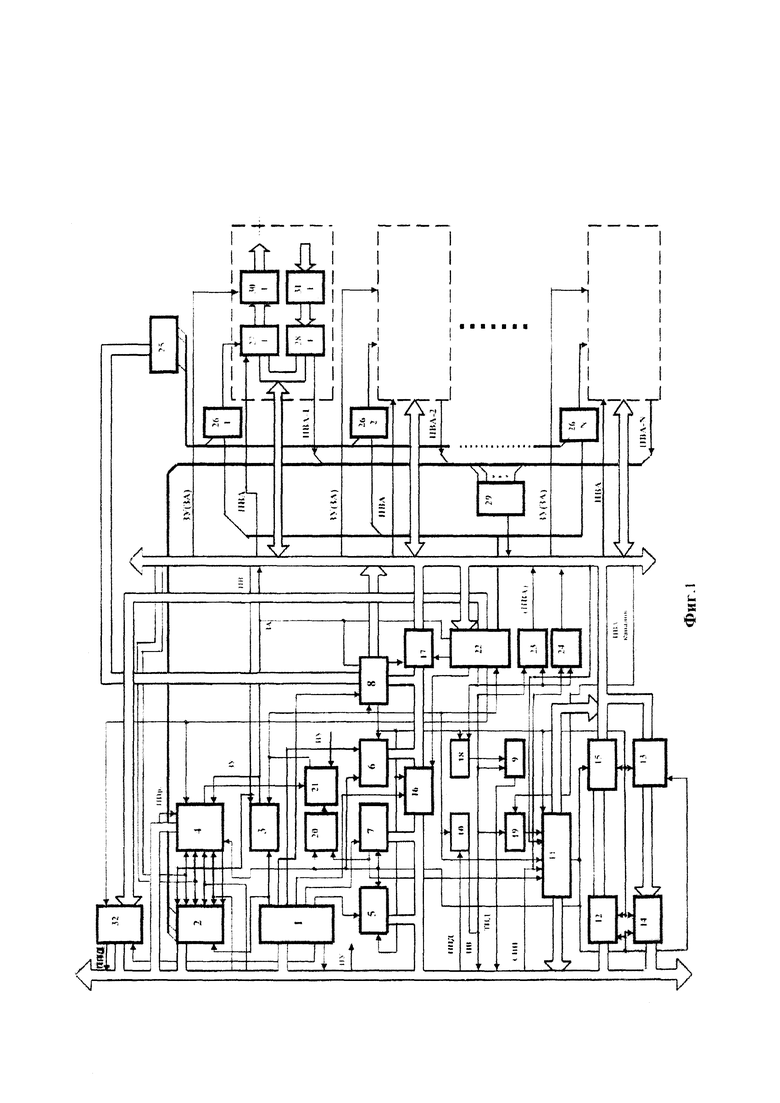

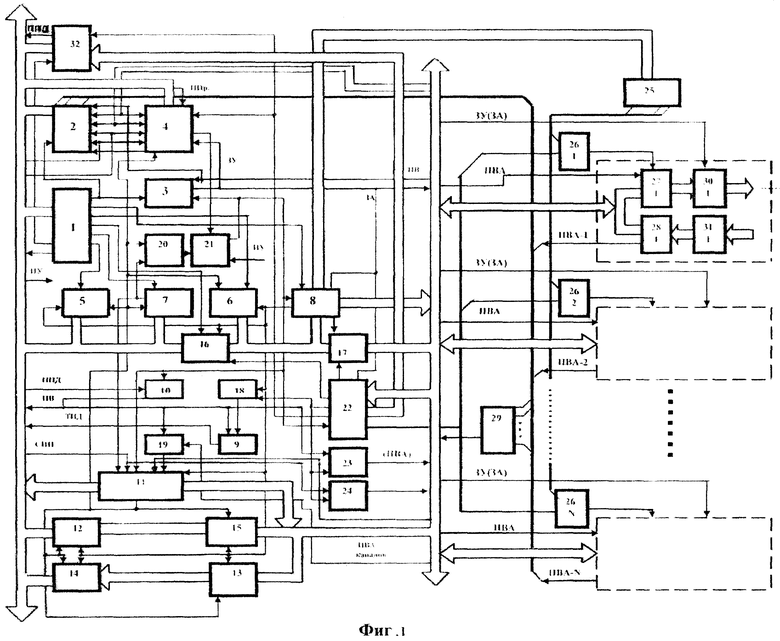

1. На фиг.1 представлена блок - схема устройства;

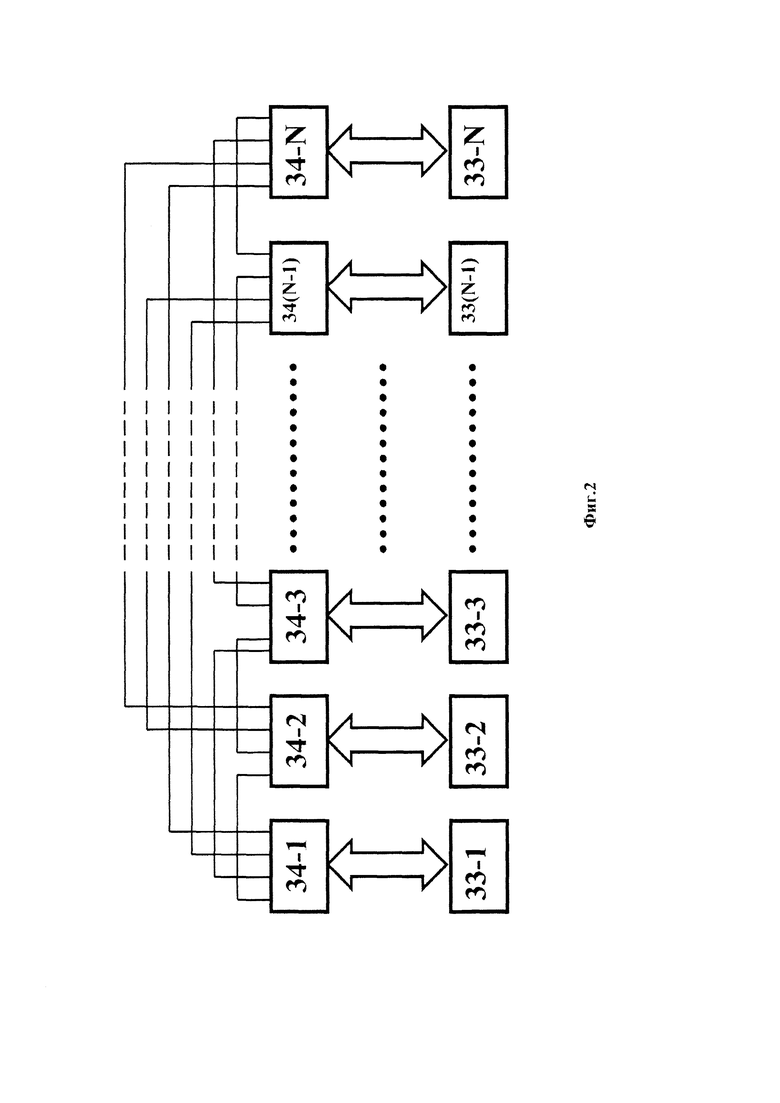

2. На фиг.2 представлена структурная схема вычислительной системы, использующей предлагаемое устройство. На фиг.2. представлены: (33-1) - (33-N) - вычислительные устройства; (34-1) - (34-N) - предлагаемое устройство, структура которого представлена на фиг.1.

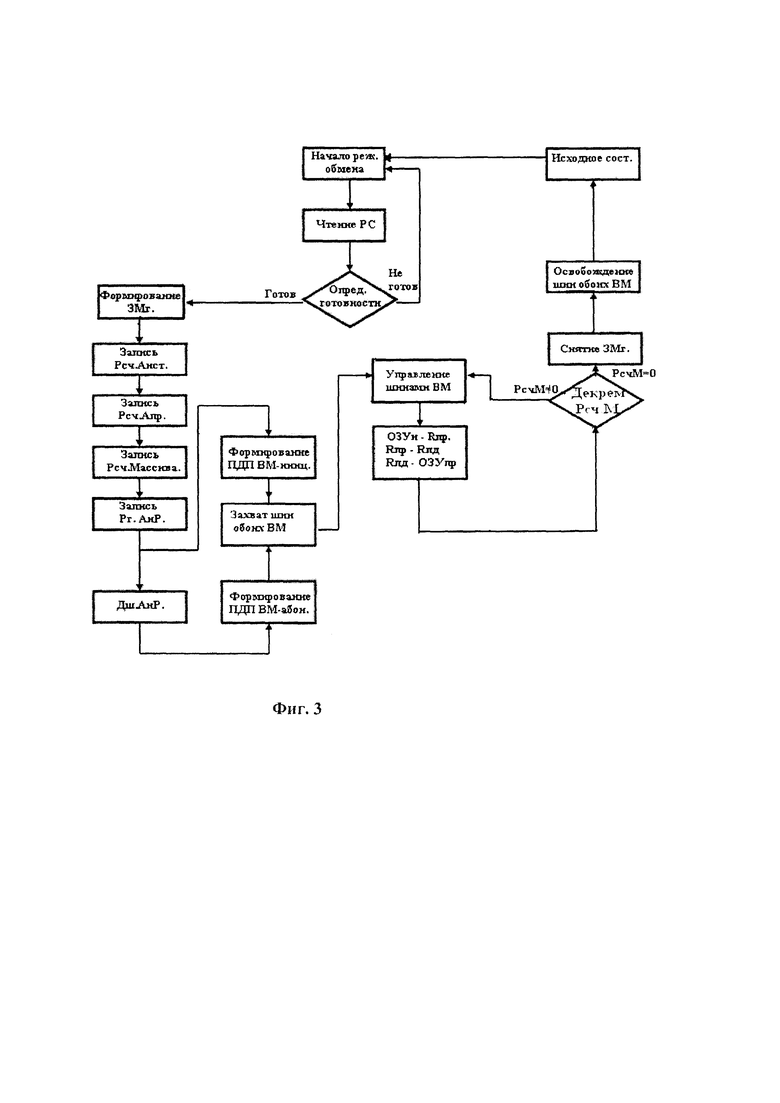

3. На фиг.3 представлен алгоритм работы предлагаемого устройства.

Устройство содержит селектор 1 адреса, адресные входы которого подключены к информационным шинам магистрали ВМ. Выходы селектора 1 адреса подключены к входу регистра 2 состояния, к управляющему входу блока 3 формирования сигнала занятости устройства, к входам управления регистров 5, 6 адресов, к входу управления регистра 7 массива, к входу управления регистра 8 режима и адреса канала, к входу управления регистра 32 команд. Информационные выходы регистра 2 состояния подключены к информационным шинам магистрали ВМ. Информационные входы регистра 2 состояния подключены к соответствующим входам блока 4 прерывания, к выходам «подтверждения выбора абонента» группы входных (28-1) - (28-N) приемопередатчиков, управляющий вход регистра 2 состояния подключен к соответствующему выходу блока 4 прерывания. Информационные входы блока 4 прерывания подключены к соответствующим информационным шинам магистрали ВМ и канала устройства, к управляющему выходу дешифратора 22 режима и управляющему входу регистра 32 команд. Информационные и управляющие выходы блока 4 прерывания соединены с соответствующими шинами магистрали ВМ. Выход блока 3 формирователя сигнала «занятости устройства» соединен с информационными входами передающих высокоскоростных каналов (30-1) - (30-N) передачи информации. Информационный вход блока 3 формирователя сигнала «занятости устройства» соединен с выходом элемента И 23, первый вход которого соединен с первым выходом дешифратора 22 режима, второй вход элемента И 23 соединен с выходом триггера 10 «подтверждение выбора», выход триггера 10 также соединен с соответствующей шиной магистрали ВМ. На первый вход триггера 10. из магистрали ВМ поступает сигнал «предоставление прямого доступа», на второй вход триггера 10 поступает сигнал начальной установки с выхода элемента ИЛИ 21. Первый вход элемента ИЛИ 21 соединен с выходом блока 4 прерывания, второй вход элемента ИЛИ 21 соединен с выходом элемента И 20, первый вход которого соединен с входом блока 4 прерывания, входом регистра 6 адреса и выходом блока 11 формирователя интерфейсных сигналов. Второй вход элемента И 20 соединен с выходом регистра 7 массива и входом блока 11 формирователя интерфейсных сигналов. Выход элемента ИЛИ 21 соединен с входом начальной установки регистра 8 режима и адреса канала и дешифратора 22 режима. Тактовые входы регистров 5, 6 адресов, регистра 7 массива соединены с соответствующими выходами блока 11 формирователя интерфейсных сигналов. Управляющие выходы регистра 8 режима соединены с соответствующими входами регистра 6 адресов и блока 17 магистральных приемопередатчиков, регистра 5 адресов, приемопередающих 12, 13, 14, 15 регистров и первым входом элемента ИЛИ 18. Второй вход элемента ИЛИ 18 соединен с соответствующим выходом дешифратора 22 режима. Управляющий выход дешифратора 22 режима соединен с входом блока 16 магистральных приемопередатчиков. Выход элемента ИЛИ 18 соединен с входом триггера 9 формирователя сигнала «требование прямого доступа». Выход триггера 9 соединен с шиной требования прямого доступа магистрали ВМ. Первый вход элемента И 19 соединен с выходом триггера 10 формирователя сигнала «подтверждение выбора» для ВМ. Второй вход элемента И 19 соединен с выходом многовходового элемента ИЛИ 29, входы которого соединены с выходами группы входных (28-1) - (28-N) магистральных приемопередатчиков - «подтверждение выбора абонента». Выход элемента И 23 «подтверждение выбора абонента» соединен с соответствующими входами группы выходных (27-1) - (27-N) приемопередатчиков. Выход элемента И 19 соединен с запускающим входом блока 11 формирователя интерфейсных сигналов, выходы которого соединены с соответствующими шинами магистрали ВМ, соответствующими входами группы выходных (27-1) - (27-N) приемопередатчиков. Коммутирующие выходы блока 11 формирователя интерфейсных сигналов соединены с входами управления приемопередающих 12, 13, 14, 15 регистров. Информационные выходы регистров 15 передачи соединены с входами группы выходных (27-1) - (27-N) приемопередатчиков. Информационные выходы регистров 14 передачи соединены с соответствующими шинами магистрали ВМ. Информационные входы регистров 12 приемников соединены с соответствующими шинами магистрали ВМ. Информационные входы регистров 13 приемников соединены с соответствующими выходами группы входных (28-1) - (28-N) приемопередатчиков. Информационные входы-выходы регистра 5 адреса, регистра 7 массива и блока 16 магистральных приемопередатчиков соединены с информационным шинам магистрали ВМ. Информационные входы-выходы регистра 6 адреса, регистра 8 режима и адреса высокоскоростного канала передачи информации соединены с информационными входами-выходами магистральных 16, 17 приемопередатчиков. Информационные выходы регистра 8 режима и адреса высокоскоростного канала передачи информации соединены с информационными входами коммутатора 25 высокоскоростных каналов передачи информации и информационными входами группы выходных (27-1) - (27-N) приемопередатчиков. Информационные выходы группы выходных (27-1) - (27-N) приемопередатчиков соединены с входами группы передающих высокоскоростных (30-1) - (30-N) каналов передачи информации. Информационные выходы группы приемных высокоскоростных (31-1) - (31-N) каналов передачи информации соединены с информационными входами группы входных (28-1) - (28-N) магистральных приемопередатчиков, информационные выходы которых соединены с информационными шинами канала устройства. Управляющие выходы коммутатора 25 высокоскоростных каналов передачи информации соединены с соответствующими входами группы двухвходовых элементов ИЛИ (26-1) - (26-N), выходы которых соединены с соответствующими управляющими входами группы выходных (27-1) - (27-N) приемопередатчиков. Вторые входы двухвходовых элементов ИЛИ (26-1) - (26-N) соединены с соответствующими выходами дешифратора 22 режима, информационные входы которого соединены с информационными выходами группы входных (28-1) - (28-N) магистральных приемопередатчиков. Информационные выходов дешифратора 22 режима соединены с информационными входами регистра 32 команд, информационные выходы которого соединены с соответствующими шинами магистрали вычислительного модуля. Выход ППД - предоставление прямого доступа регистра 32 команд объединен по монтажному ИЛИ с соответствующей шиной магистрали вычислительного модуля.

Устройство работает следующим образом.

В соответствии с программой один из вычислительных модулей (ВМ), входящих в комплекс, определяет момент времени, когда необходимо передать информацию. Передача информации между ВМ осуществляется в два этапа: организация канала передачи информации между ВМ - источником и ВМ -приемником и непосредственно передача информационного массива.

Работа начинается с опроса регистра 2 состояния для определения готовности устройства к работе. При обращении к устройству, ВМ, инициализирующий режим работы, выставляет в магистраль адрес устройства. При совпадении адреса с кодом селектора 1 адреса регистр 2 состояния, по сигналу селектора 1 адреса, выставляет на шины данных магистрали ВМ свое содержимое. ВМ определяет готовность устройства к работе. Тот же сигнал, с выхода селектора 1 адреса, поступает на вход блока 3 формирования сигнала занятости устройства (ЗУ). Если, к этому моменту времени, ни одно из аналогичных устройств, других, входящих в вычислительный комплекс ВМ, не сформировало сигнал ЗУ, то формирователь 3 сигнала занятости устройства, на своем выходе, сформирует сигнал ЗУ, который поступает на соответствующие информационные входы группы передающих высокоскоростных каналов (30-1) - (30-N) передачи информации, выходы которых соединены с каналами аналогичных устройств всех, входящих в комплекс, ВМ и тем самым, сигнал ЗУ, устройства ВМ - инициализирующего режим обмена, поступает на соответствующие входы регистров 2 состояния всех устройств вычислительного комплекса, информируя их о занятости устройства ВМ - инициализирующего режим обмена. Таким образом, все, входящие в комплекс ВМ, будут информированы об активировании данным устройством режима обмена информацией.

Последующими обращениями к устройству ВМ запишет в регистры 5 и 6 адресов информацию о начальных адресах ОЗУ - источника и ОЗУ - приемника информации, а также в регистр 7 массива - информацию о величине передаваемого массива информации. В регистр 8 режима записывается информация о режиме работы (прием или передача), код адреса абонента, а также код команды и «бит» - требования прерывания. Запись информации в регистр 8 режима осуществляется по совокупности сигнала ЗУ и сигнала от селектора 1 адреса. По сигналу с выхода регистра 8 режима, поступающему на элемент ИЛИ 18, срабатывает триггер 9 формирователь сигнала «требование прямого доступа» (ТПД), который поступает в магистраль ВМ, инициализирующего обмен. ВМ выставляет ответный сигнал - «предоставление прямого доступа» (ПДП), поступающий в устройство на синхровход триггера 10 - формирователя сигнала «подтверждение выбора» (ПВ). Сигнал ПВ поступает в ВМ и блокирует его процессор, а также устанавливает триггер 9 в исходное состояние, снимая, тем самым, сигнал ТПД. Кроме того, сигнал ПВ поступает на один из входов элемента И 19 и элемента И 23.

Код адреса абонента с выхода регистра 8 режима поступает на коммутатор 25 высокоскоростных каналов передачи информации (КВКПИ). Сигналом с выхода коммутатора 25, к внутреннему каналу устройства, подключается один из выходных магистральных приемопередатчиков группы выходных (27-1) - (27-N) приемопередатчиков. В исходном состоянии все выходные магистральные приемопередатчики закрыты, все входные приемопередатчики открыты.

Код режима работы и адрес абонента, записанный в регистре 8 режима, через соответствующий, подключенный к выходам выходного магистрального приемопередатчика, передающий высокоскоростной 30 канал передачи информации (ВКПИ), поступает на вход дешифратора 22 режима работы аналогичного устройства абонента. В устройстве абонента с выхода дешифратора 22 режима работы, управляющие сигналы поступают на входы управления блоков 16 и 17 магистральных приемопередатчиков, на один из входов элемента ИЛИ 18 и элементов И 23 и И 24, а также на вход одного из элементов ИЛИ группы двухвходовых элементов ИЛИ (26-1) - (26-N), с выхода которого разрешающий сигнал поступает на вход управления выходного 27 магистрального передатчика соответствующего канала абонента, тем самым подключая к шине абонента передающий 30 ВКПИ. Сигнал «занятость абонента» (ЗА), формируемый в дешифраторе 22 режима работы устройства абонента также, как и сигал ЗУ поступает на соответствующие информационные входы группы передающих высокоскоростных каналов (30-1) - (30-N) передачи информации, выходы которых соединены с каналами аналогичных устройств всех, входящих в комплекс, ВМ и тем самым, сигнал ЗА, устройства абонента поступает на соответствующие входы регистров 2 состояния всех устройств вычислительного комплекса, информируя их о занятости устройства абонента ВМ - абонента. Таким образом, все, входящие в комплекс ВМ, будут информированы об активировании режима обмена информацией между ВМ, инициализирующим обмен и ВМ - абонентом.

По сигналу с выхода элемента ИЛИ 18 так же, как и в устройстве ВМ, инициализирующего режим обмена, срабатывают триггеры 9 и 10, и процессор ВМ - абонента блокируется по прямому доступу к памяти.

Сигнал ПВ (подтверждение выбора) ВМ - абонента через элемент И 23 поступает через выходные магистральные приемопередатчики в подключенный передающий 30 ВКПИ. Магистральные передатчики 16 и 17 устройства абонента, включаются на передачу информации в направлении, определяемом соответствующими разрядами дешифратора 22 режима работы устройства абонента. Таким образом, устройство абонента подсоединяет канал ВМ -абонента через ВКПИ к внутренней магистрали устройства ВМ, инициализирующего режим обмена. Соответственно сигнал ПВ устройства абонента через ВКПИ поступает на второй вход элемента И 19 устройства ВМ, инициализирующего режим обмена. С выхода элемента И 19 устройства сигнал поступает на включение блок 11 формирования интерфейсных сигналов. Блок 11 формирует интерфейсные сигналы циклов «ввод» и «вывод» для каналов обоих ВМ и, тем самым, осуществляет передачу массива информации из ОЗУ -источника в ОЗУ - приемник таким образом, что в каждом цикле производится прием слова данных из ОЗУ - источника в регистр - приемник [Рг.пр. 12(13)] устройства и одновременно с этим, передача, ранее принятого слова данных, из регистра - передатчика [Рг.пер.14(15)] устройства в ОЗУ - приемник. По окончании каждого цикла приемо - передачи слово данных, принятое в регистр -приемник, переписывается в регистр - передатчик. Далее цикл приемо - передачи повторяется. Таким образом, реализуется режим последовательно - параллельной (конвейерной) передачи массива данных из ОЗУ ВМ - источника в ОЗУ ВМ -приемника данных (передача информации в рассматриваемом устройстве полностью аналогична режиму передач в прототипе).

По окончании режима передачи информации, сигнал с выхода регистра 7 массива поступает на один из входов элемента И 20. На второй вход элемента И 20 поступает сигнал с блока 11 формирователя интерфейсных сигналов. Сигнал с выхода элемента И 20 поступает на вход элемента ИЛИ 21 и с его выхода воспринимается устройством, как сигнал начальной установки. Снимается сигнал ПВ устройства и ВМ, инициализирующий режим обмена, переходит к дальнейшему выполнению программы. В момент снятия сигнала ЗУ в блоке 4 прерывания устройства ВМ - абонента формируется сигнал, который через элемент ИЛИ 21 воспринимается устройством ВМ - абонента, как сигнал начальной установки. В устройстве абонента снимается сигнал ПВ, ВМ - абонента разблокируется и переходит к дальнейшему выполнению программы.

Применение предлагаемого устройства позволяет реализовать режим передачи команд между ВМ системы. Для этого ВМ, инициализирующий режим работы, записывает в соответствующую область регистра 8 режима код команды и «бит» -требования прерывания». Активирование в регистре 8 режима «бита» - требования прерывания (ТПР) отменяет процедуру организации режима ПДП. Так как шина регистра 8 режима - «бит» - ТПР объединена, по монтажному ИЛИ, с выходом блока 3 формирования сигнала ЗУ, все ВМ системы будут извещены о занятости устройства. Далее код команды и «бит» - ТПР, через передающий высокоскоростной канал 30 передачи информации поступает на вход дешифратора 22 режима устройства ВМ - абонента. В устройстве абонента также отменяется процедура организации режима ПДП. Управляющий сигнал с выхода дешифратора 22 режима поступает на вход регистра 32 команд и на вход блока 4 прерывания. В регистр 32 команд записывается код команды, а блок 4 прерывания активирует режим прерывания программы ВМ - абонента. ВМ - абонента переходит на подпрограмму обслуживания прерывания, читает содержимое регистра 32 команд и переходит к выполнению команды. Рассмотренный командный режим работы абонента позволяет реализовать контроль работоспособности вычислительных модулей, входящих в систему.

В случае выявления неисправности ВМ - абонента, ВМ, инициализирующий режим обмена, записывает в регистр 8 режима «бит» ППД - предоставление прямого доступа абонента, который транслируется через дешифратор 22 режима абонента в регистр 32 команд абонента и далее во внутреннюю магистраль, отказавшего ВМ - абонента. Таким образом, реализуется режим обмена данными с памятью отказавшего ВМ - абонента при условии целостности внутренней магистрали ВМ - абонента.

Применение предлагаемого устройства для организации информационного обмена в многомашинных вычислительных комплексах позволяет организовать одновременный информационный обмен между парами вычислительных модулей, что повышает общую производительность вычислительного системы.

Список литературы

1. Удаленный прямой доступ к памяти [Электронный ресурс] // Компьютерное Обозрение. URL: http://ko.com.ua/ (19. 03.2013).

2. Н. Слепов., RapidIO - коммутационная структура последовательного типа. [Электронный ресурс] // http://www.electronics.ru/iournal/article/760

3. ПАТЕНТ №1605242. G06F 13/00, 1990 г., - "Устройство для сопряжения ЭВМ с магистралью."

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1605242A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1462341A1 |

| УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ АБОНЕНТОВ К ОБЩЕМУ РЕСУРСУ | 1991 |

|

RU2017205C1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Резервированная вычислительная система | 1989 |

|

SU1798946A1 |

| Устройство для подключения абонентов к магистрали ЭВМ | 1988 |

|

SU1608681A1 |

| Устройство для подключения абонентов к общей магистрали | 1991 |

|

SU1820382A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения вычислительной машины с общей магистралью | 1986 |

|

SU1354199A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1990 |

|

SU1734099A1 |

Изобретение относится к многоканальному устройству межмашинного прямого доступа к памяти. Технический результат заключается в обеспечении межмашинного прямого доступа к памяти при построении больших распределенных вычислительных систем. Устройство содержит селектор адреса, регистр состояния, блок прерывания, блок формирования сигнала занятости устройства, два регистра счетчика адресов, регистр счетчик массива, регистр режима и адреса абонента, два блока магистральных приемопередатчиков, блок формирования интерфейсных сигналов, два регистра приемника, два регистра передатчика, блок прерывания, информационные и управляющие шины магистрали вычислительного модуля (ВМ) и внутреннего канала устройства, элементы ИЛИ, элементы И, а также коммутатор высокоскоростных каналов приемопередачи информации, группа двухвходовых элементов ИЛИ, один многовходовой элемент ИЛИ, группа выходных магистральных приемопередатчиков, группа входных магистральных приемопередатчиков, группа передающих высокоскоростных каналов передачи информации, группа приемных высокоскоростных каналов передачи информации, регистр команд. 3 ил.

Многоканальное устройство межмашинного прямого доступа к памяти, содержащее селектор адреса, регистр состояния, блок прерывания, блок формирования сигнала занятости устройства, два регистра счетчика адресов, регистр счетчика массива, регистр режима и адреса абонента, два блока магистральных приемопередатчиков, блок формирования интерфейсных сигналов, два регистра приемника, два регистра передатчика, причем информационные и синхронизирующие входы первого и второго регистров приемников являются соответственно входами устройства для подключения к информационным и управляющим шинам магистрали вычислительного модуля (ВМ) и внутреннего канала устройства, информационные выходы первого и второго регистров приемников соединены соответственно с информационными входами второго и первого регистров передатчиков, выходы которых являются соответственно с выходами устройства для подключения к информационным шинам магистрали ВМ и внутреннего канала устройства, первый вход первого элемента ИЛИ является входом устройства для подключения к шине начальной установки ВМ, второй вход первого элемента ИЛИ соединен с выходом сигнала начальной установки блока прерывания, третий вход первого элемента ИЛИ соединен с выходом первого элемента И, первый вход которого соединен с входом пуска блока прерывания, первые группы информационных входов-выходов первого и второго блоков магистральных приемопередатчиков являются соответственно входами-выходами устройства для подключения к информационным шинам ВМ и канала устройства, первый выход селектора адреса соединен с первым управляющим входом первого блока магистральных приемопередатчиков, вторая группа информационных входов-выходов первого блока магистральных приемопередатчиков соединена со второй группой информационных входов-выходов второго блока магистральных приемопередатчиков, информационные выходы регистра состояния являются выходами устройства для подсоединения к информационным шинам ВМ, первый и второй информационные входы регистра состояния и блока прерывания соответственно объединены и являются входами устройства для подсоединения к шинам сигналов подтверждения выбора и ответа канала устройства, третий и четвертый информационные входы регистра состояния и блока прерывания соответственно объединены и являются входами устройства для подсоединения к шинам подтверждения выбора и ответа ВМ, стробирующий выход блока прерывания соединен со стробирующим входом регистра состояния, вход синхронизации которого соединен со вторым выходом селектора адреса, группа входов которого является группой входов устройства для подсоединения к информационным шинам ВМ, третий выход селектора адреса является выходом устройства для подсоединения к шине ответа ВМ, группа информационных входов-выходов блока прерывания является группой входов-выходов устройства для организации режима прерывания программы ВМ, стробирующий выход блока формирования интерфейсных сигналов соединен с соответствующими входами первого и второго регистров передатчиков, синхровходами первого и второго регистров адресов, регистра массива и первым входом первого элемента И, первая и вторая группы магистральных выходов блока формирования интерфейсных сигналов являются соответственно группами выходов устройства для подключения к группе управляющих шин ВМ и группе управляющих шин канала устройства, первый вход блока формирования интерфейсных сигналов соединен с первым входом четвертого элемента И и является входом устройства для подсоединения к шине ответа ВМ, второй вход блока формирования интерфейсных сигналов является входом устройства для подсоединения к шине ответа канала устройства, выход первого элемента ИЛИ соединен с входом начальной установки блока формирования сигнала занятости устройства, регистра режима работы, блока дешифрации адресов, триггера подтверждения выбора и третьим входом блока формирования интерфейсных сигналов, информационные входы регистра массива совместно с информационными входами-выходами первого регистра адреса соединены с соответствующими входами-выходами первого блока магистральных приемопередатчиков, первый информационный выход регистра режима соединен с управляющими входами первого и второго регистров адресов, вторым управляющим входом первого блока магистральных приемопередатчиков, первым входом второго элемента ИЛИ, четвертым управляющим входом блока формирования интерфейсных сигналов и с входами режима регистров передатчиков и регистров приемников, пятый вход блока формирования интерфейсных сигналов соединен с выходом второго элемента И, первый вход которого является входом устройства для подсоединения к шине подтверждения выбора канала устройства, второй вход второго элемента И соединен с первым входом третьего элемента И, с входом сброса триггера требования прямого доступа, с выходом триггера подтверждения выбора и является выходом устройства для подсоединения к шине подтверждения выбора ВМ, информационный выход регистра массива соединен со вторым входом первого элемента И и с шестым входом управления блока формирования интерфейсных сигналов, выход триггера требования прямого доступа соединен с входом начальной установки триггера подтверждения выбора и является выходом устройства для подсоединения к шине требования прямого доступа ВМ, вход синхронизации триггера требования прямого доступа соединен с выходом второго элемента ИЛИ, второй вход которого соединен с вторым выходом блока дешифратора адреса и режима работы и вторыми входами третьего и четвертого элементов И, вход синхронизации триггера подтверждения выбора является входом устройства для подсоединения к шине предоставления прямого доступа ВМ, группа информационных входов-выходов второго регистра адреса совместно с группой информационных входов регистра режима соединена со второй группой магистральных входов-выходов первого блока магистральных приемопередатчиков, четвертый, пятый и шестой выходы селектора адреса соединены соответственно с управляющими входами первого и второго регистров адреса и регистра массива, второй выход селектора адреса соединен с входом пуска формирователя сигнала занятости устройства, выход которого является выходом устройства для подсоединения к шине занятости устройства, выход формирователя сигнала занятости устройства соединен с входом разрешения блока прерывания и вторым управляющим входом регистра режима, седьмой выход селектора адреса соединен со стробирующим входом регистра режима, вход управления которого соединен со вторым информационным входом регистра состояния, группа информационных выходов регистра режима является группой выходов для подсоединения к информационным шинам канала устройства, третий информационный выход регистра режима подсоединен к первому управляющему входу второго блока магистральных приемопередатчиков, второй управляющий вход которого соединен с третьим выходом блока дешифратора режима, первый выход которого подсоединен к третьему управляющему входу первого блока магистральных приемопередатчиков, адресные входы блока дешифратора режима являются входами устройства для подсоединения к информационным шинам канала устройств, выход требования прерывания регистра режима объединен по монтажному ИЛИ с выходом блока формирователя сигнала занятости устройства, выход третьего элемента И является выходом устройства для подсоединения к шине подтверждения выбора абонента, выход четвертого элемента И является выходом устройства для подсоединения к шине «ответ» канала устройства,

отличающееся тем, что с целью расширения функциональных возможностей, а именно применения межмашинного прямого доступа к памяти при построении больших распределенных вычислительных систем, в которых вычислительные устройства расположены на значительном расстоянии друг от друга, введены:

коммутатор высокоскоростных каналов приемопередачи информации, группа двухвходовых элементов ИЛИ, один многовходовой элемент ИЛИ, группа выходных магистральных приемопередатчиков, группа входных магистральных приемопередатчиков, группа передающих высокоскоростных каналов передачи информации, группа приемных высокоскоростных каналов передачи информации, регистр команд, причем информационные входы выходных магистральных приемопередатчиков соединены с информационными шинами внутреннего канала устройства, информационные выходы выходных приемопередатчиков соединены с входами соответствующих передающих высокоскоростных каналов передачи информации, информационные выходы группы приемных высокоскоростных каналов передачи информации соединены с информационными входами соответствующих входных магистральных приемопередатчиков, информационные выходы которых соединены с информационными шинами внутреннего канала устройства, управляющие выходы коммутатора высокоскоростных каналов приемопередачи информации соединены с первыми входами группы двухвходовых элементов ИЛИ, вторые входы которых соединены с соответствующими выходами дешифратора режима работы устройства, выходы двухвходовых элементов ИЛИ соединены с управляющими входами соответствующих выходных приемопередатчиков, информационные входы коммутатора высокоскоростных каналов приемопередачи информации соединены с соответствующими выходами регистра режима устройства, входы многовходового элемента ИЛИ соединены с соответствующими выходами подтверждения выбора абонента входных магистральных приемопередатчиков, входы подтверждения выбора абонента входных магистральных приемопередатчиков соединены с соответствующими выходами приемных высокоскоростных каналов передачи информации, выходы подтверждения выбора абонента входных магистральных приемопередатчиков соединены с соответствующими информационными входами регистра состояния устройства, выход многовходового элемента ИЛИ соединен с входом второго элемента И устройства, выход блока формирования сигнала занятости устройства объединен по монтажному ИЛИ с выходом занятости абонента дешифратора режима работы и соединен с соответствующими информационными входами передающих высокоскоростных каналов передачи информации, информационные входы регистра команд соединены с соответствующими выходами блока дешифратора режима, управляющий выход которого соединен с соответствующим входом блока прерывания и стробирующим входом регистра команд, вход управления регистра команд соединен с соответствующим выходом селектора адреса, информационные выходы регистра команд соединены с информационными шинами магистрали вычислительного устройства, выход ППД - предоставление прямого доступа регистра команд объединен по монтажному ИЛИ с соответствующей шиной магистрали вычислительного модуля, информационные входы выходных магистральных приемопередатчиков, информационные выходы входных магистральных приемопередатчиков, информационные входы дешифратора режима работы, информационные выходы регистра режима работы соединены с соответствующими шинами канала устройства.

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1605242A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРА С ПАМЯТЬЮ | 1991 |

|

RU2018941C1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Устройство для управления подключением к магистрали общего блока памяти | 1980 |

|

SU934834A1 |

| Устройство для обслуживания запросов и памяти прямого доступа | 1984 |

|

SU1188738A1 |

| Контроллер прямого доступа к памяти | 1991 |

|

SU1789987A1 |

| Электронная вычислительная машина с прямым доступом в память | 1990 |

|

SU1751776A1 |

| US 5634099 A1, 27.05.1997 | |||

| CN 102231142 A, 02.11.2011. | |||

Авторы

Даты

2022-07-06—Публикация

2021-03-30—Подача