сл с

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированная вычислительная система | 1989 |

|

SU1798946A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Резервированное процессорное устройство | 1987 |

|

SU1594545A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для управления обменом данными между ЭВМ и абонентами по общей шине | 1988 |

|

SU1543412A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1985 |

|

SU1249523A2 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| Устройство начальной синхронизации процессоров в резервированной системе | 1988 |

|

SU1582873A1 |

Изобретение относится к вычислительной технике, и может найти при- менение при построении высоконадежных систем. Цель изобретения - расширение функциональных возможностей за счет резервирования активных модулей. Система состоит из блоков голосования, синхронизаторов, процессоров, активных модулей, пассивных модулей, блоков магистральных формирователей, регистра адреса данных, тактового генератора. Цель изобретения достигй- ётся за счет обнаружения отибок блоком голосования и включения отдель- .ного синхронизатора на каждую подсистему. 2 з.п. ф-лы, 11 ил. ;

Изобретение относится к вычислительной технике и может найти применение при построении систем обработ- ки информации высокой надежности.

Цель изобретения - расширение функциональных возможностей за счет резервирования активных модулей.

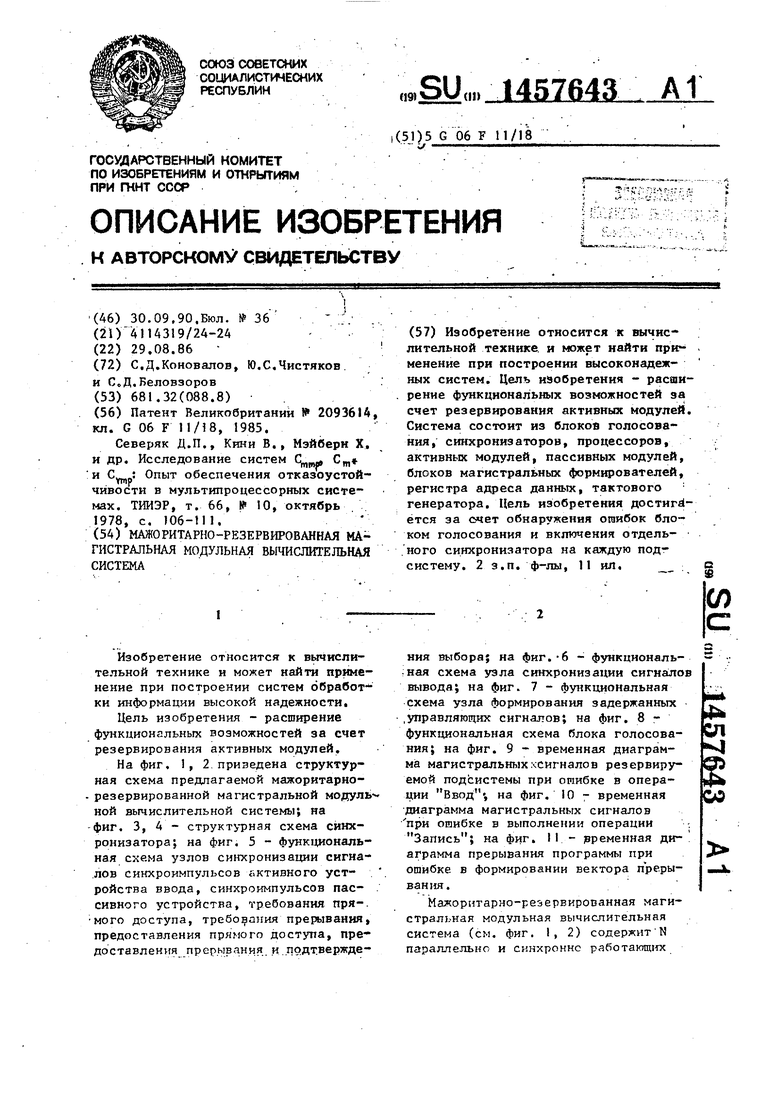

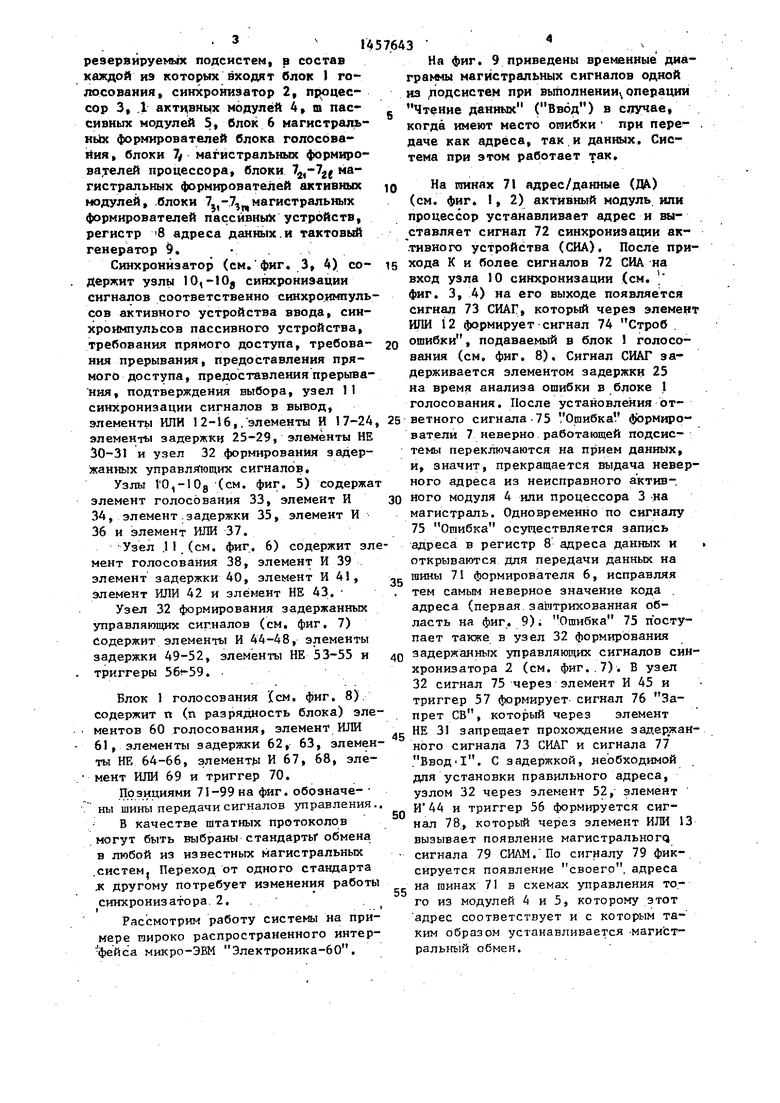

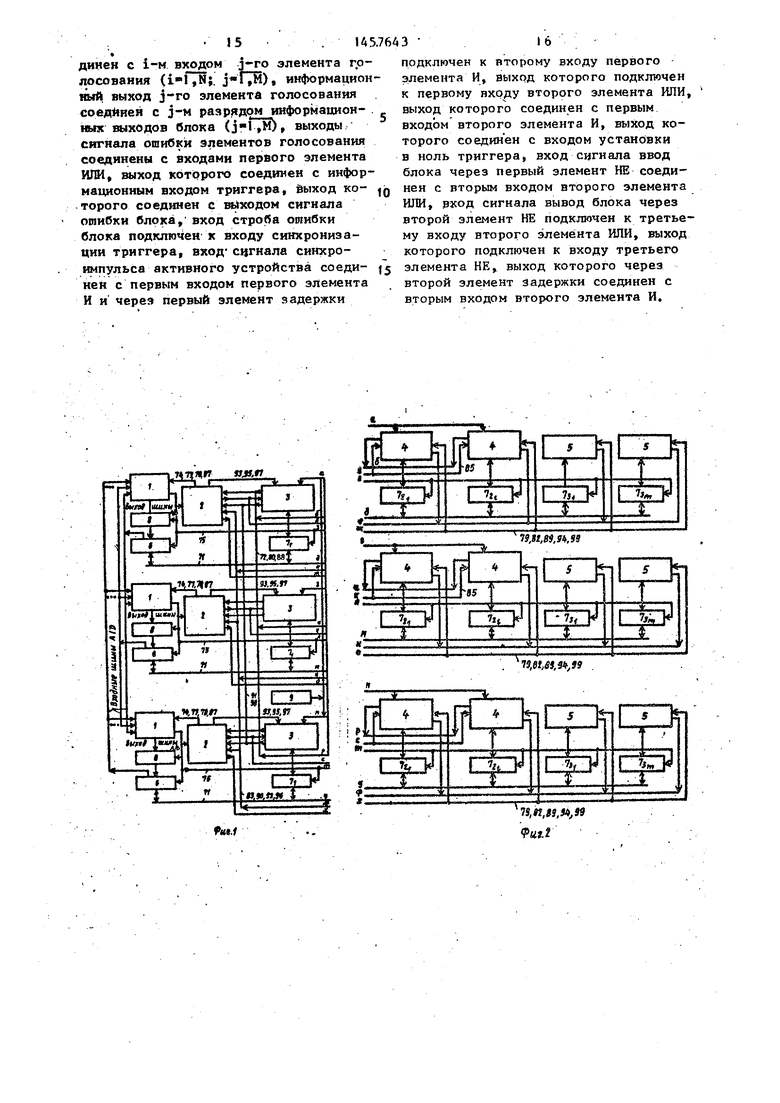

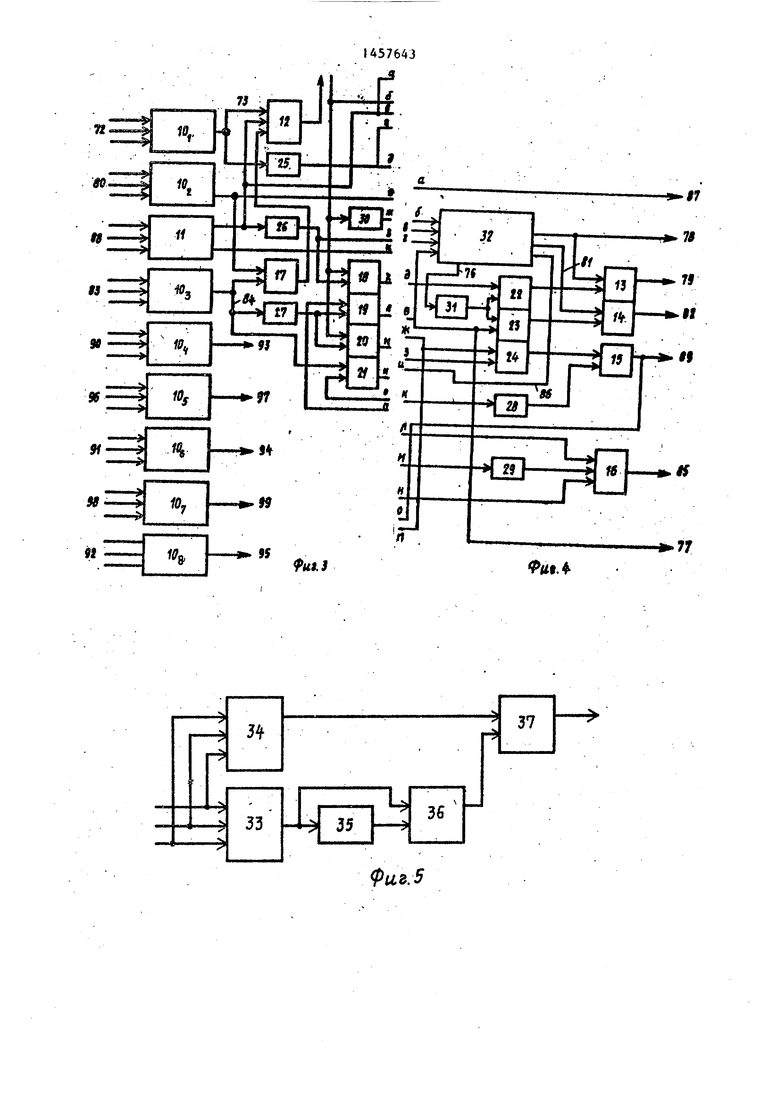

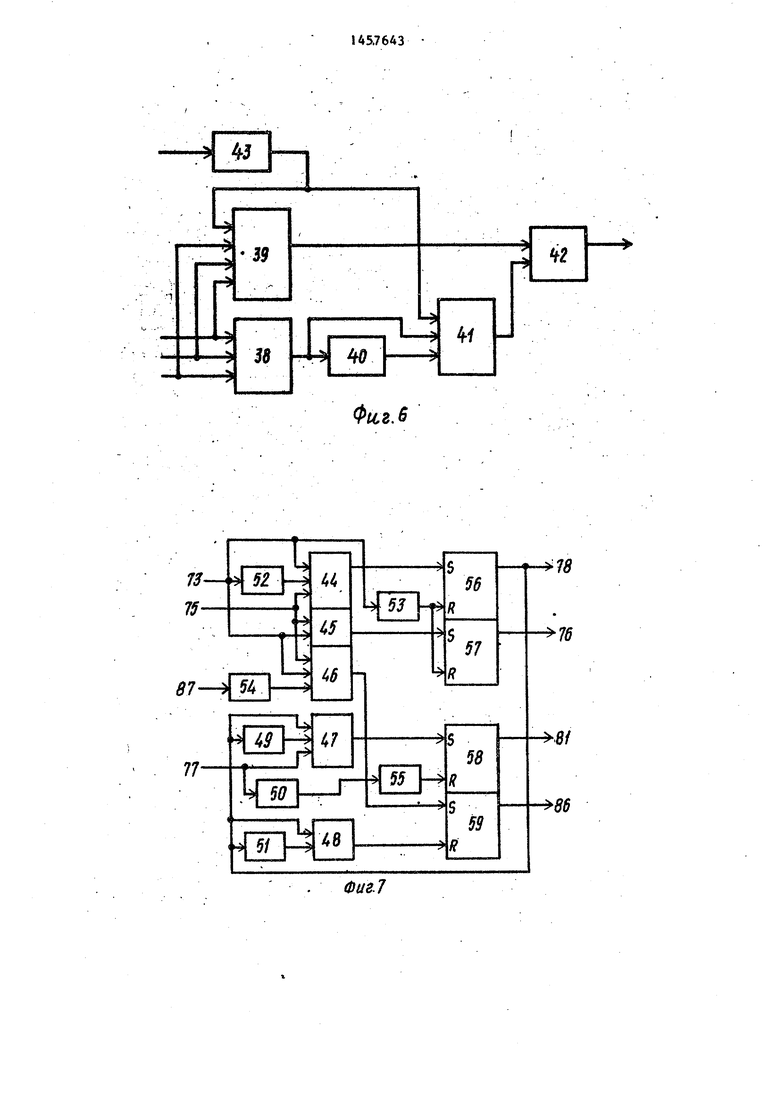

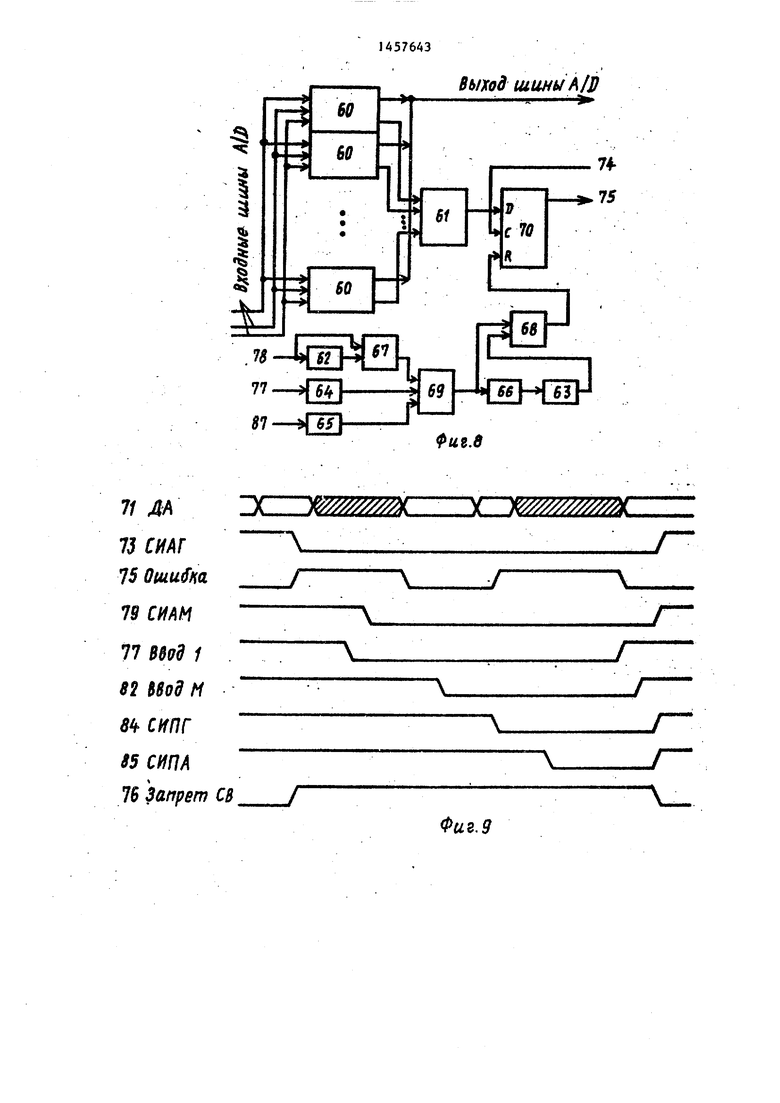

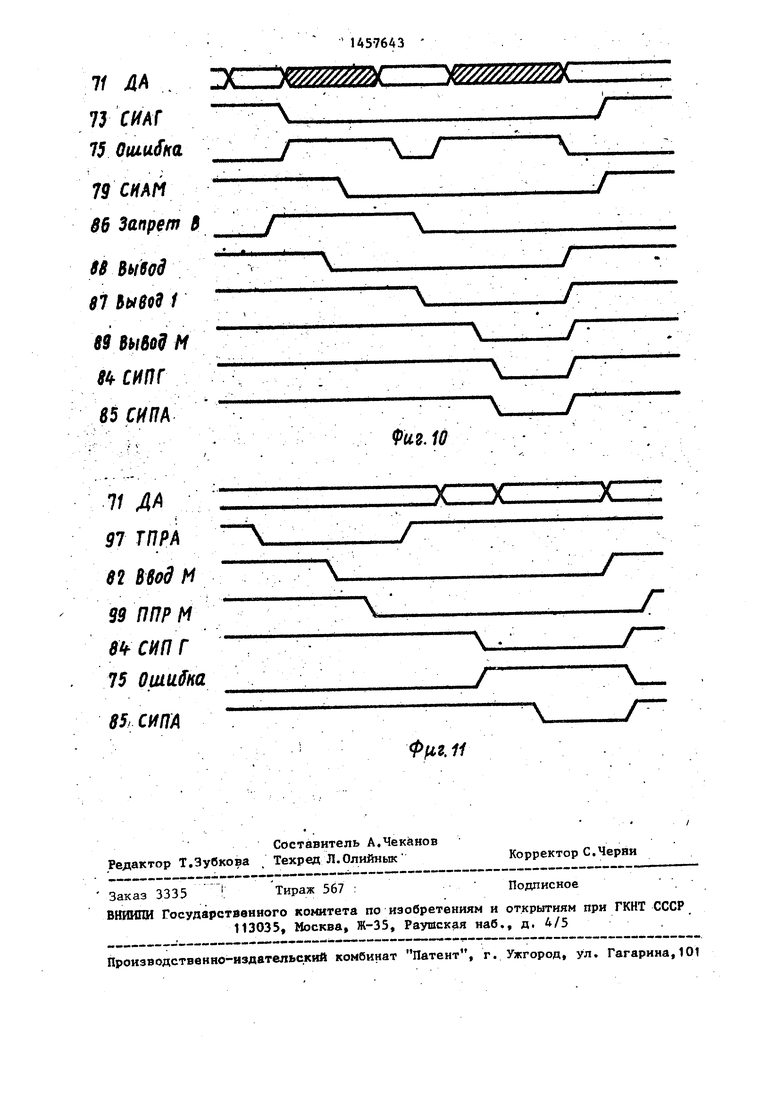

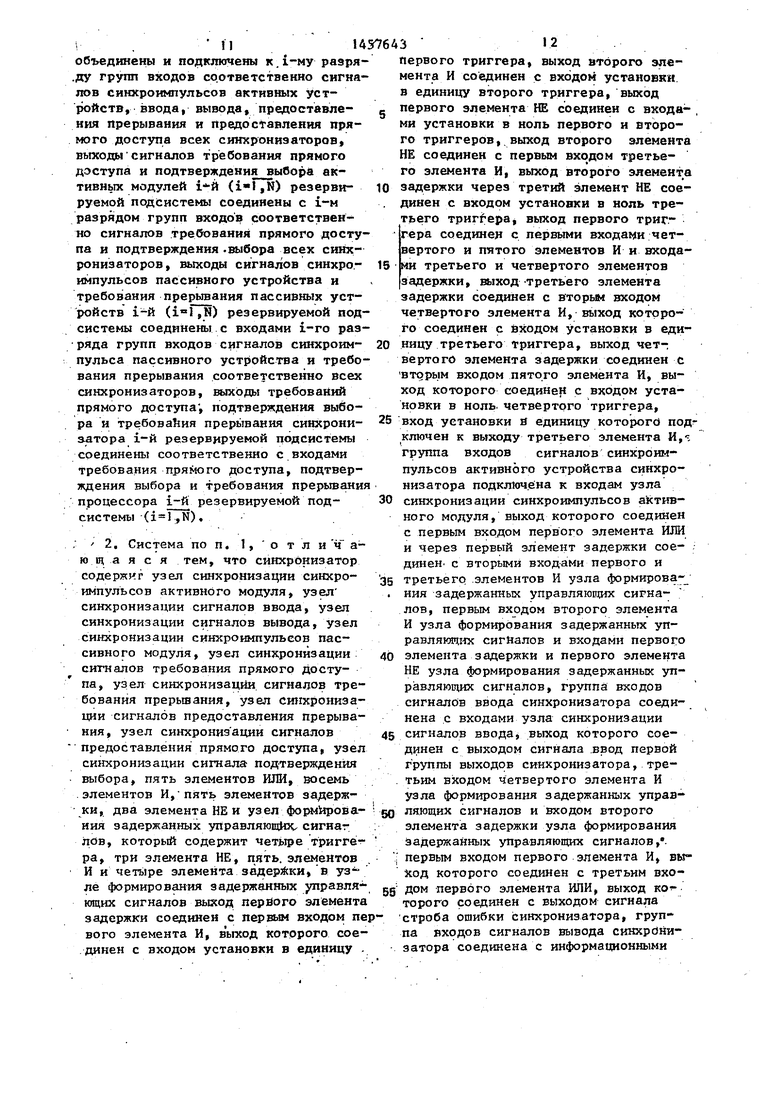

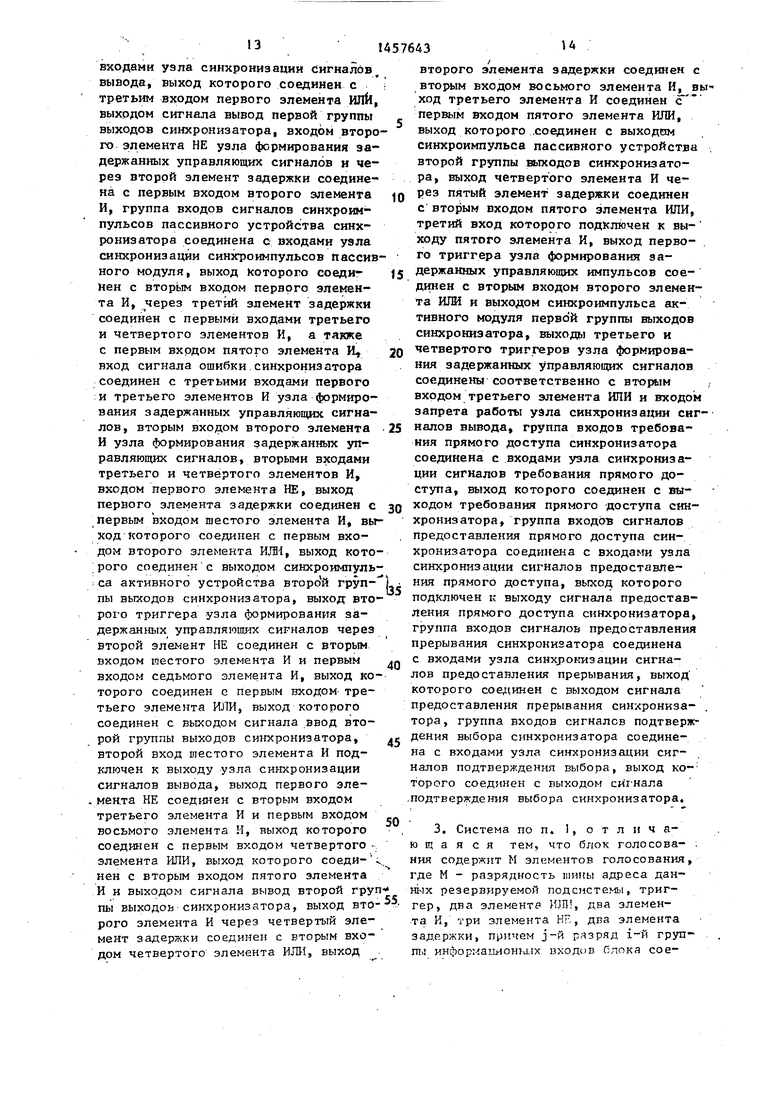

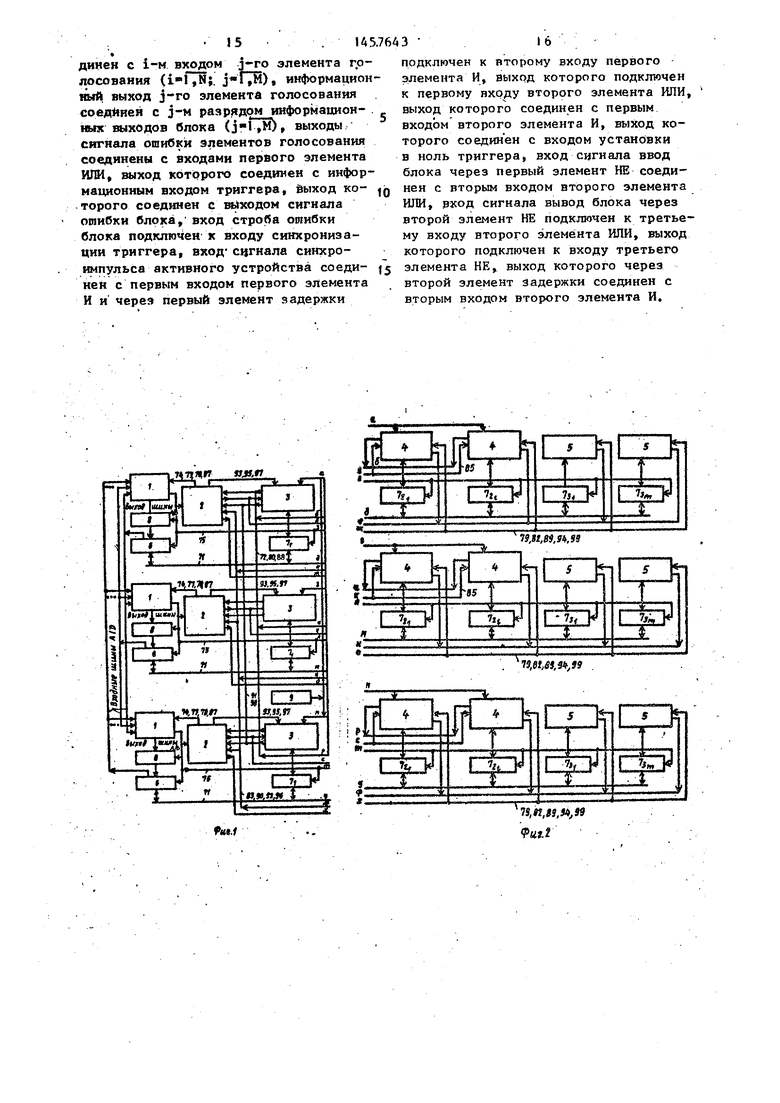

На фиг. 1, 2. приведена структурная схема предлагаемой мажоритарно- резервированной магистральной модуль-- ной вычислительной системы; на фиг, 3, 4 - структурная схема синхронизатора; на фиг. 5 - функи1иональ- ная схема узлов синхронизации сигиа- .лов синхроимпульсов активного уст- . ройства ввода, синхроимпульсов пассивного устройства, требования пря-. мого доступа, требования прерывания, предоставления прямого доступа, предоставления прерывания и подт.верждения выбора; на фиг.-6 - функциональ- ;ная схема узла синхронизации сигналов вывода; на фиг. 7 - функциональная схема узла формирования задержанных .втравляющих сигналов; на фиг. 8 - функциональная схема блока голосования; на фиг. 9 - временная диаграмма магистральныххсигналов резервируемой подсистемы при ошибке в операции , на фиг. 10 - временная диаграмма магистральных сигналов при ошибке в выполнении операции Запись ; на фиг. И - рременная ди- аграмма прерывания программы при ошибке в формировании вектора прерывания.

Мажоритарно-резервированная магистральная модульная вычислительная система (см. фиг. I, 2) содержит М параллельно и синхронно работактщт-гх

сд

1

ре9ервируемь|х подсистем, в состав каждой иэ которых входят блок I голосования, синхронизатор 2, сор 3 .1 активных модулей 4, m пассивных модулей 5, блок 6 магистраль- Hbbt формирователей блока голосова- йия, блоки 7/ магистральных формнро- ва,телей процессора, блоки J2t гистрапьных формирователей активных модулей, .блоки 7.,-.7 магистральных формирователей пассивных устройств, регистр 6 адреса данных.и тактовый генератор 9,

10

На фиг. 9 приведены временные диаграммы магистральных сигналов одной на ;1одснстен при выполнении операции Чтение данных (Ввод) в cjjynae, когда имеют место ошибки при пере- . даче как адреса, так.и данных. Система при этом работает так.

На шинах 71 адрес/данные (ДА) (см. фиг. , 2) активнь й модуль или процессор устанавливает адрес и выставляет сигнал 72 синхронизации ак- .тивного устройства (СИЛ), После приСинхронйэатор (см. фиг. 3, 4) со- 15хода К и более сигналов 72 СИЛ на

держит узлы 10,-lOj синхронизациивход узла JO синхронизации (см,

сигналов соответственно синхроимпуль-Фиг. 3, 4) на его выходе появляется

сов активного устройства ввода, снн-сигнал 73 СИАГ, который через элемент

хроймпульсов пассивного устройства,ИЛИ 12 формирует сигнал 74 Строб

20

требования прямого доступа, требования прерывания, предоставления прямого доступа, предоставления прерыва- ния, подтверждения выбора, узел 1 1 синхронизации сигналов в вывод.

ошибки, подаваемый в блок 1 голосования (см, фиг. 8). Сигнал СИАГ задерживается элементом задержки 25 на время анализа ошибки в блоке 1 голосования. После установления от-

элементы ИЛИ 12-16,/элементы И 17-24, 25 ветногр сигнала-75 УОшибка формиро- элементы задержки 25-29, элементы НЕ ватели 7 неверно работающей подсис- и

30-31 и узел 32 формирования задер- жанных управл5йощих сигналов.

Узлы V0, (см. фиг. 5) содержат элемент голосования 33, элемент И 30 34, элемент.задержки 35, элемент И 36 и элемент ИЛИ 37.

Узел .11 (см. фиг. 6) содержит элемент голосования 38, элемент И 39 элемент задержки 40, элемент И 41, элемент ИЛИ 42 и элемент НЕ 43.Узел 32 формирования задержанных управляющих сигналов (см. фиг. 7) Содержит элементы И 44-48, элементы задержки 49-52, элементы НЕ 53-55 и триггеры 561-59.

темы переключаются на прием данных, и, значит, прекращается выдача неверного адреса из неисправного актив-, ного модуля 4 или процессора 3 на магистраль. Одновременно по сигналу 75 Ошибка осуществляется запись

35

адреса в регистр 8 адреса данных и открываются для передачи данных на шины 71 формирователя 6, исправляя тем самым неверное значение кода . адреса (первая.заштрихованная область на фиг. 9); Ошибка 75 поступает также в узел 32 формирования 40 задержанных управляющих сигналов синхронизатора 2 (см. фиг..7). В узел 32 сигнал 75 через элемент И 45 и триггер 57 формирует сигнал 76 За45

50

Блок 1 голосования Кем. фиг. 8). содержит п (п разрядность блока) элементов 60 голосования, элемент ИЛИ 61 , элементы задержки 62, 63, элементы НЕ 64-66, элементы И 67, 68, эле- мент ИЛИ 69 и триггер 70.

Позициями 71-99 на фиг. обозначе- ны шины передачи сигналов управления..

В качестве штатных протоколов могут быть выбраны стандартьг обмена в любой из известных магистральных .систем. Переход от одного стандарта JC Другому потребует изменения работы синхронизатора. 2. .

Рассмотрим работу системы на примере широко распространенного интер- фейса микро-ЭВМ Электроника-60.

40

На фиг. 9 приведены временные диаграммы магистральных сигналов одной на ;1одснстен при выполнении операции Чтение данных (Ввод) в cjjynae, когда имеют место ошибки при пере- . даче как адреса, так.и данных. Система при этом работает так.

На шинах 71 адрес/данные (ДА) (см. фиг. , 2) активнь й модуль или процессор устанавливает адрес и выставляет сигнал 72 синхронизации ак- .тивного устройства (СИЛ), После приИЛИ 12 формирует сигнал 74 Строб

ошибки, подаваемый в блок 1 голосования (см, фиг. 8). Сигнал СИАГ задерживается элементом задержки 25 на время анализа ошибки в блоке 1 голосования. После установления от-

ветногр сигнала-75 УОшибка формиро- ватели 7 неверно работающей подсис-

темы переключаются на прием данных, и, значит, прекращается выдача неверного адреса из неисправного актив-, ного модуля 4 или процессора 3 на магистраль. Одновременно по сигналу 75 Ошибка осуществляется запись

30

35

адреса в регистр 8 адреса данных и открываются для передачи данных на шины 71 формирователя 6, исправляя тем самым неверное значение кода . адреса (первая.заштрихованная область на фиг. 9); Ошибка 75 поступает также в узел 32 формирования 40 задержанных управляющих сигналов синхронизатора 2 (см. фиг..7). В узел 32 сигнал 75 через элемент И 45 и триггер 57 формирует сигнал 76 За5

0

прет СВ, который через элемент НЕ 31 запрещает прохождение задержанного сигнала 73 СИАГ и сигнала 77 Ввод 1, С задержкой, необходимой для установки правильного адреса, узлом 32 через элемент 52, элемент И 44 и триггер 56 формируется сигнал 78., который через элемент ИЛИ 13 вызывает появление магистральнога сигнала 79 СИЛМ. По сигналу 79 фик-. сируется появление своего , адреса на шинах 71 в схемах управления то.- го из модулей 4 и 5, которому этот адрес соответствует и с которым та- КИМ образом устанавливается -магиЬт- ральный обмен.

С задержкой, необходимой Для гаантированной фиксации своего адеса, снимается сигнал 75 Ошибка формирователи 6 и 7 возвращаются свое нормальное состояние; 6 - на риём данных с пин 71, 7 - в режим рием - передача, зависимости от игналов управления соответствуюих модулей.

В то время, ,как идет корректировка адреса на шинах 71, активное устройство выставляет сигнал 80 Ввод, После прихода К и .более сигналов Ввод на вход узла 10 синхронизации на его выходе появляется сигнал 77 Ввод I. Сигнал 75 Ошибка, сформировав сигнал 76 Запрет СВ, не разрешает прохождение -сигнала 77 Ввод 1 через алемент И 23.

С задержкой, необходимой на фиксацию своего адреса модулем, и после возврата формирователей 6 и 7 в нормальное состояние через элемент задержки 49, элемент И 47 и триггер 58 формируется на выходе узла 32 сигнал 81, который через элемент ИЛИ 14 вызывает появление магистрального сигнала 82 Ввод М. На сигнал 82 выбранный модуль подсистемы отвечает сигналом 83 синхронизации пассивного устройства (СИП). В этот мо- мент происходит подсинхронизация подсистем, которая обеспечивается в данном случае узлом 10. Задержки формирования сигнала 83 СИП на неверно работающей магистрали, связанные с необходимостью корректировки адреса, по сравнению с исправной магистралью составляют 250-300 не. Поэтому значение задержки (элемент задержки 35) в соответствуищем.узле. 10 принято равным 500 не с таким расчетом, чтобы подсистемы после ошибки адреса в одной из них не вышли из синхронизма. На выходе узла 10 фор- мируется сигнал 84 СИПГ. Этот сигнал через элемент И 17 и элемент ИЛИ 12 формирует 74 сигнал Строб ошибки и с задержкой на время анализа ошибочной ситуации через элемент задержки 27 поступает на входы элементов И 19 и 20. В случае появления сигнала 75 Ошибка аналогично корректировке

адреса происходит исправление данных gg pa 8 адреса данных. В ято время в (вторая заштрихованная область нанормально работающих подсистемах

фиг. 9), а сигнал 84 СИПГ с задерж- , (сигналы 75 Ошибка и, следовлтель- кой через элемент И 20, элемент за-но, 86 Запрет В отсутствуют) в отдержки,29 и элемент ИЛИ 16 (сигнал . вет на К и более сигналов 88 Вывйд

85 СИПА) поступает на входы активных модупей 4 и процессора 3.

В ответ на сигнал 85 СИПА активный модуль 3 или 4 снимает сигнал 80 Ввод .. При этом последовательно снимаются сигналы 77 Ввод I , 75 Ошибка, формирователи 6 и 7 приходят в нормальное состояние, снимается сигнал 82 Ввод М. В ответ на это сбрасывается сигнал 83 СИП, а затем сигналы 84 СИПГ и 85 СИПА.Заканчивается цикл снятием сигналов 72 СИА, 73 СИАГ, 76 Запрет СВ, 79 СИАМ.

К этому моменту неисправная подсистема опаздывает во времени по отношению к правильно работающим. Полная синхронизация подсистем произойдет в начале следующего цикла обмена на магистрали с приходом сигналов 72 СИА соответствующие узлы 10 ;синхронизации сформируют сигна- лы 73 СИМ одновременно во всех под- .системах). /

На фИг. IU приведены временные диаграммы магистральных сигналов одной

из подсистем при выполнении операции Запись данных (Вывод) в случае, когда имеют место ошибки при передаче как адреса, так и данных по магистрали.

Адрес на шинах 71 ДА и сигналы 73 СИАГ, 75 Ошибка, 79 СИАМ устанавливаются при корректировке и передаче адреса по магистрали так же, как и в случае выполнения операции . Ввод. Кроме того, сигнал 75 Ошибка через элемент И- 46 и триггер 59 вводит сигнал 86 Запрет В, который поступает на вход элемента НЕ 43 и до завершения передачи адреса по магистрали и установки передаваемь : данных на пшнах 71 задерживает появление сигнала 87 Вывод I на выходе узла 11,;

Появлению сигнала 88 Вывод на . выходе активного модуля предшествует установка на выходных шинах переда- вае. данных. Поэтому до завершения корректировки лдреса его значение считывается на магистраль с регист

14

через узел 11 и эл.емент задержки 26,

элемент И 24 iji элеме нт ИЛИ 15 будет установлен сигнал 89. Вывод М. В ртвет на сигнал 89 модули подсистем (в каждой подсистеме один)выетвгвит: сигнал 83 СИП. Начиная с этого момента,- нормально работанхцие подсир- темы будут приостановлены благодаря задержке в элементе задержки 35 до появления сигнала СИП от модуля в неисправной подсистеме. С его появлением произойдет подсишсронизация параллельно работапхцих подсистем.

В неисправной подсистеме, как это представлено на фиг. 8, сигнал 87 Вывод I появится на выходе узла I1 после снятия сигнала 86 Запрет В. В это время на шинах 71 всех магистрлей установлены передаваемые данные. Сигнал 87 Вывод I через элемент ИЛИ 12 формирует сигнал 74 Строб ошибки. При появлении сигнала 75 Ошибка от блока голосования происходит пврнключение формиррва- телей -6 и 7 с корректировки данных на шинах 71. Сигнал, 87 Вывод 1, задержанный на время анализа ошибочной ситуации элементом задержки .26, поступает в этом случае через элемент И 18 на вход элемента задержки 28. Элемент задержки 28 задёржи- вает сигнал Вывод I на время переключения формирователей 6 и 7 и корректировки данных на тинах 71. Затем этот сигнал с выхода элемента зедерж ки 28 через элемент ИЛИ 5 формирует магистральный сигнал 89 Вывод М . На сигнал 89 появляется ответный сиг иал СИП 83, с приходом которого происходит подсинхронизация подсйстем. В этот момент формируется сигнал 84 СИПГ, который через элемент 21 и элемент ИЛИ 16 вызывает появление сигнала 85 СИПА. Поступление на вход активного модуля или процессора сигнала 85 ведет к снятию сигнала 88 Вывод и последовательному выключению сигналов 87 Вывод I, 89.; Вывод М, снятию 75 Ошибка,- возвращению в нормальное состояние формирователей 6, 7 и снятию сигналов 84 СИПГ, 85 СИПА,73 СИАГ и 79 СИАМ. На этом магистральная операци

заканчивается. Выполнение магистральной операци

Вывод

Ввод пауза - вывод является комбинацией различных этапов выполнения операций Ввод и Вывод.8

0

5

25

0

30

i Временная ди аграмма предоставления пряного доступа к памяти в рассматриваемой системе отличается от штатного протокола обмена только тем, что управляющие сигналы 90 Требование, прямого доступа (ТПД), 91 Предоставление прямого доступа (ППД) и 92 Подтверждение выбора (ПВ) проходят через соответствующие узлы 10 синхронизации , где осуществляется их под- синхронизация и формирование сигналов 93 ТПДА, 94.ППДМ и 95 ПВА, которые можно рассматривать как аналоги соответствующих управляющих сигналов ; штатного протокола обмена.

На фиг. 11 приведена времеиная диаграмма прерьшания программы в случае ошибки при формировании адреса вектора прерывания.

Работа системы в этом случае начинается с формирования модулями в подсистемах сигнала 96 Требование прерывания (ТПР), который, проходя через узел 10 синхронизации, вызывает появление на входе процессора 3 сигнала 97 ТПРА. Процессор 3 удовлетворяет требование, вырабатывая сначала , сигнал 80 Ввод, а затем 98 Предоставление прерьшания (ППР) . Сизгнал 80 Ввод через узел 10, элемент И 23 и элемент ИЛИ 14 формирует сигнал 82 Ввод М, а сигнал 98 ППР через узел 10 вводит сигнал 99 ППРН.

В ответ на сигналы 82 и 99 модуль нимает сигнал 96 ТПР и устанавливат на шинах 71 адрес вектора прерывания, после Чего вьфабатывает сиг г

ал 83 СИП. Сигнал 83, пройдя через узел 10, вызывает появление сигнала 84 СИПГ, который через элемент И 17 и элемент ИЛИ 12 формирует сигнал 74,Строб ошибки. В ответ на сигнал .

74 блок 1 голосования вырабатываем сигнал 75 Ошибк а при неверно установленном адресе вектора. По сигналу 75 переключаются формирователи 6, 7 и корректируется адрес вектора прерывания. Сигнал 75 разрешает прохождение задержанного на элементе задержки 27 сигнала 84 СИПГ через эяе- мент И 20 на вход элемента эадержки . . 29, где он задерживается на время,

необходимое для корректировки адреса вектора и затем через элемент ИЛИ 16 формирует сигнал 85 СИПА, В ответ на сигнал 85 процессор 3 снимает сигнал 80 Ввод. После этого последо 1457643 °,

вательно снимаются сигналы 82 Ввод стралькых формирователей i-й (,п) М, 75 Ошибка, переключаются в нор- резервируемой подсистемь соединены faльнoe состояние формирователи 6, 7 и сбрасываются сигналы 83 СИП, 8А с СИПГ, и 85 СИПА. операция передачи адраса BeKtopa прерывания заканчивается.

Если все модули вычислительной

10

системы исправны или исправны хотя бы те модули, которые участвуют в обмене информацией по магистрали в данный момент времени, то протокол обмена практически ничем не отлича- . ется от штатного протокола. В этом случае может наблюдаться лишь рас- синхронизация магистральных сигналов в подсистемах, вызванная различиями в скорости распространения сигналов по однотипным электрическим цепям, 20 Элементы задержки 35 и 40 в узлах 10 и 11 синхронизации синхронизаторов 2 будут в течение каждого цикла обмена на магистрали осуществлять операцию поддержки подсистем в синхронизме. Кроме ТОГО) дополнительные задержки по сравнению со штатным протоколом обмена необходимы для анализа ошибочной ситуации на магистрас информационными входами i-й.группы блоков голосования, в каждой ре- зepвиpye foй подсистеме информационные выходы резервирования подключены к информационным входам регистра адреса данных, выходы каторо - го соединены с входами блока системных магистральных формирователей, входы-выходы которых через шину адреса данных резервируемой подсистемы соединены с входами-выходами пер- 15 вых групп блоков магистральных фор- миррвателей, активньк модулей группы, блоков магистральных формирователей naccHBfiix модулей группы и бло ка процессоров магистральных формирователей, выход сигнала наличия ошибки блока голосования соединен с входом сигнала наличия ошибки синхро низатора, входом синхронизации регистра адреса данных и управляющими входами блока системных магистральных формирователей, блока процессорных магистральных формирователей, блоков магистральных формирователей активных модулей группы и блоков

25

АГД.;} сх ./ илвя rii. у , . .-к.ъ

ЛИ. Эти задержки формируются элемен- 30 магистральных формирователей пассивтами задержки 25, 26 и 7.7 низаторов 2,

синхроных модулей группы, выход синхроимпульса пассивного устройства синхро низатора соедийен с одноименнымн входами синхроимпульсов пассивного

Формула изобретения

I. Мажоритарно-резервированная магистральная модульная вычислительная система, содержащая тактовый ге- нератор и N резервируемых подсистем, где N - кратность резервирования , причем каждая из резервируемых подсистем содержит процессор и группу пассивных модулей, выход тактового генератора соединен с тактовыми входами всех процессоров, о т л и ч а ю щ а я с я тем, что, с целью расширения функциональных возможностей за счет резервирования активных мо- дулей, каждая резервируемая подсис тема содержит блок голосования, регистр адреса данных, блок системных магистральных формирователей, блок Процессорных магистральных формирователей, группу активных модулей.

ных модулей группы, выход синхроимпульса пассивного устройства синхро низатора соедийен с одноименнымн входами синхроимпульсов пассивного

or устройства процессоров активных и пассивных модулей, выходы сигналов строба ошибки, ввода синхроимпульса активного устройства и вывода первой группы синхронизатора соединены с

40 одноименными входами блока голосования, выходб сигналов синхроимпульса активного устройства, ввода и вывода второй группы синхронизатора соеди- нены с одноименными входами активных

45 и пассивных модулей, выход сигнала предоставления прямого доступа сда- хронизатора соединен с входамн предоставления прямого доступа активных модулей, выход предоставления преры5Q вания синхронизатора соединен с входами предоставления прерывания пассивных модулей, в ыход тлктозого генератора соединен с тактовыми шхода- ми активных модулей, выходы сигналов

группу блоков магистральных формиро- 55 сшосроимпульсов активных устройств.

вателей активньгх модулей, группу блоков магистральных формирователей пассивных модулей и синхронизатор, причем выходы блоков системны.х магиввода, вывода, предоставления преры- .вания и предостапления прямого досту гпа процессора и актив;1ых модулей .

i-й ( резервируемой подсистемы

стралькых формирователей i-й (,п) резервируемой подсистемь соединены

0

0

с информационными входами i-й.группы блоков голосования, в каждой ре- зepвиpye foй подсистеме информационные выходы резервирования подключены к информационным входам регистра адреса данных, выходы каторо - го соединены с входами блока системных магистральных формирователей, входы-выходы которых через шину адреса данных резервируемой подсистемы соединены с входами-выходами пер- 5 вых групп блоков магистральных фор- . миррвателей, активньк модулей группы, блоков магистральных формирователей naccHBfiix модулей группы и блока процессоров магистральных формирователей, выход сигнала наличия ошибки блока голосования соединен с входом сигнала наличия ошибки синхронизатора, входом синхронизации регистра адреса данных и управляющими входами блока системных магистральных формирователей, блока процессорных магистральных формирователей, блоков магистральных формирователей активных модулей группы и блоков

5

магистральных формирователей пассивных модулей группы, выход синхроимпульса пассивного устройства синхро. низатора соедийен с одноименнымн входами синхроимпульсов пассивного

устройства процессоров активных и пассивных модулей, выходы сигналов строба ошибки, ввода синхроимпульса активного устройства и вывода первой группы синхронизатора соединены с

одноименными входами блока голосования, выходб сигналов синхроимпульса активного устройства, ввода и вывода второй группы синхронизатора соеди- - нены с одноименными входами активных

и пассивных модулей, выход сигнала предоставления прямого доступа сда- хронизатора соединен с входамн предоставления прямого доступа активных модулей, выход предоставления прерывания синхронизатора соединен с входами предоставления прерывания пассивных модулей, в ыход тлктозого генератора соединен с тактовыми шхода- ми активных модулей, выходы сигналов

сшосроимпульсов активных устройств.

ввода, вывода, предоставления преры- .вания и предостапления прямого досту- гпа процессора и актив;1ых модулей .

i-й ( резервируемой подсистемы

10

15

20

25

объединены и подключены к,i-му разря- ДУ групп входов со.ответственно снгна лов синхроимпульсов активных устройств, ввода, вывода, предоставления прерывания и предоставления прямого доступа всех синхронизаторов, выходы сигналов требования прямого доступа и подтверждения выбора ак- тивньпс модулей (i«1,N) резервируемой подсистемы соединены с i-м разрядом групп входов соответственно сигналов требоваиия прямого доступа и подтверждения .выбора всех синхронизаторов, выходы сигналов синхроимпульсов пассивного устройства и требования прерывания пассивнь х устройств i-й (,N) резервируемой подсистемы соединены с входами i-ro разряда групп входов сигналов синхроимпульса пассивного устройства и требования прерывания соответственно всех синхронизаторов, выходы требований прямого доступа , подтверждения выбора и требова 1ия прерывания синхронизатора i-й резервируемой подсистемы соединены соответственно с входами требования прямого доступа, подтверждения выбора и требования прерьгогшия процессора i-й резервируемой подсистемы (,N).

2, Система по п, 1, о т л и ч а- ю щ а я с я тем, что синхронизатор содержит узел синхронизации синхроимпульсов активного модуля, узел синхронизации сигналов ввода, узел синхронизации сигналов вывода, узел синхронизации синхроимпульсов пассивного модуля, узел синхронизации сигналов требования прямого доступа, узел синхронизации сигналов требования прерывания, узел синхронизации сигналов предоставления прерывания, узел синхрониз ации сигналов предоставления прямого доступа, узел синхронизации сигнала подтверждения выбора, пять злементов ИЛИ, восемь элементов И, пять элементов задержки, два злемента НЕ и узел фо1 111рова- go

g

30

40

45

35 третьего .элементов И узла формирова. ния задержанных управляюп их сигналов, первым входом второго элемента И узла формирования задержанных управляющих сигналов и входами первого элемента задержки и первого элемента НЕ узла формирования задержанных управляющих сигналов, группа входов сигналов ввода синхронизатора соединена с входами узла синхронизации сигналов ввода, выход которого соединен с выходом сигнала .ввод первой группы выходов синхронизатора, третьим входом четвертого элемента И узла формирования задержанных управляющих сигналов и входом второго злемента задержки узла формирования задержанных управляющих сигналов,, первым входом первого элемента И, вы ход которого соединен с третьим вхония задержанных управляющих сигна- ; лов, который содержит четь1ре триггёт-

ра, три элемента НЕ, пять, элементов И и четь1ре злемента задержки, в узле формирования задержанных управля-gg дом первого элемента ИЛИ, выход ко - ющих сигналов выход перйого элементаторого соединен с выходом сигнала задержки соединен с первым входом пер- строба ошибки синхронизатора, груп- вого элемента И, в ыход которого сое-па входов сигналов вывода синхрони- динен с входом установки в единицу .затора соединена с информационными

0

5

0

5

go

Первого триггера, выход второго элемента И соединен с входом установки, в единицу второго триггера, выход

первого элемента НЕ соединен с входами установки в ноль первого и второго триггеров,.выход второго элемента НЕ соединен с первым входом третьего злемента И, выход второго злемеит а задержки через третий элемент НЕ соединен с входом установки в ноль третьего триггера, выход первого триггера соединен с первыми входами четвертого и пятого элементов И и входами третьего и четвертого элементов задержки, выход-третьего злемента задержки соединен с вторьм входом четвертого элемента И, выход которого соединен с входом установки в единицу третьего триггера, выход чет-; вертого злемента задержки соединен с вторым входом пятого элемента И, выход которого соединен с входом установки в ноль, четвертого триггера, вход установки я единицу которого подг ключей к выходу третьего злемента И,-, группа входов сигналов синхроимпульсов активного устройства синхронизатора подключена к входам узла синхронизации синхроимпульсов akTHB- ного модуля, выход которого соединен с первым входом первого элемента ИЛИ и через первый элемент задержки соединен, с вторыми входами первого и

5 третьего .элементов И узла формирова . ния задержанных управляюп их сигналов, первым входом второго элемента И узла формирования задержанных управляющих сигналов и входами первого элемента задержки и первого элемента НЕ узла формирования задержанных управляющих сигналов, группа входов сигналов ввода синхронизатора соединена с входами узла синхронизации сигналов ввода, выход которого соединен с выходом сигнала .ввод первой группы выходов синхронизатора, третьим входом четвертого элемента И узла формирования задержанных управляющих сигналов и входом второго злемента задержки узла формирования задержанных управляющих сигналов,, первым входом первого элемента И, выход которого соединен с третьим вхо0

0

45

gg дом первого элемента ИЛИ, выход ко - торого соединен с выходом сигнала строба ошибки синхронизатора, груп- па входов сигналов вывода синхрони- затора соединена с информационными

13

10

15

20

25

входами узла синхронизации сигналов, вывода, выход которого соединен с : третьим входом первого элемента ИЛИ, выходом сигнала вывод первой группы выходов синхронизатора, входом второго элемента НЕ узла формирования задержанных управляющих сигналов и через второй элемент задержки соединена с первым входом второго элемента И, группа входов сигналов синхроимпульсов пассивного устройства синхронизатора соединена с входами узла синхронизации синхт)оимпульсов пассивного модуля, выход Которого соединен с BTopbiM входом первого злемен- та И, через третий элемент задержки соединен с первыми входами третьего и четвертого элементов И, а также с первым входом пятого элемента R, вход сигнала ошибки.синхронизатора соединен с третьими входами первого и третьего элементов И узла формирования задержанных управляющих сигналов, вторым входом второго элемента . И узла формирования задержанных управляющих сигналов, вторыми входами третьего и четвертого элементов И, входом первого элемента НЕ, выход первого элемента задержки соединен с первым входом шестого элемента И, выход которого соединен с первым входом второго элемента ИШ, выход которого соединен с выходом синхроимпуль- са активного устройства второ й rpyn- Lz пы выходов синхронизатора, выход второго триггера узла формирования задержанных управляющих сигналов через второй элемент НЕ соединен с вторым входом шестого элемента И и первым ,Q входом седьмого элемента И, выход которого соединен с первым входом- третьего элемента ИЛИ, выход которого соединен с выходом сигнала ввод второй группы выходов синхронизатора, второй вход шестого элемента И подключен к выходу узла синхронизации сигналов вывода, выход первого зле- мента НЕ соединен с вторым входом третьего элемента И и первым входом восьмого элемента И, выход которого соединен с первым входом четвертого - элемента ИЛИ, выход которого соеди-Ч.. нен с вторым входом пятого элемента И и выходом сигнала вывод второй груп- пы выходов синхронизатора, выход вто- рого элемента И через четвертый элемент задержки соединен с вторым входом четвертого элемента ИЛИ, выход

30

45

50

ого элемента задержки соединен с

10

15

20

25

z ,Q

30

45

0

вторым входом восьмого злемента И, вы- ход третьего элемента И соединен первым входом пятого элемента ИЛИ, выход которого .соединен с выходам синхроимпульса пассивного устройства второй группы выходов синхронизатора, выход четвертого элемента И через пятый элемент задержки соединен с вторым входом пятого элемента ИЛИ, третий вход которого подключен к вы- ходу пятого элемента И, выход первого триггера узла формирования задержанных управляющих импульсов соединен с вторым входом второго элемента ИШ и выходом синхроимпульса активного модуля перво й группы выходов синхронизатора, выходь третьего и четвертого триггеров узла формирования задержанных управляющих сигналов соединены соответственно с вторым,

входом третьего элемента ИЛИ и входом запрета работы уйла синхронизадин сигналов вывода, группа входов требования прямого доступа синхронизатора соединена с входами узла синхронизации сигналов требования прямого доступа, выход которого соединен с выходом требования прямого доступа синхронизатора, группа входов сигналов предоставления прямого доступа синхронизатора соединена с входами узла синхронизации сигналов предоставления прямого доступа, выход которого подключен к выходу сигнала предоставления прямого доступа синхронизатора, группа входов сигналов предоставления прерывания синхронизатора соединена с входами узла синхронизации сигналов предоставления прерывания, выход которого соединен с выходом сигнала предоставления прерывания синхронизатора , группа входов сигналов подтверждения выбора синхронизатора соединена с входами узла синхронизащин сигналов подтверждения выбора, выход ко- торого соединен с выходом сиГ Нала .подтверждения выбора синхронизатора.

f(t.f

подключен к второму входу первого элемента И, выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И, выход которого соединен с входом установки в ноль триггера, вход сигнала ввод блока через первый элемент НЕ соединен с вторым входом второго элемента ИЛИ, вход сигнала вывод блока через второй элемент НЕ подключен к третьему входу второго элемента ИЛИ, выход которого подключен к входу третьего элемента НЕ, выход которого через второй элемент задержки соединен с вторым входом второго элемента И.

75,n,g3,K,S9 9{itt

.77

tft.

иг.5

Фиг. 7

Фи,в. 6

СВ

74- 75

иг.в

Y j(///// mk

J

Фив. 9

.

UI

Фиг. 10

.И

| ЭЛЕКТРОЛИТ ЛУЖЕНИЯ ЖЕСТИ | 1995 |

|

RU2093614C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Северян Д.П., Кини В., Мэйбери X | |||

| и др | |||

| Исследование систем С С„ и Опыт обеспечения отказоустойчивости в мультипроцессорных системах | |||

| ТШЭР, т | |||

| Приспособление для соединения пучка кисти с трубкою или втулкою, служащей для прикрепления ручки | 1915 |

|

SU66A1 |

| Светоэлектрический измеритель длин и площадей | 1919 |

|

SU106A1 |

Авторы

Даты

1990-09-30—Публикация

1986-08-29—Подача