Изобретение относится к технике электросвязи и может быть использовано в цифровых системах передачи.

Цель изобретения - расширение функциональных возможностей устройства за счет формирования не только относительного биимпульсного сигнала, но и сигналов RZ, BI-LNRZ-S, BI-M, DBI и МИЛЛЕР.

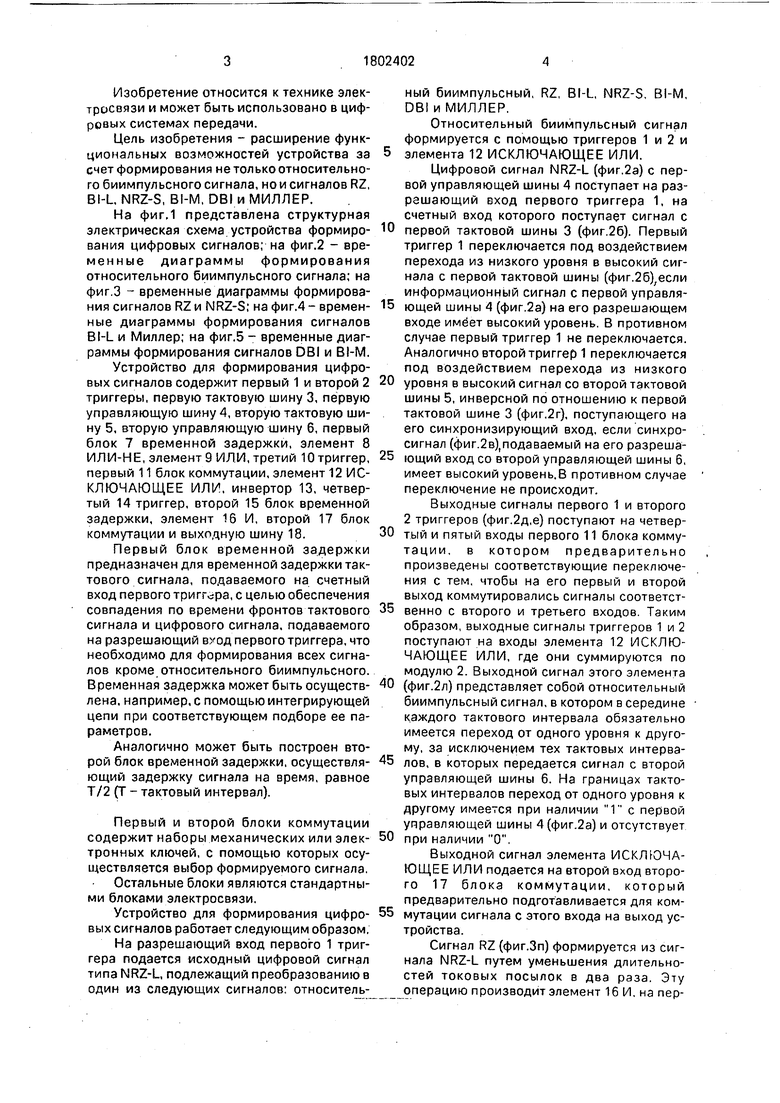

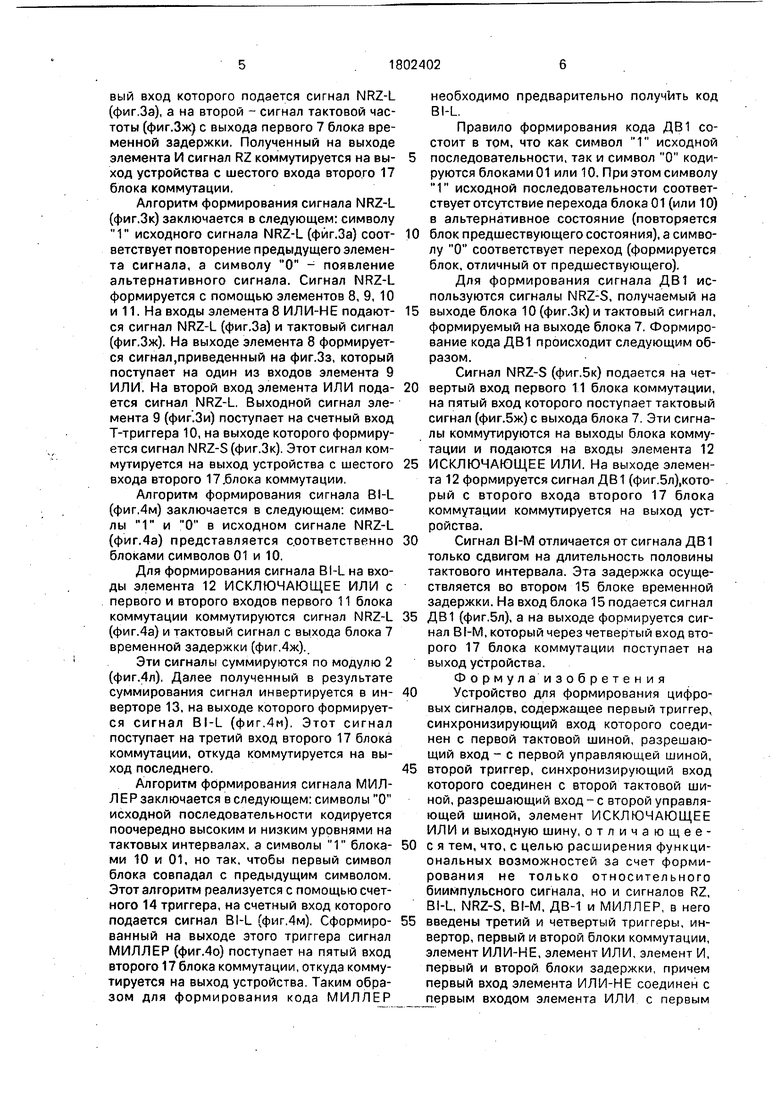

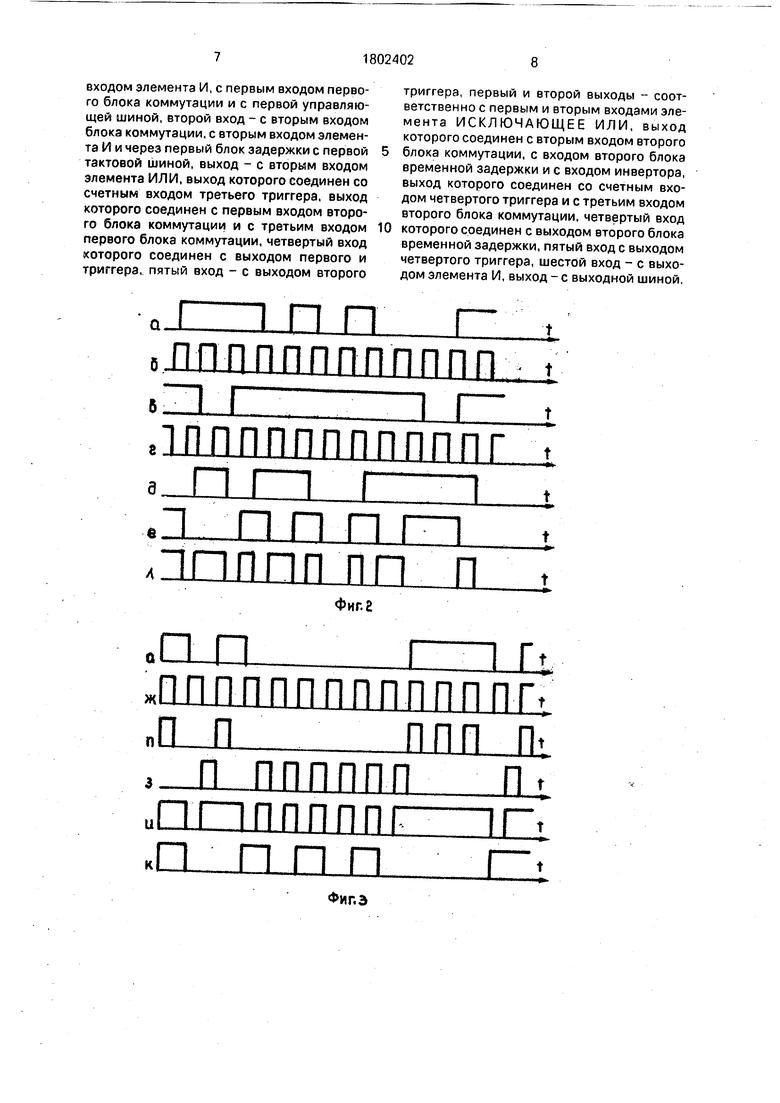

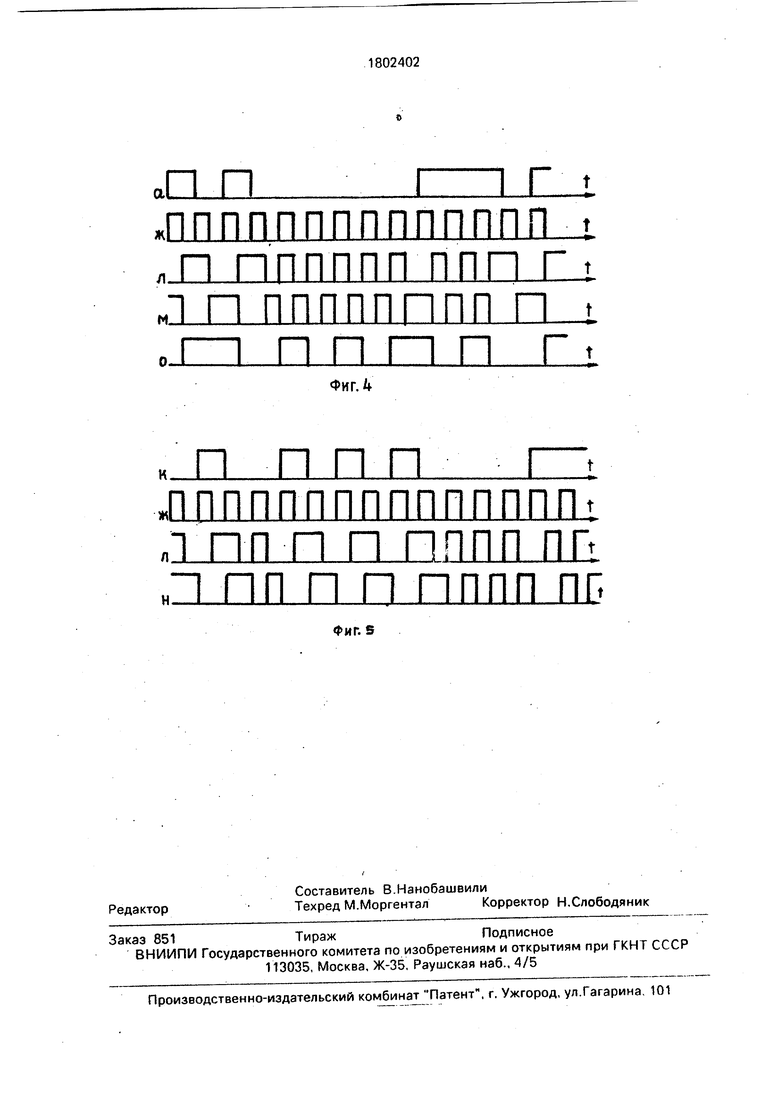

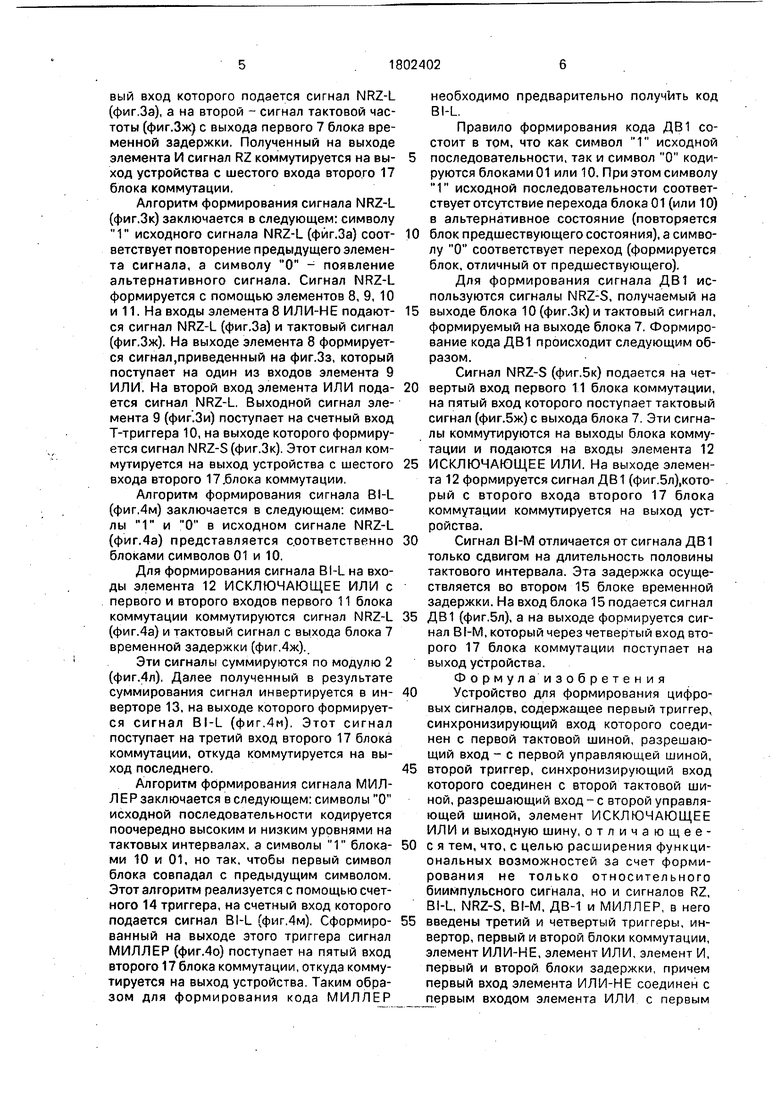

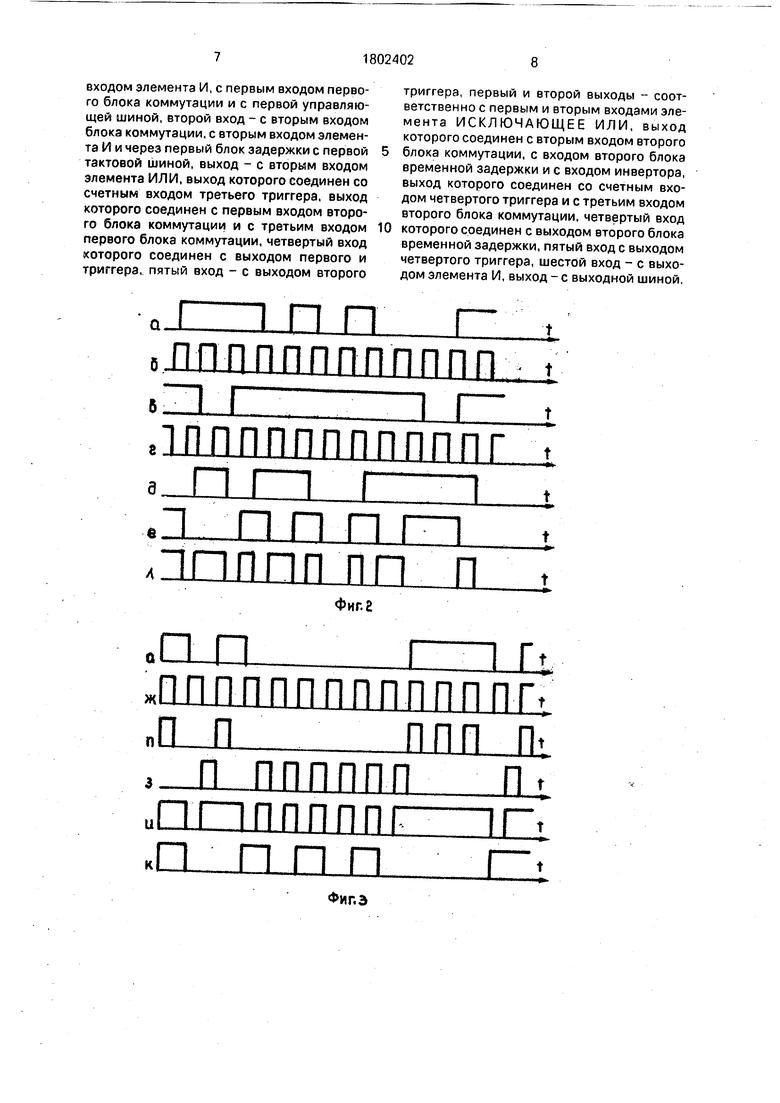

На фиг,1 представлена структурная электрическая схема устройства формирования цифровых сигналов; на фиг.2 - временные диаграммы формирования относительного биимпульсного сигнала; на фиг.З - временные диаграммы формирования сигналов RZ и NRZ-S; на фиг.4 - временные диаграммы формирования сигналов BI-L и Миллер; на фиг.5 - временные диаграммы формирования сигналов DBI и BI-M.

Устройство для формирования цифровых сигналов содержит первый 1 и второй 2 триггеры, первую тактовую шину 3, первую управляющую шину 4, вторую тактовую шину 5, вторую управляющую шину 6, первый блок 7 временной задержки, элемент 8 ИЛИ-НЕ, элемент 9 ИЛИ, третий 10 триггер, первый 11 блок коммутации, элемент 12 ИСКЛЮЧАЮЩЕЕ ИЛИ. инвертор 13, четвертый 14 триггер, второй 15 блок временной задержки, элемент 16 И, второй 17 блок коммутации и выходную шину 18.

Первый блок временной задержки предназначен для временной задержки тактового сигнала, подаваемого на счетный вход первого триггера, с целью обеспечения совпадения по времени фронтов тактового сигнала и цифрового сигнала, подаваемого на разрешающий вход первого триггера, что необходимо для формирования всех сигналов кроме относительного биимпульсного. Временная задержка может быть осуществлена, например, с помощью интегрирующей цепи при соответствующем подборе ее параметров.

Аналогично может быть построен второй блок временной задержки, осуществляющий задержку сигнала на время, равное Т/2 (Т - тактовый интервал).

Первый и второй блоки коммутации содержит наборы механических или электронных ключей, с помощью которых осуществляется выбор формируемого сигнала.

Остальные блоки являются стандартными блоками электросвязи.

Устройство для формирования цифровых сигналов работает следующим образом.

На разрешающий вход первого 1 триггера подается исходный цифровой сигнал типа NRZ-L, подлежащий преобразованию в один из следующих сигналов: относительный биимпульсный, RZ, BI-L, NRZ-S, BI-M, DBI и МИЛЛЕР.

Относительный биимпульсный сигнал формируется с помощью триггеров 1 и 2 и

элемента 12 ИСКЛЮЧАЮЩЕЕ ИЛИ.

Цифровой сигнал NRZ-L (фиг.2а) с первой управляющей шины 4 поступает на разрешающий вход первого триггера 1, на счетный вход которого поступает сигнал с

0 первой тактовой шины 3 (фиг.2б). Первый триггер 1 переключается под воздействием перехода из низкого уровня в высокий сигнала с первой тактовой шины (фиг.2б);если информационный сигнал с первой управля5 ющей шины 4 (фиг.2а) на его разрешающем входе имеет высокий уровень. В противном случае первый триггер 1 не переключается. Аналогично второй триггер 1 переключается под воздействием перехода из низкого

0

уровня в высокий сигнал со второй тактовой

шины 5, инверсной по отношению к первой тактовой шине 3 (фиг.2г), поступающего на его синхронизирующий вход, если синхросигнал (фиг.2в),подаваемый на его разреша5 ющий вход со второй управляющей шины 6, имеет высокий уровень.В противном случае переключение не происходит.

Выходные сигналы первого 1 и второго 2 триггеров (фиг.2д,е) поступают на четвер0 тый и пятый входы первого 11 блока коммутации, в котором предварительно произведены соответствующие переключения с тем, чтобы на его первый и второй выход коммутировались сигналы соответст5 венно с второго и третьего входов. Таким образом, выходные сигналы триггеров 1 и 2 поступают на входы элемента 1.2 ИСКЛЮЧАЮЩЕЕ ИЛИ, где они суммируются по модулю 2. Выходной сигнал этого элемента

0 (фиг.2л) представляет собой относительный биимпульсный сигнал, в котором в середине каждого тактового интервала обязательно имеется переход от одного уровня к другому, за исключением тех тактовых интерва5 лов, в которых передается сигнал с второй управляющей шины 6. На границах тактовых интервалов переход от одного уровня к другому имеется при наличии 1 с первой управляющей шины 4 (фиг.2а) и отсутствует

0 при наличии О,

Выходной сигнал элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подается на второй вход второго 17 блока коммутации, который предварительно подготавливается для ком5 мутации сигнала с этого входа на выход устройства.

Сигнал RZ (фиг.Зп) формируется из сигнала NRZ-L путем уменьшения длительностей токовых посылок в два раза. Эту операцию производит элемент 16 И. на первый вход которого подается сигнал NRZ-L (фиг.За), а на второй - сигнал тактовой частоты (фиг.Зж) с выхода первого 7 блока временной задержки, Полученный на выходе элемента И сигнал RZ коммутируется на вы- ход устройства с шестого входа второго 17 блока коммутации.

Алгоритм формирования сигнала NRZ-L (фиг.Зк) заключается в следующем: символу 1 исходного сигнала NRZ-L (фйг.За) соот- ветствует повторение предыдущего элемента сигнала, а символу О - появление альтернативного сигнала. Сигнал NRZ-L формируется с помощью элементов 8, 9, 10 и 11. На входы элемента 8 ИЛ И-НЕ подают- ся сигнал NRZ-L (фиг.За) и тактовый сигнал (фиг.Зж). На выходе элемента 8 формируется сигнал,приведенный на фиг.Зз, который поступает на один из входов элемента 9 ИЛИ. На второй вход элемента ИЛИ пода- ется сигнал NRZ-L. Выходной сигнал элемента 9 (фиг.Зи) поступает на счетный вход Т-триггера 10, на выходе которого формируется сигнал NRZ-S (фиг.Зк). Этот сигнал коммутируется на выход устройства с шестого входа второго 17,блока коммутации.

Алгоритм формирования сигнала BI-L (фиг.4м) заключается в следующем: символы 1 и О в исходном сигнале NRZ-L (фиг.4а) представляется соответственно блоками символов 01 и 10.

Для формирования сигнала BI-L на входы элемента 12 ИСКЛЮЧАЮЩЕЕ ИЛИ с первого и второго входов первого 11 блока коммутации коммутируются сигнал NRZ-L (фиг.4а) и тактовый сигнал с выхода блока 7 временной задержки (фиг.4ж).

Эти сигналы суммируются по модулю 2 (фиг.4л). Далее полученный в результате суммирования сигнал инвертируется в ин- верторе 13, на выходе которого формируется сигнал BI-L (фиг.4м). Этот сигнал поступает на третий вход второго 17 блока коммутации, откуда коммутируется на выход последнего.

Алгоритм формирования сигнала МИЛЛЕР заключается в следующем: символы О исходной последовательности кодируется поочередно высоким и низким уровнями на тактовых интервалах, а символы 1 блока- ми 10 и 01, но так, чтобы первый символ блока совпадал с предыдущим символом. Этот алгоритм реализуется с помощью счетного 14 триггера, на счетный вход которого подается сигнал BI-L (фиг.4м). Сформиро- ванный на выходе этого триггера сигнал МИЛЛЕР (фиг.4о) поступает на пятый вход второго 17 блока коммутации, откуда коммутируется на выход устройства. Таким образом для формирования кода МИЛЛЕР

необходимо предварительно получать код BI-L.

Правило формирования кода ДВ1 состоит в том, что как символ 1 исходной последовательности, так и символ О кодируются блоками 01 или 10. При этом символу 1 исходной последовательности соответствует отсутствие перехода блока 01 (или 10) в альтернативное состояние (повторяется блок предшествующего состояния), а символу О соответствует переход (формируется блок, отличный от предшествующего).

Для формирования сигнала ДВ1 используются сигналы NRZ-S, получаемый на выходе блока 10 (фиг.Зк) и тактовый сигнал, формируемый на выходе блока 7. Формирование кода ДВ1 происходит следующим образом.

Сигнал NRZ-S (фиг.5к) подается на четвертый вход первого 1.1 блока коммутации, на пятый вход которого поступает тактовый сигнал (фиг.5ж)с выхода блока 7. Эти сигналы коммутируются на выходы блока коммутации и подаются на входы элемента 12 ИСКЛЮЧАЮЩЕЕ ИЛИ. На выходе элемента 12 формируется сигнал ДВ1 (фиг.5л),кото- рый с второго входа второго 17 блока коммутации коммутируется на выход устройства.

Сигнал BI-M отличается от сигнала ДВ1 только сдвигом на длительность половины тактового интервала. Эта задержка осуществляется во втором 15 блоке временной задержки. На вход блока 15 подается сигнал ДВ1 (фиг.5л), а на выходе формируется сигнал BI-M, который через четвертый вход второго 17 блока коммутации поступает на выход устройства.

Формулаизобретения

Устройство для формирования цифровых сигналов, содержащее первый триггер, синхронизирующий вход которого соединен с первой тактовой шиной, разрешающий вход - с первой управляющей шиной, второй триггер, синхронизирующий вход которого соединен с второй тактовой шиной, разрешающий вход - с второй управляющей шиной, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и выходную шину, отличающее- с я тем, что, с целью расширения функциональных возможностей за счет формирования не только относительного биимпульсного сигнала, но и сигналов RZ, BI-L, NRZ-S. BI-M, ДВ-1 и МИЛЛЕР, в него введены третий и четвертый триггеры, инвертор, первый и второй блоки коммутации, элемент ИЛИ-НЕ, элемент ИЛИ, элемент И, первый и второй блоки задержки, причем первый вход элемента ИЛИ-НЕ соединен с первым входом элемента ИЛИ с первым

входом элемента И, с первым входом первого блока коммутации и с первой управляющей шиной, второй вход - с вторым входом блока коммутации, с вторым входом элемента И и через первый блок задержки с первой тактовой шиной, выход - с вторым входом элемента ИЛИ, выход которого соединен со счетным входом третьего триггера, выход которого соединен с первым входом второго блока коммутации и с третьим входом первого блока коммутации, четвертый вход которого соединен с выходом первого и триггера, пятый вход - с выходом второго

триггера, первый и второй выходы - соответственно с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым входом второго блока коммутации, с входом второго блока временной задержки и с входом инвертора, выход которого соединен со счетным входом четвертого триггера и с третьим входом второго блока коммутации, четвертый вход которого соединен с выходом второго блока временной задержки, пятый вход с выходом четвертого триггера, шестой вход - с выходом элемента И, выход - с выходной шиной,

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ БИИМПУЛЬСНОГО СИГНАЛА | 1992 |

|

RU2048706C1 |

| Устройство для формирования биимпульсного сигнала | 1989 |

|

SU1637000A1 |

| ЭЛЕКТРОННЫЙ ЗАМОК | 2002 |

|

RU2213191C1 |

| СПОСОБ КОДИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2168270C2 |

| СПОСОБ КОДИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ | 2002 |

|

RU2215369C1 |

| Управляемая линия задержки | 1990 |

|

SU1725370A2 |

| Биимпульсный регенератор | 1980 |

|

SU892742A1 |

| Устройство цикловой синхронизации | 1983 |

|

SU1332551A1 |

| Биимпульсный регенератор | 1986 |

|

SU1413727A2 |

Изобретение может быть использовано в цифровых системах передачи. Устройство содержит: 4 триггера (1, 2, 10, 14), 2 блока временной задержки (7, 15), 2 блока коммутации (11. 17), 1 элемент ИЛИ-НЕ (8), 1 элемент ИЛИ (9), 1 элемент ИСКЛЮЧАЮЩЕЕ ИЛ И (12), 1 инвертор (13), 1 элемент И (16), 2 тактовые шины (3, 5), 2 управляющие шины (4, 6), 1 выходную шину (18) с соответствующими функциональными связями. 5 ил.

П П

-ппп-пппппплппп-г

„П П

П ПППППП

..пппппппг

„П П П Л

Г

д

п

г

ФИГ./t

К.

ПППП

ЛПППГГППППППППППг Л ПП П П ПППП ПГт

Л ПП П П ПППП ПП

ФИГ. S

| Устройство для передачи и приема цифровых сигналов | 1980 |

|

SU978375A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для формирования относительного биимпульсного сигнала | 1986 |

|

SU1396255A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-03-15—Публикация

1991-04-22—Подача