Изобретение относится к автоматике и вычислительной технике и может использоваться в системах управления принятием решений.

Цель изобретения состоит в повышении быстродействия устройства.

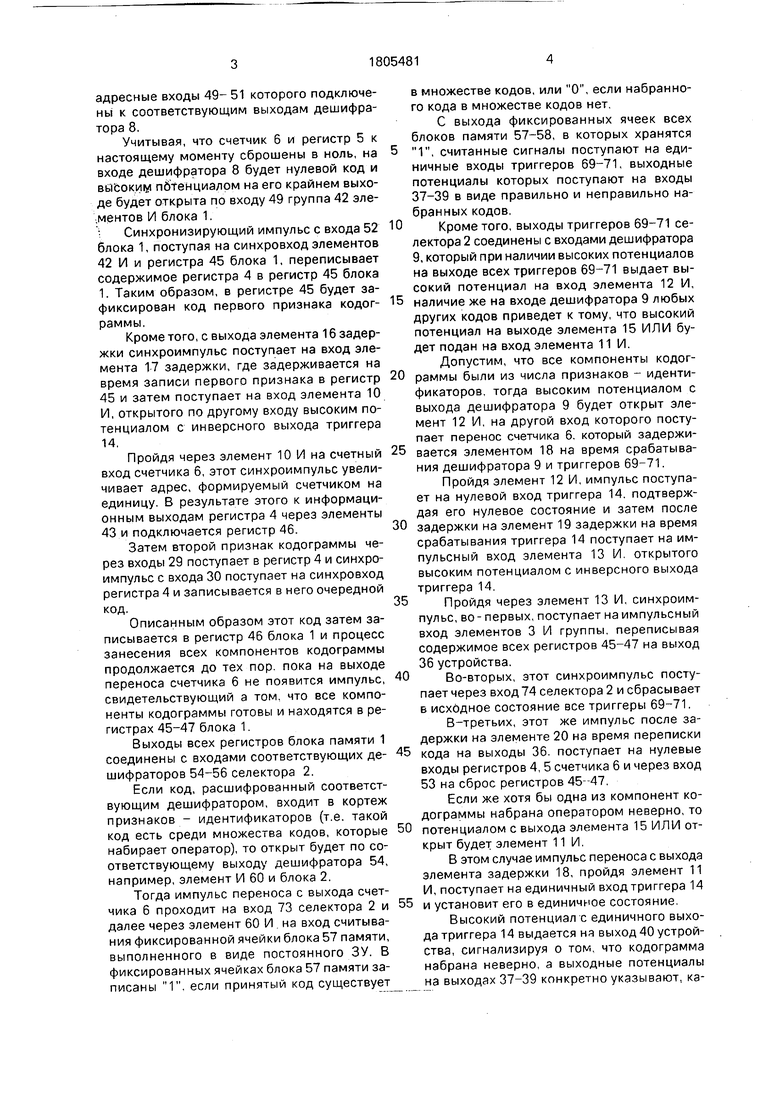

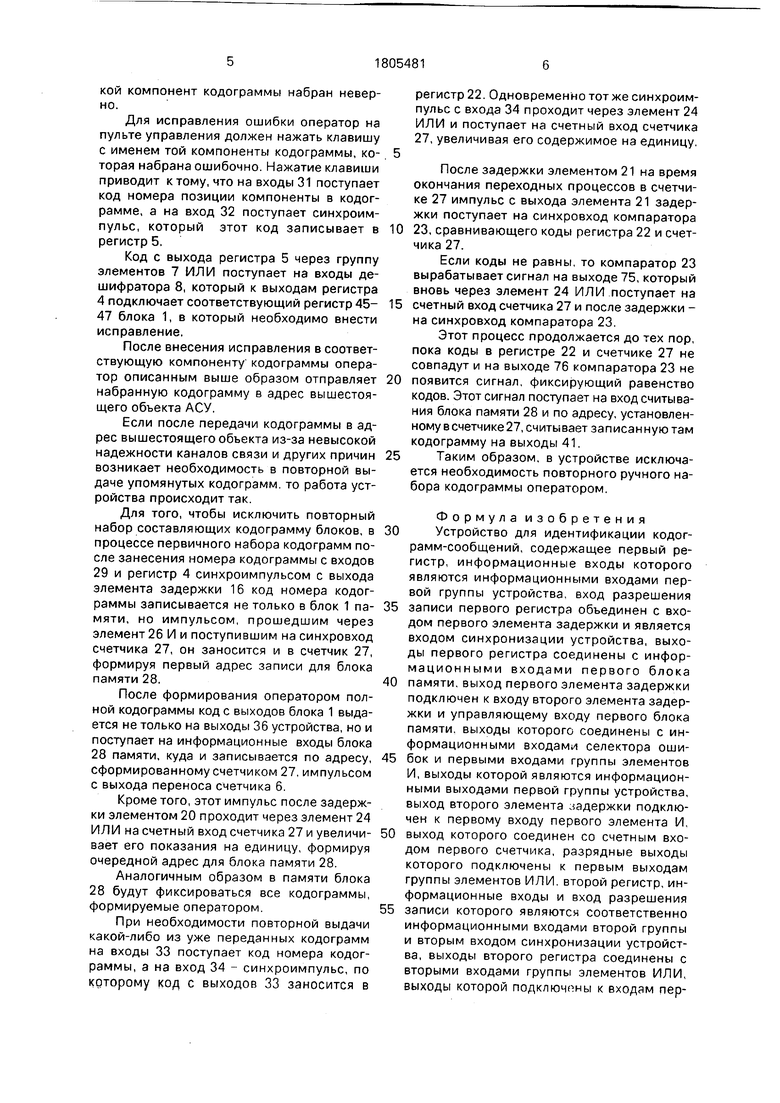

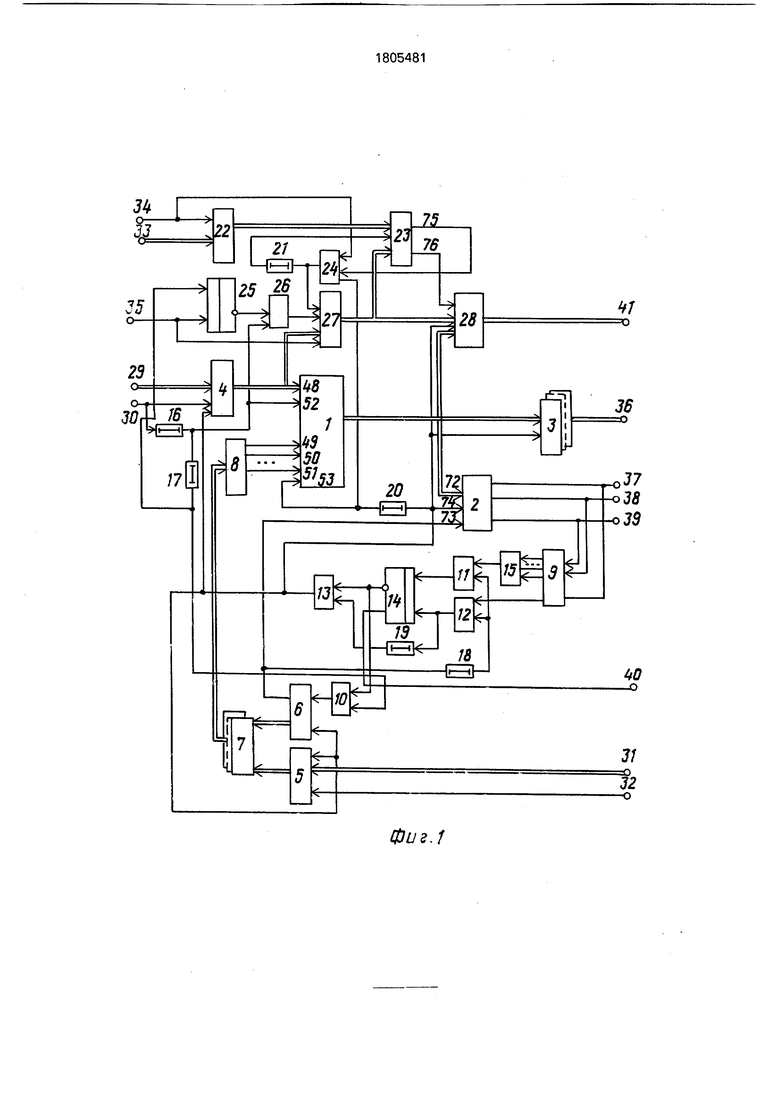

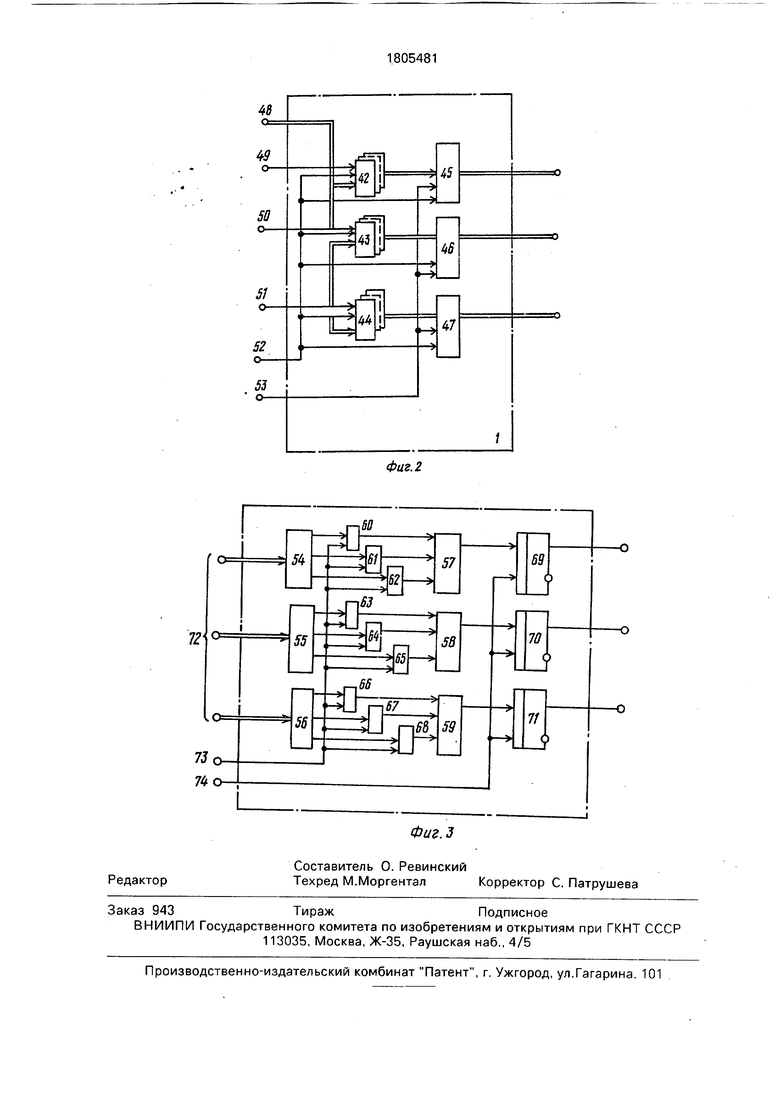

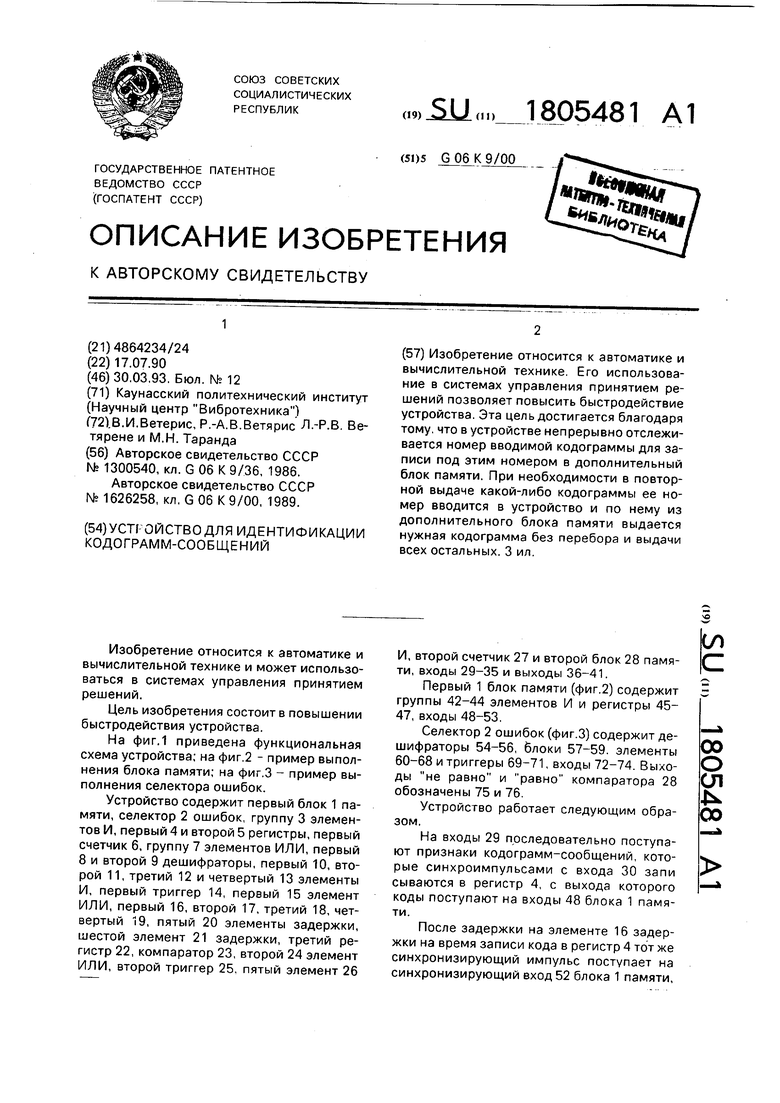

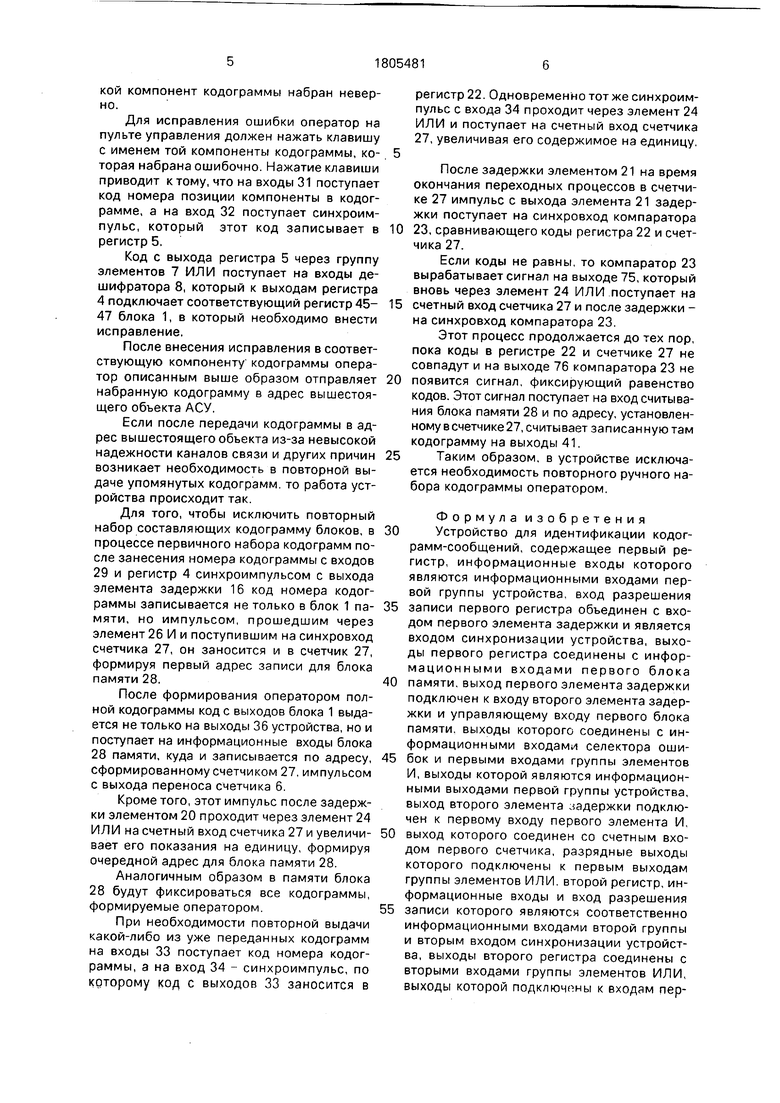

На фиг.1 приведена функциональная схема устройства; на фиг.2 - пример выполнения блока памяти; на фиг.З - пример выполнения селектора ошибок.

Устройство содержит первый блок 1 памяти, селектор 2 ошибок, группу 3 элементов И, первый 4 и второй 5 регистры, первый счетчик 6, группу 7 элементов ИЛИ, первый 8 и второй 9 дешифраторы, первый 10, второй 11, третий 12 и четвертый 13 элементы И, первый триггер 14, первый 15 элемент ИЛИ, первый 16, второй 17, третий 18, четвертый 19, пятый 20 элементы задержки, шестой элемент 21 задержки, третий регистр 22, компаратор 23, второй 24 элемент ИЛИ, второй триггер 25, пятый элемент 26

И, второй счетчик 27 и второй блок 28 памяти, входы 29-35 и выходы 36-41.

Первый 1 блок памяти (фиг.2) содержит группы 42-44 элементов И и регистры 45- 47, входы 48-53.

Селектор 2 ошибок (фиг.З) содержит дешифраторы 54-56, блоки 57-59. элементы 60-68 и триггеры 69-71, входы 72-74. Выходы не равно и равно компаратора 28 обозначены 75 и 76.

Устройство работает следующим образом.

На входы 29 последовательно поступают признаки кодограмм-сообщений, которые синхроимпульсами с входа 30 запи сываются в регистр 4, с выхода которого коды поступают на входы 48 блока 1 памяти.

После задержки на элементе 16 задержки на время записи кода в регистр 4 тот же синхронизирующий импульс поступает на синхронизирующий вход 52 блока 1 памяти,

00

о ел

00

адресные входы 49- 51 которого подключены к соответствующим выходам дешифратора 8.

Учитывая, что счетчик 6 и регистр 5 к настоящему моменту сброшены в ноль, на входе дешифратора 8 будет нулевой код и высоким пбтенциалрм на его крайнем выходе будет открыта по входу 49 группа 42 элементов И блока 1.

Синхронизирующий импульс с входа 52 блока 1, поступая на синхровход элементов 42 И и регистра 45 блока 1, переписывает содержимое регистра 4 в регистр 45 блока 1. Таким образом, в регистре 45 будет зафиксирован код первого признака кодог- раммы.

Кроме того, с выхода элемента 16 задержки синхроимпульс поступает на вход элемента 17 задержки, где задерживается на время записи первого признака в регистр 45 и затем поступает на вход элемента 10 И, открытого по другому входу высоким потенциалом с инверсного выхода триггера 14,

Пройдя через элемент 10 И на счетный вход счетчика 6, этот синхроимпульс увеличивает адрес, формируемый счетчиком на единицу. В результате этого к информационным выходам регистра 4 через элементы 43 и подключается регистр 46.

Затем второй признак кодограммы через входы 29 поступает в регистр 4 и синхроимпульс с входа 30 поступает на синхровход регистра 4 и записывается в него очередной

код.

Описанным образом этот код затем записывается в регистр 46 блока 1 и процесс занесения всех компонентов кодограммы продолжается до тех пор. пока на выходе переноса счетчика 6 не появится импульс, свидетельствующий а том, что все компоненты кодограммы готовы и находятся в регистрах 45-47 блока 1.

Выходы всех регистров блока памяти 1 соединены с входами соответствующих де- шифраторов 54-56 селектора 2.

Если код, расшифрованный соответствующим дешифратором, входит в кортеж признаков - идентификаторов (т.е. такой код есть среди множества кодов, которые набирает оператор), то открыт будет по соответствующему выходу дешифратора 54, например, элемент И 60 и блока 2.

Тогда импульс переноса с выхода счетчика 6 проходит на вход 73 селектора 2 и далее через элемент 60 И. на вход считывания фиксированной ячейки блока 57 памяти, выполненного в виде постоянного ЗУ. В фиксированных ячейках блока 57 памяти записаны 1. если принятый код существует

5

0

5 0

5

0

5

0

5

в множестве кодов, или О, если набранного кода в множестве кодов нет,

С выхода фиксированных ячеек всех блоков памяти 57-58, в которых хранятся 1, считанные сигналы поступают на единичные входы триггеров 69-71, выходные потенциалы которых поступают на входы 37-39 в виде правильно и неправильно набранных кодов.

Кроме того, выходы триггеров 69-71 селектора 2 соединены с входами дешифратора 9, который при наличии высоких потенциалов на выходе всех триггеров 69-71 выдает высокий потенциал на вход элемента 12 И, наличие же на входе дешифратора 9 любых других кодов приведет к тому, что высокий потенциал на выходе элемента 15 ИЛИ будет подан на вход элемента 11 И.

Допустим, что все компоненты кодограммы были из числа признаков - идентификаторов, тогда высоким потенциалом с выхода дешифратора 9 будет открыт элемент 12 И, на другой вход которого поступает перенос счетчика 6. который задерживается элементом 18 на время срабатывания дешифратора 9 и триггеров 69-71.

Пройдя элемент 12 И, импульс поступает на нулевой вход триггера 14. подтверждая его нулевое состояние и затем после задержки на элемент 19 задержки на время срабатывания триггера 14 поступает на импульсный вход элемента 13 И. открытого высоким потенциалом с инверсного выхода триггера 14.

Пройдя через элемент 13 И, синхроимпульс, во-первых, поступает на импульсный вход элементов 3 И группы, переписывая содержимое всех регистров 45-47 на выход 36 устройства.

Во-вторых, этот синхроимпульс поступает через вход 74 селектора 2 и сбрасывает в исходное состояние все триггеры 69-71.

В-третьих, этот же импульс после задержки на элементе 20 на время переписки кода на выходы 36. поступает на нулевые входы регистров 4, 5 счетчика 6 и через вход 53 на сброс регистров 45-47.

Если же хотя бы одна из компонент кодограммы набрана оператором неверно, то потенциалом с выхода элемента 15 ИЛИ открыт будет элемент 11 И.

В этом случае импульс переноса с выхода элемента задержки 18, пройдя элемент 11 И, поступает на единичный вход триггера 14 и установит его в единичное состояние.

Высокий потенциал с единичного выхода триггера 14 выдается на выход 40 устройства, сигнализируя о том, что кодограмма набрана неверно, а выходные потенциалы на выходах 37-39 конкретно указывают, какой компонент кодограммы набран неверно.

Для исправления ошибки оператор на пульте управления должен нажать клавишу с именем той компоненты кодограммы, которая набрана ошибочно. Нажатие клавиши приводит к тому, что на входы 31 поступает код номера позиции компоненты в кодограмме, а на вход 32 поступает синхроимпульс, который этот код записывает в регистр 5.

Код с выхода регистра 5 через группу элементов 7 ИЛИ поступает на входы дешифратора 8, который к выходам регистра 4 подключает соответствующий регистр 45- 47 блока 1, в который необходимо внести исправление.

После внесения исправления в соответствующую компоненту кодограммы оператор описанным выше образом отправляет набранную кодограмму в адрес вышестоящего объекта АСУ.

Если после передачи кодограммы в адрес вышестоящего объекта из-за невысокой надежности каналов связи и других причин возникает необходимость в повторной выдаче упомянутых кодограмм, то работа устройства происходит так.

Для того, чтобы исключить повторный набор составляющих кодограмму блоков, в процессе первичного набора кодограмм после занесения номера кодограммы с входов 29 и регистр 4 синхроимпульсом с выхода элемента задержки 16 код номера кодограммы записывается не только в блок 1 памяти, но импульсом, прошедшим через элемент 26 И и поступившим на синхровход счетчика 27, он заносится и в счетчик 27, формируя первый адрес записи для блока памяти 28.

После формирования оператором полной кодограммы код с выходов блока 1 выдается не только на выходы 36 устройства, но и поступает на информационные входы блока 28 памяти, куда и записывается по адресу, сформированному счетчиком 27, импульсом с выхода переноса счетчика 6.

Кроме того, этот импульс после задержки элементом 20 проходит через элемент 24 ИЛИ на счетный вход счетчика 27 и увеличивает его показания на единицу, формируя очередной адрес для блока памяти 28.

Аналогичным образом в памяти блока 28 будут фиксироваться все кодограммы, формируемые оператором.

При необходимости повторной выдачи какой-либо из уже переданных кодограмм на входы 33 поступает код номера кодограммы, а на вход 34 - синхроимпульс, по которому код с выходов 33 заносится в

регистр 22. Одновременно тот же синхроимпульс с входа 34 проходит через элемент 24 ИЛИ и поступает на счетный вход счетчика 27, увеличивая его содержимое на единицу.

После задержки элементом 21 на время окончания переходных процессов в счетчике 27 импульс с выхода элемента 21 задержки поступает на синхровход компаратора

23, сравнивающего коды регистра 22 и счетчика 27.

Если коды не равны, то компаратор 23 вырабатывает сигнал на выходе 75, который вновь через элемент 24 ИЛИ поступает на

счетный вход счетчика 27 и после задержки - на синхровход компаратора 23.

Этот процесс продолжается до тех пор, пока коды в регистре 22 и счетчике 27 не совпадут и на выходе 76 компаратора 23 не

появится сигнал, фиксирующий равенство кодов. Этот сигнал поступает на вход считывания блока памяти 28 и по адресу, установленному всчетчике27, считывает записанную там кодограмму на выходы 41.

Таким образом, в устройстве исключается необходимость повторного ручного набора кодограммы оператором.

Формула изобретения

Устройство для идентификации кодограмм-сообщений, содержащее первый регистр, информационные входы которого являются информационными входами первой группы устройства, вход разрешения

записи первого регистра объединен с входом первого элемента задержки и является входом синхронизации устройства, выходы первого регистра соединены с информационными входами первого блока

памяти, выход первого элемента задержки подключен к входу второго элемента задержки и управляющему входу первого блока памяти, выходы которого соединены с информационными входами селектора ошибок и первыми входами группы элементов И, выходы которой являются информационными выходами первой группы устройства, выход второго элемента задержки подключен к первому входу первого элемента И.

выход которого соединен со счетным входом первого счетчика, разрядные выходы которого подключены к первым выходам группы элементов ИЛИ. второй регистр, информационные входы и вход разрешения

записи которого являются соответственно информационными входами второй группы и вторым входом синхронизации устройства, выходы второго регистра соединены с вторыми входами группы элементов ИЛИ, выходы которой подключены к входам первого дешифратора, выходы которого соединены с адресными входами первого блока памяти, выходы селектора ошибок подключены к входам второго дешифратора и являются информационными выходами второй группы устройства, первые выходы второго дешифратора соединены с входами первого элемента ИЛИ, выход которого и второй выход дешифратора подключены к первым входам соответственно второго и третьего элементов И, выход переполнения первого счетчика соединен непосредственно и через третий элемент задержки соответствен- но с управляющим входом селектора ошибок и вторыми входами второго и третьего элементов И, выход второго элемента И подключен к единичному входу первого триггера, прямой выход которого является контрольным выходом устройства, выход третьего элемента I/I через четвертый элемент задержки и непосредственно соединен соответственно с первым входом четвертого элемента И и нулевым входом первого триггера, инверсный выход которого подключен к входам первого и четвертого элементов И. выход четвертого элемента И соединен с входами обнуления первого и второго регистров, первого счетчика и селектора ошибок, с вторым входом группы элементов И и входом пятого элемента задержки, выход которого подключен к управляющему входу первого блока памяти, о т л и чающееся тем, что, с целью повышения быстродействия устройства, в него введены второй триггер, второй блок памяти, второй счетчик, пятый элемент И. второй элемент ИЛИ, шестой элемент задержки, компаратор и третий регистр, информационные вхои

10

15

20

25

30

35

ды которого являются информационными входами третьей группы устройства, вход разрешения записи третьего регистра объединен с первым входом второго элемента ИЛИ и является третьим входом синхронизации устройства, выходы третьего регистра подключены к информационным входам первой группы компаратора, выход Не равно которого соединен с вторым входом второго элемента ИЛИ, третий вход которого подключен выходу пятого элемента задержки, выход второго элемента ИЛИ через шестой элемент задержки и непосредственно соединен соответственно с управляющим входом компаратора и счетным входом второго счетчика, входы установки которого подключены к выходам первого регистра, а вход обнуления объединен с нулевым входом второго триггера и является входом обнуления устройства, единичный вход второго триггера подключен к выходу второго элемента задержки, а инверсный выход соединен с первым входом пятого элемента И, второй вход и выход которого подключены соответственно к выходу первого элемента задержки и входу разрешения записи второго счетчика, выходы которого соединены с информационными входами второй группы компаратора и адресными входами второго блока памяти, информационные входы и вход разрешения записи которого подключены соответственно к выходам первого блока памяти и выходу четвертого элемента задержки, выход Равно компаратора соединен с входом разрешения считывания второго блока памяти, выходы которого являются информационными выходами второй группы устройства.

Фиг-f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля работы оператора | 1990 |

|

SU1718263A2 |

| Устройство для контроля работы оператора | 1989 |

|

SU1619330A1 |

| Устройство для идентификации признаков объектов | 1989 |

|

SU1626258A1 |

| Устройство для ввода информации | 1990 |

|

SU1709294A1 |

| Устройство для распознавания образов | 1991 |

|

SU1798806A1 |

| Устройство для записи информации в блок памяти | 1990 |

|

SU1730680A1 |

| Устройство для ввода информации | 1988 |

|

SU1599851A1 |

| Устройство для обмена информацией | 1989 |

|

SU1644149A1 |

| СИСТЕМА УПРАВЛЕНИЯ ВЫБОРКОЙ И ОБРАБОТКОЙ ДАННЫХ ГОСУДАРСТВЕННОГО РЕГИСТРА НАСЕЛЕНИЯ | 2004 |

|

RU2277721C1 |

| СИСТЕМА УПРАВЛЕНИЯ РАСПРЕДЕЛЕНИЕМ ДАННЫХ В ИНФОРМАЦИОННОЙ СЕТИ ГАС "ВЫБОРЫ" | 2003 |

|

RU2239229C1 |

Изобретение относится к автоматике и вычислительной технике. Его использование в системах управления принятием решений позволяет повысить быстродействие устройства. Эта цель достигается благодаря тому, что в устройстве непрерывно отслеживается номер вводимой кодограммы для записи под этим номером в дополнительный блок памяти. При необходимости в повторной выдаче какой-либо кодограммы ее номер вводится в устройство и по нему из дополнительного блока памяти выдается нужная кодограмма без перебора и выдачи всех остальных. 3 ил.

| Устройство для управления вызовом информации | 1985 |

|

SU1300540A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для идентификации признаков объектов | 1989 |

|

SU1626258A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-03-30—Публикация

1990-07-17—Подача