Изобретение относится к измерительной технике и может быть использовано в информационно-измерительных системах, гибридных вычислительных комплексах, системах автоматики, регулирования и контроля.

Цель изобретения - повышение точности устройства.

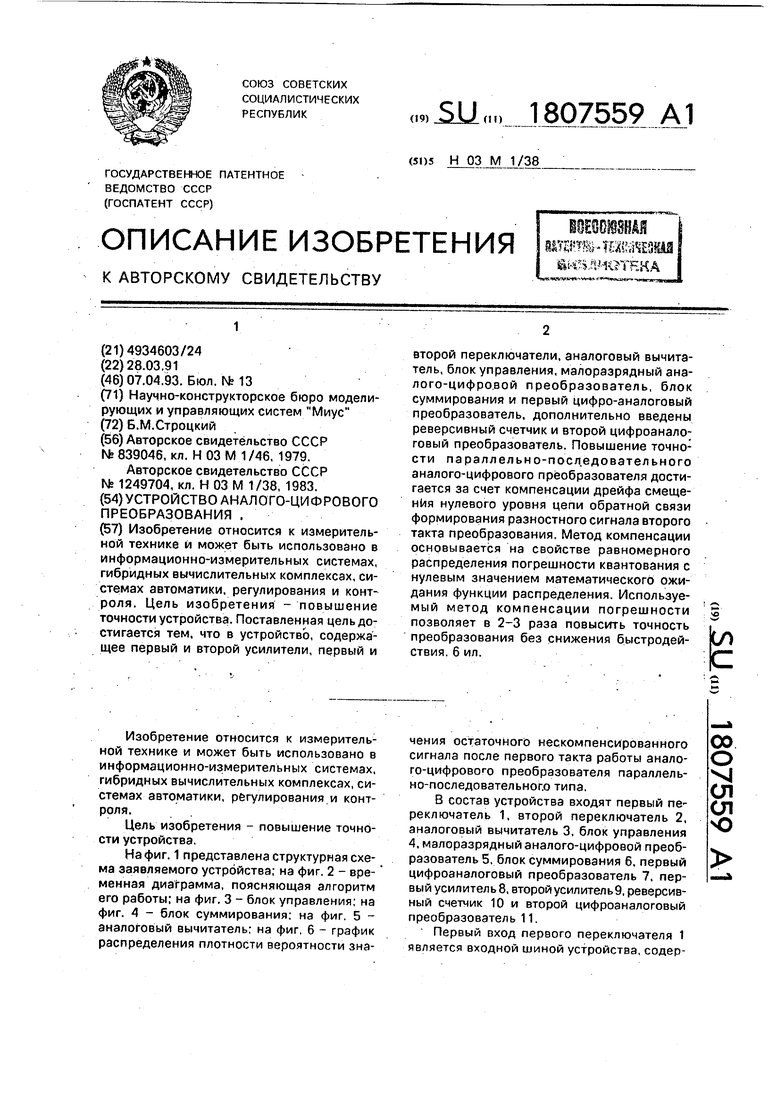

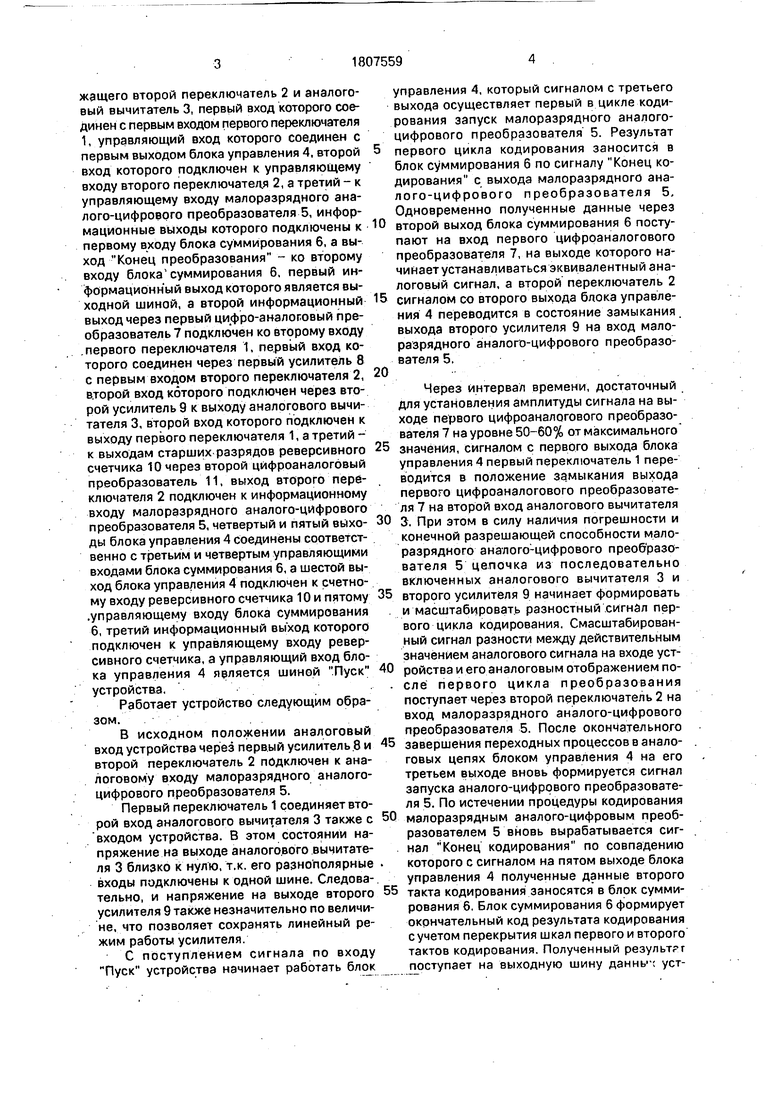

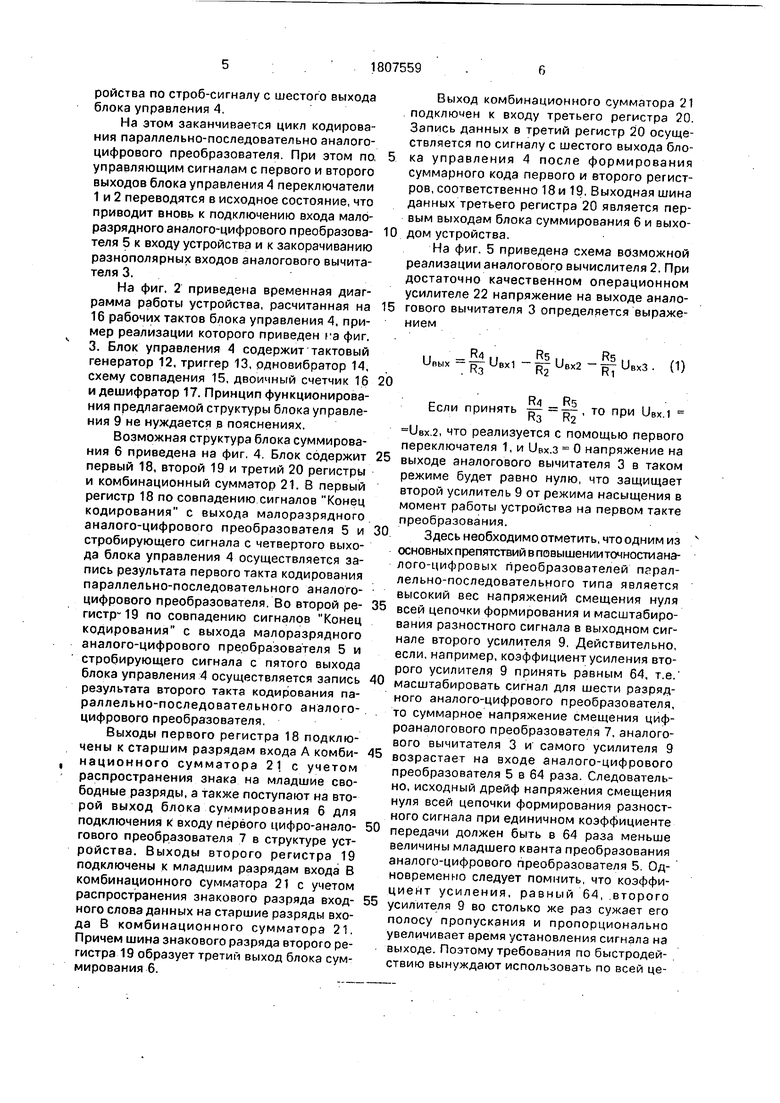

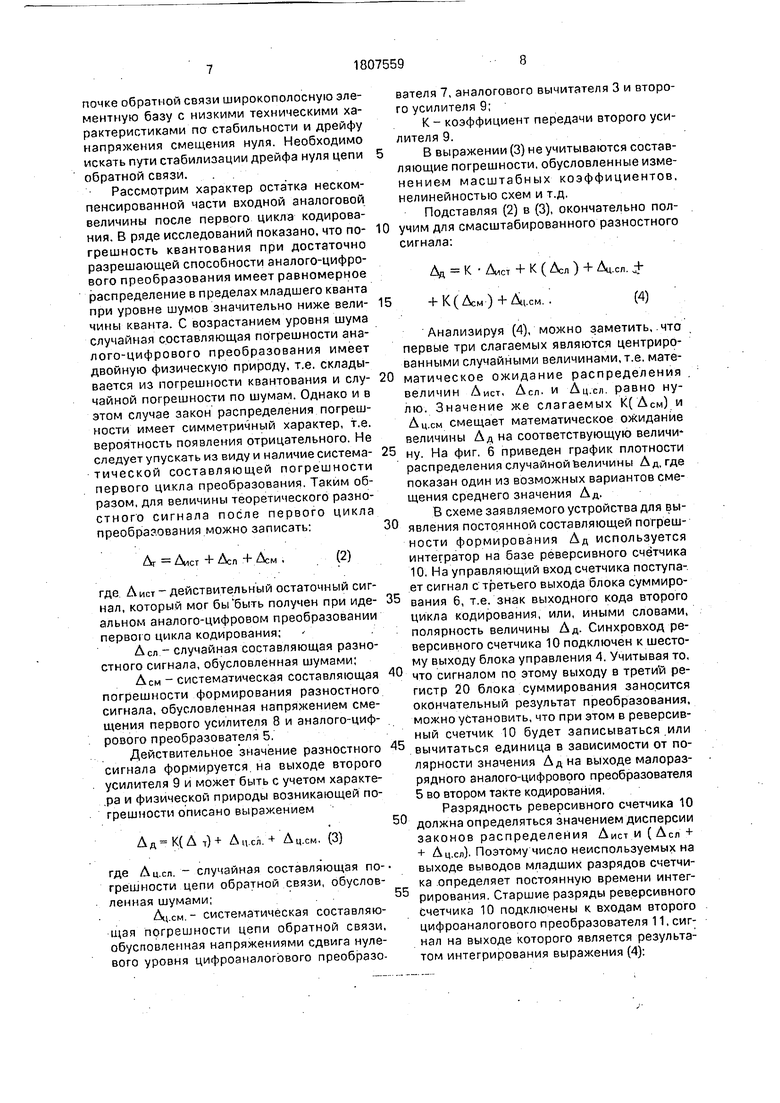

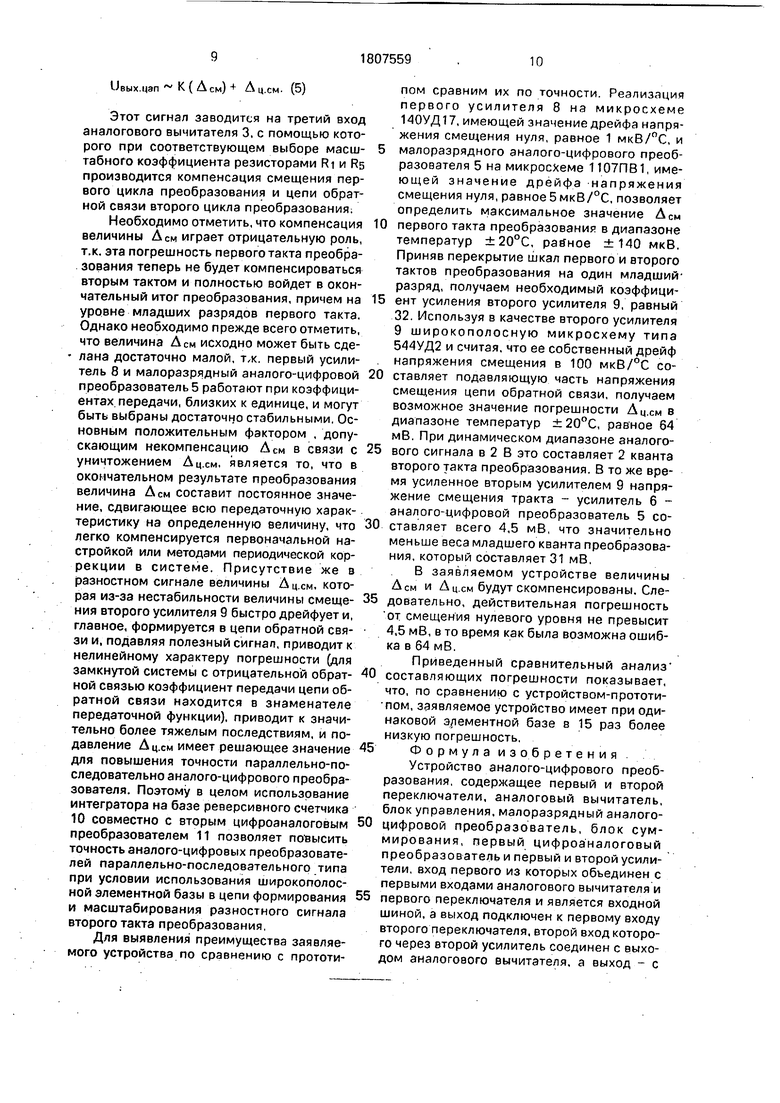

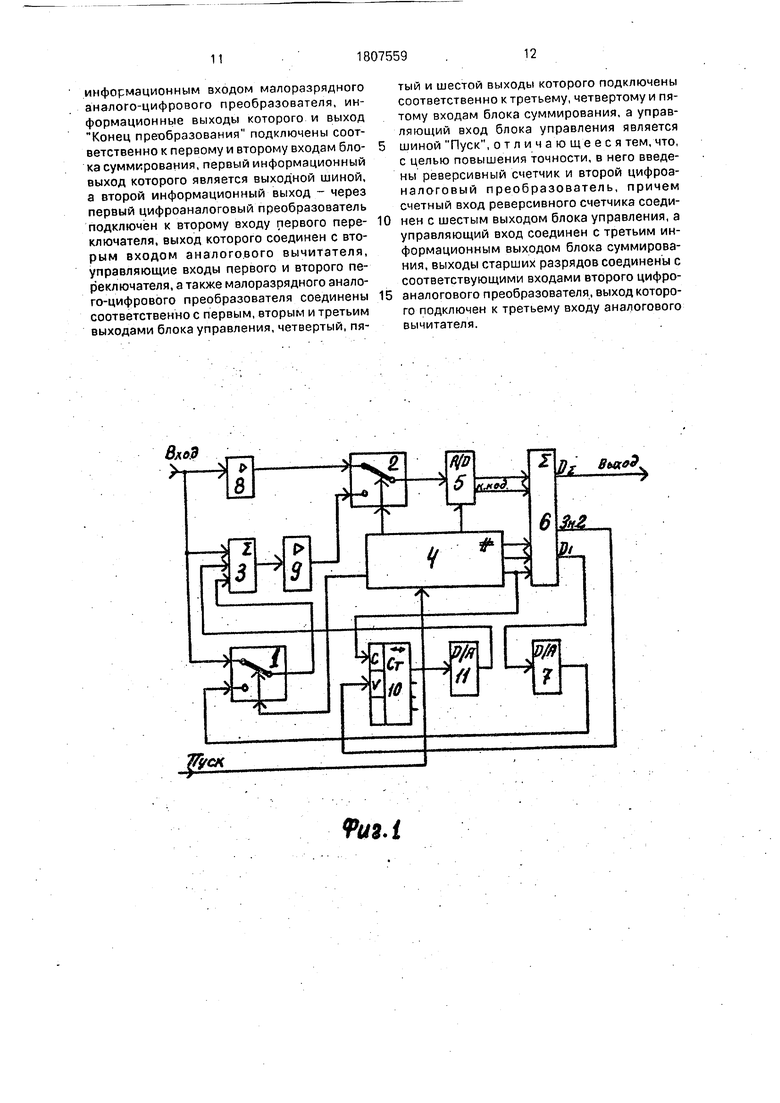

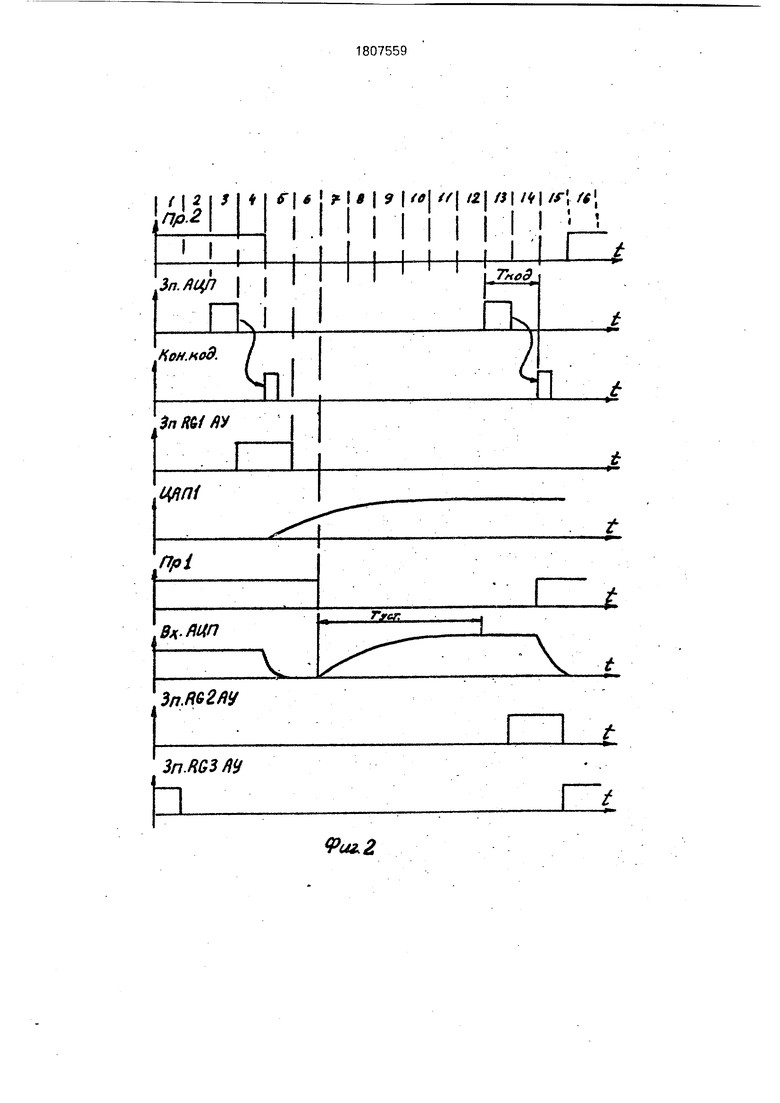

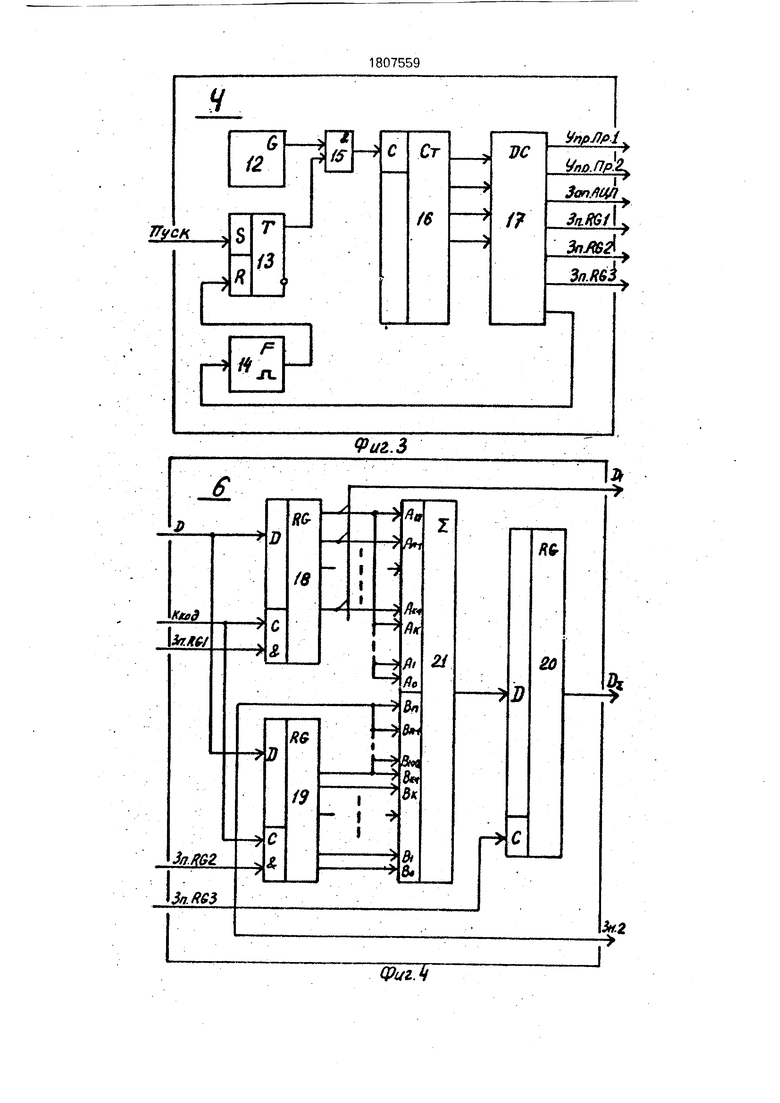

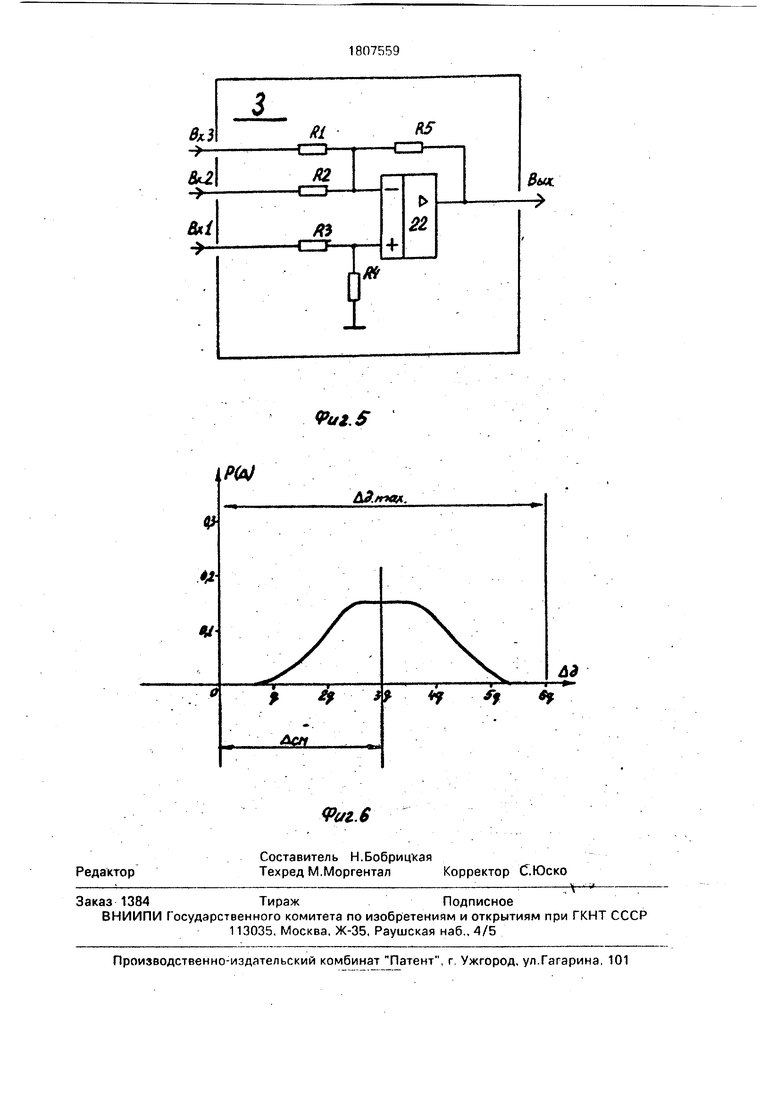

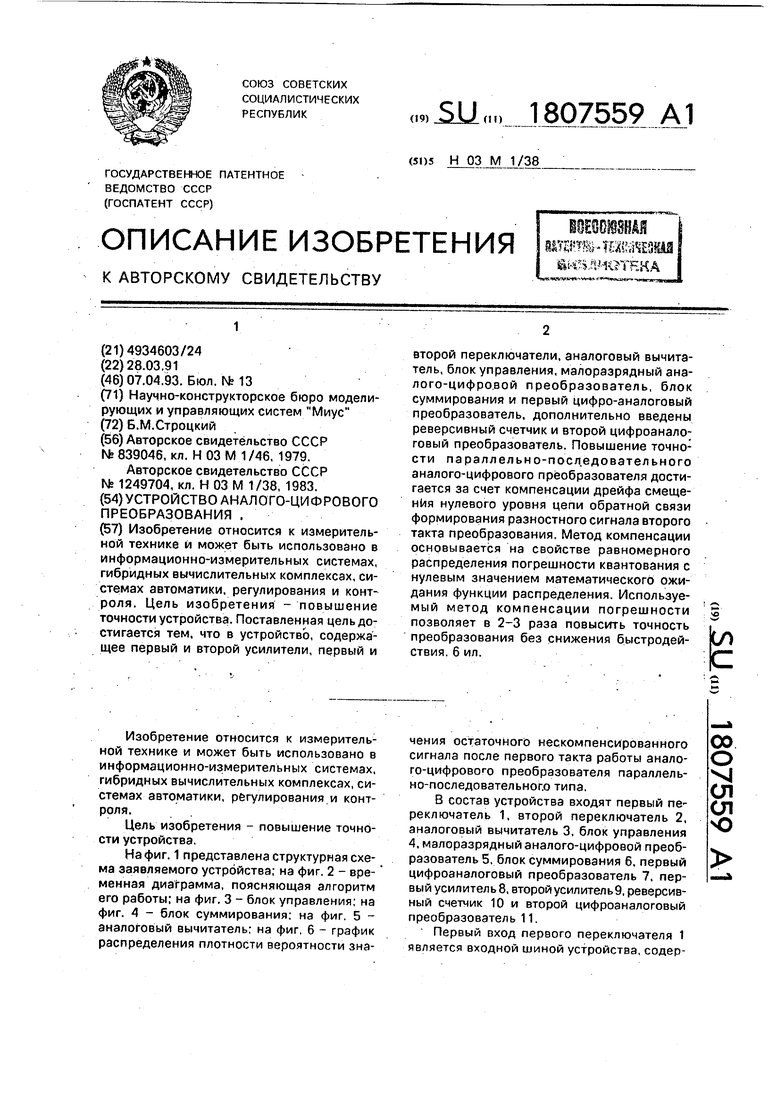

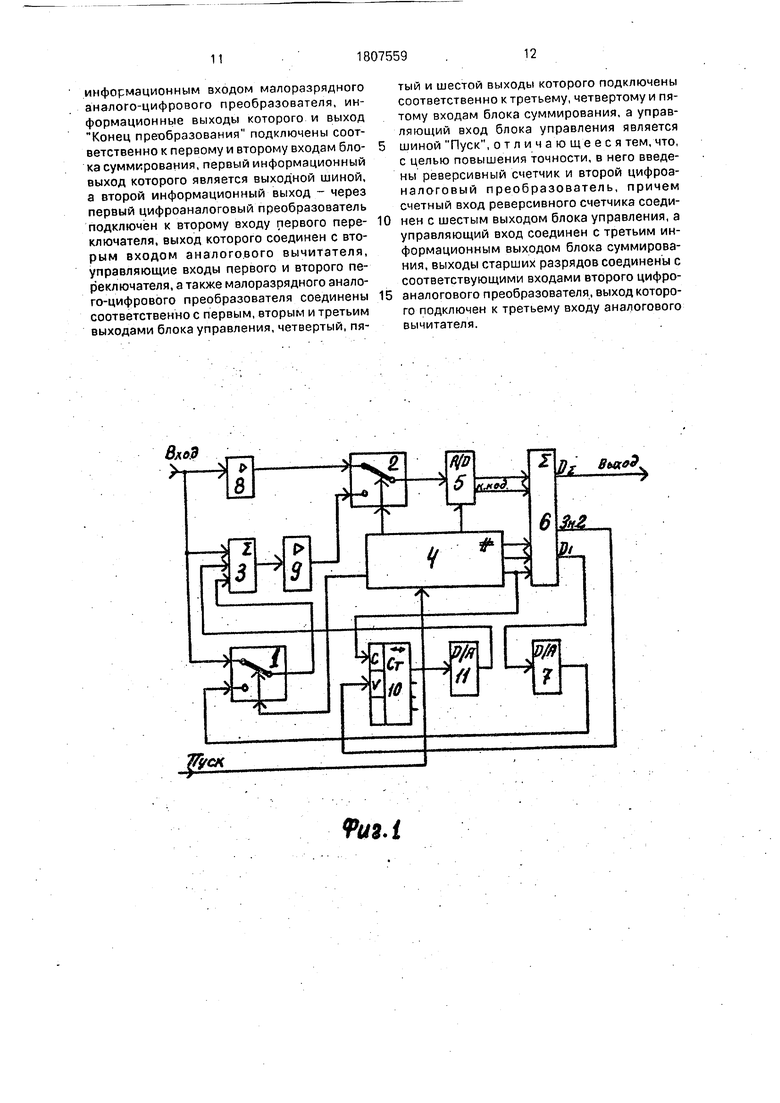

На фиг. 1 представлена структурная схема заявляемого устройства; на фиг. 2 - вре- менная диаграмма, поясняющая алгоритм его работы; на фиг. 3 - блок управления; на фиг. 4 - блок суммирования; на фиг. 5 - аналоговый вычитатель; на фиг. 6 - график распределения плотности вероятности значения остаточного нескомпенсированного сигнала после первого такта работы аналого-цифрового преобразователя параллельно-последовательного типа.

В состав устройства входят первый переключатель 1, второй переключатель 2, аналоговый вычитатель 3, блок управления 4, малоразрядный аналого-цифровой преобразователь 5. блок суммирования 6, первый цифроаналоговый преобразователь 7, первый усилитель 8, второй усилитель 9, реверсивный счетчик 10 и второй цифроаналоговый преобразователь 11.

Первый вход первого переключателя 1 является входной шиной устройства, содер00

о

v|

ел ел ю

жащего второй переключатель 2 и аналоговый вычитатель 3, первый вход которого соединен с первым входом первого переключателя 1, управляющий вход которого соединен с первым выходом блока управления 4, второй вход которого подключен к управляющему входу второго переключатедя 2, а третий - к управляющему входу малоразрядного аналого-цифрового преобразователя 5, информационные выходы которого подключены к первому входу блока суммирования 6, а выход Конец преобразования - ко второму входу блока суммирования б, первый информационный выход которого является выходной шиной, а второй информационный выход через первый цифро-аналоговый преобразователь 7 подключен ко второму входу .первого переключателя 1, первый вход которого соединен через первый усилитель 8 с первым входом второго переключателя 2, второй вход которого подключен через второй усилитель 9 к выходу аналогового вычи- тателя 3, второй вход которого подключен к выходу первого переключателя 1, а третий - к выходам старших разрядов реверсивного счетчика 10 через второй цифроаналоговый преобразователь 11, выход второго переключателя 2 подключен к информационному входу малоразрядного аналого-цифрового преобразователя 5, четвертый и пятый выходы блока управления 4 соединены соответственно с третьим и четвертым управляющими входами блока суммирования 6, а шестой выход блока управления 4 подключен к счетному входу реверсивного счетчика 10 и пятому .управляющему входу блока суммирования 6, третий информационный выход которого подключен к управляющему входу реверсивного счетчика, а управляющий вход блока управления 4 является шиной Пуск устройства,

Работает устройство следующим образом.

В исходном положении аналоговый вход устройства через перв.ый усилитель.8 и второй переключатель 2 подключен к аналоговому входу малоразрядного аналого- цифрового преобразователя 5.

Первый переключатель 1 соединяет второй вход аналогового вычитателя 3 также с входом устройства. В этом состоянии напряжение на выходе аналогового вычитателя 3 близко к нулю, т.к. его разнополярные входы подключены к одной шине. Следова-. тельно, и напряжение на выходе второго усилителя 9 также незначительно по величине, что позволяет сохранять линейный режим работы усилителя.

С поступлением сигнала по входу Пуск устройства начинает работать бло

управления 4, который сигналом с третьего выхода осуществляет первый в цикле кодирования запуск малоразрядного аналого- цифрового преобразователя 5. Результат

первого цикла кодирования заносится в блок суммирования б по сигналу Конец кодирования с выхода малоразрядного аналого-цифрового преобразователя 5, Одновременно полученные данные через

второй выход блока суммирования 6 поступают на вход первого цифроаналогового преобразователя 7, на выходе которого начинает устанавливаться эквивалентный аналоговый сигнал, а второй переключатель 2

5 сигналом со второго выхода блока управления 4 переводится в состояние замыкания. выхода второго усилителя 9 на вход малоразрядного аналого-цифрового преобразователя 5.

0

Через Интервал времени, достаточный для установления амплитуды сигнала на выходе первого цифроаналогового преобразователя 7 на уровне 50-60% от максимального

5 значения, сигналом с первого выхода блока управления 4 первый переключатель 1 переводится в положение замыкания выхода первого цифроаналогового преобразователя 7 на второй вход аналогового вычитателя

0 з. При этом в силу наличия погрешности и конечной разрешающей способности малоразрядного аналого-цифрового преобразователя 5 цепочка из последовательно включенных аналогового вычитателя 3 и

5 второго усилителя 9 начинает формировать . и масштабировать разностный сигнал первого цикла кодирования. Смасштабирован- ный сигнал разности между действительным значением аналогового сигнала на входе уст0 ройства и его аналоговым отображением по. слё первого цикла преобразования

поступает через второй переключатель 2 на

вход малоразрядного аналого-цифрового

преобразователя 5. После окончательного

5 завершения переходных процессов в аналоговых цепях блоком управления 4 на его третьем выходе вновь формируется сигнал запуска аналого-цифрового преобразователя 5. По истечении процедуры кодирования

0 малоразрядным аналого-цифровым преобразователем 5 вновь вырабатывается сигнал Конец кодирования по совпадению которого с сигналом на пятом выходе блока управления 4 полученные данные второго

5 такта кодирования заносятся в блок суммирования б. Блок суммирования 6 формирует окончательный код результата кодирования с учетом перекрытия шкал первого и второго тактов кодирования. Полученный результат поступает на выходную шину данну; устройства по строб-сигналу с шестого выхода блока управления 4.

На этом заканчивается цикл кодирования параллельно-последовательно аналого- цифрового преобразователя. При этом по, управляющим сигналам с первого и второго выходов блока управления А переключатели 1 и 2 переводятся в исходное состояние, что приводит вновь к подключению входа малоразрядного аналого-цифрового преобразователя 5 к входу устройства и к закорачиванию рэзнополярных входов аналогового вычита- теля 3.

На фиг, 2 приведена временная диаграмма работы устройства, расчитанная на 16 рабочих тактов блока управления 4, пример реализации которого приведен га фиг. 3. Блок управления 4 содержит тактовый генератор 12, триггер 13, одновибратор 14, схему совпадения 15, двоичный счетчик 16 и дешифратор 17. Принцип функционирования предлагаемой структуры блока управления 9 не нуждается в пояснениях.

Возможная структура блока суммирования 6 приведена на фиг. 4. Блок содержит первый 18, второй 19 и третий 20 регистры и комбинационный сумматор 21. В первый регистр 18 по совпадению сигналов Конец кодирования с выхода малоразрядного аналого-цифрового преобразователя 5 и стробирующего сигнала с четвертого выхода блока управления 4 осуществляется запись результата первого такта кодирования параллельно-последовательного аналого- цифрового преобразователя. Во второй регистр- 19 по совпадению сигналов Конец кодирования с выхода малоразрядного аналого-цифрового преобразователя 5 и стробирующего сигнала с пятого выхода блока управления 4 осуществляется запись результата второго такта кодирования параллельно-последовательного анэлого- цифрового преобразователя.

Выходы первого регистра 18 подключены к старшим разрядам входа А комби- национного сумматора 21 с учетом распространения знака на младшие свободные разряды, а также поступают на второй выход блока суммирования 6 для подключения к входу первого цифро-аналогового преобразователя 7 в структуре устройства. Выходы второго регистра 19 подключены к младшим разрядам входа В комбинационного сумматора 21 с учетом распространения знакового разряда входного слова данных на старшие разряды входа В комбинационного сумматора 21. Причем шина знакового разряда второго регистра 19 образует третий выход блока суммирования 6.

Выход комбинационного сумматора 21 . подключен к входу третьего регистра 20. Запись данных в третий регистр 20 осуществляется по сигналу с шестого выхода блока управления 4 после формирования суммарного кода первого и второго регистров, соответственно 18 и 19. Выходная шина данных третьего регистра 20 является первым выходам блока суммирования б и выходом устройства.

На фиг. 5 приведена схема возможной реализации аналогового вычислителя 2. При достаточно качественном операционном усилителе 22 напряжение на выходе аналогового вычитателя 3 определяется выражением

20

и„ых ЦиВх1 - Uex2 - { UBx3 . (D

5

0

5

0

5

0

5

г-R/J Rg .. Если принять - Б, то при UBX.I

Uex.2, что реализуется с помощью первого переключателя 1, и Uox.3 0 напряжение на выходе аналогового вычитателя 3 в таком режиме будет равно нулю, что защищает второй усилитель 9 от режима насыщения в момент работы устройства на первом такте преобразования.

Здесь необходимо отметить, что одним из основных препятствий вповышенииточностиана- лого-цифровых преобразователей параллельно-последовательного типа является высокий вес напряжений смещения нуля всей цепочки формирования и масштабирования разностного сигнала в выходном сигнале второго усилителя 9. Действительно, если, например, коэффициент усиления второго усилителя 9 принять равным 64, т.е. масштабировать сигнал для шести разрядного аналого-цифрового преобразователя, то суммарное напряжение смещения циф- роаналогового преобразователя 7, аналогового вычитателя 3 и самого усилителя 9 возрастает на входе аналого-цифрового преобразователя 5 в 64 раза. Следовательно, исходный дрейф напряжения смещения нуля всей цепочки формирования разностного сигнала при единичном коэффициенте передачи должен быть в 64 раза меньше величины младшего кванта преобразования аналого-цифрового преобразователя 5. Одновременно следует помнить, что коэффициент усиления, равный 64, .второго усилителя 9 во столько же раз сужает его полосу пропускания и пропорционально увеличивает время установления сигнала на выходе. Поэтому требования по быстродействию вынуждают использовать по всей цепочке обратной связи широкополосную элементную базу с низкими техническими характеристиками по стабильности и дрейфу напряжения смещения нуля. Необходимо искать пути стабилизации дрейфа нуля цепи обратной связи. . .

Рассмотрим характер остатка нескомпенсированной части входной аналоговой величины после первого цикла кодирования. В ряде исследований показано, что погрешность квантования при достаточно разрешающей способности аналого-цифро- вого преобразования имеет равномерное распределение в пределах младшего кванта при уровне шумов значительно ниже величины кванта. С возрастанием уровня шума случайная составляющая погрешности ана- лого-цифрового преобразования имеет двойную физическую природу, т.е. складывается из погрешности квантования и случайной погрешности по шумам. Однако и в этом случае закон распределения погрешности имеет симметричный характер, т.е. вероятность появления отрицательного. Не следует упускать из виду и наличие система- тической составляющей погрешности первого цикла преобразования. Таким образом, для величины теоретического разностного сигнала после первого цикла преобразования можно записать:

Дг Дист + Дел Н-.Дсм ,

где Лист - действительный остаточный сигнал, который мог бы быть получен при идеальном аналого-цифровом преобразовании первого цикла кодирования;

Дел.- случайная составляющая разностного сигнала, обусловленная шумами;

А см - систематическая составляющая погрешности формирования разностного сигнала, обусловленная напряжением смещения первого усилителя 8 и аналого-циф- рового преобразователя 5.

Действительное значение разностного сигнала формируется на выходе второго усилителя 9 и может быть с учетом характера и физической природы возникающей погрешности описано выражением

(Д Т)+ Дц.СЛ.+ Ац.СМ. (3)

где Ац.сп. - случайная составляющая погрешности цепи обратной связи, обусловленная шумами;. .

Ац.см.- систематическая составляющая погрешности цепи обратной связи, обусловленная напряжениями сдвига нулевого уровня цифроаналогового преобразователя 7, аналогового вычитателя 3 и второго усилителя 9;

К - коэффициент передачи второго усилителя 9.

В выражении (3) не учитываются составляющие погрешности, обусловленные изменением масштабных коэффициентов, нелинейностью схем и т.д.

Подставляя (2) в (3), окончательно получим для смасштабированного разностного сигнала:

Ад К ЛиСТ + К ( Дел ) + Дц,СЛ. +

15 +К(Дсм)+Ац.см..

(4)

Анализируя (4), можно заметить, .что первые три слагаемых являются центрированными случайными величинами, т.е. мате20 матическое ожидание распределения величин Аист, Дел. и Ац.сл. равно нулю. Значение же слагаемых К( АСм) и Ац.см смещает математическое ожидание величины Ад на соответствующую величи

25 ну. На фиг. 6 приведен график плотности распределения случайнойьеличины Ад, где показан один из возможных вариантов смещения среднего значения Ад.

В схеме заявляемого устройства для вы30 явления постоянной составляющей погрешности формирования Ад используется интегратор на базе реверсивного счётчика 10. На управляющий вход счетчика поступает сигнал с третьего выхода блока суммиро35 вания 6, т.е. знак выходного кода второго цикла кодирования, или, иными словами, полярность величины Ад. Синхровход реверсивного счетчика 10 подключен к шестому выходу блока управления 4. Учитывая то,

4 что сигналом по этому выходу в третий регистр 20 блока суммирования заносится окончательный результат преобразования, можно установить, что при этом в реверсивный счетчик 10 будет записываться или

45 вычитаться единица в зависимости от полярности значения Ад на выходе малоразрядного аналого-цифрового преобразователя 5 во втором такте кодирования.

Разрядность реверсивного счетчика 10

50 должна определяться значением дисперсии законов распределения Аист и (ДСл + + Ац.сл). Поэтому число неиспользуемых на выходе выводов младших разрядов счетчика .определяет постоянную времени интег- рирования. Старшие разряды реверсивного счетчика 10 подключены к входам второго цифроаналогового преобразователя 11, сигнал на выходе которого является результатом интегрирования выражения (4):

ивых.цап К( А см)4 Дц.см. (5)

Этот сигнал заводится на третий вход аналогового вычитателя 3, с помощью которого при соответствующем выборе масштабного коэффициента резисторами RI и RS производится компенсация смещения первого цикла преобразования и цепи обратной связи второго цикла преобразования;

Необходимо отметить, что компенсация величины А см играет отрицательную роль, т.к. эта погрешность первого такта преобразования теперь не будет компенсироваться вторым тактом и полностью войдет в окончательный итог преобразования, причем на уровне младших разрядов первого такта. Однако необходимо прежде всего отметить, что величина А см исходно может быть сделана достаточно малой, тж. первый усилитель 8 и малоразрядный аналого-цифровой преобразователь 5 работают при коэффициентах, передачи, близких к единице, и могут быть выбраны достаточно стабильными, Основным положительным фактором , допускающим некомпенсацию А см в связи с уничтожением Ац.см, является то, что в окончательном результате преобразования величина А см составит постоянное значение, сдвигающее всю передаточную характеристику на определенную величину, что легко компенсируется первоначальной настройкой или методами периодической коррекции в системе. Присутствие же в разностном сигнале величины А ц.см, которая из-за нестабильности величины смещения второго усилителя 9 быстро дрейфует и, главное, формируется в цепи обратной связи и, подавляя полезный сигнал, приводит к нелинейному характеру погрешности (для замкнутой системы с отрицательной обратной связью коэффициент передачи цепи обратной связи находится в знаменателе передаточной функции), приводит к значительно более тяжелым последствиям, и подавление Ац.см имеет решающее значение для повышения точности параллельно-последовательно аналого-цифрового преобразователя. Поэтому в целом использование интегратора на базе реверсивного счетчика 10 совместно с вторым цифроаналоговым преобразователем 11 позволяет повысить точность аналого-цифровых преобразователей параллельно-последовательного типа при условии использования широкополосной элементной базы в цепи формирования и масштабирования разностного сигнала второго такта преобразования,

Для выявления преимущества заявляемого устройства по сравнению с прототипом сравним их по точности. Реализация первого усилителя 8 на микросхеме 140УД17, имеющей значение дрейфа напряжения смещения нуля, равное 1 мкВ/°С, и 5 малоразрядного аналого-цифрового преобразователя 5 на микросхеме 1107ПВ1, имеющей значение дрейфа напряжения смещения нуля, равное 5 мкВ/°С, позволяет определить максимальное значение АСм 10 первого такта преобразования в диапазоне температур ±20°С, ±140 мкВ. Приняв перекрытие шкал первого и второго тактов преобразования на один младший- разряд, получаем необходимый коэффици- 5 ент усиления второго усилителя 9, равный 32. Используя в качестве второго усилителя 9 широкополосную микросхему типа 544УД2 и считая, что ее собственный дрейф . напряжения смещения в 100 мкВ/°С со- 0 ставляет подавляющую часть напряжения смещения цепи обратной связи, получаем возможное значение погрешности Ац.см в диапазоне температур ±20°С, равное 64 мВ. При динамическом диапазоне аналого- 5 вого сигнала в 2 В это составляет 2 кванта второго такта преобразования. В то же время усиленное вторым усилителем 9 напряжение смещения тракта - усилитель 6 - аналого-цифровой преобразователь 5 со- 0 ставляет всего 4,5 мВ, что значительно меньше веса младшего кванта преобразования, который составляет 31 мВ. . В заявляемом устройстве величины АСМ и Ац.см будут скомпенсированы. Сле- 5 довательно, действительная погрешность от смещения нулевого уровня не превысит 4,5 мВ, в то время как была возможна ошибка в 64 мВ.

Приведенный сравнительный анализ 0 составляющих погрешности показывает, что, по сравнению с устройством-прототи- пом, заявляемое устройство имеет при одинаковой элементной базе в 15 раз более низкую погрешность. 5 Формула изобретения

Устройство аналого-цифрового преобразования, содержащее первый и второй переключатели, аналоговый вычитатель, блок управления, малоразрядный аналого- 0 цифровой преобразователь, блок суммирования, первый цифроаналоговый преобразователь и первый и второй усилители, вход первого из которых обьединен с первыми входами аналогового вычитателя и 5 первого переключателя и является входной шиной, а выход подключен к первому входу второго переключателя, второй вход которого через второй усилитель соединен с выходом аналогового вычитателя, а выход - с

информационным входом малоразрядного аналого-цифрового преобразователя, информационные выходы которого и выход Конец преобразования подключены соответственно к первому и второму входам блока суммирования, первый информационный выход которого является выходной шиной, а второй информационный выход - через первый цифроаналоговый преобразователь подключён к второму входу первого переключателя, выход которого соединен с вторым входом аналогового вычитателя, управляющие входы первого и второго переключателя, а также малоразрядного аналого-цифрового преобразователя соединены соответственно с первым, вторым и третьим выходами блока управления, четвертый, пятый и шестой выходы которого подключены соответственно к третьему, четвертому и пятому входам блока суммирования, а управляющий вход блока управления является

шиной Пуск, отличаю щ е вся тем, что, с целью повышения точности, в него введены реверсивный счетчик и второй цифроаналоговый преобразователь, причем счетный вход реверсивного счетчика соединен с шестым выходом блока управления, а управляющий вход соединен с третьим информационным выходом блока суммирования, выходы старших разрядов соединены с соответствующими входами второго цифроаналогового преобразователя, выход которого подключен к третьему входу аналогового вычитателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для аналого-цифрового преобразования | 1983 |

|

SU1249703A1 |

| Устройство для измерения динамических характеристик аналого-цифровых преобразователей | 1978 |

|

SU738151A1 |

| Устройство для аналого-цифровогопРЕОбРАзОВАНия | 1979 |

|

SU815898A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ - КОД | 1991 |

|

RU2027303C1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU945978A1 |

| Устройство для сжатия данных | 1983 |

|

SU1089609A1 |

| Преобразователь напряжения в код | 1988 |

|

SU1547061A1 |

| Следящий аналого-цифровой преобразователь | 1988 |

|

SU1562972A1 |

| Параллельно-последовательный аналого- цифровой преобразователь | 1978 |

|

SU790287A1 |

| Аналого-цифровой преобразователь с частотным преобразованием | 1988 |

|

SU1547066A1 |

Изобретение относится к измерительной технике и может быть использовано в информационно-измерительных системах, гибридных вычислительных комплексах, системах автоматики, регулирования и контроля. Цель изобретения - повышение точности устройства. Поставленная цель достигается тем, что в устройство, содержащее первый и второй усилители, первый и второй переключатели, аналоговый вычита- тель, блок управления, малоразрядный ана- лого-цифро.вой преобразователь, блок суммирования и первый цифро-аналоговый преобразователь, дополнительно введены реверсивный счетчик и второй цифроанало говый преобразователь. Повышение точности параллельно-посл.едовательного аналого-цифрового преобразователя достигается за счет компенсации дрейфа смещения нулевого уровня цепи обратной связи формирования разностного сигнала второго такта преобразования. Метод компенсации основывается на свойстве равномерного распределения погрешности квантования с нулевым значением математического ожидания функции распределения. Используемый метод компенсации погрешности позволяет в 2-3 раза повысить точность преобразования без снижения быстродействия. 6 ил. w е

ФиЫ

ЗпЯОЗ fly

Фы2

12

/s

Ууск

13

-

-

Э

PC

ft

УпрЛр

Упо.Пр.

ЗапДЦП

ЗМ1

ЗпЯ&Ж

3n.RB$

Фиг.З

Фи г. 5

1

А2./гм&.

О

| Аналого-цифровой преобразователь | 1979 |

|

SU839046A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь угла поворота вала в код | 1984 |

|

SU1249704A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-04-07—Публикация

1991-03-28—Подача