1

I Изобретение относится к преобразователям аналоговых сигналов в цифровые с noBfcJmeHHfjf быстродействием и, в частности, предназначено для построения на его основе систем сбора аналоговой 5 информации для управляющих вычислительных комплексов.

Известен преобразователь, содержащий аналоговый вычитатель, усилитель с управляемым коэффициентом уси-«О ления, преобразователь считывания, цифроаналоговый преобразователь, регистр-счетчик и блок управления..

При этом управляющая шина блока управления соединена с управляющими 15 входами регистра-счетчика и усилителя, вход которого соединен через аналоговый вычитатель с входной шиной и с выходом цифроаналогового преобразователя, выход - через преобразователь 20 считывания с кодовыми входами регистра-счетчика, кодовыми выходами подсоединенного к кодовым входам цифроаналогового преобразователя, а входом параллельной записи кода - к 25 блоку управления l В этой схеме имеется один преобразователь считывания и с его помощью последовательно по тактам определяют-, : ся группы разрядов. Время выполнения 30

этих тактов определяется переходным процессом усилителя, как самого инерционного узла из всех элементов схемы. Для всех уровней входных сигналов время выполнения такта преобразования остается неизменным и устанавливается исходя из наиболее длительного переходного процесса усилителя. Это приводит к дополнительным затратам времени при выполнении преобразования. На устранение этого недостатка направленно данное предложение .

Цель изобретения - увеличение быстродействия преобразования аналоговой величины в код.

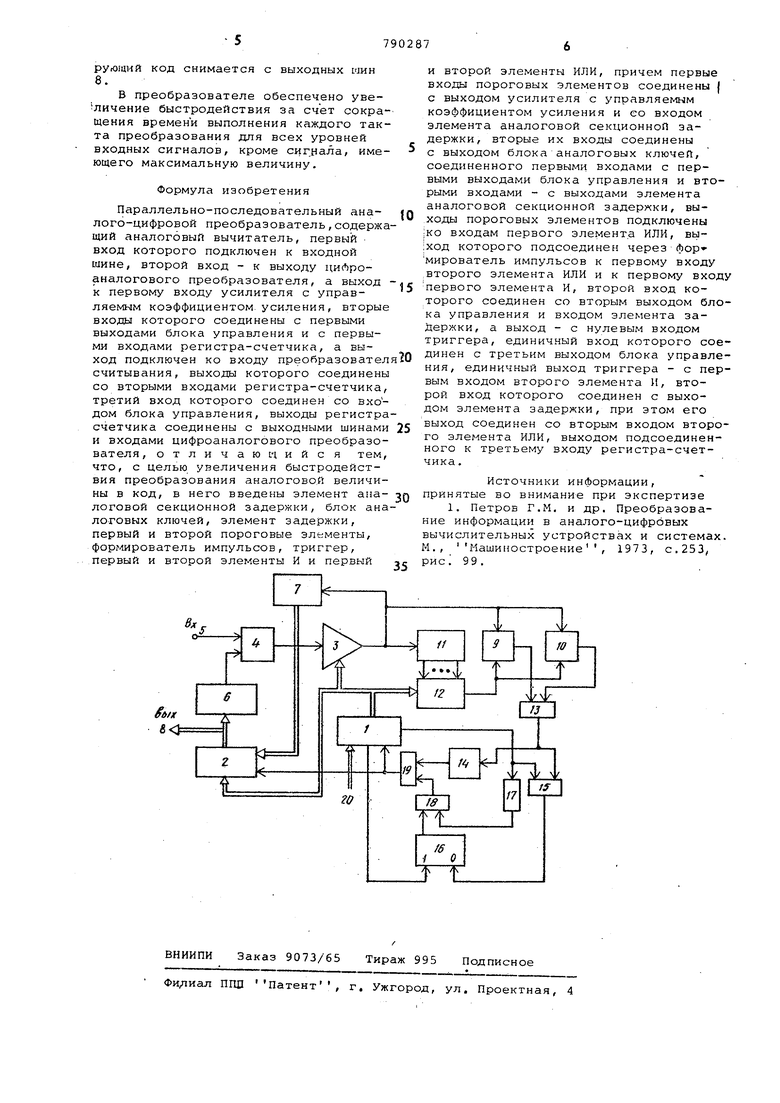

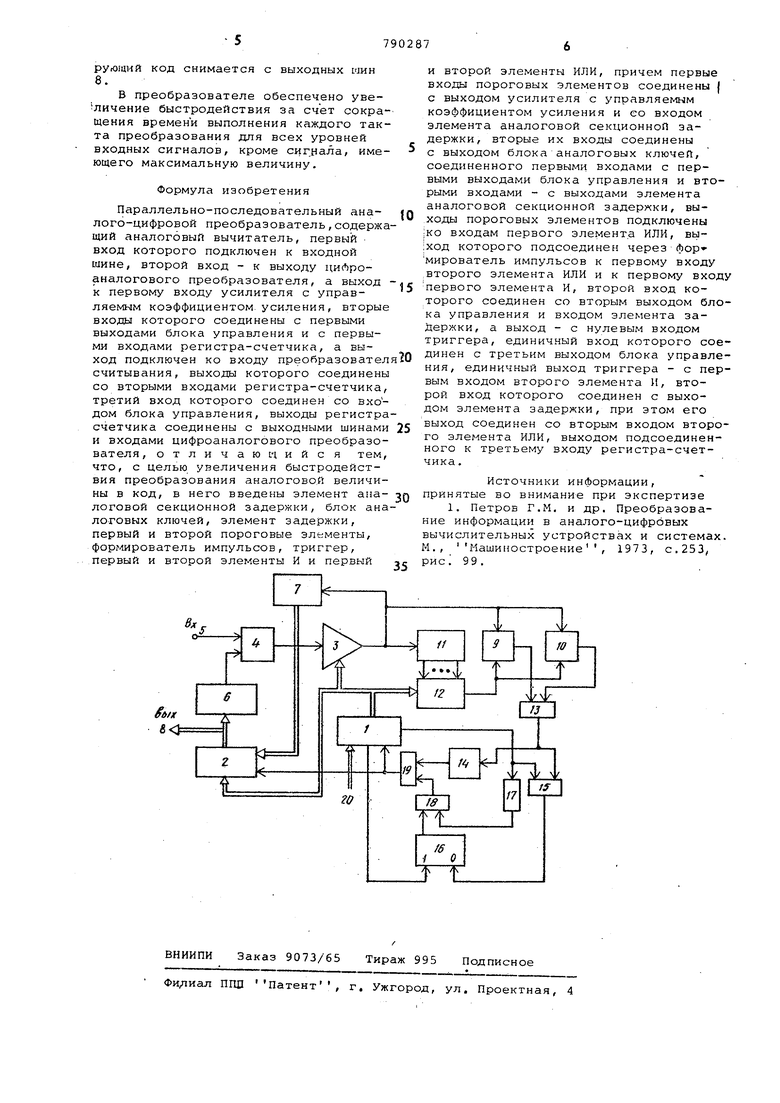

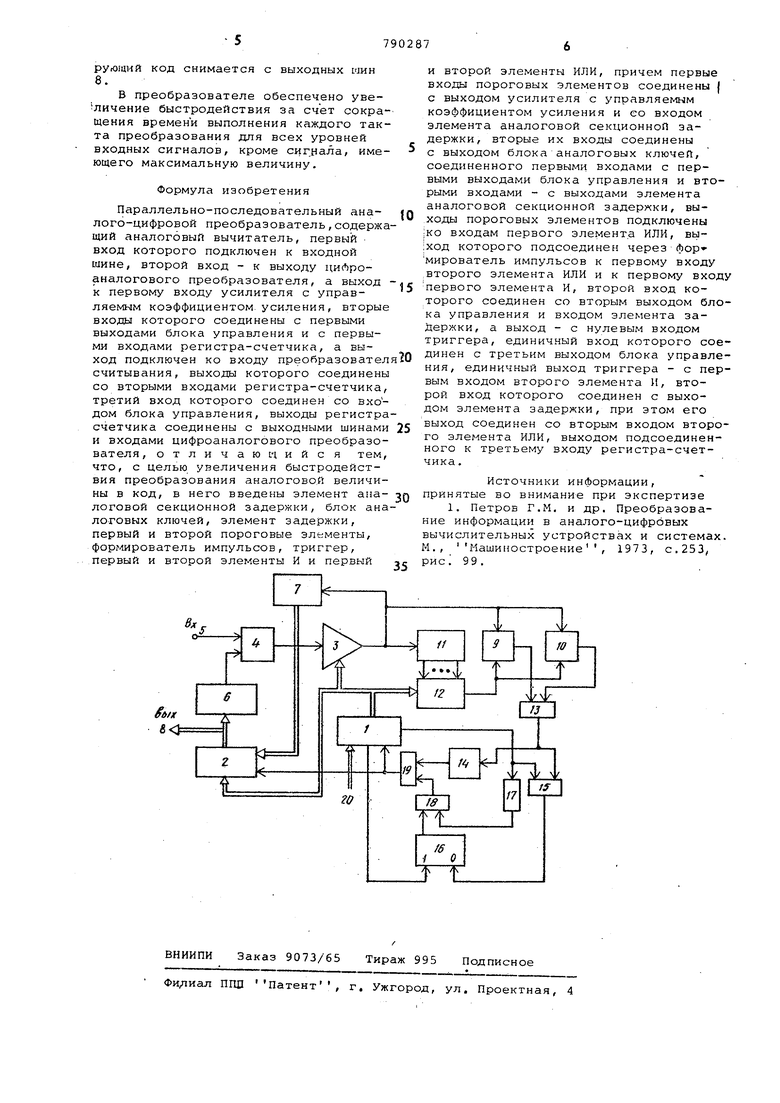

Посталенная цель достигается тем, что в параллельно-последовательный аналого-цифровой преобразователь, содержащий аналоговый вычитатель, первый вход которого подключен к входной шине,второй вход - к выходу цифроаналогового преобразователя, а выход к перовому входу усилителя с управляемым коэффициентом усиления, вторые входы которого соединены с первыми выходами блока управления и первыми входами регистра-счетчика, а выход подключен ко входу преобразователя считывания, выходы которого сослннепы со вторыми входами регистра-счетчика, третий, вход которого соединен со входом блока управления, выходы регистра счетчика соединены с выходными шинами И, входами цифроаналогового преобразователя, введены элемент аналоговой секционной задержки, блок аналоговых ключей, элемент задержки, первый и вт рой пороговые элементы, формирователь импульсов, триггер, первый и второй Элементы И и первый и второй элементы ИЛИ, причем первые входы пороговых элементов соединены с выходом усилителя с управляемым коэффициентом усиления и со входом элемента аналоговой секционной задержки,, вторые их входы соединены с выходом блока аналоговых ключей, соединенного первыми входами с первыми выходами блока управления и вторыми входами с выходами элемента аналоговой секционной задержки, выходы .подключены ко входам первого эле мента ИЛИ, выход которого подсоединен через формирователь импульсов к первому входу второго элемента ИЛИ и к . первому входу первого элемента И, второй вход которого соединен со вторым выходом блока управления и входом элемента задержки, а выход - с нулевым в.ходом триггера, единичный вход которого соединен с третьим выходом блока управления, единичный выход триггера - с первым входом второго элемента И, второй вход которого сое динен с выходом элемента задержки, при этом его выход соединен со вторым входом- второго элемента ИЛИ, выходом подсоединенного к третьему входу регистра-счетчика. На чертеже представлена структурная схема параллельно-последовательного аналого-цифрового преобразовате ля . Преобразователь содержит блок управления 1, регистр-счетчик 2, усили тель 3 с управляемым коэффициентом усиления, аналоговый вычитатель 4) входную шину 5, цифроаналоговый преобразователь б, преобразователь 7 считывания, выходные шины 8, первый и второй, пороговые элементы 9 и 10, элемент,11 аналоговой секцибннЬй задержки, блок 12 аналоговых ключей, первый элемент 13 МЛИ, формирователь 14 импульсов, первый элемент 15 И, триггер 16, элемент задержки 17, второй элемент 18 И, второй элемент 19 ИЛИ, шина 20 связи с микропроцессором. Преобразователь работает следующи образом. Получение результирующего кода происходит, последовательно по тактам отдельными.Группами разрядов, которые формиру. .тся с помощью преобразов теля 7 считывания и записывгхются в регистр-счетчик 2. Выходной код этог регистра преобразуется с помощью пре Ъ разЬвателя 6 в аналоговый сигнал,, который вычитается из входного сигнала вычитателем 4. Полученный разностный сигнал усиливается усилителем 3 с коэффициентом, соответствующим выполняемому такту преобразования. В первом такте по сигналам блока 1управления устанавливается минимальное значение коэффициента усиления усилителя 3 и гасится регистр 2. Входной сигнал без изменения проходит через вычитатель 4 на вход усилителя 3. Время установления выходного сигнала усилителя 3 определяется скоростью отклика усилителя, которая постоянна на данном такте и уменьшается при уверичении коэффициента усиления усилителя. Только после истечения времени установления выходного сигнала усилителя выполнять считывание кода из преобразователя 7. Считывание кода происходит по сигналу, сформированному формирователем 14 импульсов по перепадам выходных сигналов пороговых элементов 9 или 10. Эти элементы имеют одинаковые, но противоположные по знаку пороги срабатывания относительно выходного сигнала блока 12, представляющего собой сдвинутый во времени элементом 11 (на различную величину в зависимости от выполняемого такта) выходной сигнал - усилителя 3. По- . этому после установления сигнал.а на выходе усилителя один из пороговых элементов обязательно срабатывает. Для тех случаев, когда сигнал на выходе усилителя 3 не изменяется на величину, меньшую порога срабатывания элементов 9 и 10, в схеме предусмотрено считывание кода с выходов преобразователя 7 по другому сигналу, которыр формируется следу.ющим образом. Каждый такт преобразования начинается с выдачи блоком 1 сигнала, который устанавливает триггер 16 в единичное состояние. Через некоторое время блоком 1 формируется сигнал, который подается на элементы 15 и 17. Если ни один из элементов 9 и 10 не сработал, то этот сигнал, задержанный элементом 17 на время срабатывания триггера, проходит через элементы 18 и 19 и по нему выполняется считывание. Если элементы 9 или 10 сработали, упомянутый сигнал проходит через элемент 15 и устанавливает триггер 1.6 в исходное состояние. Считывание произойдет в этом случае, как описано вьше. После запис и кода в регистр-счетчик 2данный такт работы п-реобразователя заканчивается, Вновь записанная группа разрядов в регистре-счетчике 2 изменяет в преобразователе 6выходной сигнал и на.чинается процесс преобразован-йя следующего такта. После дыполненйя последнего такта блок .1. на шину связи 20 вьщает сигнал об .окончании преобразования. Результируютий код снимается с выходных шин 8.

В преобразователе обеспечено уве личение быстродействия за счет сокращения времени выполнения каждого такта преобразования для всех уровней входных сигналов, кроме сигнала, имеющего максимальную величину.

Формула изобретения

Параллельно-последовательный аналого-цифровой преобразователь,содержащий аналоговый вычитатель, первый вход которого подключен к входной шине, второй вход - к выходу циЛроаналогоБОГО преобразователя, а выход к первому входу усилителя с управляемым коэффициентом, усиления, вторые входы которого соединены с первыми выходами блока управления и с первыми входами регистра-счетчика, а выход подключен ко входу преобразовател считывания, выходы которого соединены со вторыми входами регистра-счетчика, третий вход которого соединен со входом блока управления, выходы регистрасчетчика соединены с выходными шинами и входами цифроаналогового преобразователя, отличаю 11ийся тем, что, с целью увеличения быстродействия преобразования аналоговой величины в код, в него введены элемент аналоговой секционной задержки, блок аналоговых ключей, элемент задержки, первый и второй пороговые элементы, фop лиpoвaтeль импульсов, триггер, первый и второй элементы И и первый

8л

и второй элементы ИЛИ, причем первые входы пороговых элементов соединены j с выходом усилителя с управляемым коэффициентом усиления и со входом элемента аналоговой секционной задержки, вторые их входы соединены с выходом блока аналоговых ключей, соединенного первыми входами с первыми выходами блока управления и вторыми входами - с выходами элемента аналоговой секционной задержки, выходы пороговых элементов подключены ;ко входам первого элемента ИЛИ, вь1;ход которого подсоединен через фор мирователь импульсов к первому входу .второго элемента ИЛИ и к первому входу первого элемента И, второй вход которого соединен со вторым выходом блока управления и входом элемента заДержки, а выход - с нулевым входом триггера, единичный вход которого соединен с третьим выходом блока управления, единичный выход триггера - с первым входом второго элемента И, второй вход которого соединен с выходом элемента задержки, при этом его выход соединен со вторым входом второго элемента ИЛИ, выходом подсоединенного к третьему входу регистра-счетчика.

Источники информации, принятые во внимание при экспертизе

1. Петров Г.М, и др. Преобразование информации в аналого-цифровых вычислительных устройствах и системах. М., Машиностроение, 1973, с,253, рис 99.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ параллельно-последовательногоАНАлОгО-цифРОВОгО пРЕОбРАзОВАНия | 1979 |

|

SU819953A1 |

| Система многоканального приема и преобразования в код аналоговых сигналов | 1978 |

|

SU758511A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Параллельно-последовательныйАНАлОгО-цифРОВОй пРЕОбРАзОВАТЕль | 1978 |

|

SU819952A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Цифровой измеритель аналоговой величины | 1988 |

|

SU1638650A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Устройство для коррекции временных искажений | 1985 |

|

SU1270797A1 |

Авторы

Даты

1980-12-23—Публикация

1978-08-01—Подача