(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1981 |

|

SU1005300A1 |

| Аналого-цифровой преобразователь сАВТОМАТичЕСКОй КОРРЕКциЕй Нуля | 1979 |

|

SU805490A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Программируемый генератор импульсов | 1984 |

|

SU1248029A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Цифровой фазовращатель | 2024 |

|

RU2823429C1 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2326494C1 |

| Инкроментный умножитель аналоговых сигналов | 1982 |

|

SU1057970A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Устройство для аналого-цифрового преобразования | 1986 |

|

SU1387195A1 |

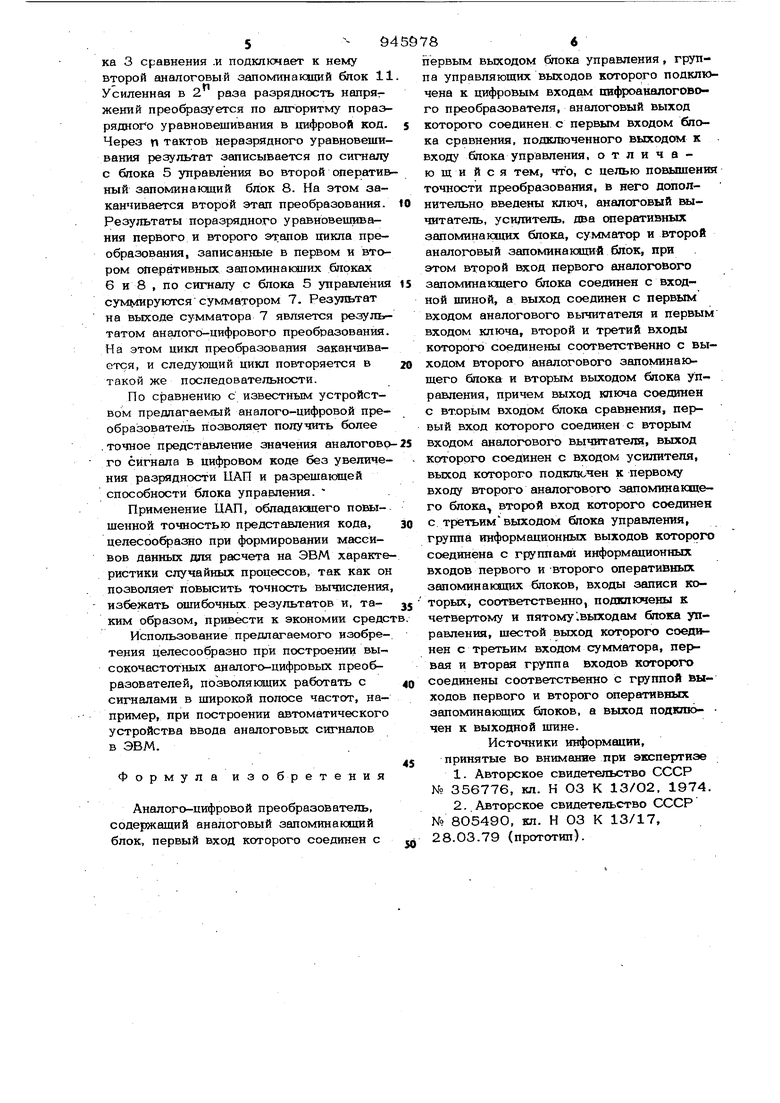

Устройство относится к цифровой электроизмерительной технике и может быть применено в цифровых измерител1 ных приборах, устройствах автоматики и вычислительной техники. Известен аналого-цифровой преобраэователь, содержащий два аналоговых запоминающих устройства, блок управляемы резисторов, два аналого-цифровых преобразователя, устройство управления, масшта&1ое устройство и сумматор Cll Этот преобразователь позволяет проиэ вести коррекцию погрешностей, зависимых от конечности входного сопротивления устройства, однако не позволяет производить коррекцию нестабильности параметров аналого-цифрового преобразователя и, таким образом, имеет небольшую точность. Известен также аналого-цифровой пре.образователь (АЦП), содержащий аналоговый запоминающий блок, подключенный выходом к первому входу блока сравнения, второй вход которого соединен с вы ХОДОМ цифро-аналоглвого преобразователя (ЦАП), блок управления блок коррекции, ключи, два aneMeifra ИЛИ, блок установки кода нуля, подключенный выходом к входам блока управления, блок регулирующих резисторов, два элемента НЕ, пять элементов И, генератор тактовых импульсов, аналоговый мультиплексор, реверсивный счетчик, счетчик, триггер коррекции, соединенный выходам с входами первых элементов НЕ, И и реверсивного счетчика 2 . Основным элементом, определяющим характеристики аналого-цифрового преобразователя, есть блок сравнения. Точность преобразования в аналого-цифровом преобразователе обычно достигается путем увеличения разрядности цифро-аналогового преобразователя, т.е. увеличением числа высокочастотных резисторов, требующих специальной юстировки и ключей. При этом увеличивается число элементов и, соответственно, разбцос их параметров, повышаются требования к разрешающей способности блока сравнения, которая принципиально ограничена. Увеличение разрядности цифро-аналогового преобразователя вьпие определяемых пределов и приводит к нестабильности характеристики аналого-цифрового преобразователя и снижению точности преобразования, напряжения сигнала в цифровой код. Цель изобретения - повышение томности преобразования напряжения в код. При этом аналого-цифровым преобразова телем, содержащим ц -разрядный цифроаналоговый преобразователь, обеспечивается точность, обыкновенно достигаемая пр1 1менением 2 -разрядного цифро;аналогового преобразователя. Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержащий аналоговый гзЕШОМИнакщий блок, первый вход которого соединен с первым выходом блока управления, труппа управлякяцих выходов которого подключена к цифровым входам цифроаналогового преобразователя, аналогх)вый вых которого соединен с первым входом блока сравнения, подключенного выходом к входу блока управления, дополнительно введены ключ, аналоговый вычитатель, усилитель, второй аналоговый запомИнающий блок, два оперативных зеаюминаю,щих блока и сумматор, при этом второй вход первого аналогового запоминающег блока соединен с входной шиной, а выхо соединен с первым входом аналогового. вычитателя и первым входом клвэча, вто рой и третий входы которого соединены соответственно с выходом второго анало гового запоминающего блока и вторым выходом блока управления, причем выхо ключа соединен с вторым входом блока сравнения, первый вход которого соединен с вторым входо1у1 аналогового вычи-т тателя, выход которого соединен -с входом усилителя, выходкоторого подклюпче к первому входу второго аналогового за поминающего блока, второй вход которо го соединен с третьим выходом блока управления, группа информационных выходов которого соединена с группами ин формационных входов первого и второго оперативных запоминающих блоков, вход записи которых, соответственно, подклю чены к- четвертому и пятому выходам блока управления, шестой выход которог соединен с третьим входом сумматора, первая и вторая группа входов которого соединены соответственно с группой вы ходов первого и второго оперативных запоминающих блоков, а выход подключен к выходной щине. На чертеже показана структурная схема предлагаемого преобразователя. Устройство содержит первый аналоговый запоминающий блок 1, ключ 2, блок 3 сравнения, цифроаналоговый преобразователь 4, блок 5 управления, первый оперативный запоминающий блок 6, сумматор 7, второй оперативный запоминающий блок 8, аналоговы-й вычитатель 9, усилитель 10 и второй аналоговый запоминающий блок. Аналого-цифровой преобразователь работает следующим образом. Цикл аналого-цифрового преобразования состоит из двух этапов, и .начинается с приходом тактового импульса от блока 5 управления на первый аналоговый запоминающий блок 1, при этом он-устанавливается в режим запоминания мгновенного значения входного сигнала, который длится на протяжении первого такта, остальное время айалоговь1й запоминающий блок 1 находится в режиме хранения. Выборка сигнала с аналогового запоминающего блока 1. через замкнутый ключ 2 подается на блок 3 сравнения, и с второго такта начинается процесс поразрядного уравновещивания. Через п тактов Поразрядного уравновещивания (о определяется числом разрядов цифроаналогсивого преобразователя ) результат пораз- , рядного уравновешивания с блока 5 управления переписывается по сигналу с блока 5 управления в первый оперативный запоминающий блок 6. Результат уравновещивания с аналогового выхода цифроаналогового преобразователя 4 подается на второй вход аналогового вычитателя 9, на первый вход которого постоянно подается сигнал с первого аналогового запоминакщего блока 1. Результат разности напряжений усиливается усилителем Ю скоэффициентом усиления 2 и подается на второй аналоговый запоминающий блок 11, на этом заканчивается первый этап преобразования. На первом такте второго этапа преобразования усиленная в 2 раза разрядность выходных напряжений первого аналогового запоминающего блока 1 и цифроаналогового преобразователя 4 по сигналу с блока 5 управления запоминается вторым аналоговым запоминающим блоком 11. На втором такте второго этапа преобразования по сигналу с блока 5 управления ключ 2 отключает первый аналоговый запоминающий блок 1 от бт1 ка 3 сравнения .и подключает к нему второй аналоговый запоминакадий блок 1 Усиленная в 2 раза разрядность напряжений преобразуется по алгоритму пораз рядного уравновешивания в цифровой код. Через г тактов неразрядного уравновеши вания результат записывается по сигналу с блока 5 управления во второй оператив ный запоминающий блок 8. На этом заканчивается второй этап преобразования. Результаты поразрядного уравновешивания первого и второго этапов цикла преобразования, записанные в первом и втором оперативных запоминакших блоках 6 и 8 , по сигналу с блока 5 управления сум отруются сумматором 7. Результат на выходе сумматора 7 является результатом аналого-цифрового преобразования. На этом цикл преобразования заканчиваетдя, и следующий цикл повторяется в такой же последовательности. По сравнению с известным устройством предлагаемый аналого-цифровой преобразователь позволяет получить более .точное представление значения аналоговр го сигнала в цифровом коде без увеличения разрядности ЦАП и разрешающей способности блока управления. Применение 11АП, обладающего повышенной точностью представления кода, целесообразно при формировании массивов данных для расчета на ЭВМ характе ристики случайных процессов, так как он позволяет повысить точность вычисления избежать ошибочных результатов и, таКИМ образом, привести к экономии средс Использование предлагаемого изобретения целесообразно при построении высокочастотных аналого-цифровых преобразователей, позволяющих работать с сигналами в широкой полосе частот, например, при построении автоматического устройства ввода аналоговых сигналов в ЭВМ. Формула изобретения Аналого-цифровой преобразователь, содержащий аналоговый запоминающий блок, первый вход которого соединен с первым выходом блока управления , группа управляющих выходов которого подключена к цифровым входам 11ифроаналогов1 го преобразователя, аналоговый выход которого соединен с первым входом блока сравнения, подключенного выходом к входу блока управления, отличающийся тем, что, с целью повышения точности преобразования, в него дополнительно введены ключ, аналоговый вычитатель, усилитель, два оперативных запоминающих блока, сумматор и второй аналоговый запоминакадий блок, при этом второй вход первого аналогового запоминаюцего блока соединен с входной шиной, а выход соединен с первым входом аналогового вьгчитателя и первым входом ключа, второй и третий входы которого соединены соответственно с выходом второго аналогового запоминающего блока к вторым выходом блока управления, причем выход ключа соединен с Вторым входом блока сравнения, первый вход которого соединен с вторым входом аналогового вычитателя, выход которого соединен с входом усилителя, выход которого подключен к первому входу второго аналснговогч запоминакщего блока, второй вход которого соединен с третьимвыходом блока управления, группа информационных выходов которого соединена с группами информационных входов первого и второго оперативных запоминакядих блоков, входы записи которых, соответственно, подключены к четвертому и пятому .выходам блока управления, шестой выход которого соединен с третьим входом сумматора, первая и вторая группа входов которого соединены соответственно с группой выходов первого и второго оперативных запоминающих блоков, а выход подклю- чен к выходной шине. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 356776, кл. Н ОЗ К 13/О2, 1974. 2.Авторское свидетельство СССР №805490, кл. Н 03 К 13/17, 28.03.79 (прототип).

Авторы

Даты

1982-07-23—Публикация

1981-01-16—Подача