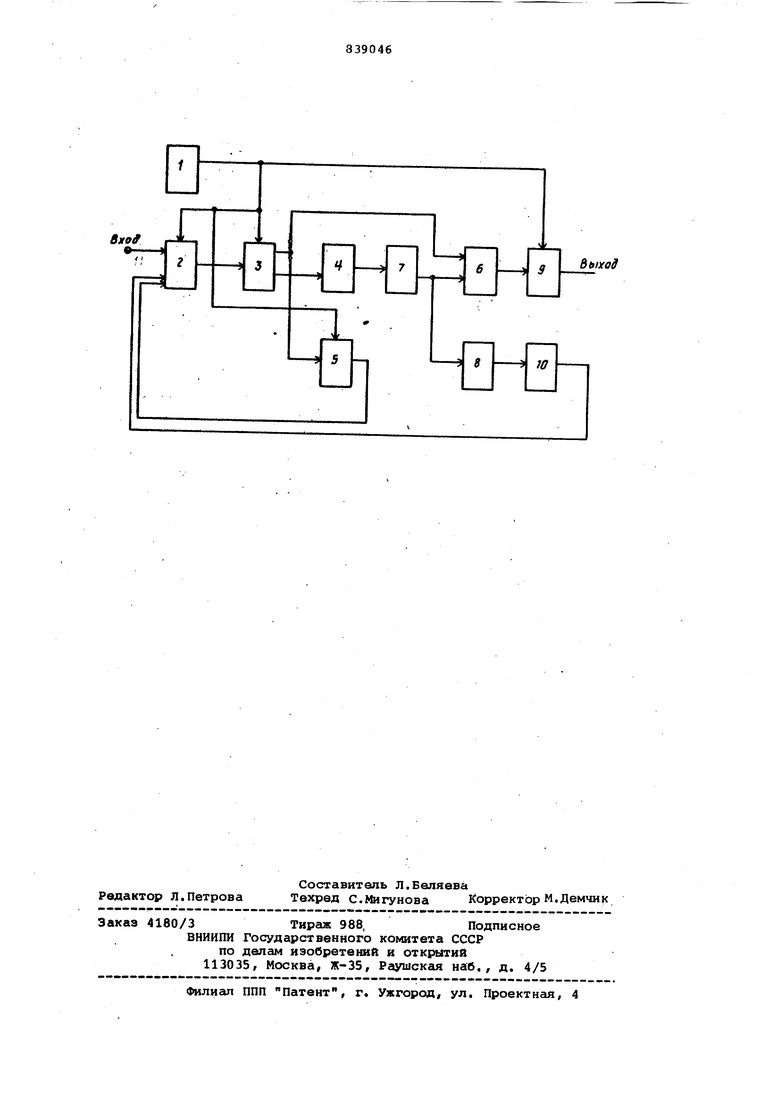

Изобретение относится к измеритель ной технике и может быть использовано в информационно-измерительных системах, гибридных вычислительных комплексах, системах автоматики, регулирования и контроля. Известен аналого-цифровой преобразователь повышенного быстродействия, содержащий суммирующий усилитель, основной цифроаналоговый преобразователь (ЦАП), компараторы, дополнительный ЦАП, дешифраторы, регистр промежуточной памяти, выходной регистр и блок управления l . Недостатком этого преобразователя являются отсутствие возможности коди рования сигналов обеих полярностей и необходимость использования для его реализации прецизионных, сложвлх в настройке элементов. Известен также аналого-цифровой преобразователь с циклическим уточнением результата, содержащий набор масштабных усилителей (усилитель с перестраиваекым коэффициентом усилений) , коммутатор аналоговых сигналов, многопороговый компаратор, ну орган, дешифратор, блок управления, сумматор, регистр памяти и набор роаналоговых преобразователей 2 . Однако данное устройство характеризуется невозможностью кодирования двухполярных сигналов, приводящей также.к тому, что время преобразования входного сигнала становится переменном и может колебаться в пределах (, время одного элементарного цикла преобразования; минимально возможное количество циклов в течение всего процесса преобразования. Цель изобретения - расширение функциональных возможностей преобразователя. Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержащий усилитель с перестраиваемым коэффициентом передачи, первый вход которого соединен с шиной входного сигнала, второй вход через последоват льно соединенные цифроаналоговый преобразователь, регистр памяти соединен с выкодом дешифратора, выход подключен к первому входу многопорогового компаратора, а третий вход соединен с выходом блока управления, вторым входом многопорогового компаратора и первым входом сумматс а, введены блок формирования нормального унита ного кода, формирователь кода и Слок коррекции сигнала обратной свя первый вход которого соединен с выходом блока управления, второй вхол соединен с первым выходом многопсчро гового компаратора и первым входом формирователя кода, а выход соединен со вторым входом усилителя с перестраиваемым коэффициентом передачи причем второй выход многопорогового компаратора через блок формирования нормального унитарного кода соединен с входом дешифратора, выход которого соединен со вторым входом формирователя кода, выход которого соединен со вторым входом суммато,ра. На чертеже представлена структурная схема аналого-цифрового прео разователя. Преобразователь содержит блок 1 управления, усилитель 2 с перестраи ваемым коэффициентом передачи, мно пороговый компаратор 3, блок 4 форм рования нормального унитарного код блок 5 коррекций сигнала обратной связи, формирователь 6 кода, дешиф ратор 7, регистр 8 памяти, сумматор 9, цифроаналоговый преобразователь (ЦАП) 10, шина 11 входного сигнала. Выход блока управления соединен с управляющим входом усилителя 2, к неинвертируквдему входу которого подключена шина входного сигнала. В процессе преобразования коэффици ент передачи усилителя 2 К принимает & различных значений, возрас тая последовательно раз Hai каждом.цикле .. 1,2,...,е, aiki2 : где k - коэффициент увеличения передачи К усилителя 2; (4l таков по сравнению с л -ым циклом; - номер цикла преобразования;О - число элементарных циклов преобразования; П - число двоичных разрядов кода цифрового эквивалента входного аналогового сигна определяемых на одном цикл Выход усилителя 2 соединен со в дом многопорогового компаратора 3, число порогов N которого выбираетс из соотношения . Пороги выб ни таким образом, что порога, наст енного на нулейой сигнал, нет. Оде ио это для того, чтобы избежать ошибки знака при кодировании сигнала в ок рестности нуля. Пороги расположены симметрично отно.сительно нуля в обе полярности и отличаются друг от друга на постоянную величину - квант цикл.а. Один выход многопорогового компаратора соединен со входом блока 4 формирования нормального унитарного кода, а другой выход - со входами блока 5 коррекций сигнала обратной связи и формирователя б кода. Блок 4 приводит возможно ошибочные кодовые комбинации на. выходе многопорогового компаратора, возникаюище вследствие большого допустимого разброса зон нечувствительности соседних компараторов, к сплошной последовательности единиц, т.е. к нормальному унитарному коду. Выход блока 4 соединен со входом дешифратора 7 унитарного кода в позиционный двоичный код. Блок 5 вводит поправку в сигнал обратной связи, учитывающую полярность результата измерения, полученного на текущем цикле, и компенсирующую добавку в сигнал обратной связи на последнем цикле, учитывающую смещение пороroBi многопорогового компаратора относительно нуля. Выход дешифратора 7 соединен со вторыми входами формирователя б кода и со входами регистра 8 памяти. Выход формирователя б соединен со входом сумматора 9, а выход регистра 8 памяти со входами ЦАП 10, который на каждом цикле формирует аналоговый эквивалент сигнала, соответствующий поступающему на регистр 8 памяти цифровому коду из дешифратора 7. Аналоговые выходы ЦАП 10 и блока 5 подключены к инвертирующему входу усилителя 2. Выход блока 1 управления соединен также с управляющими-входами многопорогЬвогр компаратора 3/ блока 5, регистра памяти 8 и сумматора 9. Блок 1 управления осуществляет синхронизацию работы преобразователя. Устройство работает следующим образом. Импульсом подготовки к работе все узлы устанавливаются в исходное состояние. Преобразуемый сигнал поступает на неинвертирующий вход усилителя, который на первом цикле имеет коэффициент передачи V К 1. С выхода усилителя сигнал подается на вход многопорогового компаратора. Код, формируемый на его выходе, может отличаться от унитарного наличием нулей среди сплошного ряда единиц. Возникает это вследствие грубой настройки (подборки) компараторов, зоны нечувствительности которых могут перекрываться (между собой). Код с выхода многопорогового компаратора поступает поэтому на вход блока 4 формирования нормального унитарного кода. Унитарный код, формируемый на вых де блока 4, преобразуется в дешифраторе 7 в прямой двоичный позиционный код для записи в регистр 8 памяти, у равлякхций цифроаналоговым преобразователем 10, и в формирователь б кода, который может формировать, напри мер, дополнительный код, что создает очевидшле преимущества при реализации арифметической операции сложения разнопопярных кодов. . Сформированные в деши(1фаторе 7 на первом цикле преобразования п раз ряды цифрового эквивалента преобразу емого сигнала поступают на формирование аналогового эквивалента через соответствующую секцию регистра 8 па мяти в п старише разряды ЦАП 10 и через формирователь б в п старшие разряды сумматора 9. Одновременно признак знака цифрового эквивалента преобразуемого сигнала подается в блок 5 для формирования поправки на полярность в сигнал обратной связи. Эквивалент сигнала с ЦАП 10, скорректированный сигналом от блока 5 в усилителе 2 компенсирует входной сигнал. Разность между входным и эквивалентным ему сигналами на следукАцих циклах передается усилителем с коэффициентом K;-k , где . Выбор коэффициента передачи усилителя 2 таким образец приводит к расширению в 1о раз диапазона измерения разности сигнало на каждом элементарном цикле, что по воляет использовать быстродействующие компараторы низкой точности и значительно упрощает принципиальную схему преобразователя. В этом случае результат сравнения предыдущего цикла уточняется в последующем цикле в (и-т) младших разрядах, где m logok. Таким образом, за Е циклов преоб разования формируется М-разрядный двоичный эквивалент входного сигнал где. М п+( 6-) «(&-( )&og,k. Учитывая то, что пороги срабатывания смещены относительно нуля на половину кванта цикла, а кодош:1е комбинации, формируемые на выходе .многопорогового компаратора и управляющие (включением) формированием эквивалентных сигналов на ЦАП 10, такого смещения не имеют, очевидно, ;на последнем цикле преобразования аналогового сигнала, кратного величи не младшего разряда выходного кода, получим аналоговую величину, смещенную на половину кванта цикла, а не равную одному из порогов срабатывания (и цифровой эквивалент, на единицу меньше истинного значения Для устранения этой методической сошбки блок 5 на последнем цикле формирует корректирующую добавку в ангшоговый эквивалент, компенсирующую смещение сигнёша по отношению к порогам срабатывания ксялпаратора 3, что приводит к соответствию выходного цифрового кода входному аналоговому сигналу с точностью до кванта преобразования. Технический эффект состоит в значительном расширении класса вводимых в ЦВМ функций, имеющих двухполярное представление аналоговой информации, а экономический - в сокращении вдвое времени (а следовательно, и удешевлении ввода информации в ЦВМ. формула изобретения Аналого-цифровой преобразователь, содержащий усилитель с перестраиваемым коэффициентом передачи, первый вход которого соединен с шиной входного сигнала, второй вход через последовательно соединенные цифроаналогошлй преобразователь, регистр памяти соединен с выходом дапифратора, выход подключен к первому вхсщу многопорогового компаратора, а третий вход соединен с выходом блока управления, втор« 1м входом многопорогового компаратора и первым входом сумматора, о тличающийся тем, что, с целью расширения функциональных возможностей преобразователя, введены блок формирования нормального унитарного кода, формирователь кода и блок коррекции сигнала обратной связи, первый вход которого соединен с выходом блока управления, второй вход соединен с первым выходом многопорогового компаратора и первым входом формирователя кода, а выход соединен со вторым входом усилителя с перестраиваемым коэффициентом передачи, причем второй выход многопорогового компаратора через блок формирования нормального унитарного кода соединен с входом дешифратора, выход которого соединен со вторым входом формирователя кода, выход которого соединен со вторым входой сумматора. Источники информации принятые во внимание при экспертизе 1. Автометрия, №.3, 1973, с.104. 2. Приборы и техника эксперимента, 2, 1979, с. 96.

Выход

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ПРИБЛИЖЕНИЯ | 2004 |

|

RU2275739C2 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ - КОД | 1991 |

|

RU2027303C1 |

| Устройство для преобразования перемещения в код | 1981 |

|

SU978174A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU947956A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Устройство для измерения частоты сердечных сокращений | 1990 |

|

SU1759401A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1312737A1 |

Авторы

Даты

1981-06-15—Публикация

1979-09-27—Подача