Изобретение относится к цифровой вычислительной технике и может быть использовано при построении устройств передачи информации в системах управлениях технологическими-процессами промыншенных предприятий.

Цель изобретения - упрощение преобразователя.

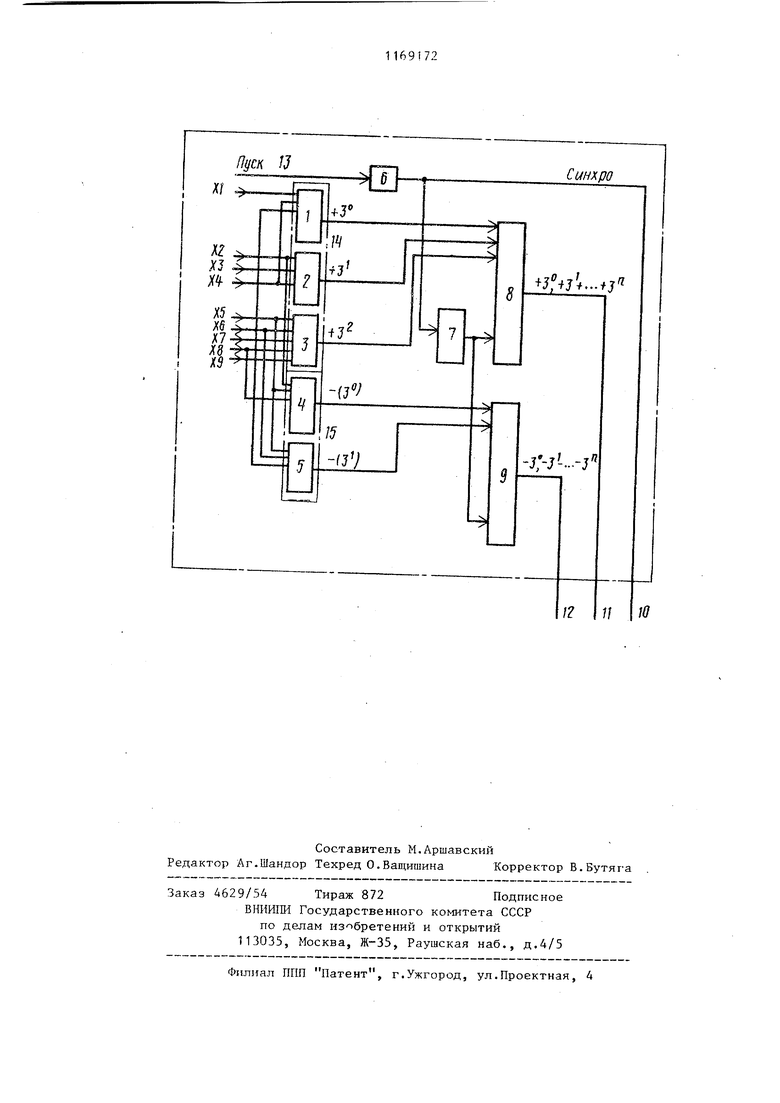

На чертеже приведена блок-схема предлагаемого преобразователя.

Преобразователь содержит элементы ИЛИ 1-5, генератор 6 импульсов, счетчик 7, первый 8 и второй 9 коммутаторы, тактовый выход 10, выходы положительного 11 и отрицательного 12 разрядов преобразователя, вход 13 пуска преобразователя. Элементы ИЛИ 1-3 в совокупности образуют первую группу 14 элементов ИЛИ, а элементы ИЛИ 4 и 5 - вторую группу 15 элементов ИЛИ.

Предлагаемый преобразователь работает следующим образом.

На входы XI-Х9 подается двоичный код, подлежащий преобразованию. При этом возбуждаются линии, соответствующие троичному числу, которое требуется передать по каналам передачи информации. Каналов троичного кода два положительный с кодовой последовательностью о, , отрицательный с кодовой последовательностью , -(3)j . Выходы элементов ИИИ 1-3 подают соответственно положительному каналу троичных кодов положительные потенциалы на входы коммутатора 8, а элементы ШШ 4 и 5 подают соответственно отрицательному каналу кодов положительные потенциалы на входы .коммутатора 9. Тактовые импульсы подаются на входы счетчика 7, который синхронно управляет KONSMyTaTopaми, преобразующими параллельный код в последовательный.

С выхода коммутатора 8 в один канал поступает положительная последовательность троичных кодов, а с выхода коммутатора 9 в другой канал поступает отрицательная последовательность троичных кодов. Полярность серии троичных кодов со знаком +1,0 в линии положительна. Полярность серии троичных кодов со знаком -1,0 при отдельном канале тоже положительна, а полярность серии троичных кодов при общем канале с кодами со знаком +1,0 отрицательна. В общем получается код +1,0-, -1.

Применение передачи информации с троичным кодом ограничивается ассортиментом троичных логических элементов. В основном это магнитные элементы с малой по сравнению с полупроводниковыми микросхемами скоростью переключения.

Использование предложенного преобразователя двоичного кода в троичный код обеспечивает применение полупроводниковых двоичных логических элементов вместо магнитных троичных, упрощение и удешевление преобразователя, увеличение быстродействия.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичной последовательности в балансный троичный код | 1991 |

|

SU1807561A1 |

| Преобразователь троичного кода 1,0,1 в двоичный код | 1978 |

|

SU741261A1 |

| Преобразователь двоично-десятичного кода в код восьмисегментного индикатора | 1983 |

|

SU1130857A1 |

| Преобразователь двоично-десятичного кода в код семисегментного индикатора | 1980 |

|

SU898416A1 |

| Преобразователь троично-десятичного кода в код семисегментного индикатора | 1982 |

|

SU1092488A1 |

| Преобразователь четырехпозиционного временного кода в двоичный код | 1990 |

|

SU1797162A1 |

| Преобразователь троичного кода 1,0,1 в двоичный код | 1979 |

|

SU773615A1 |

| Преобразователь троичного кода 1,0,1 в двоичный код | 1982 |

|

SU1078423A1 |

| Преобразователь троично-десятичного кода в код восьмисегментного индикатора | 1983 |

|

SU1107117A1 |

| Преобразователь последовательного троичного кода в десятичный код | 1983 |

|

SU1172018A1 |

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ТРОИЧНЫЙ КОД, содержапцш генератор импульсов, отличающийс я тем, что, с цедГью упрощения преобразователя, он содержит две группы элементов ИЛИ, первый и второй коммутаторы, счетчик импульсов, вход которого соединен с выходом генератора импульсов, соединенного с тактовым выходом преобразователя, выходы положительного и отрицательного разрядов которого соединены соответственно с выходами первого и второго коммутаторов, управляющие входы которых соединены с выходами счетчика., а группы информационных входов первого и второго коммутаторов соответственно соединены с выходами соответствующих элементов ИЛИ первой и второй групп, причем входы первого и второго разрядов преобразователя соединены соответственно с nepBbiNm входами первого и второго элементов ИЛИ первой группы, вторые входы которых соединены с входом четвертого разряда преобразователя, вход третьего разряда которого соединен с третьим входом второго элемента ИЛИ первой группы, входы с первого по пятый третьего § элемента ИЛИ первой группы соединены сл соответственно с входами с пятого по девятый разрядов преобразователя, входы второго, пятого и восьмого разрядов которого соединены соответственно с первым, вторым и третьим входами первого элемента ИЛИ второй группы, первый, второй и третий входы второго элемента ИЛИ которой соединены соответственно с входами пятого, шестого и седьмого разрядов преобраО) зователя, вход седьмого разряда и со вход пуска которого соединены соответственно с третьим входом первого элемента ШШ первой группы и входом генератора импульсов.

| Соколов Т.Н., Васильев Ф.А | |||

| Ферритовые логические элементы и узлы информационных систем | |||

| Л., 1970, с | |||

| Способ укрепления под покрышкой пневматической шины предохранительного слоя или манжеты | 1917 |

|

SU185A1 |

| Коридорная многокамерная вагонеточная углевыжигательная печь | 1921 |

|

SU36A1 |

| Шифратор троичного кода 1,0,1 | 1978 |

|

SU750479A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-23—Публикация

1983-06-01—Подача