Изобретение относится к устройствам передачи данных и может найти применение в телекоммуникационных системах, системах радиосвязи, радионавигации и управления, функционирующих в неблагоприятной помеховой обстановке.

Известны системы передачи данных, например, по патентам РФ 2249914, Н04В 7/00, 2003 г., 2258313, Н04К 3/00, H04L 27/26, 2004 г., в которых предлагается реализация передачи и приема многочастотных сигналов.

Основным недостатком этих систем является использование на приемной стороне генератора тактовых импульсов, который должен подстраиваться в процессе приема информации, а это, во-первых, инерционный процесс, во-вторых, реализуется с применением довольно сложного контура фазовой автоподстройки.

Наиболее близким по технической сущности к предлагаемому является устройство для передачи данных, описанное в патенте РФ 2242789, G06F 13/14, опубл. 20.12.2004 г.], принятое за прототип.

На фиг.1 изображена блок-схема устройства-прототипа, где обозначено:

1 - двухканальный преобразователь параллельного кода в последовательный (ППс);

2 - генератор тактовых импульсов;

9 - блок формирования синхросигнала;

13 - двухканальный преобразователь последовательного кода в параллельный (ППр);

14 - блок передачи данных (БПРД);

15 - канал связи;

16 - блок приема данных (БПРМ);

17-20 - с первого по четвертый усилители;

21, 22 - первый и второй регулируемые элементы задержки;

23, 24 - первый и второй компьютеры.

Устройство-прототип содержит блок передачи данных 14 и блок приема данных 16, соединенные каналом связи 15.

Блок передачи данных 14 содержит генератор тактовых импульсов 2, выход которого соединен с входом синхронизации ППс 1, два выхода данных первого и второго каналов которого соединены соответственно с входами первого 17 и второго 18 усилителей, выходы которых являются выходами БПРД 14. При этом выход готовности ППс 1 соединен с входным портом первого компьютера 23, выходной порт которого соединен с группой входов данных ППс 1.

Блок приема данных 16 содержит третий 19 и четвертый 20 усилители, выходы которых соединены с входами первой 21 и второй 22 регулируемых элементов задержки соответственно, выходы которых соединены с соответствующими входами блока формирования синхросигнала 9 и соответствующими входами данных первого и второго каналов ППр 13, группа выходов данных которого подсоединена к первому входному порту второго компьютера 24, второй входной порт которого соединен с выходом готовности ППр 13. Кроме того, группы управляющих входов первого 21 и второго 22 регулируемых элементов задержки подсоединены соответственно к первому и второму выходным портам второго компьютера 24. При этом выход блока формирования синхросигнала 9 соединен с входом ППр 13. Входы первого 19 и второго 20 усилителей являются входами БПРМ 16.

Устройство-прототип работает следующим образом. Компьютер 23 хранит данные, которые должны быть переданы в компьютер 24. Эти данные могут быть сформированы, например, в результате опроса датчиков либо получены по каналам связи (датчики и каналы связи на фиг.1 не показаны) и т.д. Данные основного канала скремблируются и побайтно передаются через выходной порт компьютера 23 в ППс 1. Передаче каждого байта предшествует проверка сигнала готовности, который поступает во входной порт компьютера 23. Выдача очередного байта компьютером 23 в выходной порт происходит только при обнаружении очередного сигнала готовности в его входном порте. Все процессы, протекающие при передаче данных, синхронизированы сигналами от генератора тактовых импульсов 2. Этот генератор формирует непрерывную последовательность синхроимпульсов со скважностью, равной двум. Период синхросигнала равен длительности битового интервала.

ППс 1 по положительному фронту синхросигнала принимает байт данных и формирует на своих выходах две последовательности битов - основную и дополнительную, которые через усилители 17 и 18 передаются по каналу связи 15.

Переданные по каналу связи 15 ослабленные сигналы усиливаются в усилителях 19 и 20. Разность задержек сигналов с выходов усилителей 19 и 20 компенсируется регулируемыми элементами задержки 21 и 22. Выравненные по времени сигналы поступают на соответствующие входы блока формирования синхросигнала 9 и одновременно поступают на соответствующие входы ППр 13. С выхода блока 9 синхросигнал поступает на соответствующий вход ППр 13. По положительному фронту синхросигнала ППр 13 из последовательных потоков данных формирует параллельные потоки данных. По сигналу готовности вновь сформированного байта параллельного кода, поступающему во второй порт компьютера 24. С группы выхода данных ППр 13 через первый порт компьютером 24 осуществляется считывание данных. Принятые данные размещаются в памяти компьютера 24 и анализируются. Определяются границы информационных кадров, из потока данных удаляются биты синхронизации, данные, полученные из канала связи 15 дескремблируются, с помощью избыточных циклических кодов проверяется правильность принятых кадров. Выполняется программа поиска области работоспособности путем декодирования информации о положении границ между кадрами, передаваемыми по обеим линиям канала связи 15, что позволяет компьютеру 24 восстановить исходную структуру принятых из канала данных. Далее компьютером 24 осуществляется процесс адаптации устройства-прототипа к разности задержек, которыми сопровождается передача данных по линиям канала связи 15. Проводится несколько серий экспериментов с различными задержками и в каждом эксперименте проверяется правильность приема данных по обеим линиям. При этом если параметры канала связи 15 периодически изменяются, то адаптация устройства-прототипа к таким изменениям будет проводиться довольно часто, чтобы вовремя отслеживать такие изменения.

Недостатки устройства-прототипа следующие:

- наличие схем скремблирования и дескремблирования данных для преобразования блоков единиц и нулей двоичной последовательности в блоки со случайным сочетанием нулей и единиц, что усложняет реализацию передающего и приемного устройств;

- наличие двух линий канала связи, одна из которых предназначена для передачи большей части данных, вторая - для передачи синхронизирующей информации и остальной части данных, передача которых по второй линии возможна, благодаря скремблированию из-за неидентичности линий по времени распространения требует определения разности задержки распространения сигналов по этим линиям;

- наличие блока формирования синхросигнала в виде генератора с инерционной системой ФАПЧ;

- обязательное наличие двух компьютеров, которые кроме других стандартных операций реализуют алгоритм адаптации устройства-прототипа к разности задержек распространения сигналов по двум линиям канала связи.

Для устранения указанных недостатков в устройство для передачи цифровой информации, состоящее из соединенных линией связи блока передачи данных (БПРД) и блока приема данных (БПРМ), при этом БПРД содержит преобразователь параллельного кода в последовательный (ППс), вход синхронизации которого соединен с выходом генератора тактовых импульсов (ГТИ), БПРМ содержит последовательно соединенные блок выделения синхросигнала (БВС) и преобразователь последовательного кода в параллельный (ППр), согласно изобретению введены: в БПРД - последовательно соединенные преобразователь двоичного кода в код с тремя состояниями (ПДТ), модулятор и передатчик данных (ПРД), выход которого является выходом БПРД, вход синхронизации ПДТ подсоединен к выходу ГТИ, N входов ППс являются входами БПРД; в БПРМ - последовательно соединенные приемник данных (ПРМ) и демодулятор, выходы которого соединены с соответствующими входами формирователя троичного кода (ФТК), выходы которого соединены с соответствующими входами БВС, блока коррекции ошибок (БКО) и блока контроля длительности стираний (БКД), при этом первый и второй выходы БКО соединены соответственно с первым и вторым входами преобразователя троичного кода в двоичный (ПТД), выход которого соединен со вторым входом ППр, N выходов которого являются выходами БПРД, причем выход БКД соединен с пятым входом БКО, третий выход которого соединен с четвертым входом БВС, первый выход которого соединен с первым входом ППр и четвертым входом БКО, шестой вход которого подсоединен ко второму выходу БВС.

Блок-схема предлагаемого устройства представлена на фиг.2, где обозначено:

1 - преобразователь параллельного кода в последовательный (ППс);

2 - генератор тактовых импульсов (ГТИ);

3 - преобразователь двоичного кода в код с тремя состояниями (ПДТ);

4 - модулятор;

5 - передатчик данных (ПРД);

6 - приемник данных (ПРМ);

7 - демодулятор;

8 - формирователь троичного кода (ФТК);

9 - блок выделения синхросигнала (БВС);

10 - блок коррекции ошибок (БКО);

11 - блок контроля длительности стираний (БКД);

12 - преобразователь троичного кода в двоичный (ПТД);

13 - преобразователь последовательного кода в параллельный (ППр);

14 - блок передачи данных (БПРД);

15 - линия связи (ЛС);

16 - блок приема данных (БПРМ).

Предлагаемое устройство содержит БПРД 14 и БПРМ 16, соединенные линией связи 15.

БПРД 14 содержит последовательно соединенные ППс 1, ПДТ 3, модулятор 4 и ПРД 5, выход которого является выходом БПРД 14. При этом выход ГТИ 2 соединен с входами синхронизации ППс 1 и ПДТ 3, два других выхода которого соединены с соответствующими входами модулятора 4. N входов ППс 1 являются входами БПРД 14.

БПРМ 16 содержит последовательно соединенные ПРМ 6 и демодулятор 7, три выхода которого соединены с соответствующими входами формирователя троичного кода 8, три выхода которого соединены с соответствующими входами БКО 10, два выхода которого соединены с соответствующими входами ПТД 12, выход которого соединен со вторым входом ППр 13, N выходов которого являются выходами БПРМ 16. Кроме того, выходы ФТК 8 соединены с соответствующими входами БВС 9 и БКД 11, выход которого соединен с пятым входом БКО 10, третий выход которого соединен с четвертым входом БВС 9, первый выход которого соединен с первым входом ППр 13 и четвертым входом БКО 10, шестой вход которого подсоединен ко второму выходу БВС 9.

Предлагаемое устройство работает следующим образом.

Данные от различных источников одновременно поступают на соответствующие входы блока ППс 1, на его синхронизирующий вход поступают тактовые импульсы с выхода блока ГТИ 2. Блок ППс 1 в соответствии с тактовыми импульсами формирует последовательность двоичных данных (битов), которая с его выхода поступает на вход блока ПДТ 3, на синхронизирующий вход которого поступают тактовые импульсы с выхода блока ГТИ 2. В блоке ПДТ 3 на каждом такте над поступающими двоичными символами осуществляют логические операции, результат которых заключается в следующем. Если в блоке нулей или единиц двоичный символ стоит на нечетной позиции, то на первом выходе блока ПДТ 3 появится импульс, а на втором и третьем выходах блока ПДТ 3 одновременно будут нулевые значения. То есть на данном такте сформируют символ троичного кода (столбец, верхний элемент которого, соответствующий первому выходу блока ПДТ 3, ненулевой, а два остальных элемента нулевые), несущий информацию об этой позиции двоичного символа в блоке единиц. Для блока нулей в этом случае на выходе блока ПДТ 3 формируют символ троичного кода (столбец, нижний элемент которого, соответствующий третьему выходу блока ПДТ 3, ненулевой, а два остальных, нулевые), несущий информацию об этой позиции двоичного символа в блоке нулей. Если же в блоке нулей или единиц двоичный символ занимает четную позицию, то формируют третий символ троичного кода (столбец, средний элемент которого, соответствующий второму выходу блока ПДТ 3, ненулевой, а два остальных элемента нулевые), несущий информацию о соответствующей позиции двоичного символа в блоке нулей или в блоке единиц. При этом в потоке символов троичного кода не бывает смежных символов с одинаковым состоянием (двух одинаковых смежных столбцов). Далее на каждом такте символы троичного кода с выходов блока ПДТ 3 поступают на соответствующие входы блока 4, где осуществляют модуляцию несущей частоты параметрами, значения которых выбираются в соответствии с символом троичного кода. Модуляция может быть частотной, фазовой, кодовой (например, коды Баркера), то есть каждый символ троичного кода модулируется либо своей частотой либо своей фазой и т.д. С выхода блока 4 модулированный сигнал поступает на вход блока ПРД 5, с выхода которого он излучается в ЛС 15.

В блоке приема данных 16 полезные модулированные сигналы с выхода БПРД 14 через ЛС 15 поступают на вход блока ПРМ 6, с выхода которого поступают на вход блока 7, где демодуляцией выделяют искаженные символы троичного кода, доставленные сигналами, которые с выходов блока 7 поступают на соответствующие входы блока ФТК 8, где их корректируют. С выходов блока ФТК 8 они поступают на соответствующие входы блоков БКО 10, БВС 9 и БКД 11. При этом в формирующемся потоке символов троичного кода не должно быть одинаковых смежных символов. В блоке БКД 11 введенную таким образом избыточность используют для контроля длительности стираний, при этом, если длительность стирания больше 1,5·τ (τ - длительность информационного двоичного символа), то с выхода блока БКД 11 на пятый вход блока БКО 10 поступит короткий импульс сброса устройства в исходное состояние. Если же длительность стирания не больше 1,5·τ, то стертый (подавленный) символ троичного кода (нулевой столбец) поступает на соответствующие входы блока БКО 10. Одновременно в блоке БВС 9 на каждом такте из поступающих символов троичного кода выделяют синхроимпульсы, которые с его выхода поступают на четвертый вход блока БКО 10 и первый вход блока ППр 13, согласуя работу блоков БКО 10, ППр 13 и ПТД 12. В блоке БКО 10, используя тот факт, что не может быть двух одинаковых смежных символов троичного кода, на каждом такте выделяют триаду таких символов (матрицу) и логическими операциями над элементами столбцов триады корректируют средний стертый символ (столбец) в триаде. Далее первый и третий элементы символов троичного кода (элементы столбцов) с выходов блока БКО 10 поступают на соответствующие входы блока ПТД 12, где логическими операциями над ними восстанавливают поток принятых двоичных символов. Этот поток двоичных символов поступает на второй вход блока ППр 13, где под управлением синхроимпульсов, поступающих с первого выхода блока БВС 9, формируют исходные параллельные данные. Если в блоке БВС 9 произойдет потеря более чем одного синхроимпульса или будут стерты первый или последний символы последовательности символов троичного кода, то с его второго выхода на шестой вход блока БКО 10 поступит короткий импульс сброса устройства в исходное состояние. Если в блоке БКО 10 ошибка не может быть исправлена, то этот блок формирует короткий импульс сброса устройства в исходное состояние.

Реализация блоков предлагаемого устройства не представляет затруднений, так как схемные решения их общеизвестны. Блоки ППс 1, ГТИ 2 и ППр 13 соответствуют аналогичным блокам прототипа. Отличие блока 13 в прототипе заключается в том, что он двухканальный.

Обобщенная структурная схема m-позиционного модулятора ортогональных сигналов (блок 4) может быть выполнена, например, как представлена в [Б.Скляр. Цифровая связь. Москва, С-Петербург, Киев, 2003, стр.339-341, рис.6.4]. Структурная схема и описание работы многофазного модулятора приведены там же на стр.232-234, рис.4.23. Схема амплитудно-фазового модулятора (QAM) приведена на стр.585-586, рис.9.16. В частности, трехчастотный модулятор представляет собой автогенератор (например, [Ю.И.Судаков. Амплитудная модуляция и автомодуляция транзисторных генераторов. М.: Энергия, 1969, стр.32, рис.1-20 (б)]), к контуру которого с помощью ключей подключаются емкости различной величины. Ключи управляются поступающими с соответствующих выходов блока ПДТ 6 на их управляющие входы элементами троичных символов.

Блоки ПРД 5 и ПРМ 6 легко реализуются радиомодулями [В.Кученко. Миниатюрные радиомодули для передачи цифровой информации. Радиолюбитель, 11/96, стр.39, рис.1, рис.2].

Блок-схема блока ПДТ 3 представлена на фиг.3, где обозначено:

3.1. 3.4 - первый и второй блоки суммирования по модулю 2 (mod2);

3.2, 3.3 - первый и второй блоки динамической памяти (ДП);

3.5-3.7 - первый второй и третий блоки инверсии (НЕ);

3.8 - блок И.

Блок ПДТ 3 содержит последовательно соединенные первый блок mod2 3.1 и второй блок НЕ 3.6, выход которого соединен с первым входом блока И 3.8, при этом выход блока mod2 3.1 соединен с первым входом первого блока ДП 3.2, выход которого соединен со вторым входом блока mod2 3.1, первый вход которого является входом ПДТ 3 и соединен с входом первого блока НЕ 3.5, выход которого соединен с первым входом второго блока mod2 3.4, выход которого соединен с первым входом второго блока ДП 3.3 и входом третьего блока НЕ 3.7, выход которого соединен со вторым входом блока И 3.8. Вторые входы первого ДП 3.2 и второго ДП 3.3 блоков соединены и являются синхронизирующим входом блока ПДТ 3, причем выход второго блока ДП 3.3 соединен со вторым входом второго блока mod2 3.4.

При этом выход первого блока mod2 3.1 является выходом первого элемента символа троичного кода, выход третьего блока И является выходом второго элемента символа троичного кода, выход второго блока mod2 3.4 - выходом третьего элемента символа троичного кода.

Блок ПДТ 3 работает следующим образом.

В начальном состоянии в первом и втором блоках ДП 3.2 и 3.3 хранится значение нуля.

На синхронизирующий вход блока ПДТ 3 поступает поток двоичных символов в виде блоков единиц и нулей различной длины, на вход блока ПДТ 3 поступают тактовые импульсы, при этом двоичные символы одновременно поступают на первый вход первого блока mod2 3.1 и на вход первого блока НЕ 3.5, тактовые импульсы, одновременно поступающие на вторые входы первого 3.2 и второго 3.3 блоков ДП, определяют моменты поступления с выходов первого 3.2 и второго 3.3 блоков ДП на вторые входы первого 3.1 и второго 3.4 блоков mod2 хранящихся там значений. При поступлении на вход блока ПДТ 3 двоичной единицы на первые входы блоков mod2 31. и 3.4 поступят соответственно двоичная единица и двоичный нуль, одновременно на их вторые входы поступят значения двоичных нулей. При этом с выхода первого блока mod2 3.1 выйдет двоичная единица, с выхода второго блока mod2 3.4 выйдет двоичный нуль, на первый и второй входы блока И 3.8 и на входы первого 3.2 и второго 3.3 блоков ДП поступят соответственно двоичный нуль и двоичная единица, значит, с выхода блока И 3.8 выйдет двоичный нуль. Таким образом, на втором и третьем выходах блока ПДТ 3 появятся нули, а на первом выходе - единица. Это значит, что второй и третий входы блока 4 (фиг.2) будут «заперты», а первый вход «открыт», значит, на входы блока 4 поступит символ троичного кода (столбец), несущий информацию о том, что текущий двоичный символ занимает нечетную позицию в блоке единиц. Если на второй вход блока ПДТ 3 снова поступит двоичная единица, то так как на этом такте в первом блоке ДП 3.2 вместо нуля хранится единица, которая в этот момент поступит на второй вход первого блока mod2 3.1, с его выхода выйдет уже не единица, а нуль, в то время как с выхода второго блока mod2 3.4 по-прежнему выйдет нуль. При этом с выходов второго 3.6 и третьего 3.7 блоков НЕ на соответствующие входы блока И 3.8 поступят единицы, значит, на его выходе получится единица. Следовательно, на первом и третьем выходах блока ПДТ 3 появятся нули, а на втором выходе - единица. Это значит, что первый и третий входы блока 4 (фиг.2) будут «заперты», а второй вход «открыт» и на его вход поступит символ троичного кода (столбец), несущий информацию о том, что текущий двоичный символ занимает четную позицию в блоке единиц, то есть информацию о повторении двоичного символа в блоке единиц.

Аналогично блок ПДТ 3 работает и при поступлении на его вход блока двоичных нулей или чередующихся нуля и единицы.

Принципиальная схема и работа блоков mod2 3.1, mod2 3.4 приведены в [Микросхемы и их применение. Вып. 1070. М.: Радио и связь, 1980, стр.127-128, рис.4.23 (а)], а также в [М.Мэндл. 200 избранных схем электроники. / Пер. с англ. под ред. Я.С.Ицхоки. М.: Мир, 1980, стр.183-184, рис.8.8 (а)]. Варианты реализации блоков ДП 6.2, ДП 6.3 даны, например, в [Ф.Мейдза. Интегральные схемы. Технология и применение. М.: Мир, 1981, стр.129-131, рис.5.7], [О.Н.Лебедев. Применение микросхем памяти в электронных устройствах. М.: Радио и связь, 1999, стр.98-104]. Схемы и работа логических блоков НЕ 6.5-НЕ 6.7 и И 6.8 представлены в [М.Мэндл. 200 избранных схем электроники. / Пер. с англ. под ред. Я.С.Ицхоки. М.: Мир, 1980, стр.176-181, рис.8.3 (б), 8.6 (б)].

Общие структурные схемы многопозиционных демодуляторов когерентных и некогерентных сигналов (варианты построения демодулятора 7) даны в [А.Г.Зюко, Ю.Ф.Коробов. Теория передачи сигналов. М.: Связь, 1972, стр.136-140, рис.5.8, рис.5.9]. Частный вариант реализации m-фазного демодулятора разработан в [В.Б.Стешенко и др. Демодулятор максимального правдоподобия, использующий межсимвольную фазовую связь и декодер Витерби. Цифровая Обработка Сигналов, №1, 2005, стр.19-25].

Блок-схема блока БКД 11 представлена на фиг.4, где обозначено:

11.1 - блок логического суммирования (ИЛИ);

11.2, 11.5 - первый и второй блоки логического отрицания (НЕ);

11.3, 11.6 - первый и второй блоки дифференцирования (БД);

11.4 - одновибратор (OB);

11.7 - блок логического умножения (И).

Блок БКД 11 содержит последовательно соединенные блок ИЛИ 11.1, первый блок НЕ 11.2, первый блок БД 11.3, блок ОВ 11.4, второй блок НЕ 11.5, второй блок БД 11.6 и блок И 11.7, выход которого является выходом БКД 11. При этом выход первого блока НЕ 11.2 соединен со вторым входом блока И 11.7. Три входа блока ИЛИ 11.1 являются соответствующими входами БКД 11.

Блок БКД 11 работает следующим образом.

На каждом такте на входы блока ИЛИ 11.1 с соответствующих выходов блока ФТК 8 (фиг.2) поступают символы троичного кода (столбцы), характеризующие позицию двоичных символов в блоках единиц и нулей исходной двоичной последовательности. Если символы троичного кода не будут ошибочными, то в столбцах одним из элементов всегда будет единица, значит, на входе первого блока БД 11.3 и на втором входе блока И 11.7 будет логический нуль. При этом независимо от того, что поступит на первый вход блока И 11.7, на протяжении этих тактов на его выходе будет логический нуль, который будет блокировать сброс устройства в исходное состояние.

В случае наличия ошибочных символов троичного кода в соответствующих столбцах все элементы будут нулевыми, значит, на второй вход блока И 11.7 и на вход первого блока БД 11.3 поступит логическая единица. Одновременно импульс с выхода первого блока БД 11.3 запустит одновибратор ОВ 11.4, с выхода которого выйдет импульс длительностью 1,5·τ. При этом на вход второго блока БД 11.6 поступит инвертированный импульс длительностью 1,5·τ (то есть логический нуль такой же длительности). Следовательно, по окончании нулевого импульса с выхода второго блока БД 11.6 на первый вход блока И 11.7 поступит короткий импульс. Если ошибочен только один троичный символ, то есть длительность нуля (длительность стирания) на входе второго блока БД 11.6 не более 1,5·τ, то в момент поступления на первый вход блока И 11.7 короткого импульса с выхода второго блока БД 11.6 единица с выхода первого блока НЕ 11.2 уже уступит место нулю и с выхода блока И 11.7 выйдет логический нуль, блокируя сброс устройства в исходное состояние. Если же ошибочны подряд два и более символов троичного кода, то на втором входе блока И 11.7 единица будет сохраняться во времени больше чем 1,5·τ. Одновременно с поступлением этой единицы на второй вход блока И 11.7 она же поступает на вход первого блока БД 11.3, с выхода которого короткий импульс запускает одновибратор ОВ 11.4. Импульс длительностью 1,5·τ с выхода одновибратора ОВ 11.4 инвертируется вторым блоком НЕ 11.5 (стирание) и поступает на вход второго блока БД 11.6. По окончании этого нуля (через время 1,5·τ) с выхода второго блока БД 11.6 на первый вход блока И 11.7 поступит короткий импульс, но в это время на второй вход блока И 11.7 еще подана единица. Значит, с выхода блока И 11.7 выйдет короткий импульс, который сбросит устройство в исходное состояние.

Таким образом, блок БКД 11 разрешает проходить на входы блока БКО 10 только по одному стертому символу троичного кода, то есть может пропускать «лесенку» стертых символов. В противном случае блок БКД 11 осуществляет сброс всего устройства в исходное состояние.

Работу блока БКД 11 в случае стираний дополнительно поясняют временные диаграммы, представленные на фиг.5.

Принципиальная схема и работа блока ИЛИ 11.1 (двух и более входовых) приведены в [М.Мэндл. 200 избранных схем электроники. / Пер. с англ. под ред. Я.С.Ицхоки. М.: Мир, 1980, стр.175-176, рис.8.2 (б)]. Варианты реализации блоков БД 11.3, БД 11.6 даны, например, в [И.С.Гоноровский. Радиотехнические цепи и сигналы. М.: Сов. радио, 1977, стр.222-223, рис.6.5 (б)], [С.И.Баскаков. Радиотехнические цепи и сигналы. М.: Высшая школа, 1983, стр.252-253]. Схема и работа блока типа ОВ 11.4 представлены в [Применение интегральных схем. Практическое руководство, кн.1. М.: Мир, 1987, стр.416-417, рис.7.7 (а)] или в [У.Титце, К.Шенк. Полупроводниковая схемотехника. М.: Мир, 1982, стр.98-99, рис.8.14].

Блок-схема БВС 9 представлена на фиг.6, где обозначено:

9.1-9.3, 9.18, 9.21, 9.30 - с первого по шестой блоки логического умножения (И);

9.4-9.6, 9.20, 9.26, 9.27, 9.33, 9.34 - с первого по восьмой блоки логического отрицания (НЕ);

9.7-9.12, 9.22, 9.28, 9.29, 9.35, 9.36 - с первого по одиннадцатый блоки дифференцирования (БД);

9.24, 9.25 - первый и второй одновибраторы на длительность информационного импульса (ОВ);

9.13-9.16, 9.31, 9.32, 9.37 - с первого по седьмой блоки логического сложения (ИЛИ);

9.17 - одновибратор на время равное длительности информационного сообщения минус половина длительности информационного импульса (Тсообщ - τ/2);

9.19 - десятичный счетчик на заданное число (СЧ);

9.23 - одновибратор на время равное длительности трех информационных импульсов (3τ);

9А - часть блока БВС 9, вырабатывающая первые n синхроимпульсов;

9В - часть блока БВС 9, вырабатывающая три последних синхроимпульса.

Блок БВС 9 содержит часть 9А, вырабатывающую первые n синхроимпульсов и часть 9В, вырабатывающую три последних синхроимпульса.

Часть блока 9А содержит последовательно соединенные первый блок И 9.1, первый блок НЕ 9.4, первый блок БД 9.7 и первый блок 9.13, последовательно соединенные второй блок И, второй блок НЕ 9.5, третий блок БД 9.9 и второй блок ИЛИ 9.14, последовательно соединенные третий блок И 9.3, третий блок НЕ 9.6, пятый блок БД 9.11 и третий блок ИЛИ 9.15. Кроме того, выход первого блока И через второй блок БД 9.8 соединен со вторым входом первого блока ИЛИ, выход которого соединен с первым входом четвертого блока ИЛИ 9.16, выход второго блока И 9.2 через четвертый блок БД 9.10 соединен со вторым входом второго блока ИЛИ 9.14, выход которого соединен со вторым входом четвертого блока ИЛИ 9.16, выход третьего блока И 9.3 через шестой блок БД 9.12 соединен со вторым входом третьего блока ИЛИ 9.15, выход которого соединен с третьим входом четвертого блока ИЛИ 9.16. При этом первые сигнальные входы блоков И 9.1-И 9.3 являются входами для соответствующих элементов троичных символов (столбцов), поступающих с соответствующих выходов блока ФТК 8 (фиг.2).

Часть блока 9В содержит последовательно соединенные блок ОВ на Т-τ/2 9.17, четвертый блок И 9.18, СЧ 9.19, четвертый блок НЕ 9.20 и седьмой блок 9.22, последовательно соединенные первый блок ОВ 9.24, пятый блок НЕ 9.26 и восьмой блок БД 9.28, выход которого соединен со вторым входом шестого блока ИЛИ 9.32 и с входом второго блока ОВ 9.25, выход которого через последовательно соединенные шестой блок НЕ 9.27 и девятый блок БД 9.29 соединен с третьим входом шестого блока ИЛИ 9.32, последовательно соединенные восьмой блок НЕ 9.34, десятый БД 9.35, ОВ на 3τ 9.23, выход которого соединен с входом седьмого блока НЕ 9.33 и первым входом шестого блока И 9.30, выход которого соединен со вторым входом пятого блока ИЛИ 9.31, выход которого является первым выходом блока 9. Выход блока ОВ на Т-τ/2 9.17 соединен с входом восьмого блока НЕ 9.34 и первым входом блока И 9.21, выход которого соединен с первым входом седьмого блока ИЛИ 9.37, выход которого является вторым выходом блока 9. Выход блока БД 9.22 соединен с входом первого блока ОВ 9.24, со вторым входом пятого блока И 9.21 и первым входом шестого блока ИЛИ 9.32, выход которого подсоединен ко второму входу шестого блока И 9.30. Выход блока ОВ на 3τ 9.23 соединен с входом седьмого блока НЕ 9.33, выход которого соединен со вторыми входами трех блоков И 9.1, 9.2, 9.3,и через одиннадцатый блок БД 9.36 соединен со вторым входом седьмого блока ИЛИ 9.37. Кроме того, выход четвертого блока ИЛИ 9.16 соединен со вторым входом четвертого блока И 9.18 и с первыми входами пятого блока ИЛИ 9.31 и ОВ на Т-τ/2 9.17, второй вход которого и второй вход счетчика 9.19, и первый вход ОВ на 3τ 9.23 подсоединены к четвертому входу БВС 9.

Работу блока БВС 9 поясняют временные диаграммы, представленные на фиг.7-10. На фиг.7 показаны временные диаграммы при безошибочном приеме в наиболее важных точках части блока 9А: а) - исходная последовательность двоичных символов; б), в) и г) - элементы символов троичного кода (элементы столбцов), поступающие с выходов ФТК 13 на соответствующие входы БВС 9. Первый синхроимпульс с выхода блок ИЛИ 9.16 поступает на вход блока ОВ 9.17 и запускает его, одновременно этот синхроимпульс поступает на первый вход блока ИЛИ 9.31. Пока блок ОВ 9.17 выдает на выходе единицу с выхода блока И 9.30 и работает блок СЧ 9.19, на второй вход блока ИЛИ 9.31 поступает нуль, с выхода блока НЕ 9.33 на вторые управляющие входы блоков И 9.1-И 9.3 поступает единица, разрешая вход символам троичного кода. Следовательно, с выхода блока ИЛИ 9.31 все это время будут поступать синхроимпульсы. Таким образом, за время длительности сообщения на каждом такте на выходе БВС 9 формируется синхронизирующий импульс.

На фиг.8 показаны временные диаграммы при безошибочном приеме в наиболее важных точках части блока 9В. В момент прихода на вход блока СЧ 9.19 последнего синхроимпульса (за время τ/2 до окончания работы блока ОВ 9.17) с выхода блока СЧ 9.19 выйдет импульс длительностью τ. По окончании работы блока ОВ 9.17 на его выходе будет нуль. В этот момент импульс с выхода блока БД 9.35 запустит блок ОВ 9.23, а через время τ/2 с выхода блока БД 9.22 на вход блока ОВ 9.24 и на первый вход блока ИЛИ 9.32 поступит первый дополнительный синхроимпульс. В момент запуска блока ОВ 9.23 с выхода блока НЕ 9.33 на вторые управляющие входы блоков И 9.1-И 9.3 поступит нуль, запрещая проход любых сигналов через эти блоки, то есть на первый вход блока ИЛИ 9.31 поступит нуль. На первый вход блока И 9.30 с выхода блока ОВ 9.23 поступит единица, разрешая прохождение дополнительного синхроимпульса с выхода блока ИЛИ 9.31. Далее через время τ с выхода блока БД 9.28 на второй вход блока ИЛИ 9.32 и на вход блока ОВ 9.25 поступит второй дополнительный синхроимпульс, а еще через время τ с выхода блока БД 9.29 на третий вход блока ИЛИ 9.32 поступит третий дополнительный синхроимпульс. Эти три синхроимпульса через блоки И 9.30 и ИЛИ 9.31 последовательно поступят на выход блока БВС 9. Далее через половину такта блок ОВ 9.23 закончит работу и с выхода блока БД 9.36 через блок ИЛИ 9.37 на шестой вход блока БКО 10 (фиг.2) поступит импульс сброса устройства в исходное состояние для приема очередного сообщения.

На фиг.9 показаны временные диаграммы в наиболее важных точках части блока 9В в том случае, когда за счет действия помех счетчик СЧ 9.19 зафиксирует необходимое количество синхроимпульсов раньше, чем закончит работу блок ОВ 9.17. При этом с выхода блока БД 9.22 на второй вход блока И 9.21 поступит импульс, а на первом входе блока И 9.21 еще будет единица. Значит, с выхода блока ИЛИ 9.37 на шестой вход блока БКО 10 (фиг.2) поступит импульс сброса устройства в исходное состояние.

На фиг.10 показаны временные диаграммы в наиболее важных точках части блока 9В в том случае, когда первый символ троичного кода будет стерт.При этом блок ОВ 9.17 начнет работу на такт позже. На выходе счетчика СЧ 9.19 импульс так и не появится, так как он не зафиксирует необходимое количество синхроимпульсов, следовательно, сброса устройства в исходное состояние не последует. По окончании работы блока ОВ 9.17 с выхода блока БД 9.35 выйдет импульс, который запустит блок ОВ 9.23. До конца работы этого блока устройство будет принимать информацию, но так как часть блока 9В не сформирует три дополнительных синхроимпульса, то три последних символа троичного кода останутся в регистрах СР 8.1-СР 8.3 блока БКО 10 (фиг.2) и правильного приема не будет. По окончании работы блока ОВ 9.23 с выхода блока БД 9.36 через блок ИЛИ 9.37 на шестой вход блока БКО 10 (фиг.2) поступит импульс сброса устройства в исходное состояние.

Работа и временные диаграммы в наиболее важных точках части блока 9В в том случае, когда последний символ троичного кода будет стерт, аналогичны описанному в последнем абзаце, за исключением того, что блок ОВ 9.17 запустится первым синхроимпульсом и начнет работу с первого такта.

Реализация блока СЧ 9.19 представлена в [Микросхемы и их применение. Вып.1070. М.: Радио и связь, 1980, стр.138-139, рис.4.37 (а)] или в [Шило В.Л. Популярные цифровые микросхемы. Справочник.. М.: Радио и связь, 1987 стр.94-97, рис.1.69].

Блок-схема блока БКО 10 представлена на фиг.11, где обозначено:

10.1-10.3 - с первого по третий блоки трехразрядных сдвиговых регистров (СР);

10.4-10.6 - с первого по третий ключи (Кл);

10.7-10.9, 10.14 - с первого по четвертый блоки логического отрицания (НЕ);

10.10-10.12 - с первого по третий блоки суммирования по модулю 2 (mod2);

10.13, 10.21 - первый и второй блоки логического суммирования (ИЛИ);

10.15-10.18, 10.20 - с первого по четвертый и пятый блоки логического умножения (И);

10.19 - блок дифференцирования (БД).

Блок БКО 10 содержит три блока трехразрядных сдвиговых регистров (СР) 10.1, 10.2 и 10.3, первые сигнальные входы которых являются входами для элементов символа троичного кода (элементов столбца), поступающих с соответствующих выходов блока ФТК 8 (фиг.2), а четвертые выходы первого блока 10.1 и третьего блока 10.3 соединены с соответствующими входами блока ПТД 12 (фиг.2), второй, четвертый и шестой входы блоков 10.1-10.3 соединены с первым выходом блока БВС 9 (фиг.2), блоки И 10.16-10.18, 10.20 и блок ИЛИ 10.21, последовательно соединенные блок ИЛИ 10.13 и блок НЕ 10.14, последовательно соединенные блок И 10.15 и блок БД 10.19, последовательно соединенные блок mod2 10.10, блок НЕ 10.7 и Кл 10.4, последовательно соединенные блок mod2 10.11, блок НЕ 10.8 и Кл 10.5, последовательно соединенные блок mod2 10.12, блок НЕ 10.9 и Кл 10.6, третий, пятый и седьмой входы блоков 10.1-10.3 соединены с выходом блока ИЛИ 10.21, восьмые входы блоков 10.1-10.3 соединены с соответствующими выходами ключей 10.4-10.6, первый и третий выходы блоков 10.1-10.3 соединены с сигнальными входами соответствующих блоков mod 2 10.10-10.12, выходы блоков НЕ 10.7-10.9 соединены с соответствующими входами блока И 10.15, первые входы блоков И 10.17, 10.18 соединены с выходом блока mod 2 10.10, вторые входы блоков И 10.16 и 10.18 соединены с выходом блока mod 2 10.12, первый вход блока И 10.16 и второй вход блока И 10.18 соединены с выходом блока mod 2 10.11, вторые выходы блоков 10.1-10.3 соединены с соответствующими входами блока ИЛИ 10.13, выход блока НЕ 10.14 соединен с первым входом блока И 10.20, выход блока БД 10.19 соединен со вторым входом блока И 10.20, выход которого соединен с третьим входом блока ИЛИ 10.21, выход блока И 10.16 соединен с управляющим входом ключа 10.4, выход блока И 10.17 соединен с управляющим входом ключа 10.5, выход блока И 10.18 соединен с управляющим входом ключа 10.6, первый вход блока ИЛИ 10.21 соединен со вторым выходом блока БВС 9 (фиг.2), а второй его вход соединен с выходом блока БКД 11 (фиг.2).

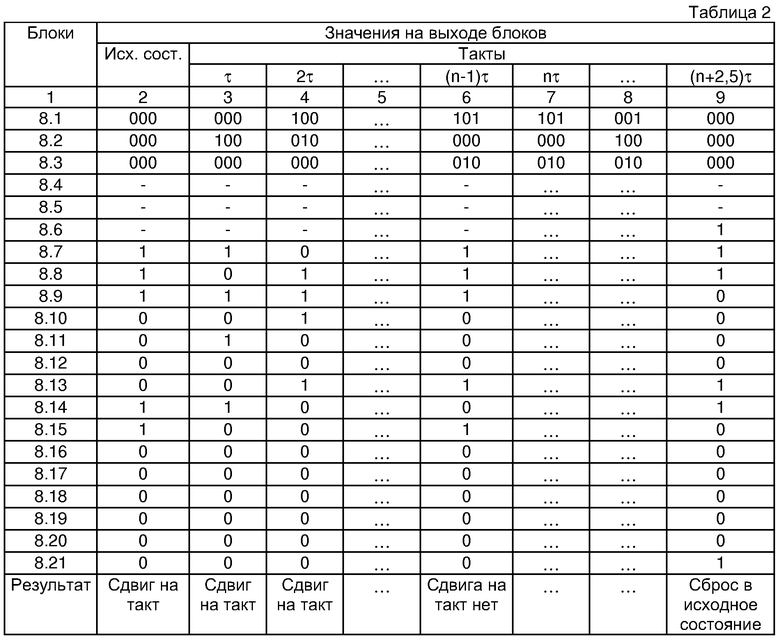

Состояния входов и выходов всех блоков, входящих в БКО 10, определяются состоянием содержимого разрядов регистров 10.1-10.3. В исходном состоянии содержимое блоков 10.1-10.3, таймер и счетчик синхроимпульсов в блоке БВС 9 (фиг.2) обнулены, ключи 10.4-10.5 закрыты. Блок БКО 10 работает следующим образом.

Прием без ошибок, например, следующего фрагмента последовательности двоичных символов: 111101100… При этом на первые сигнальные входы блоков СР 8.1-СР 8.3 с соответствующих выходов блока ФТК 13 (фиг.2) поступают символы троичного кода (столбцы):  .

.

В момент поступления первого столбца на соответствующие входы блоков 10.1-10.3 с первого выхода блока БВС 9 (фиг.2) поступают синхроимпульсы, под воздействием которых символы троичного кода начинают заполнять разряды блоков 10.1-10.3. На каждом такте содержимое разрядов блоков 10.1-10.3 можно представить в виде матрицы (триады символов троичного кода). Работу блока БКО 10 в этом случае представим таблицей 1, в соответствующих столбцах которой будем записывать результаты каждого такта на выходе всех его блоков. На первом такте содержимое третьих разрядов регистров 10.1-10.3 будет замещено первым столбцом [100]T и содержимое регистров представится матрицей  . При этом на вторых выходах регистров 10.1-10.3 будут нули, которые поступят на соответствующие входы блока ИЛИ 10.13. На выходах блоков mod2 10.10-10.12 будет результат сложения по mod2 содержимого первых и третьих разрядов регистров 10.1-10.3 соответственно: 1⊕ 0=1, 0 ⊕ 0=0,

. При этом на вторых выходах регистров 10.1-10.3 будут нули, которые поступят на соответствующие входы блока ИЛИ 10.13. На выходах блоков mod2 10.10-10.12 будет результат сложения по mod2 содержимого первых и третьих разрядов регистров 10.1-10.3 соответственно: 1⊕ 0=1, 0 ⊕ 0=0,

0 ⊕ 0=0. Эти значения поступят на соответствующие входы блока И 10.15. Одновременно на выходах блоков НЕ 10.7-10.9 окажутся инвертированные значения результатов сложения по mod2 содержимого первых и третьих разрядов регистров 10.1-10.3 соответственно:  ,

,  ,

,  . Как видно из блок-схемы фиг.11, эти выходные значения блоков 10.1-10.3, mod2 10.10-10.12 и НЕ 10.7-10.9 будут определять результат выхода остальных блоков БКО 10 на каждом такте. На первом такте на выходе блока ИЛИ 10.13 будет нуль и с выхода блока НЕ 10.14 на первый вход блока И 10.20 поступит единица.

. Как видно из блок-схемы фиг.11, эти выходные значения блоков 10.1-10.3, mod2 10.10-10.12 и НЕ 10.7-10.9 будут определять результат выхода остальных блоков БКО 10 на каждом такте. На первом такте на выходе блока ИЛИ 10.13 будет нуль и с выхода блока НЕ 10.14 на первый вход блока И 10.20 поступит единица.

С выхода блока И 10.15 на вход блока БД 10.19 поступит нуль, и так как фронта нет, то с выхода блока БД 10.19 на второй вход блока И 10.20 поступит нуль (см.таблицу).

Одновременно на первый вход блока И 10.16 с выхода блока mod2 10.11 поступит единица, на второй его вход с выхода блока mod2 10.12 поступит нуль, следовательно, с его выхода на управляющий вход ключа 10.4 поступит нуль, ключ будет закрыт и содержимое второго разряда регистра 10.1 останется неизменным. На первый вход блока И 10.17 с выхода блока mod2 10.10 поступит единица, на второй его вход с выхода блока mod2 10.12 поступит нуль, следовательно, с его выхода на управляющий вход ключа 10.5 поступит нуль, ключ будет закрыт и содержимое второго разряда регистра 10.2 останется неизменным. На первый вход блока И 10.18 с выхода блока mod2 10.10 поступит нуль, на второй его вход с выхода блока mod2 10.11 поступит нуль, следовательно, с его выхода на управляющий вход ключа 10.4 поступит нуль, ключ будет закрыт и содержимое второго разряда регистра 10.3 также не изменится. С выхода блока И 10.20 на третий вход блока ИЛИ 10.21 поступит нуль. Так как предполагается безошибочный прием, то на первый и второй входы блока ИЛИ 10.21 также на этом такте поступят нули, следовательно, сброса устройства в исходное состояние не будет и далее начнется следующий (второй) такт работы блока БКО 10. Результат работы первого такта представлен в таблице 1 в третьем столбце.

На втором такте содержимое третьих разрядов вытесняется следующим столбцом из последовательности символов троичного кода во вторые разряды. На третьем такте все разряды блоков 10.1-10.3 заполнены принятыми символами троичного кода. На четвертом, пятом и последующих тактах элементы столбцов с четвертых выходов блоков 10.1 и 10.3 будут поступать на соответствующие входы блока ПТД 12 (фиг.2). Результаты второго, …, седьмого тактов записаны в соответствующих столбцах таблицы 1.

Анализ таблицы 1 показывает, что при безошибочном приеме операция коррекции содержимого вторых разрядов одного из блоков СР 10.1-10.3 осуществляется только тогда, когда первый и третий символы троичного кода (столбцы матриц) различны. Так как в данном случае второй столбец безошибочен, то его элементы не изменятся. Во всех остальных случаях происходит только сдвиг содержимого регистров.

Пусть в принятом фрагменте последовательности символов троичного кода первый из них ошибочен, при этом с выхода блока БКД 11 (фиг.2) на второй вход блока ИЛИ 10.23 импульс сброса не поступит, но при этом блок БВС 9 не выработает первый синхроимпульс, значит, в этом блоке счетчик СЧ 9.19 не доберет одного синхроимпульса до заданного числа и на его выходе будет нуль, запрещая сброс устройства в исходное состояние. Блок БКО 10 начнет работу со второго такта, но при этом блок БВС 9 не выдаст три последних синхроимпульса, чтобы вывести три последних символа троичного кода из блоков 10.1-10.3. Сообщение не будет принято полностью. Тогда в конце работы блока ОВ 9.23 блока БВС 9 (фиг.2) с выхода блока БД 9.36 выйдет короткий импульс, который сбросит устройство в исходное состояние. Работа блока БКО 10 в этом случае представится таблицей 2:

Как видно из таблицы 2, если первый символ троичного кода последовательности содержит однократную (обнаруживаемую) ошибку, то блок БВС 9 всегда будет сбрасывать устройство в исходное состояние, так как правильного приема не будет.

Аналогично блок БКО 10 работает, если стерт последний символ троичного кода последовательности.

Учитывая, что блок БКД 11 (фиг.2) контролирует длительность стираний и осуществляет сброс устройства в исходное состояние, если стерто более одного символа троичного кода с обнаруженной ошибкой, то можно сказать, что блок БКО 10 будет корректировать обнаруженные ошибки, которые распределены в последовательности символов троичного кода через одну (так называемой лесенкой), причем первый и последний символы в триаде должны быть безошибочны.

Пусть передается следующий фрагмент двоичной последовательности: 1101100… Рассмотрим работу блока БКО 10 при распределении ошибок «лесенкой», то есть в принимаемом фрагменте последовательности символов троичного кода стертые символы представлены нулевыми столбцами:

.

.

В таблице 3 показана работа блока БКО 10 для этого случая. Первый такт ничем не отличается от первого такта при безошибочном приеме, описанном выше, а на втором такте в матрице, представляющей содержимое разрядов регистров 10.1-10.3, два крайних столбца будут нулевыми. При этом на выходе блоков mod2 10.10-10.12 будут нули, на выходе блоков НЕ 10.7-10.9 будут единицы, значит, на выходе блока ИЛИ 10.13 будет единица, на выходе блока НЕ 10.14 - нуль, на выходе блока И 10.15 будет единица. Так как на предыдущем такте значение на выходе блока И 10.15 было нулевым, то на этом такте на входе блока БД 10.19 появился фронт импульса, следовательно, с его выхода на второй вход блока И 10.20 поступит короткий импульс. Одновременно на второй вход блока И 10.20 с выхода блока НЕ 10.14 поступит нуль, значит, сброс устройства в исходное состояние на этом такте будет блокирован. В этот же момент с входов блоков mod2 10.10-10.12 на соответствующие входы блоков И 10.16-10.18 поступят нули, значит, с их выходов на управляющие входы ключей 10.4-10.6 поступят нули, значит, эти ключи останутся закрытыми и содержимое вторых разрядов регистров СР 10.1-10.3 не изменится.

Следующий синхроимпульс сдвинет содержимое регистров 10.1-10.3 на один такт. На третьем такте нулевой столбец заполнит вторые разряды регистров 10.1-10.3, а два крайних столбца будут безошибочными. При этом на выходе блоков mod2 10.10-10.12 будут соответственно значения 1, 0, 1, на выходе блоков НЕ 10.7-10.9 - инверсии этих значений соответственно 0, 1, 0. На первый вход блока И 10.20 с выхода блока НЕ 10.14 поступит единица, на выходе блока И 10.15 будет нуль. Значит, с выхода блока БД 10.19 на второй вход блока И 10.20 поступит нуль, запрещая сброс устройства в исходное состояние. Одновременно на первый вход блока И 10.16 и второй вход блока И 10.18 с выхода блока mod2 10.11 поступит нуль, значит, ключи 10.4 и 10.6 будут заперты. На оба входа блока И 10.17 с выходов блоков mod2 10.10 и 10.12 поступят единицы, значит ключ 10.5 будет открыт и результат логического сравнения первого и третьего разрядов регистра 10.2, а именно  заменит содержимое второго разряда этого регистра, то есть ошибка будет исправлена. Аналогично БКО 10 работает и далее. То есть при расположении ошибок «лесенкой» блок БКО 10 исправляет стертый символ троичного кода только тогда, когда он находится во вторых разрядах блоков 10.1-10.3. При этом необходимо, чтобы первый и третий символы троичного кода (столбцы) в триаде были различными. Если первый и третий символы троичного кода безошибочны, но одинаковы, а второй символ ошибочен (средний столбец матрицы нулевой), то блок БКО 10 формирует короткий импульс сброса устройства в исходное состояние (столбец 9 таблицы 3).

заменит содержимое второго разряда этого регистра, то есть ошибка будет исправлена. Аналогично БКО 10 работает и далее. То есть при расположении ошибок «лесенкой» блок БКО 10 исправляет стертый символ троичного кода только тогда, когда он находится во вторых разрядах блоков 10.1-10.3. При этом необходимо, чтобы первый и третий символы троичного кода (столбцы) в триаде были различными. Если первый и третий символы троичного кода безошибочны, но одинаковы, а второй символ ошибочен (средний столбец матрицы нулевой), то блок БКО 10 формирует короткий импульс сброса устройства в исходное состояние (столбец 9 таблицы 3).

Варианты реализации блоков 10.1-10.3 представлены в [Микросхемы и их применение. Вып.1070. М.: Радио и связь, 1980, стр.135-136, рис.4.35 (а)] или в [Шило В.Л. Популярные цифровые микросхемы. Справочник.. М.: Радио и связь, 1987 стр.108, рис.1.76].

При согласованных полосах спектров сигналов и полосы канала передачи на выходе блока ДМ 7 (фиг.2) сигналы, несущие информацию, перекрываются во времени. Блок ФТК 8 (фиг.2) осуществляет формирование символов троичного кода, не перекрывающихся во времени. Этот блок выполнен в виде дифференциального усилителя с тремя входами и тремя выходами, выходные сигналы которых определяются разностью напряжений на двух его входах таким образом, что выход с максимальным напряжением остается открытым, а остальные два выхода запираются отрицательным потенциалом [Павлов В.Н., Ногин В.Н. Схемотехника аналоговых электронных устройств, М.: Горячая линия - Телеком, стр.107, рис.6.8]. Введение третьего входа и третьего выхода не изменяет функционирование такого устройства, так как сигналы с выхода демодулятора ДМ 7 появляются последовательно во времени, что и определяет разность напряжений на двух входах блока ФТК 8. Временные диаграммы работы блока ФТК 8, приведенные на фиг.12, дополнительно поясняют работу этого блока. Здесь а), б) и в) - элементы символов троичного кода (элементы столбцов), поступающие с выходов ДМ 7, 13 на соответствующие входы ФТК 8; а'), б') и в') - элементы символов троичного кода на выходах блока ФТК 8.

Блок ПТД 12 является широко используемым триггером, выполненным на логике ИЛИ-НЕ [Г.И.Пухальский, Т.Я.Новосельцева. Проектирование дискретных устройств на интегральных микросхемах. М.: Радио и связь, 1990, стр.66-68, рис.2.36]. С соответствующих выходов блока БКО 10 на два информационных входа блока ПТД 12 подаются первый и третий элементы символов троичного кода (столбцов), а с прямого выхода блока ПТД 12 на вход данных блока ППр 13 поступает восстановленная двоичная последовательность. При этом инверсный выход блока ПТД 12 не используется.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2344544C2 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2348102C2 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РОЛЕВОЙ ФУНКЦИИ УЧАСТНИКА ТВОРЧЕСКОГО КОЛЛЕКТИВА | 2013 |

|

RU2541431C1 |

| Декодер балансного кода | 1990 |

|

SU1795556A1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| СИСТЕМА РАДИОСВЯЗИ СО СВЕРХШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 2014 |

|

RU2580070C2 |

| Устройство для преобразования двоичной последовательности в балансный троичный код | 1991 |

|

SU1807561A1 |

| Преобразователь последовательного кода в параллельный | 1989 |

|

SU1795557A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1115063A1 |

Изобретение относится к устройствам передачи данных и может найти применение в телекоммуникационных системах, системах радиосвязи, радионавигации и управления. Достигаемый технический результат - увеличение пропускной способности и помехоустойчивости линии связи. Устройство содержит блок передачи данных, состоящий из преобразователя параллельного кода в последовательный, преобразователя двоичного кода в код с тремя состояниями, модулятора, передатчика данных и генератора тактовых импульсов и блок приема данных, состоящий из приемника данных, демодулятора, формирователя троичного кода, блока выделения синхросигнала, блока коррекции ошибок, блока контроля длительности стираний, преобразователя троичного кода в двоичный и преобразователя последовательного кода в параллельный. 12 ил., 3 табл.

Устройство для передачи цифровой информации, состоящее из соединенных линией связи блока передачи данных (БПРД) и блока приема данных (БПРМ), при этом БПРД содержит преобразователь параллельного кода в последовательный (ППс), вход синхронизации которого соединен с выходом генератора тактовых импульсов (ГТИ), БПРМ содержит последовательно соединенные блок выделения синхросигнала (БВС) и преобразователь последовательного кода в параллельный (ППр), отличающееся тем, что введены: в БПРД - последовательно соединенные преобразователь двоичного кода в код с тремя состояниями (ПДТ), модулятор и передатчик данных (ПРД), выход которого является выходом БПРД, вход и вход синхронизации ПДТ подсоединены соответственно к выходу ППс и к выходу ГТИ, N входов ППс являются входами БПРД; в БПРМ - последовательно соединенные приемник данных (ПРМ) и демодулятор, выходы которого соединены с соответствующими входами формирователя троичного кода (ФТК), выходы которого соединены с соответствующими входами БВС, блока коррекции ошибок (БКО) и блока контроля длительности стираний (БКД), при этом первый и второй выходы БКО соединены соответственно с первым и вторым входами преобразователя троичного кода в двоичный (ПТД), выход которого соединен со вторым входом ППр, N выходов которого являются выходами БПРД, причем выход БКД соединен с пятым входом БКО, третий выход которого соединен с четвертым входом БВС, первый выход которого соединен с первым входом ППр и четвертым входом БКО, шестой вход которого подсоединен ко второму выходу БВС.

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2003 |

|

RU2242789C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Способ получения двойного суперфосфата | 1981 |

|

SU1104125A1 |

| Способ фазового анализа волокнистых материалов | 1987 |

|

SU1492248A1 |

Авторы

Даты

2009-05-20—Публикация

2007-12-17—Подача