Изобретение относится к вычислитель- ной технике и может быть использовано для построения шифраторов кода нормализации в малых и высокопроизводительных цифровых вычислительных машинах.

Цель изобретения - сокращение аппаратных затрат (количества требуемых логических элементов и, следовательно, базовых ячеек (БМК) при сохранении быстродействия шифратора.

Поставленная цель достигается тем, что шифратор, содержащий первый и второй дешифраторы границы нулей, блок шифрации прямого кода, первый, второй и третий элементы И, причем выход третьего элемента И является первым выходом шифратора, вход блокировки которого соединен с входом

блокировки блока шифрации прямого кода, группа выходов которого является группой выходов шифратора, соответствующие старшие и младшие информационные входы которого являются информационными входами соответственно первого и второго дешифраторов границы нулей, группа выходов первого дешифратора границы нулей соединена с группой информационных входов блока шифрации прямого кода, первый и второй входы третьего элемента И соединены с прямыми выходами соответственно первого и второго элементов И, входы первого и второго элементов И соединены соот- ветственно со старшими и младшими информационными входами шифратора, первый информационный вход блока шиф00

о

гл

Ј

рации прямого кода соединен с инверсным выходом первого элемента И и с входом блокировки первого дешифратора границы нулей, дополнительно содержит четвертый элемент И, причем соответствующие выхо- ды первого и второго дешифраторов границы нулей соединены с соответствующими входами четвертого элемента И, выход которого соединен с вторым информационным входом блока шифрации прямого кода, вто- рая группа информационных входов которого соединены с первыми выходами второго дешифратора границы нулей, вход блокировки которого «Единен с прямым выходом первого элемента И.,

Заявляемый шифратор содержит признаки (четвертый элемент И со связями), которые отсутствуют во всех известных аналогах и благодаря которым обеспечивается достижение положительного эффекта - со- кращение аппаратных затрат, т.е. количества 4-х и 2-х входовых элементов И-НЕ и И с 14 до 13 при сохранении быстродействия (4 Т)..::

Так как заявляемое техническое реше- ние содержит признаки, отсутствующие во всех аналогах и обеспечивающие достижение положительного эффекта, то оно соответствует критерию существенные отличия.-,....-. .-.

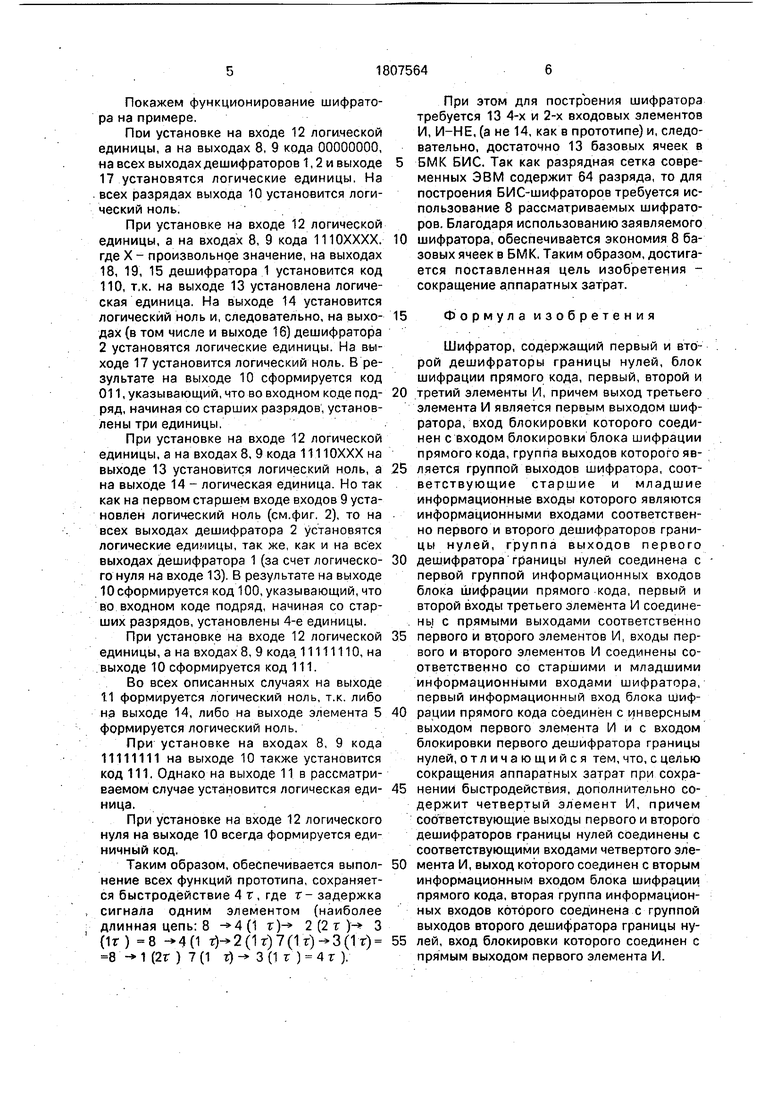

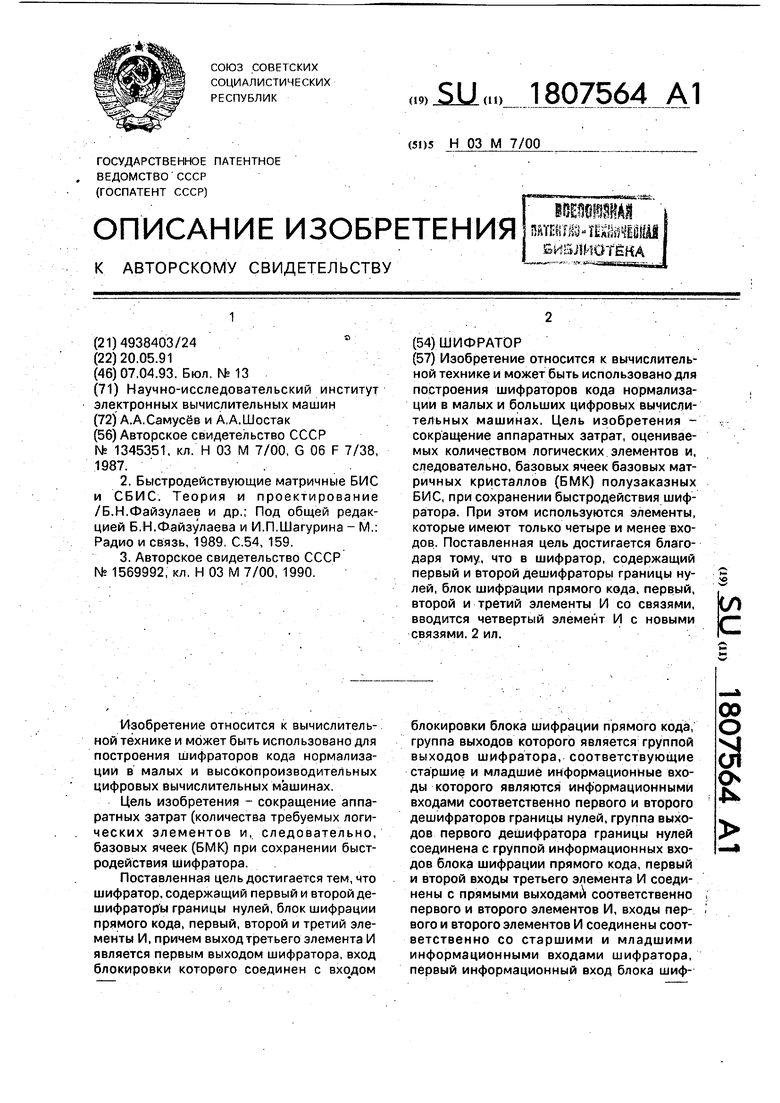

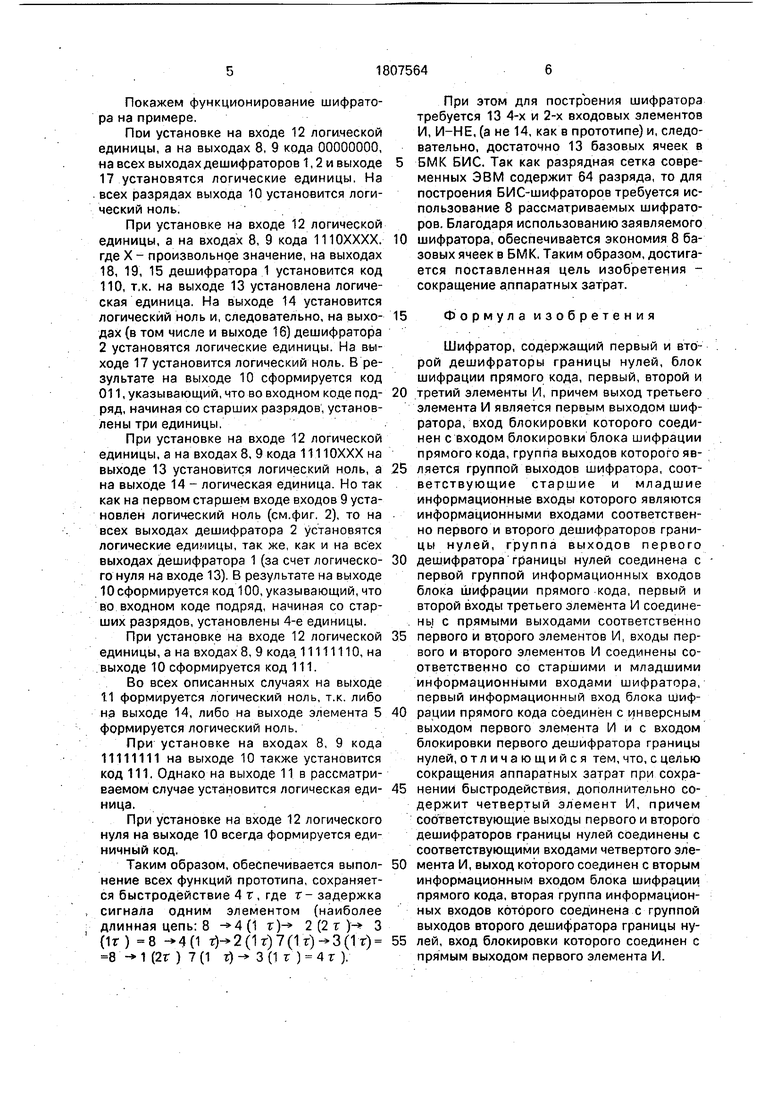

На фиг. 1 изображена структурная схема шифратора; на фиг. 2 - функциональная схема дешифратора границы нулей. .

Шифратор содержит следующие элементы:. .. .-

1, 2 - первый и второй дешифраторы границы нулей; 3 - блок шифрации прямого кода; 4, 5, 6 - первый, второй и третий элементы И; 7 - четвертый эле.мент И; 8, 9 - старшие и младшие информационные вхо- ды шифратора, входы, соответственно первого и второго элементов И: 10 - второй выход шифратора, выходы блока 3; 11 - первый выход шифратора, выход элемента 6;. 12 - вход блокировки шифратора и блока 3; 13-инверсный выход элемента И, вход блокировки дешифратора. 1, второй информационный вход блока 3; 14 - прямой выход элемента 4, первый вход элемента 6, вход блокировки дешифратора 2. 15, 16 - вторые выходы дешифраторов 1,2, входы элемента 7, 17 - выход элемента 7, третий информационный вход блока 3; 18, 19 - первые выходы дешифратора 1, первые информационные входы блока 3; 20, 21 - элементы И-НЕ в блоке 3; 22 - элементы И-НЕ в дешифраторе 1 (2) на фиг. 2.

Дешифраторы 1,2 имеют то же назначение, что и аналогичные дешифраторы в прототипе, и отличаются от последних тем, что

имеют три входа и три выхода вместо четырех входов и выходов. Это достигается путем выделения из дешифраторов границы нулей первого 4 и второго 5 элементов И. сохранив их связи, а освободившийся вход элементов И 22 дешифратора соединен с входом блокировки 13 (14) дешифратора 1 (2). По указанной причине авторы рассматривают элементы 4, 5 и связь 13 как элементы и- связь, содержащиеся в прототипе. Выделение элементов 4, 5 необходимо в связи с изменением принципа шифрации прямого кода под действием сигналов с выходов дешифратора 2.

Логика функционирования дешифраторов 1, 2 ясна из функциональной схемы на фиг. 2, Номер выхода дешифратиора 1 (2) (при отсчете слева направо, начиная с единицы) равен количеству рядом расположенных входов старших разрядов (при отсчете слева напрааво) дешифратора 1(2), на которых установлены логические единицы.Если логические единицы установлены на всех входах 8, то на выходе 13 элемента 4 устанавливается логический ноль, который через вход блокировки дешифратора 1 устанавливает (удерживает) логические единицы на выходах 15, .18, 19. При этом на выходе 14 элемента 4 устанавливается логическая единица, которая разблокировывает выходы дешифратора 2, Если же на входах 8 не все логические единицы, то на выходе 14 устанавливается логический ноль, который через вход блокировки дешифратора 2 устанавливает логические единицы на выходах дешифратора 2, которые не Мешают шифрации сигналов с выходов дешифратора 1 блоком 3, т.к. сигнал с выхода 15 свободно проходит через элемент 7 на вход 17. Аналогично, когда на выходе 13 устанавливается логический ноль, который шифруется блоком 13 логической единицей в старшем разряде выхода 10 (через элемент 21), на выходах дешифратора 1 через вход блокировки 13 устанавливаются логические единицы, которые не мешают шифрации сигналов с выходов дешифратора 2 блоком 3, т.к. сигнал с выхода 16 свободно проходит через элемент 7 на вход 17. При этом шиф- рация сигналов с выходов дешифраторов 2 и 1 осуществляется блоком 3 единообразно. В прототипе шифрация сигналов с выходов дешифратора 2 осуществлялась блоком 3 через шифрацию инверсного кода, для чего требовался блок шифрации инверсного кода, требующий для своего построения два элемента И-НЕ. В заявляемом шифраторе все те же функции, что и в прототипе, достигаются благодаря использованию одного элемента И 7.

Покажем функционирование шифратора на примере.

Пои установке на входе 12 логической единицы, а на выходах 8, 9 кода 00000000, на всех выходах дешифраторов 1,2 и выходе 5 17 установятся логические единицы. На . всех разрядах выхода 10 установится логический ноль.

При установке на входе 12 логической единицы, а на входах 8, 9 кода 1110ХХХХ. 10 где X - произвольное значение, на выходах 18, 19, 15 дешифратора 1 установится код 110, т.к. на выходе 13 установлена логическая единица. На выходе 14 установится логический ноль и, следовательно, на выхо- 15 дах (в том числе и выходе 16) дешифратора 2 установятся логические единицы. На выходе 17 установится логический ноль. В результате на выходе 10 сформируется код 011, указывающий, что во входном коде под- 20 ряд, начиная со старших разрядов, установлены три единицы.

При установке на входе 12 логической единицы, а на входах 8, 9 кода 1111ОХХХ на выходе 13 установится логический ноль, а 25 на выходе 14 - логическая единица. Но так как на первом старшем входе входов 9 установлен логический ноль (см.фиг. 2), то на всех выходах дешифратора 2 установятся логические единицы, так же, как и на всех выходах дешифратора 1 (за счет логическо- 30 го нуля на входе 13). В результате на выходе

10 сформируется код 100, указывающий, что во входном коде подряд, начиная со старших разрядов, установлены 4-е единицы.

При установке на входе 12 логической 3.5 единицы, а на входах 8, 9 кода. 11111110, на .выходе 10 сформируется код 111.

Во всех описанных случаях на выходе

11 формируется логический ноль, т.к. либо на выходе 14, либо на выходе элемента 5 40 формируется логический ноль.

При установке на входах 8, 9 кода 11111111 на выходе 10 также установится код 111. Однако на выходе 11 в рассматриваемом случае установится логическая еди- 45 ница.

При установке на входе 12 логического нуля на выходе 10 всегда формируется единичный код.

Таким образом, обеспечивается выпол- 50 нение всех функций прототипа, сохраняется быстродействие 4 т , где т- задержка сигнала одним элементом (наиболее длинная цепь: 8 (1 т)- 2 (2 т ) 3 (1г) 8 (1 т)(1г)7(1т)(1т) 55 8 (2-е ) 7(1 г)- 3(1 г ) 4г ).

При этом для построения шифратора требуется 13 4-х и 2-х входовых элементов И, И-НЕ, (а не 14, как в прототипе) и, следовательно, достаточно 13 базовых ячеек в БМК БИС. Так как разрядная сетка современных ЭВМ содержит 64 разряда, то для построения БИС-шифраторов требуется использование 8 рассматриваемых шифраторов. Благодаря использованию заявляемого шифратора, обеспечивается экономия 8 базовых ячеек в БМК. Таким образом, достигается поставленная цель изобретения - сокращение аппаратных затрат.

Формула изобретения

Шифратор, содержащий первый и второй дешифраторы границы нулей, блок шифрации прямого кода, первый, второй и третий элементы И, причем выход третьего элемента И является первым выходом шифратора, вход блокировки которого соединен с входом блокировки блока шифрации прямого кода, группа выходов которого является группой выходов шифратора, соответствующие старшие и младшие информационные входы которого являются информационными входами соответственно первого и второго дешифраторов границы нулей, группа выходов первого дешифратора границы нулей соединена с первой группой информационных входов блока шифрации прямого кода, первый и второй входы третьего элемента И соединены с прямыми выходами соответственно первого и второго элементов I/I, входы первого и второго элементов И соединены соответственно со старшими и младшими информационными входами шифратора, первый информационный вход блока шифрации прямого кода соединён с инверсным выходом первого элемента И и с входом блокировки первого дешифратора границы нулей, отличающийся тем, что, с целью сокращения аппаратных затрат при сохранении быстродействия, дополнительно содержит четвертый элемент И, причем соответствующие выходы первого и второго дешифраторов границы нулей соединены с соответствующими входами четвертого элемента И, выход которого соединен с вторым информационным входом блока шифрации прямого кода, вторая группа информационных входов которого соединена с группой выходов второго дешифратора границы нулей, вход блокировки которого соединен с прямым выходом первого элемента И.

w./

| название | год | авторы | номер документа |

|---|---|---|---|

| ШИФРАТОР | 1991 |

|

RU2023345C1 |

| Шифратор | 1988 |

|

SU1569992A1 |

| Шифратор кода нормализации | 1985 |

|

SU1345351A1 |

| Модуль для формирования признака переполнения и кода нормализации | 1988 |

|

SU1501041A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| Устройство для шифрации крайней единицы | 1984 |

|

SU1272334A1 |

| Шифратор приоритета | 1990 |

|

SU1737448A1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения шифраторов кода нормализации в малых и больших цифровых вычислительных машинах. Цель изобретения - сокращение аппаратных затрат, оцениваемых количеством логических элементов и, следовательно, базовых ячеек базовых матричных кристаллов (БМК) полузаказных БИС, при сохранении быстродействия шифратора. При этом используются элементы, которые имеют только четыре и менее входов. Поставленная цель достигается благодаря тому, что в шифратор, содержащий первый и второй дешифраторы границы нулей, блок шифрации прямого кода, первый, второй и третий элементы И со связями, вводится четвертый элемент И с новыми связями. 2 ил. ел С

И/з

Фиг. 2

| Шифратор кода нормализации | 1985 |

|

SU1345351A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Быстродействующие матричные БИС и СБИС | |||

| Теория и проектирование /Б.Н.Файзулаев и др.; Под общей редакцией Б.Н.Файзулаева и И.П.Шагурина - М.: Радио и связь, 1989 | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Шифратор | 1988 |

|

SU1569992A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-04-07—Публикация

1991-05-20—Подача