Изобретение относится к вычислительной техйике и может быть использовано в арифметических устройствах с плавающей запятой, в устройствах управления.

Известно многоканальное устройство для приоритетного кодирования запросов прерывания, содержащее узел приоритета, шифратор и элемент ИЛИ, а в каждом канале - узел приоритета группу элементов ИЛИ и шифратор, причем в каждом канале выход каждого элемента ИЛИ группы соединен с соответствующим входом узла приоритета, группа выходов которого соединена с группой входов шифратора.

Недостатком известного устройства являются большие аппаратурные затраты.

Наиболее близким к предлагаемому является устройство для шифрации крайней единицы в n-разрядном двоичном коде, содержащее первую группу узлов частичной шифрации, группа входов первой группы узлов частичной шифрации является группой входов устройства.

Недостатком прототипа является низ- С/) кая степень регулярности межсоединений, Г приводящая к большим аппаратурным за- тратам при реализации данного устройства методами микроэлектроники.

Цель изобретения - сокращение аппаратурных затрат.

Поставленная цель достигается тем, что 4s4 в устройство дляшифрациикрайней едини- СО цы в n-разрядном двоичном коде, содержащее группу узлов частичной шифрации, причем fv группа входов каждого узла частичной шифра- К ции является соответствующей группой вхо- лл дов шифратора, дополнительно введена; группа элементов И, группа блоков элементов И, (л - 1) групп элементов ИЛИ (где п - число узлов частичной шифрации), три группы элементов неравнозначности, причем сигнальные выходы первого и второго узлов частичной шифрации группы соединены соответственно с первым и вторым входами первого элемента И группы, сигнальный выход 1-го узла частичной шифрации группы (I 2,...,п) соединен с первым входом (I 1)-го элемента И группы, второй вход каждого элемента И группы начиная со второго соединен с выходом предыдущего элемента И группы, выход каждого элемента И группы соединен с первыми входами одноименных элементов неравнозначности первой группы, второй вход первого элемента неравнозначности первой группы соединен с сигнальным выходом первого узла частичной шифрации группы, второй вход первого элемента неравнозначности второй группы и вторые входы элементов неравнозначности третьей группы соединены с входом логического нуля шифратора, второй вход каждого элемента неравнозначности первой и второй групп начиная со второго соединены с выходом предыдущего элемента неравнозначности данной группы, выходы элементов неравнозначности всех групп и выходы элементов ИЛИ (п - 1)-й группы являются выходами шифратора, информационные выходы первого узла частичной шифрации группы соединены с первичными входами элементов ИЛИ первой группы, первые входы элементов ИЛИ каждой группы, начиная со второй соединены с выходами одноименных элементов ИЛИ предыдущей группы, вторые входы элементов ИЛИ каждой группы соединены с выходами одноименного блока элементов И группы, информационные входы первого блока элементов и группы соединены с информационными выходами второго узла частичной шифрации группы, управляющий вход первого блока элементов И группы соединен с сигнальным выходом первого узла частичной шифрации группы, информационные входы k-ro блока элементов И группы (к 1,...,п) соединены с информационными выходами (k + 1)-го узла частичной шифрации группы, управляющий вход 1-го блока элементов И группы соединен с выходом (I + 1)-го элемента И группы.

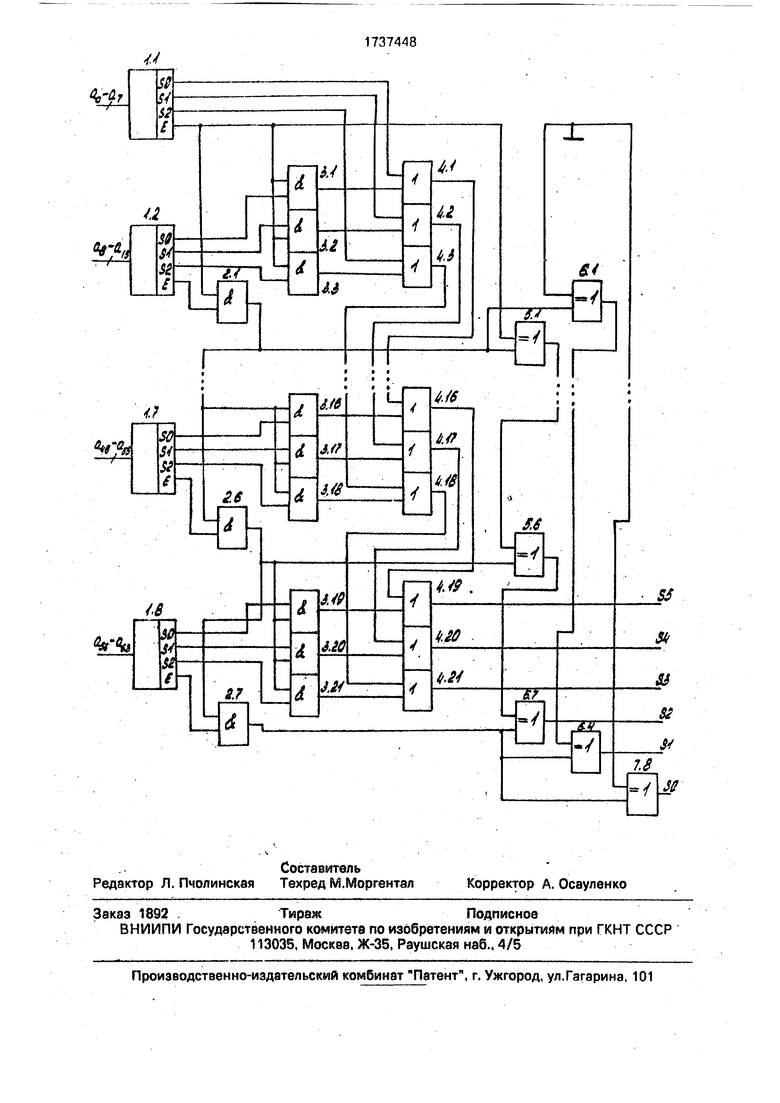

На чертеже показана схема шифратора приоритета для случая п 64 (разрядность входного кода).

Шифратор приоритета содержит 8 узлов 1.1-1.8 частичной шифрации 28 элементов 2 И 2.1-2.7 и 3.1-3.21,21 элемент 2 ИЛИ 4.1-4.21, 13 элементов 5.1-5.7. 6.1-6.4 и 7.1-7.2 неравнозначности.

Входы устройства соединены с входами узлов частичной шифрации. Выход Е узла 1.J частичной шифрации подключен к входу элемента 2 И 2.Q - 1), выходы SO-S2 узла 1.) частичной шифрации - к входам элементов 2 И 3.0 - 5)-3.(j -1).

Выход элемента 2 И 2.J соединен с входами элементов 2 И 3.(3j + 1)-3.(3j + 3} и

элементов 5J, 6 и 7 неравнозначности,

выход элемента 2 И 3.J - с входом элемента 2 ИЛИ 4.J. Выход элемента 4.J подключен к

выходу элемента 4.0 + 3), Выходы элементов 5.J-7.J связаны с входами элементов 5.Q + 1)-7.(j + 1), выходы элементов 4.19- 4.21, 5.7, 6.4 и 7.2 подключены к выходам устройства.

Устройства работает следующим образом (на примере 64-разрядного шифратора приоритета).

Входной код поступает на входы ао-аез узлов частичной шифрации. Каждый узел частичной шифрации выделяет в соответствующем 8-разрядном входном коде старшую единицу, вырабатывает двоичный код ее номера на выходах SO, S1 и S2 и при обнаружении старшей единицы вырабатывает

признак старшей единицы Е, равный О. Выход Е узла шифрации, имеющего наименьший номер среди всех узлов, во входном коде которых обнаружена старшая единица, устанавливает в О выход элемента 2.J. Выход

элемента 2.J, в свою очередь, устанавливает в О все элементы .(2 +1)-2.7, а следовательно и элементы 3.(3J + 1}-3.21. Таким образом, элементы 4.(3j + 1)-4.21 пропускают на выход сигналы с выходов предыдущих элементов 2 ИЛИ. Пусть старшая единица входного кода найдена (J + 1)-м узле 1 частичной шифрации. Тогда на выходе элементов 3.(3J - 2), 3.(3J -1), 3.3J устанавливается код старшей единицы 8-разрядного входного кода, поступающего на узел 1.Q + 1). Этот код проходит через элементы 4.(3| + 1)-4.21 на выходе S3-S5 без изменения. Сигналы S3-S5 образуют младшие разряды выходного кода устройства.

Элементы неравнозначности служат для образования старших разрядов выходного кода, т.е. двоичного кода количества 8-разрядных слов входного кода, стоящих перед старшей единицей. Выход SO является старшим, a S2 - младшим разрядом данного кода. Допустим, что старшая единица найдена в 8-разрядном слове, поступающем на узел 1 .j 0 4). Рассмотрим формирование выходного кода на выходах SO-S2. Выходной сигнал Е элемента 1Д равен 1. Пусть это будет значением младшего разряда выходного кода. Так как на входы as-ats также поступили только 0й то выходной сигнал элемента 2.1 равен Г. На входы элемента

5.1 поступают две 1, устанавливая на его выходе О. На вход элемента 6.1 поступает Г с элемента 2.1, устанавливая на его выходе 1я. Таким образом, после прохождения двух нулевых наборов получают код 010. После прохождения 3-го набора на

выходе элемента 5.2 появляется Г, т.е. код увеличивается на единицу - 01Г (старший разряд снимается с последнего элемента группы 6.k, т.е. с выхода элемента 6.1). После прохождения 4-й группы происходит обнуле- ние элементов 5.3 и 6.2 и установка в 1 элемента 7.1. Код становится равным 100, т.е. значения выходных сигналов элементов k.J, где к 5, изменяются на противоположные с увеличением на единицу, если выход- ные сигналы соответствующих элементов 2.I не равны О, т.е. старшая единица еще не найдена. Все элементы k.j, где к Ј5, которым соответствуют выходы элементов 2.I, равные нулю, пропускают сигнал с выходов эле- ментов k.(k - 1) на выходы устройства без изменения.

Аппаратурные затраты в предлагаемом 64-разрядном шифраторе приоритета составляют 348 входов. Таким образом, пред- латаемый 64-разрядный шифратор приоритета обеспечивает сокращение аппаратурных затрат и приблизительно в три раза.

Формула изобретения Шифратор приоритета, содержащий группу узлов частичной шифрации, причем группа входов каждого узла частичной шифрации является соответствующей группой входов иифратора, отличающийся тем, что, с целью сокращения объема оборудования, шифратор содержит группу элементов И, группу блоков элементов И. (п -1} групп элементов ИЛИ (где п - число узлов частич- ной шифрации), три группы элементов неравнозначности, причем сигнальные выходы первого и второго узлов частичной шифрации группы соединены соответственно с первым и вторым входами первого эле- мента И группы, сигнальный выход 1-го узла частичной шифрации группы (I « 2,...,п) соединен с первым входом (I - 1)-го элемента И группы, второй вход каждого элемента И группы начиная с второго соединен с выходом предыдущего элемента И группы, выход каждого элемента И группы соединен с первыми входами одноименных элементов неравнозначности, второй вход первого элемента неравнозначности первой группы - с сигнальным выходом первого узла частичной шифрации группы, второй вход первого элемента неравнозначности второй группы и вторые входы элементов неравнозначности третьей группы - с входом логического нуля шифратора, второй вход каждого элемента неравнозначности первой и второй групп начиная с второго соединены с выходом предыдущего элемента неоавнозначности данной группы, выходы элементов неравнозначности всех групп и выходы элементов ИЛИ (п - 1)-й группы являются выходами шифратора, информационные выходы первого узла частичной шифрации группы соединены с первичным входами элементов ИЛИ первой группы, первые входы элементов ИЛИ каждой группы, начиная с второй, - с выходами одноименных Элементов ИЛИ предыдущей группы, вторые входы элементов ИЛИ каждой группы - с выходами одноименного блока элементов И группы, информационные входы первого блока элементов И группы - с информационными выходами второго узла частичной шифрации группы, управляющий вход первого блока элементов И группы - с сигнальным выходом первого узла частичной шифрации группы, информационные входы k-ro блока элементов И группы (k 1,...,п) соединены с информационными выходами (k + 1)-го узла частичной шифрации группы, управляющий вход j-ro блока элементов И группы соединен с выходами (I - 1)-го элемента И группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Приоритетный шифратор | 1990 |

|

SU1751758A1 |

| Устройство для сравнения чисел | 1985 |

|

SU1325459A1 |

| Устройство для определения старшего значащего разряда | 1983 |

|

SU1164707A1 |

| Устройство для поиска информации | 1989 |

|

SU1686464A1 |

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1999 |

|

RU2152072C1 |

| Устройство для выделения экстремального числа | 1985 |

|

SU1553971A1 |

| ШИФРАТОР | 1991 |

|

RU2023345C1 |

| Устройство для сравнения чисел | 1987 |

|

SU1474637A2 |

| Устройство для обмена информацией | 1980 |

|

SU955014A1 |

| Устройство для сравнения кодов | 1979 |

|

SU849203A1 |

Изобретение относится к вычислительной технике. Цель изобретения - сокращение оборудования за счет использования групп последовательно соединенных элементов И и ИЛИ для передачи младших раз- рядов выходного кода и группы последовательно соединенных элементов НЕРАВНОЗНАЧНОСТЬ для формирования старших разрядов выходного кода. В устройстве повышается степень регулярности межсоединений. 1 ил.

| Устройство для приоритетного кодирования запросов прерывания | 1983 |

|

SU1160411A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для шифрации крайней единицы в -разрядном двоичном коде | 1979 |

|

SU864289A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-05-30—Публикация

1990-06-11—Подача