1501

Изобретение относится к области вычислительной техники и может быть использовано для построения устройств формирования кода нормализации и при- знака переполнения при арифметических сдвигах влево в цифровых вычислительных машинах и системах,

Целью изобретения является сокращение аппаратурных затрат.

На чертеже представлена схема модуля для формирования признака переполнения и кода нормализации.

Модуль содержит первый и второй узлы 1 и 2 шифрации соответственно, группу элементов ИЗ, элемент И-НЕ 4, узел 5 коммутации, содержащий элемент И 6, элемент НЕ 7, с первого по шестой элементы И-НЕ 8-13 соответственно, знаковый вход 14 модуля, ин- формационный вход 15 модуля, первые входы 16 и 17 соответственно узлов 1 и 2 шифрации, вход 18 задания величины сдвига модуля, вход 19 задания режима модуля, прямые выходы 20 эле- ментов И 3 группы, первый управляющий вход 21 узла 5 коммутации, вход 22 блокировки модуля, первую группу информационных входов 23-25 узла 5 коммутации, вторую группу информацион- ных входов 26-28 узла 5.коммутации, выход 29 признака нуля модуля, выход 30 признака переполнения модуля, выход 31 кода нормализации модуля.

Цифры около линий разрядов на чер- теже обозначают количество или, номера разрядов.

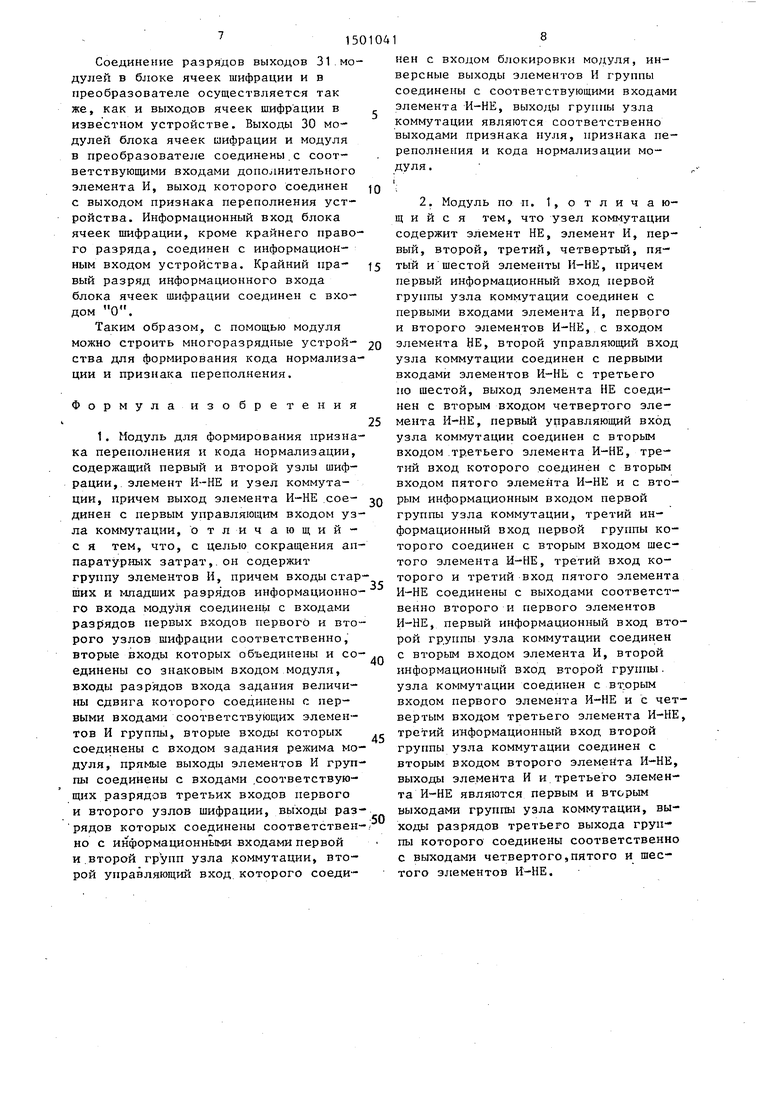

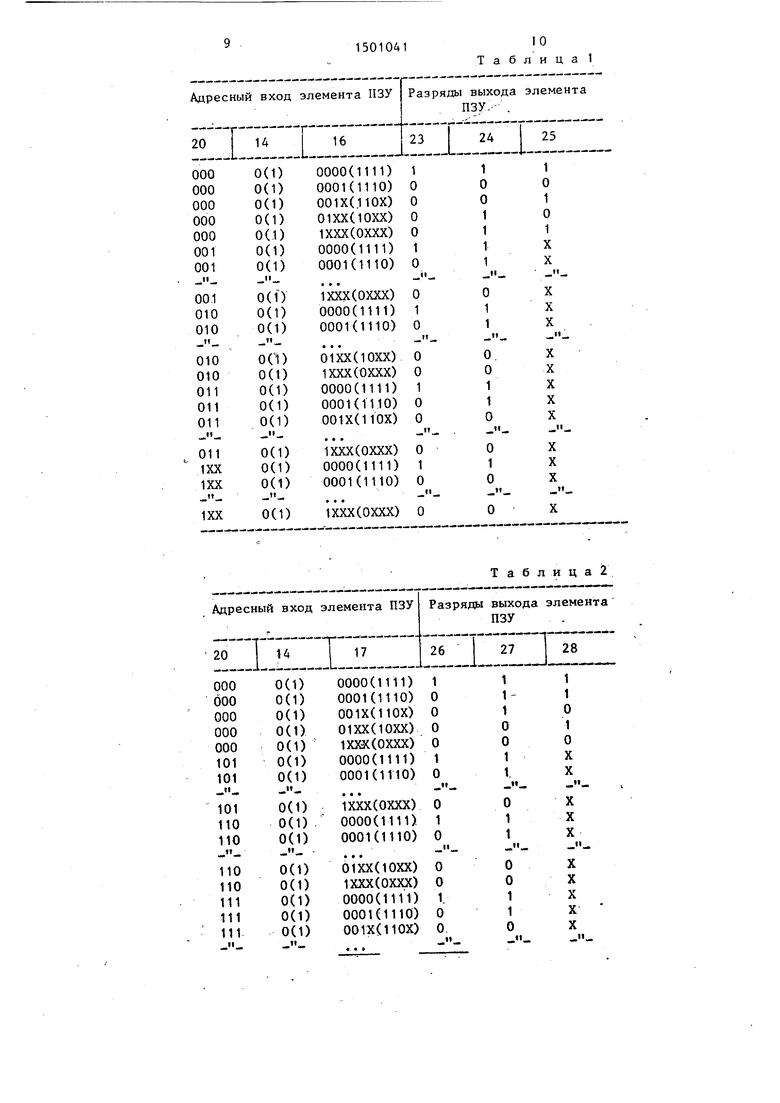

Узлы 1 и 2 предназначены для анализа значений кода на входах соответственно 16,17 с учетом значений кодов на входе 14 и выходе 20, могут быть построены на элементах постоянных запоминающих устройств (ПЗУ). Каждый узел 1 или 2 содержит один элемент ПЗУ, разряды адресного входа которо- го соединены с входами разрядов входов 16 или 17, 14 и выхода 20. Соответствующие разряды выхода элемента ПЗУ в узле 1 или 2 соединены с входами 23 - 25 или 26 - 28.

Элементы ПЗУ в узле 1 и 2 кодируются в соответствии с табл, 1 и 2. Вместо элементов ПЗУ могут быть использованы программируемые логические матрицы.

Модуль функционирует следующим образом.

В исходном состоянии на входе 15 устанавливается анализируемый информационный двоичный код. На входе 14 устанавливается код знака. На входе 18 устанавливается код величины сдвига. На входе 19 устанавливается код признака, например арифметического сдвига влево, или код признака нулевого сдвига, равные соответственно 1 и О. На входе 22 устанавливается сигнал блокировки, равный О, при котором модуль блокируется, т.е. на выходах 30, 31 устанавливаются единичные коды. При этом на выходе 29 формируется код признака О, равный 1, если значения всех бит входа 15 равны значению знака на входе 14, или О в противном случае.

Код признака нуля на выходе 29 формируется независимо от значения управляющих кодов на входах 18,19,22. Код признака нуля независимо формируется для групп бит на входах 16 и 17 в узлах соответственно 1 и 2, на входах соответственно 23 и 26 (см. табл. 1 и 2). С помощью элемента И 6 в узле 5 сигналы с входов 23,26 объединяются. Т.е. если коды на входах 16 и 17 равны нулю, то на выходе 29 появляется логический сигнал, равный 1. При 1 на входе 22 модуль функционирует и по выходам 30, 31.

При установке на входе 19 код с входа 18 передается на выход 20 и модуль функционирует в режиме формирования признака переполнения, код которого форгдаруется на выходе 30. Если значение кода на выходе 20 меньше или равно к, где к - количество разрядов входа 16, то сигнал признака переполнения формируется только на входе 24 с учетам результата анализа только кода на входе 16. При этом на входе 27 устанавливается 1, независимо от значения кода на входе 17. Если же код на выходе 20 больше к, то код признака переполнения формируется и на входе 27 с учетом знгмений кода на входе 17 и значения кода на выходе 20, равного (М-к), где М - код на выходе 20.

Сигналы с входов 24,27 объединяются элементом И-НЕ 10, если код ве- личины сдвига не равен нулевому и на входе 21 сформирована 1. Т.е. при отсутствии переполнения на входах 24, 27 формируются 1 (см. табл. 1 и 2), благодаря чему (так как на всех входах элемента И-НЕ 10 сформированы 1) на выходе 30 установится О.

Если имеет место переполнение (т.е. количество бит слева на входе 15, равных коду знака на входе 14, меньше значения величины сдвига, заданной кодом па входе 18), то хотя бы на одном входе 24 или 27 установится О, благодаря которому на выходе 30 устанавливается 1.

При нулевом коде величины сдвига на входе 18 на входе 21 устанавливается О, благодаря которому на выходе 30 устанавливается 1, означающая, что переполнение отсутствует, так как оно невозможно.

При этом модуль переходит в режим формирования кода нормализации. Для задания режима формирования кода нормализации используется также вход 19, на котором для этого устанавливается О, что эквивалентно установке на входе 18 нулевого кода.

При этом на входах 24,25 при ненулевом коде на входе 16 формируется код нормализации с инверсными значениями бит для кода на входе 16 (см. табл.1). Благодаря нулевому коду на входе 23 блокируются элементы НЕ 7, И-НЕ 8,9, на выходах которых устанавливается 1. На выходе элемента 11 устанавливается О.

В результате на выходах элементов И-НЕ 11 - 13 и, следовательно, на выходе 31 формируется прямой код нормализации. При нулевом коде на .входе 16 на входах 23 - 25 устанавливается единичный код. Параллельно формируемый код нормализации на входах 27,28 (см. табл.2) для групгш разрядов кода на входе 17 транзитом передается на выходы элементов И-НЕ 12, 13. На выходе элемента И-НЕ 11 устанавливается единичный .код, так как на входе 23 устанавливается 1, которая транзитом передается на выход элемента И-НЕ 11. В результате на выходе 31 формируется прямой код нормализации.

Если на входе 17 установлен нулевой код, то на входах 27,28 формируется единичный код, который транзитом передается на выходы элементов И-НЕ 12,13. Параллельно на выходе 29 формируется единичный код.

Модуль может быть использован в качестве ячейки шифрации в устройстве для формирования кода нормализации и признака переполнения. При этом не требуется блок дешифраторов, так как

5

0

5

L - ков качестве выходов jiemu l pnторов oж- но использовать выходы 29 модуля.

Устройство строится с иомо1.цТ)Ю модуля .следующим образом.

Строится блок ячеек шнфрации, в котором вместо ячеек шифрации используется модуль. Т.е. блок ячеек шифраLНИИ содержит - модулей, где

I

личество разрядов информационного

входа устройства. Выходы модулей соединены с соответствующими выходами блока, а информационные входы модулей соединены с соответствующиьш группами из N соседних разрядов информационного входа блока и устройства.

Одноименные управляющие входы и разряды управляющих входов 19, 18 и знаковый вход всех модулей соединяются между собой и соединяются с соответствующими входами блока и устройства. При этом входы 18 соединяются с первым входом задания величины сдвига устройства (младшими разрядами кода величины сдвига). Группа элементов И 3 и элемент И-НЕ 4 могут быть общими для всех модулей блока.

Входы 22 для всех модулей в блоке, кроме крайнего левого модуля, соединяются с соответствующими разрядами входа блокировки (или управляющего) блока. Вход 22 крайнего левого модуля блоке соединен с входом 1.

Преобразователь кода содержит модуль и дешифратор границ, вход дешифратора границ и информационный вход модуля связаны соответствующими разрядами между собой и с выходом блока ячеек шифрации, разряды которого соединены с выходами 29 модулей в блоке ячеек шифрации. Выход дешифратора границ соответствующими разрядами соединен с входом блокировки (управляюим входом) блока ячеек шифрации. Входа 14 и 22 модуля в преобразователе кода соединены с входом 1. Вход 18 модуля в преобраз ователе кода соединен с вторым входом задания величины, сдвига (старшими разрядами кода величины сдвига). Вход 19 модуля в преобразователе кодов соединен с входом признака сдвига блока шифраторов и устройства.-Выход 29 модуля в преобразователе кода соединен с выходом признака куля устройства.

Соединение разрядов выходов 31 модулей в блоке ячеек шифрации и в преобразователе осуществляется так же, как и выходов ячеек шифрации в известном устройстве. Выходы 30 модулей блока ячеек иифрации и модуля в преобразователе соединены.с соот- ветствуюпщми входами дополнительного элемента И, выход которого соединен с выходом признака переполнения устройства. Информационный вход блока ячеек шифрации, кроме крайнего правого разряда, соединен с информационным входом устройства. Крайний пра- вый разряд информационного входа блока ячеек шифрации соединен с входом О.

Таким образом, с помощью модуля можно строить многоразрядные устрой- ства для формирования кода нормализации и признака переполнения.

Формулам зобре тения

1. Модуль для формирования признака переполнения и кода нормализации, содержащий первый и второй узлы шиф- рации, элемент И-НЕ и узел коммутации, причем выход элемента И-НЕ сое- динен с первым управляющим входом узла коммутации, отличающий- с я тем, что, с целью сокращения аппаратурных затрат,, он содержит группу элементов И, причем входы старших и младших разрядов информационно го входа модуля соединены с входами разрядов первых входов первого и второго узлов шифрации соответственно, вторые входы которых объединены и соединены со знаковым входом модуля, входы разрядов входа задания величины сдвига которого соединены с первыми входами соответствующих элементов И группы, вторые входы которых соединены с входом задания режима модуля, прямые выходы элементов И группы соединены с входами .соответствующих разрядов третьих входов первого и второго узлов шифрации, выходы раз- рядов которых соединены соответственно с информационными входами первой и.второй групп узла коммутации, второй управляющий вход которого соеди.

. д (5

20 25

о. ,

35

40

нен с входом блокировки модуля, инверсные выходы элементов И группы соединены с соответствующими входами элемента И-НЕ, выходы группы узла коммутации являются соответственно выходами признака нуля, признака переполнения и кода нормализации модуля. I

2. Модуль по п. 1, о т л и ч а ю- щ и и с я тем, что узел коммутации содержит элемент НЕ, элемент И, первый, второй, третий, четвертый, пятый и шестой элементы И-НЕ, причем первый информационный вход первой группы узла коммутации соединен с первыми входами элемента И, первого и второго элементов И-НЕ, с входом элемента НЕ, второй управляющий вход узла коммутации соединен с первыми входами элементов И-НЕ с третьего по шестой, выход элемента НЕ соединен с вторым входом четвертого элемента И-НЕ, первый уцравляюш 1й вход узла коммутации соединен с вторым входом третьего элемента И-НЕ, третий вход которого соединен с вторым входом пятого элемента И-НЕ и с вторым информационным входом первой группы узла коммутации, третий информационный вход первой группы которого соединен с вторым входом шестого элемента И-НЕ, третий вход которого и третий вход пятого элемента И-НЕ соединены с выходами соответственно второго и первого элементов И-НЕ, первый информационный вход второй группы узла коммутации соединен с вторым входом элемента И, второй информационный вход второй группы. узла коммутации соединен с входом первого элемента И-НЕ и с четвертым входом третьего элемента И-НЕ, третий информационный вход второй группы узла коммутации соединен с вторым входом второго элемента И-НЕ, выходы элемента И и третьего элемента И-НЕ являются первым и вторым выходами группы узла коммутации, выходы разрядов третьего выхода группы которого соединены соответственно с выходами четвертого,пятого и шестого элементов И-НЕ.

Адресный вход элемента ПЗУ

Разряды выхода элемента ПЗУ

11

1501041 2

,V

Продолжение табл. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор кода нормализации | 1985 |

|

SU1345351A1 |

| Устройство для формирования сигналов четности | 1988 |

|

SU1571591A1 |

| Устройство для сдвига и нормализации | 1989 |

|

SU1667045A1 |

| Устройство для сопряжения вычислительного модуля с магистралью | 1985 |

|

SU1325495A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1325481A1 |

| ШИФРАТОР | 1991 |

|

RU2023345C1 |

| Модуль для сдвига операндов | 1988 |

|

SU1617434A1 |

| Устройство для сдвига данных | 1983 |

|

SU1140113A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297055A1 |

| Устройство для определения кода нормализации | 1987 |

|

SU1465878A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения устройств формирования кода нормализации и признака переполнения при арифметических сдвигах влево в цифровых вычислительных машинах и системах. Целью изобретения является сокращение аппаратурных затрат. Поставленная цель достигается тем, что модуль для формирования признака переполнения и кода нормализации, содержащий узлы 1 и 2 шифрации, элемент И-НЕ 4 и узел 5 коммутации, содержит группу элементов И 3, при этом узел 5 коммутации содержит элемент И 6, элемент НЕ 7 и элементы И-НЕ 8-13 с соответствующимися связями. 1 з.п. ф-лы, 1 ил., 2 табл.

Адресный вход элемента ПЗУ

IZiir

20

17

0(1)

0(1)

0(1)

IXXX(OXXX) О 0000(1111) 1 XXXI(XXXO) О

Разряды выхода элемента ПЗУ

iz:i

26

28

О

1 1

X X X

| Шифратор кода нормализации | 1985 |

|

SU1345351A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР {i 1331315, | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1988-02-18—Подача