Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействую- 1ЦИХ арифметических устройств.

Цель изобретения - повышение точности выполнения операции деления.

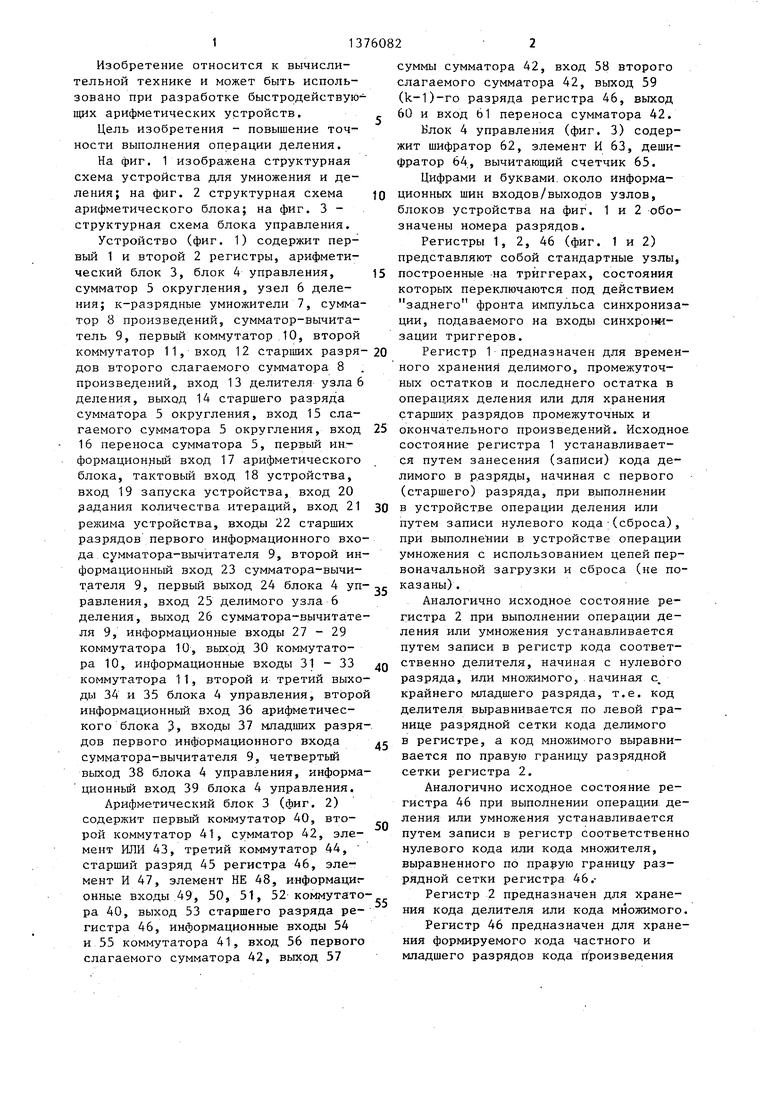

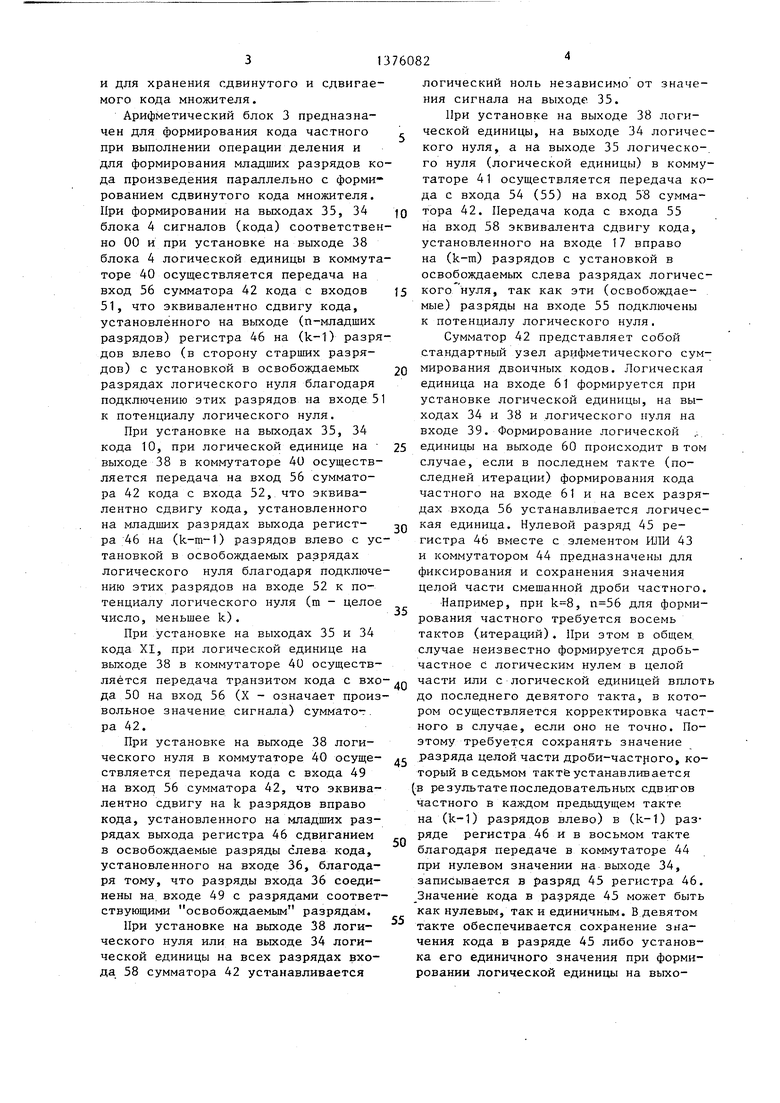

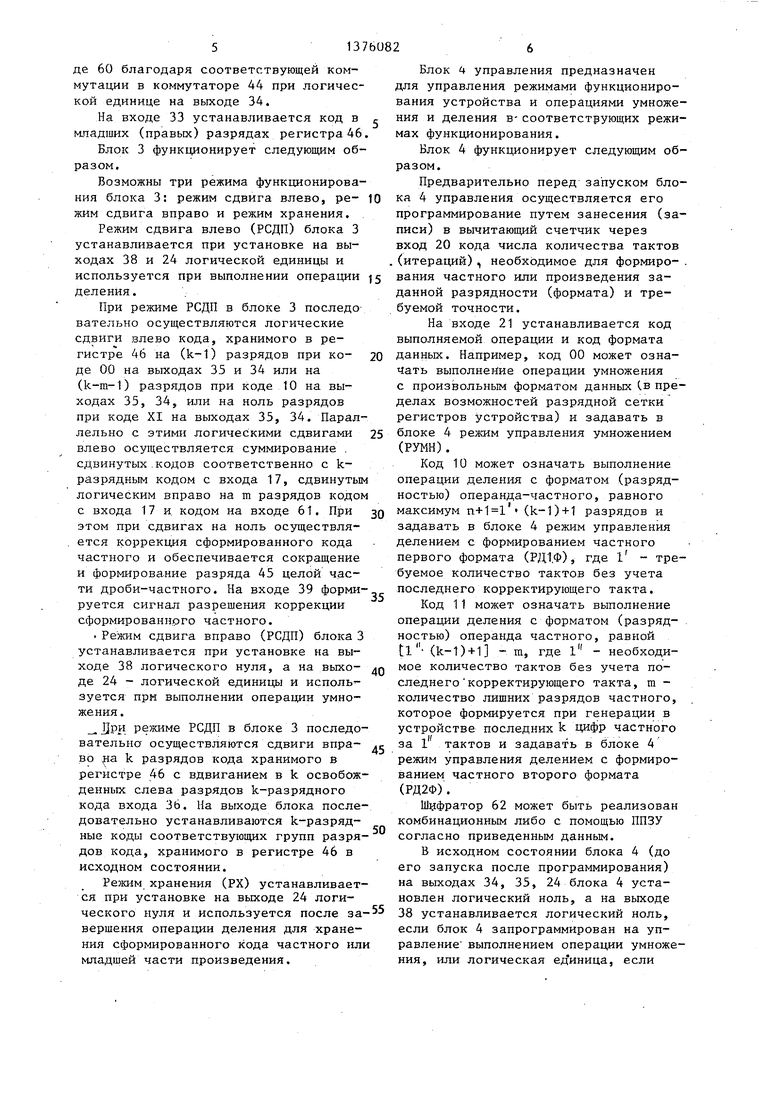

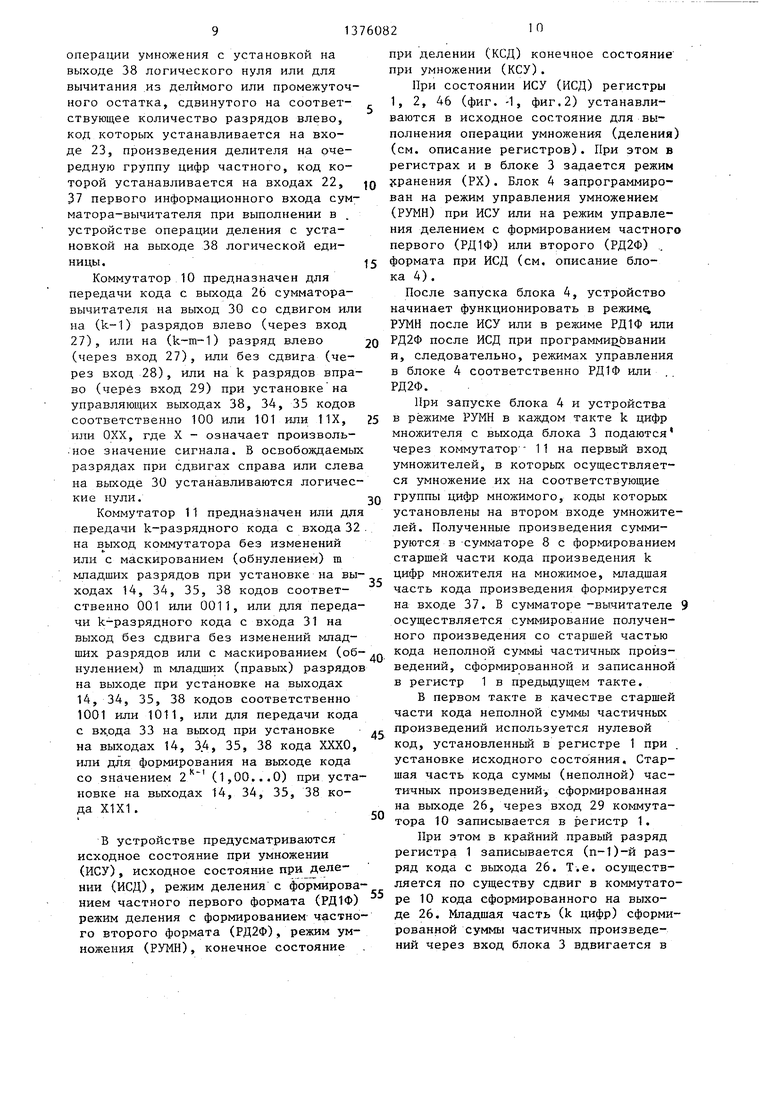

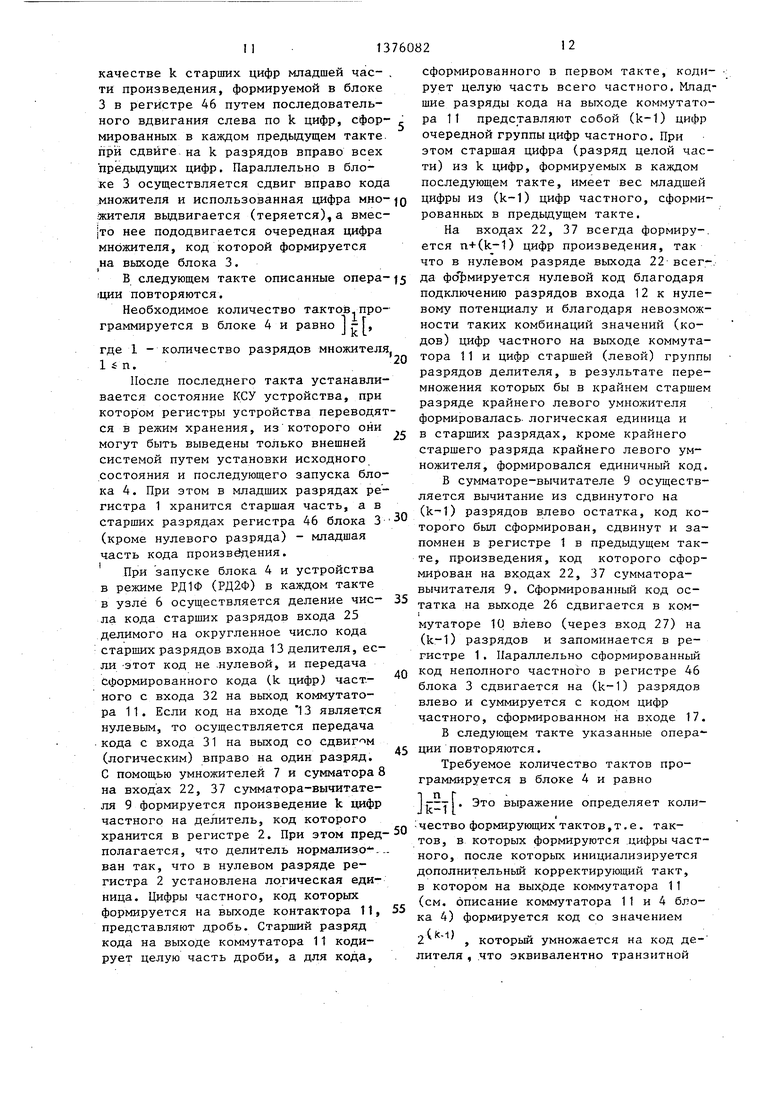

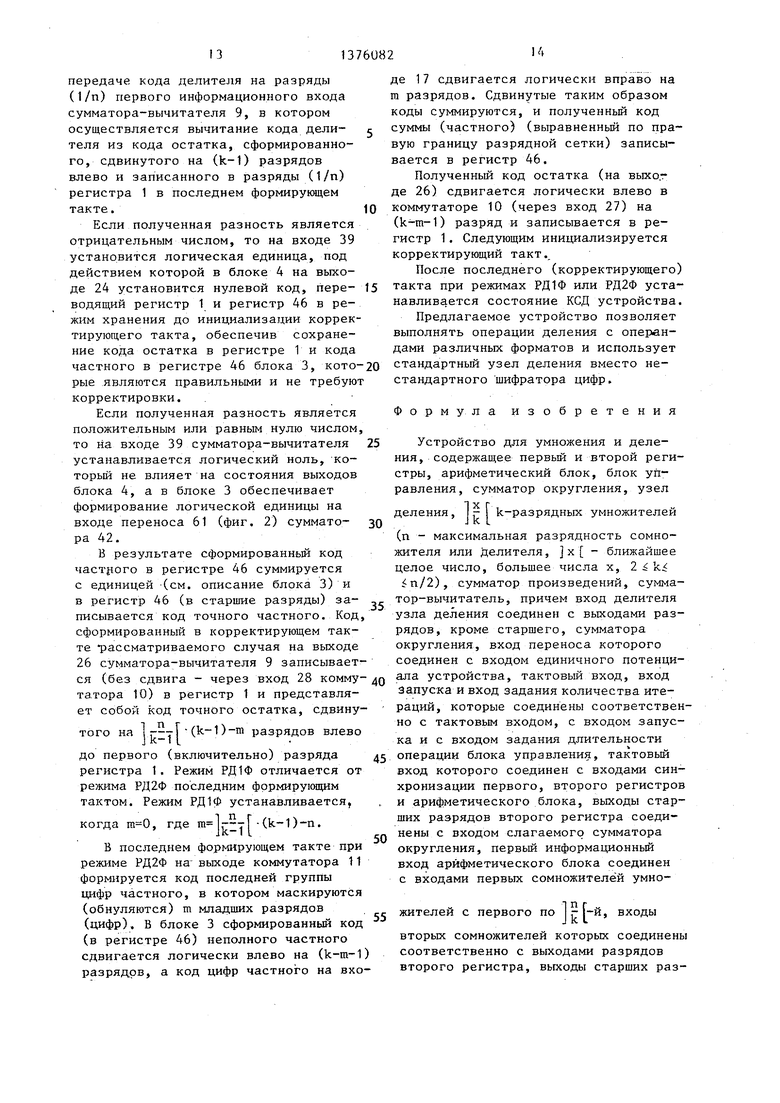

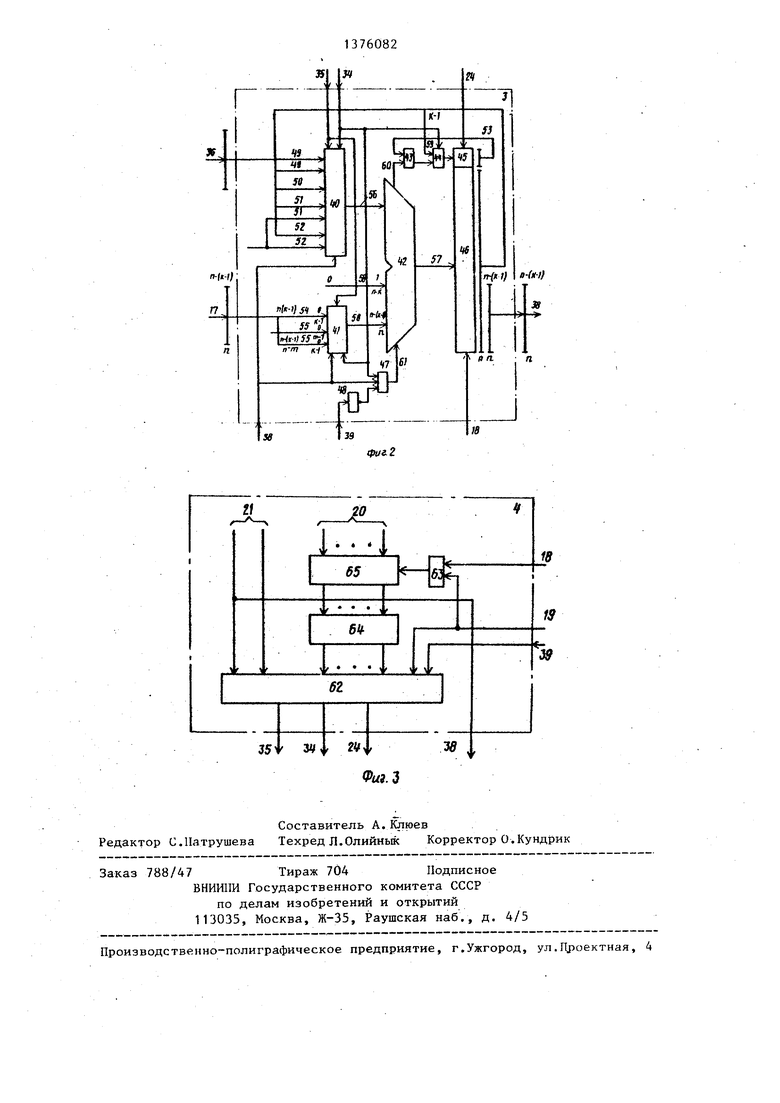

На фиг. 1 изображена структурная схема устройства для умножения и деления; на фиг. 2 структурная схема арифметического блока; на фиг. 3 - структурная схема блока управления.

Устройство (фиг. 1) содержит первый 1 и второй 2 регистры, арифметический блок 3, блок 4 управления, сумматор 5 округления, узел 6 деления; к-разрядные умножители 7, сумматор 8 произведений, сумматор-вычита- тель 9, первый коммутатор 10, второй коммутатор 11, вход 12 старших разря- дов второго слагаемого сумматора 8 произведений, вход 13 делителя узла 6 деления, выход 14 старшего разряда сумматора 5 округления, вход 15 слагаемого сумматора 5 округления, вход 16 переноса сумматора 5, первый информационный вход 17 арифметического блока, тактовый вход 18 устройства, вход 19 запуска устройства, вход 20 задания количества итераций, вход 21 режима устройства, входы 22 старших разрядов первого информационного входа с мматора-вычитателя 9, второй информационный вход 23 сумматора-вычи- т.ателя 9, первый выход 24 блока 4 уп равления, вход 25 делимого узла 6 деления, выход 26 сумматора-вычитате ля 9, информационные входы 27-29 коммутатора 10, выход 30 коммутатора 10, информационные входы 31-33 коммутатора 11, второй и третий выходы 34 и 35 блока 4 управления, второ информационньш вход 36 арифметического блока 3, входы 37 младших разрядов первого информационного входа сумматора-вычитателя 9, четвертый выход 38 блока 4 управления, информа ционньй вход 39 блока 4 управления.

Арифметический блок 3 (фиг. 2) содержит первый коммутатор 40, второй коммутатор 41, сумматор 42, элемент ИЛИ 43, третий коммутатор 44, старший разряд 45 регистра 46, элемент И 47, элемент НЕ 48, информациг онные входы 49, 50, 51, 52 коммутатора 40, выход 53 старшего разряда регистра 46, информационные входы 54 и 55 коммутатора 41, вход 56 первого слагаемого сумматора 42, выход 57

0 5 0 с 0

0

суммы сумматора 42, вход 58 второго слагаемого сумматора 42, выход 59 (k-l)-ro разряда регистра 46, выход 60 и вход 61 переноса сумматора 42.

Блок 4 управления (фиг. 3) содержит шифратор 62, элемент И 63, дешифратор 64, вычитающий счетчик 65.

Цифрами и буквами, около информационных шин входов/выходов узлов, блоков устройства на фиг. 1 и 2 обозначены номера разрядов.

Регистры 1, 2, 46 (фиг. 1 и 2) представляют собой стандартные узлы, построенные на триггерах, состояния которых переключаются под действием заднего фронта импульса синхронизации, подаваемого на входы синхрош - зации триггеров.

Регистр 1 предназначен для временного хранения делимого, промежуточных остатков и последнего остатка в операциях деления или для хранения старших разрядов промежуточных и окончательного произведений. Исходное состояние регистра 1 устанавливается путем занесения (записи) кода делимого в разряды, начиная с первого (старшего) разряда, при выполнении в устройстве операции деления или путем записи нулевого кода (сброса), при выполнении в устройстве операции умножения с использованием цепей первоначальной загрузки и сброса (не показаны) .

Аналогично исходное состояние регистра 2 при выполнении операции деления или умножения устанавливается путем записи в регистр кода соответственно делителя, начиная с нулевого разряда, или множимого, начиная с крайнего младшего разряда, т.е. код делителя выравнивается по левой границе разрядной сетки кода делимого в регистре, а код множимого выравнивается по правую границу разрядной сетки регистра 2.

Аналогично исходное состояние регистра 46 при выполнении операции деления или умножения устанавливается путем записи в регистр соответственно нулевого кода или кода множителя, выравненного по правую границу разрядной сетки регистра 46.Регистр 2 предназначен для хранения кода делителя или кода множимого.

Регистр 46 предназначен для хранения формируемого кода частного и младшего разрядов кода п роизведения

и для хранения сдвинутого и сдвигаемого кода множителя.

Арифметический блок 3 предназначен для формирования кода частного при выполнении операции деления и для формирования младших разрядов кода произведения параллельно с формированием сдвинутого кода множителя. При формировании на выходах 35, 34 блока 4 сигналов (кода) соответственно 00 и при установке на выходе 38 блока 4 логической единицы в коммутаторе 40 осуществляется передача на вход 56 сумматора 42 кода с входов 51, что эквивалентно сдвигу кода, установленного на выходе (п-младших разрядов) регистра 46 на (k-1) разрядов влево (в сторону старших разрядов) с установкой в освобождаемых разрядах логического нуля благодаря подключению этих разрядов на входе 5 к потенциалу логического нуля.

При установке на выходах 35, 34 кода 10, при логической единице на выходе 38 в коммутаторе 40 осуществляется передача на вход 56 сумматора 42 кода с входа 52, что эквивалентно сдвигу кода, установленного на младших разрядах выхода регистра 46 на (k-m-1) разрядов влево с установкой в освобождаемых разрядах логического нуля благодаря подключению этих разрядов на входе 52 к потенциалу логического нуля (т - целое число, меньшее k).

При установке на выходах 35 и 34 кода XI, при логической единице на выходе 38 в коммутаторе 40 осуществляется передача транзитом кода с входа 50 на вход 56 (X - означает произвольное значение сигнала) сумматог. ра 42.

При установке на выходе 38 логического нуля в коммутаторе 40 осуществляется передача кода с входа 49 на вход 56 сумматора 42, что эквивалентно сдвигу на k разрядов вправо кода, установленного на младших разрядах выхода регистра 46 сдвиганием в освобождаемые разряды слева кода, установленного на входе 36, благодаря тому, что разряды входа 36 соединены на входе 49 с разрядами соответствующими освобождаемым разрядам.

При установке на выходе 38 логического нуля или на выходе 34 логической единицы на всех разрядах входа 58 сумматора 42 устанавливается

логический ноль независимо от значения сигнала на выходе 35.

При установке на выходе 38 логи- ческой единицы, на выходе 34 логического нуля, а на выходе 35 логическо-. го нуля (логической единицы) в коммутаторе 41 осуществляется передача кода с входа 54 (55) на вход 58 сумма- 0 тора 42. Передача кода с входа 55 на вход 58 эквивалента сдвигу кода, установленного на входе 17 вправо на (k-m) разрядов с установкой в освобождаемых слева разрядах логичес- 5 кого нуля, так как эти (освобождаемые) разряды на входе 55 подключены к потенциалу логического нуля.

Сумматор 42 представляет собой стандартный узел арифметического сум- 0 мирования двоичных кодов. Логическая единица на входе 61 формируется при установке логической единицы, на выходах 34 и 38 и логического нуля на входе 39. Формирование логической .: 5 единицы на выходе 60 происходит в том случае, если в последнем такте (последней итерации) формирования кода частного на входе 61 и на всех разрядах входа 56 устанавливается логичес- 0 кая единица. Нулевой разряд 45 регистра 46 вместе с элементом ИЛИ 43 и коммутатором 44 предназначены для фиксирования и сохранения значения целой части смешанной дроби частного. Например, при , для формирования частного требуется восемь тактов (итераций). При этом в общем, случае неизвестно формируется дробь- частное с логическим нулем в целой ц части или с логической единицей вплоть до последнего девятого такта, в котором осуществляется корректировка частного в случае, если оно не точно. Поэтому требуется сохранять значение разряда целой части дpoби-чacт{ oгo, который в седьмом такте устанавливается (в результате последовательных сдвигов частного в каждом предыдущем такте на (k-1) разрядов влево) в (k-1) разряде регистра 46 и в восьмом такте благодаря передаче в коммутаторе 44 при нулевом значении на выходе 34, записывается в разряд 45 регистра 46. Значение кода в разряде 45 может быть как нулевым, так и единичным. В девятом такте обеспечивается сохранение значения кода в разряде 45 либо установка его единичного значения при формировании логической единицы на выхо5

0

5

е 60 благодаря соответствующей комутации в коммутаторе 44 при логичесой единице на выходе 34.

На входе 33 устанавливается код в ладших (правых) разрядах регистра 46.

Блок 3 функционирует следующим обазом.

Возможны три режима функционирования блока 3: режим сдвига влево, ре- Ю им сдвига вправо и режим хранения.

Режим сдвига влево (РСДП) блока 3 устанавливается при установке на выходах 38 и 24 логической единицы и используется при выполнении операции 5 деления.

При режиме РСДП в блоке 3 последовательно осуществляются логические сдвиги влево кода, хранимого в регистре 46 на (k-1) разрядов при ко- 20 де 00 на выходах 35 и 34 или на (k-m-1) разрядов при коде 10 на выходах 35, 34, или на ноль разрядов при коде XI на выходах 35, 34. Параллельно с этими логическими сдвигами 25 влево осуществляется суммирование . сдвинутых.кодов соответственно с k- разрядным кодом с входа 17, сдвинутым логическим вправо на m разрядов кодом с входа 17 и. кодом на входе 61. При зо этом при сдвигах на ноль осуществля- ется коррекция сформированного кода частного и обеспечивается сокращение и формирование разряда 45 целой части дроби-частного. На входе 39 формируется сигнал разрешения коррекции сформированнрго частного.

Режим сдвига вправо (РСДП) блока 3 устанавливается при установке на выходе 38 логического нуля, а на выхо- Q де 24 - логической единицы и используется при выполнении операции умножения.

Дри РСДП в блоке 3 последовательна осуществляются сдвиги впра- .с во |ia k разрядов кода хранимого в регистре 46 с вдвиганием в k освобожденных слева разрядов k-разрядного кода входа 36. На выходе блока последовательно устанавливаются k-разряд- ные коды соответствующих групп разрядов кода, хранимого в регистре 46 в исходном состоянии.

Режим хранения (РХ) устанавливается при установке на выходе 24 логического нуля и используется после за-- вершения операции деления для хранения сформированного кода частного или младшей части произведения.

35

50

о

Q

с

5

0

Блок 4 управления предназначен для управления режимами функционирования устройства и операциями умножения и деления в- соответструющих режимах функционирования.

Блок 4 функционирует следующим образом.

Предварительно перед запуском блока 4 управления осуществляется его программирование путем занесения (записи) в вычитающий счетчик через вход 20 кода числа количества тактов .(итераций), необходимое для формирования частного или произведения заданной разрядности (формата) и требуемой точности.

На входе 21 устанавливается код выполняемой операции и код формата данных. Например, код 00 может означать выполнение операции умножения с произвольным форматом данных (.в пределах возможностей разрядной сетки регистров устройства) и задавать в блоке 4 режим управления умножением (РУМН).

Код 10 может означать выполнение операции деления с форматом (разрядностью) операнда-частного, равного максимум (k-1) + 1 разрядов и задавать в блоке 4 режим управления делением с формированием частного первого формата (РД1,Ф), где 1 - требуемое количество тактов без учета последнего корректирующего такта.

Код 11 может означать выполнение операции деления с форматом (разрядностью) операнда частного, равной (k-1) + l - m, где l - необходимое количество тактов без учета последнего корректирующего такта, m - количество лишних разрядов частного, которое формируется при генерации в устройстве последних k цифр частного за 1 тактов и задавать в блоке 4 режим управления делением с формированием частного второго формата (РД2Ф).

Шифратор 62 может быть реализован комбинационным либо с помощью ППЗУ согласно приведенным данным.

В исходном состоянии блока 4 (до его запуска после программирования) на выходах 34, 35, 24 блока 4 установлен логический ноль, а на выходе 38 устанавливается логический ноль, если блок 4 запрограммирован на управление выполнением операции умножения, или логическая ед иница, если

блок 4 запрограммирован на выполнение операции деления.

Блок 4 переходит в конечное состо яние при установке в вычитающем счет, чике 65 нулевого кода, сопровождаемо установкой логического нуля на выходе 24.

При режиме РУМН после запуска бло ка 4 путем установки логической единицы на входе 19 на выходе 24 устанавливается логическая единица, а на выходе 38 - логический нуль и удерживаются в течение всего времени выпол нения операции умножения в устройств пока не будут проинициированы в устройстве необходимое количество тактов (пока в вычитающем счетчике не установится нулевой код, так как при каждом такте из вычитающего счетчика в блоке 4 вычитается единица). На выходах 34 и 35 устанавливаются логические нули.

При режиме РД1Ф после запуска блока 4 на выходах 24, 38 устанавливается логическая единица, а на выходах 34 и 35 - логический ноль. Логическая единица на выходе 38 и логический ноль на выходе 34 удерживаются в те- чение всего времени выполнения операции деления вплоть до установки конечного состояния.

После предпоследнего такта перед последним (корректирующим) тактом на выходе 34 блока 4 устанавливается логическая единица. Перед последним корректирующим тактом на входе 39 блока 4 возможна установка логического нуля или логической единицы Если на входе 39 устанавливается логический ноль, то обеспечивается сохранение установленной на выходе 24 логической единицы до установки конечного состояния блока. Это означает, что сформированное в регистре 46 частное неправильно и далее осуществляется корректировка частного и остатка.

Если на входе 39 устанавливается

логическая единица, то да инициализации (появления синхросигнала) последнего корректирующего такта на выходе 24 устанавливается логический ноль, предотвращающий изменение состояний регистров 1, 46 и означающий, что сформированное частное в регистре 46 и остаток в регистре 1 правильные и не требуется корректировка.

с

Ю з 0

5 О

.,, с

5

0

5

При режиме РД2Ф блок 4 функционирует аналогично как и в режиме РД1Ф с тем отличием, что перед двумя последними тактами, т.е. перед последним не корректирующим тактом на выходе 35 блока 4 устанавливается логическая единица, которая удерживается по крайней мере один такт (до корректирующего такта).

Сумматор 5 предназначен для округления кода старших разрядов делителя путем прибавления к нему логической единицы, подаваемой через вход 16. При на выходе сумматора 5 может Сформироваться код, имеющий количество разрядов на единицу большее, чем входной код. Это происходит в том случае, если во всех разрядах входного кода установлена логическая единица.- В этом случае на разрядах выхода 13 формируется нулевой код, а на выходе 14 - логическая единица.

Узел 6 деления предназначен для деления, например, (k+1)-x разрядного двоичного числа, код которого уста- . новлен на входе 25 узла на (k+3)-x разрядное двоичное число, код которого установлен на входе 13 узла, при условии, что оно не равно нулю. В случае, если на. входе 13 установлен нулевой код,узел 6 отключается (не используется) . Выход узла 6 содержит k старших разрядов, включая крайний старший разряд целой части.

Умножители 7 предназначены для формирования произведений двоичных цифр соответствующих групп разрядов кодов, хранимых в регистре 2, на группу цифр, код которых формируется на выходе коммутатора 11.

Сумматор 8 предназначен для суммирования двоичных чисел, формируемых на младших разрядах последующих (спра- во налево) умножителей 7, с двоичными числами, формируемыми на старших разрядах соответствующих предыдущих умножителей с целью формирования старшей части кода промежуточного произведения двоичного числа, хранимого в регистре 2, на двоичное число, формируемое на выходе коммутатора 11. Младшая часть кода промежуточного произведения формируется на k младших разрядах выхода крайнего правого умножителя 7.

Сумматор-вычитатель 9 предназначен для суммирования частичных произведений при выполнении в устройстве

операции умножения с установкой на выходе 38 логического нуля или для вычитания из делимого или промежуточного остатка, сдвинутого на соответ- ствующее количество разрядов влево, код которых устанавливается на входе 23, произведения делителя на очередную группу цифр частного, код которой устанавливается на входах 22, 37 первого информационного входа сум- матора-вычитателя при выполнении в устройстве операции деления с установкой на выходе 38 логической единицы.

Коммутатор 10 предназначен для передачи кода с выхода 26 сумматора- вычитателя на выход 30 со сдвигом или на (k-1) разрядов влево (через вход 27), или на () разряд влево (через вход 27), или без сдвига (через вход 28), или на k разрядов вправо (через вход 29) при установке на управляющих выходах 38, 34, 35 кодов соответственно 100 или 101 или 11Х, или ОХХ, где X - означает произволь- ное значение сигнала. В освобождаемых разрядах при сдвигах справа или слева на выходе 30 устанавливаются логические пули.

Коммутатор 11 предназначен или для передачи k-разрядного кода с входа 32 на выход коммутатора без изменений или с маскированием (обнулением) m младших разрядов при установке на выходах 14, 34, 35, 38 кодов соответственно 001 или 0011, или для передачи k-разрядного кода с входа 31 на выход без сдвига без изменений младших разрядов или с маскированием (об- нулением) m младших (правых) разрядов на выходе при установке на выходах 14, 34, 35, 38 кодов соответственно 1001 или 1011, или для передачи кода с вх.ода 33 на выход при установке на выходах 14, 34, 35, 38 кода ХХХО, или для формирования на выходе кода со значением (1,00...0) при установке на выходах 14, 34, 35, 38 кода Х1Х1.

В устройстве предусматриваются исходное состояние при умножении (ИСУ), исходное состояние при делении (ИСД), режим деления с формированием частного первого формата (РД1Ф) режим деления с формированием частного второго формата (РД2Ф), режим умножения (РУМН), конечное состояние

5

0 5 0

,Q 50

5

при делении (КОД) конечное состояние при умножении (КСУ).

При состоянии ИСУ (ИСД) регистры 1, 2, 46 (фиг. -1, фиг. 2) устанавливаются в исходное состояние для выполнения операции умножения (деления) (см. описание регистров). При этом в регистрах и в блоке 3 задается режим сранения (РХ). Блок 4 запрограммирован на режим управления умножением (РУМН) при ИСУ или на режим управления делением с формированием частного первого (РД1Ф) или второго (РД2Ф) формата при ИСД (см. описание блока 4 ).

После запуска блока 4, устройство начинает функционировать в режиму РУМН после ИСУ или в режиме РД1Ф или РД2Ф после ИСД при программи Ьвании и, следовательно, режимах управления в блоке 4 соответственно РД1Ф или РД2Ф.

При запуске блока 4 и устройства в режиме РУМН в каждом такте k цифр множителя с выхода блока 3 подаются через коммутатор 11 на первый вход умножителей, в которых осуществляется умножение их на соответствующие группы цифр множимого, коды которых установлены на втором входе умножителей. Полученные произведения суммируются в -сумматоре 8 с формированием старшей части кода произведения k цифр множителя на множимое, младшая часть кода произведения формируется на входе 37. В сумматоре -вычитателе 9 осуществляется суммирование полученного произведения со старшей частью кода неполной суммь частичных произведений, сформированной и записанной в регистр 1 в предыдущем такте.

В первом такте в качестве старшей части кода неполной суммы частичных произведений используется нулевой код, установленный в регистре 1 при установке исходного состояния. Старшая часть кода суммы (неполной) частичных произведений-, сформированная на выходе 26, через вход 29 коммутатора 10 записывается в регистр 1.

При этом в крайний правьй разряд регистра 1 записывается (п-1)-й разряд кода с выхода 26. Т.е. осуществляется по существу сдвиг в коммутаторе 10 кода сформированного на выходе 26. Младшая часть (k цифр) сформированной суммы частичных произведений через вход блока 3 вдвигается в

качестве k старших цифр младшей час- ти произведения, формируемой в блоке 3 в регистре 46 путем последовательного вдвигания слева по k цифр, сфор- мированных в каждом предьщущем такте при сдвиге,на k разрядов вправо всех предьщущих цифр. Параллельно в блоке 3 осуществляется сдвиг вправо кода множителя и использованная цифра множителя выдвигается (теряется), а вмес- |то нее пододвигается очередная цифра множителя, код которой формируется на выходе блока 3.

В следующем такте описанные опера|ции повторяются.

Необходимое количество такто В|Про- граммируется в блоке 4 и равно j г ,

где 1 - количество разрядов множителя 1.п.

После последнего такта устанавливается состояние КСУ устройства, при котором регистры устройства переводятся в режим хранения, из которого они могут быть выведены только внешней системой путем установки исходного состояния и последующего запуска блока 4. При этом в младших разрядах регистра 1 хранится Старшая часть, а в старших разрядах регистра 46 блока 3 (кроме нулевого разряда) - младшая часть кода произведения. При запуске блока 4 и устройства в режиме РД1Ф (РД2Ф) в каждом такте в узле 6 осуществляется деление чис- ла кода старших разрядов входа 25 делимого на округленное число кода старших разрядов входа 13 делителя, если -этот код не .нулевой, и передача Сформированного кода (k цифр) частного с входа 32 на выход коммутатора 11. Если код на входе 13 является нулевьм, то осуществляется передача кода с входа 31 на выход со сдвигам (логическим) вправо на один разряд. С помощью умножителей 7 и сумматора 8 на входах 22, 37 сумматора-вычитате- ля 9 формируется произведение k хщфр частного на делитель, код которого хранится в регистре 2. При этом предполагается, что делитель нормапизо-.- ван так, что в нулевом разряде регистра 2 установлена логическая единица. Цифры частного, код которых формируется на выходе контактора 11, представляют дробь. Старший разряд кода на выходе коммутатора 11 кодирует целую часть дроби, а для кода.

д

5

0

5

5

сформированного в первом такте, кодирует целую часть всего частного. Младшие разряды кода на выходе коммутатора 11 представляют собой (k-1) цифр

очередной группы цифр частного. При этом старшая цифра (разряд целой части) из k цифр, формируемых в каждом последующем такте, имеет вес младшей цифры из (k-1) цифр частного, сформированных в предыдущем такте.

На входах 22, 37 всегда формиру-. ется n+(k-1) цифр произведения, так что в нулевом разряде выхода 22 всег-. да фсфмируется нулевой код благодаря подключению разрядов входа 12 к нулевому потенциалу и благодаря невозможности таких комбинаций значений (кодов) цифр частного на выходе коммутатора 11 и цифр старшей (левой) группы разрядов делителя, в результате перемножения которых бы в крайнем старшем разряде крайнего левого умножителя формировалась, логическая единица и в старших разрядах, кроме крайнего старшего разряда крайнего левого умножителя, формировался единичный код.

В сумматоре-вычитателе 9 осуществляется вычитание из сдвинутого на () разрядов влево остатка, код которого был сформирован, сдвинут и запомнен в регистре 1 в предьщущем такте, произведения, код которого сформирован на входах 22, 37 сумматора- вычитателя 9. Сформированный код остатка на выходе 26 сдвигается в коммутаторе 10 влево (через вход 27) на (k-1) разрядов и запоминается в регистре 1. Параллельно сформированный код неполного частного в регистре 46 блока 3 сдвигается на (k-1) разрядов влево и суммируется с кодом цифр частного, сформированном на входе 17.

В следующем такте указанные опера ции повторяются.

Требуемое количество тактов программируется в блоке 4 и равно

Jk-TLЭто выражение определяет количество формирующих тактов,т.е. тактов, в которых формируются цифры частного, после которых инициализируется дополнительный корректирующий такт, в котором на вых.Оде коммутатора 1 1 (см. описание коммутатора 11 и 4 блока 4) формируется код со значением

С /с 1) 2 , который умножается на код делителя , .что эквивалентно транзитной

передаче кода делителя на разряды (1/п) первого информационного входа сумматора-вычитателя 9, в котором осуществляется вычитание кода дели- теля из кода остатка, сформированного, сдвинутого на (k-1) разрядов влево и записанного в разряды (1/п) регистра 1 в последнем формирующем такте.

Если полученная разность является отрицательным числом, то на входе 39 установится логическая единица, под действием которой в блоке 4 на выходе 24 установится нулевой код, пере- водящий регистр 1 и регистр 46 в режим хранения до инициализации корректирующего такта, обеспечив сохранение кода остатка в регистре 1 и кода частного в регистре 46 блока 3, которые являются правильными и не требуют корректировки.

Если полученная разность является положительным или равным нулю числом, то на входе 39 сумматора-вычитателя устанавливается логический ноль, который не влияет на состояния выходов блока 4, а в блоке 3 обеспечивает формирование логической единицы на входе переноса 61 (фиг, 2) суммато- ра 42.

В результате сформированньй код частрого в регистре 46 суммируется с единицей -(см, описание блока 3) и в регистр 46 (в старшие разряды) за- писывается код точного частного. Код, сформированный в корректирующем такте рассматриваемого случая на выходе 26 сумматора-вычитателя 9 записывается (без сдвига - через вход 28 комму- татора 10) в регистр 1 и представляет собой код точного остатка, сдвинутого на Iпт (™ разрядов влево J к I L

до первого (включительно) разряда регистра 1. Режим РД1Ф отличается от режима РД2Ф последним фррмирукмдим тактом. Режим РД1Ф устанавливается,

когда , где п1 1г-тГ-(k-D-n.

В последнем формирующем такте при режиме РД2Ф на выходе коммутатора 11 формируется код последней группы цифр частного, в котором маскируются (обнуляются) m младших разрядов (цифр), В блоке 3 сформированный код (в регистре 46) неполного частного сдвигается логически влево на (k-m-1 разрядов, а код цифр частного на вхо

Q

5

0

5

де 17 сдвигается логически вправо на m разрядов. Сдвинутые таким образом коды суммируются, и полученньй код суммы (частного) (выравненный по правую границу разрядной сетки) записывается в регистр 46,

Полученный код остатка (на выходе 26) сдвигается логически влево в коммутаторе 10 (через вход 27) на (k-m-1) разряд и записывается в регистр 1, Следующим инициализируется корректирующий такт.

После последнего (корректирующего) такта при режимах РД1Ф или РД2Ф устанавливается состояние кед устройства.

Предлагаемое устройство позволяет выполнять операции деления с операндами различных форматов и использует стандартный узел деления вместо нестандартного шифратора цифр,

Формула изобретения

Устройство для умножения и деления, содержащее первый и второй регистры, арифметический блок, блок управления, сумматор округления, узел

деления, г Г k-разрядных умножителей

(п - максимальная разрядность сомножителя или делителя, х - ближайшее целое число, большее числа х, 2 : k п/2), сумматор произведений, сумма- тор-вычитатель, причем вход делителя узла деления соединен с выходами разрядов, кроме старшего, сумматора округления, вход переноса которого соединен с входом единичного потенциала устройства, тактовый вход, вход запуска и вход задания количества итераций, которые соединены соответственно с тактовым входом, с входом запуска и с входом задания длительности операции блока управления, тактовый вход которого соединен с входами синхронизации первого, второго регистров и арифметического блока, выходы старших разрядов второго регистра соединены с входом слагаемого сумматора округления, первый информационньш вход арифметического блока соединен с входами первых сомножителей умножителей с первого по ;-|-й, входы

вторых сомножителей которых соединены соответственно с выходами разрядов второго регистра, выходы старших разрядов умножителей с первого по

тсоединены соответственно с входами разрядов первого слагаемого суммато- ра произведений, выходы младших разрядов умножителей, кроме младшего, соединены соответственно с входами разрядов, кроме старших, второго слагаемого сумматора произведений, вход старших разрядов второго слагаемого которого соединен с вх.рдом нулевого потенциала устройства, выход сумматора произведений соединен с входами старших разрядов первого информацион ного входа сумматора-вычитателя, второй информационный вход которого соединен с выходом первого регистра, вход разрешения приема которого соединен с входом разрешения работы арифметического блока и с первым выходом блока управления, выход старших разрядов первого регистра соединен с входом делимого узла деления, второй выход блока управления соеди- нен с первым входом вида операции арифметического.блока, отличаю- щ е е е с я тем, что, с целью повышения точности выполнения операции . деления, оно содержит первый и вто- рой коммутаторы, причем выход сумматора-вычитателя соединен со сдвигом на (k-1) разряд в сторону старших, без сдвига и со сдвигом на k разрядов в сторону младших соответственно с первым, вторым и третьим информационными входами первого коммутатора, выход которого соединен с информаци- .онньш входом первого регистра, выходы старших разрядов, кроме крайнего.

- jg2025-зо

35

которого соединены с первым информационным входом второго коммутатора, второй и третий информационные входы которого соединены соответственно с выходом узла деления и с выходом арифметического блока, первый информационный вход которого соединен с выходом второго коммутатора, первый управляющий вход которого соединен с выходом старшего разряда сумматора округления, второй управляющий вход второго коммутатора соединен с первым управляющим входом первого коммутатора и с вторым выходом блока уп- равления, третий выход которого соединен с вторым управляющим входом первого коммутатора, с третьим управляющим входом второго коммутатора и с вторым входом вида операции арифметического блока, второй информационный вход которого соединен с выходами k младших разрядов сумматора-вычитателя, входы младших разрядов первого информационного входа которого соединены с выходами младших разрядов младшего умножителя, четвертый выход блока управления соединен с третьим управляющим входом первого коммутатора, с четвертым управляющим входом второго коммутатора, с управляющим входом сумматора-вычитателя и с третьим входом вида операции арифметичес- кого блока, вход переноса которого соединен с информационным входом блока управления и с выходом старшего разряда сумматора-вычитетеля, вход режима устройства соединен с входом вида операции блока управления.

139

a-(ii-i)

18

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления | 1988 |

|

SU1541598A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

| Устройство для деления | 1985 |

|

SU1322264A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

Изобретение относится к вьтисли- тельной технике и может быть использовано в высокопроизйодительных системах обработки информации. Целью / изобретения является повышение точ- . ности выполнения операции деления. Поставленная цель Достигается тем, что в устройство для умножения и деления, содержащее первый 1 и второй 2 регистры, арифметический блок 3, блок 4 управления, сумматор 5 округления, узел 6 деления, группу умножителей 7, сумматор 8 произведений, сумматор-вычитатель 9 и соответствующие связи между указанными узлами и блоками, введены первьй 10 и второй 11 коммутаторы с соответствующими новыми связями. 3 ил. zt го 19 i (Л 00 О) о 00 ю за я

| Устройство для деления | 1984 |

|

SU1203515A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления чисел | 1980 |

|

SU857977A1 |

| Устройство для деления | 1978 |

|

SU802962A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-23—Публикация

1986-08-12—Подача