i

Изобретение относится к специализированным цифровым устройствам извлечения информации и служит для определения времени задержки между случайными сигналами, путем вычисления знаковой корре- ляционной функции.

Цель изобретения - упрощение устройства при сохранении прежней точности,

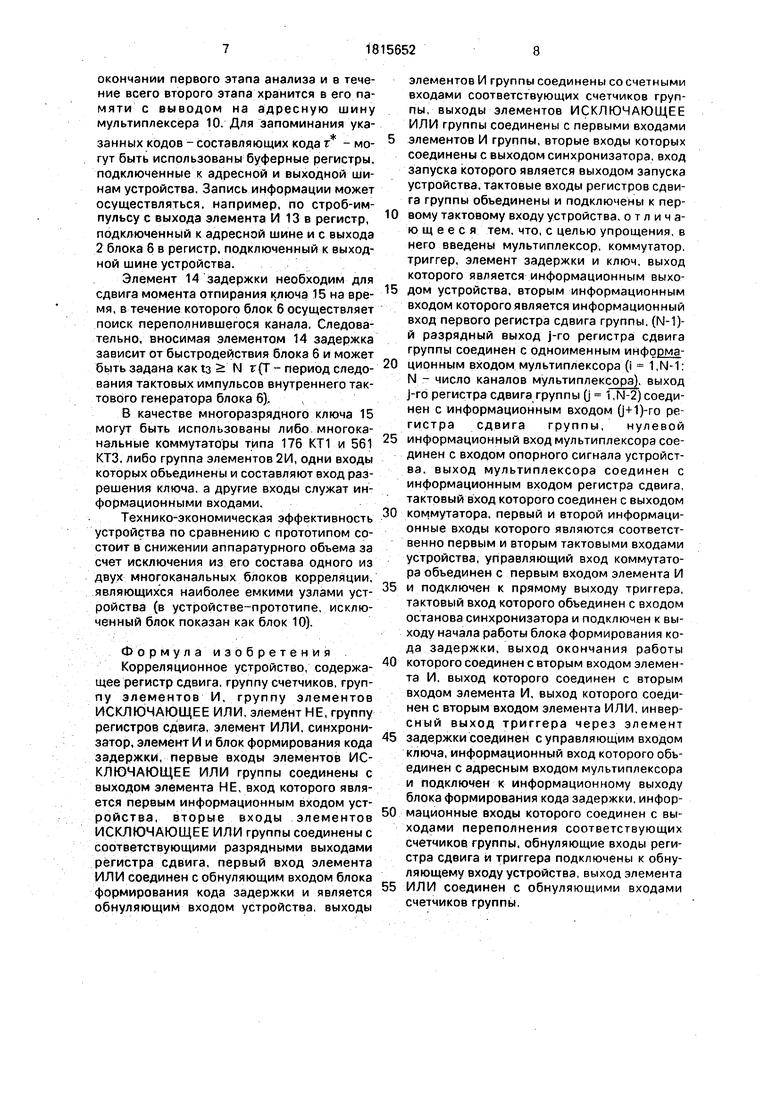

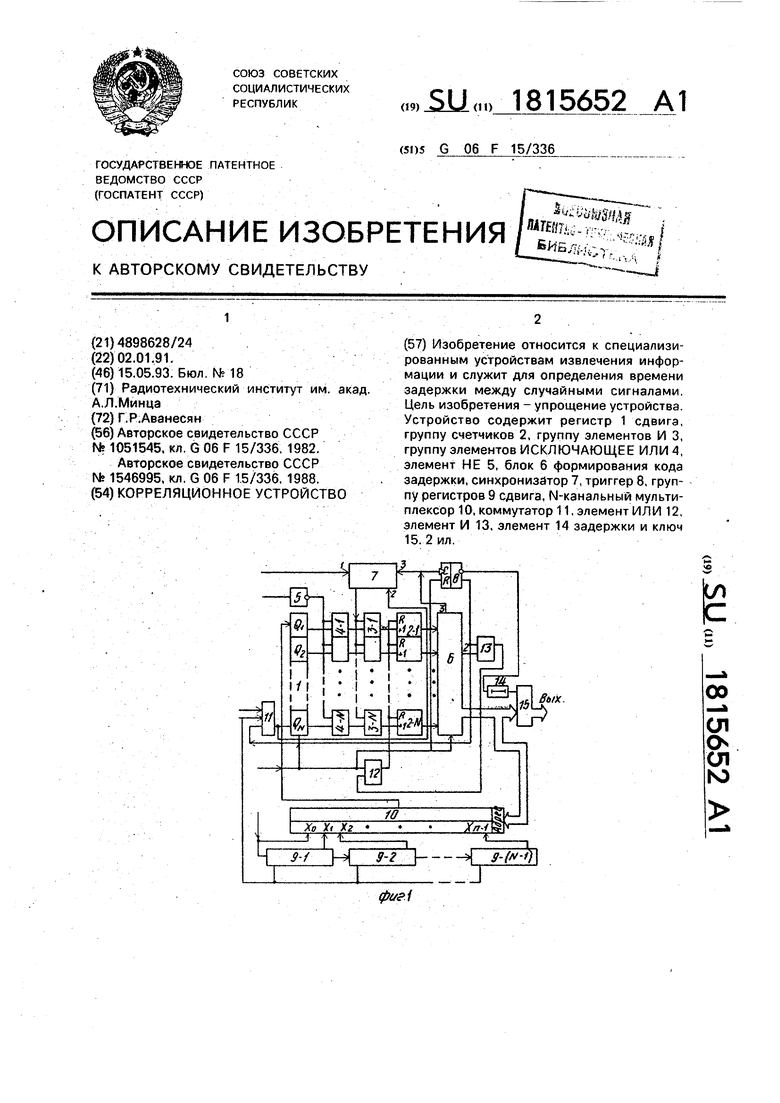

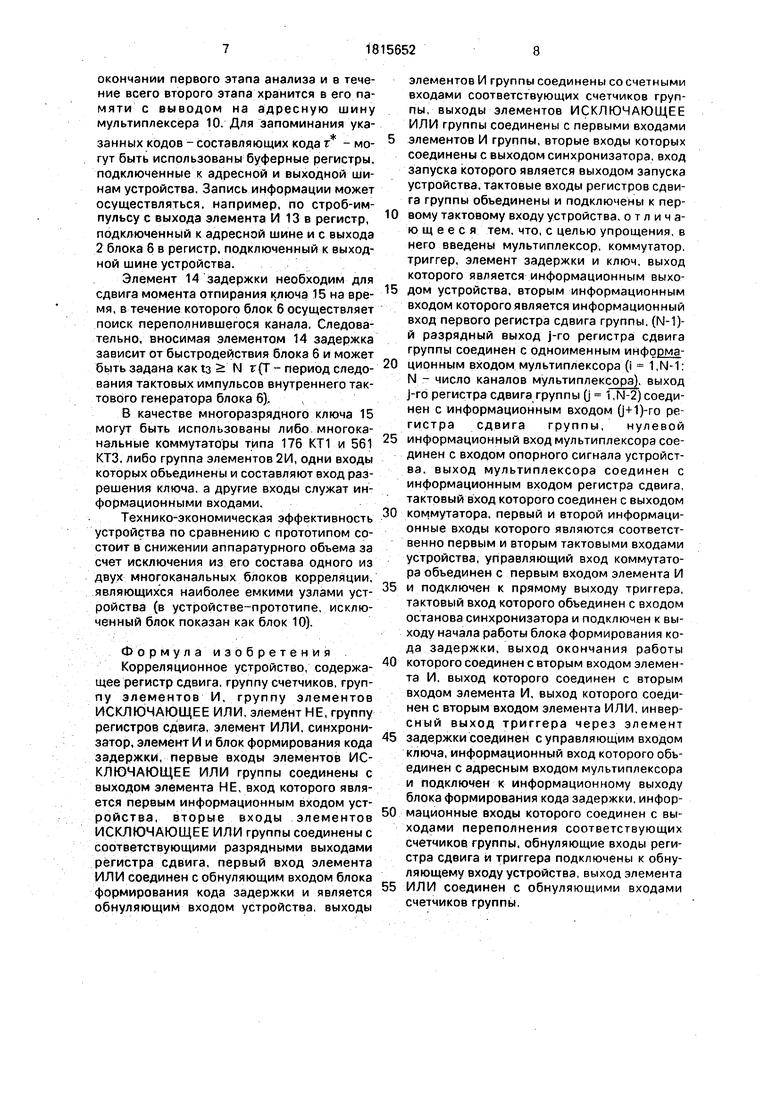

На фиг. 1 показана функциональная схема заявляемого устройства; на фиг.2 - менные диаграммы, иллюстрирующие работу устройства.

Функциональная схема (фиг, 1) содержит регистр 1 сдвига, группу счетчиков 2-1- 2-N, группу элементов И 3-1-3-N, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4-1-4-N. элемент НЕ 5, блок б формирования кода задержки, синхронизатор 7. триггер 8, группу регистров 9-14HN-1) сдвига, N-канаяь- ный мультиплексор 10, коммутатор 11, элемент ИЛИ 12, элемент И 13, элемент 14 задержки и многоразрядный ключ 15.

Первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4-1-4-N соединены с выходом элемента НЕ 5, вход которого является информационным входом X(t-r) устройства, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4-t-4-N соединены с соответствующими разрядными выходами регистре 1 сдай- га, первый вход элемента И Л И 12 соединен с обнуляющим входом 1 блока б и является обнуляющим входом Р Т, устройства, выход элемента ИЛИ 12 соединен с обнуляющими входами счетчиков 2-1-2-N, выходы элемен- тов И 3-1-3-N соединены со счетными входами соответствующих счетчиков 2-1-2-М выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4-1-4-N соединены с первыми входами элементов И 3-1-3-М, вторые входы которых соединены с выходом синхронизатора 7, вход 1 запуска которого является входом СО запуска устройства, тактовый вход 2 синхронизатора 7 соединен с тактовым входом регистра 1 сдвига, тактовый вход которого соединен с выходом коммутатора 11. первый информационный вход которого служит первым тактовым входом С К1 устройства, второй информационный вход коммутатора 11 служит вторым тактовым входом CLK2 устройства, тактовые входы регистров 9-1- 9-{N-1) сдвига объединены и подключены к второму тактовому входу CLK2 устройства, входом X(t) опорного сигнала которого служит информационный вход регистра 9-1 сдвига предпоследний (по направлению сдвига) разрядный выход которого соедй нен с первым информационным входом мультиплексора 10, предпоследний разрядный выход регистра 9-2 сдвига соединен со вторым

информационным входом мультиплексора 10, предпоследний разрядный выход регистра 9-{N-1) сдвига соединен с (М-1)-ым информационным входом мультиплексора 10, выход регистра 9-1 сдвига соединен с информационным входом регистра 9-2 сдвига и даже по правилу: выход регистра 9-i сдвига соединен с информационным входом регистра 9-{i+1) сдвига (I 1, N-1) нулевой информационный вход мультиплексора 10 соединен с входом X(t) опорного сигнала устройства, выход мультиплексора 10 сое- .динен с информационным входом регистра

1 сдвига, управляющий вход коммутатора 11 объединен с первым входом элемента И 13 и подключен к прямому выходу триггера 8, тактовый вход которого объединен со входом 3 останова синхронизатора и подключены к выходу 3 начала работы блока б, выход

2 окончания работы которого соединен с вторым входом элемента И 13. выход которого соединен с вторым входом элемента ИЛИ 12. инверсный выход триггера 8 через элемент 14 задержки соединен с разрешающим входом ключа 15. многоразрядный информационный вход которого объединен с адресным входом мультиплексора 10 и подключен к информационному выходу блока 6, информационные входы которого соединены с выходами переполнения соответствующих счетчиков 2-1-2-М, обнуляющие входы регистра 1 сдвига и триггера 8 подключены к обнуляющему входу RST устройства. Информационным выходом которого служит многоразрядный выход ключа 15.

временные диаграммы (фиг.2) содержат:. ; ;. . , : . : :

импульсы RST обнуления устройства (фиг.2а),

импульс СО запуска устройства (фиг.2б),

логические уровни на выходе 3 начала работы блока 6 (фиг.2в).

тактовые импульсы на выходе синхронизатора 7 (фиг.2г),

логические уровни на прямом выходе триггера 8 (фиг.2д),

логические уровни на разрешающем входе ключа 15 (фиг.2е),

текущий код ni на информационном вы- ходе блока 6, на этапе грубой оценки щ-1 и на этапе точной оценки П2-1 соответственно (фиг.2ж).

Принцип действия устройства (фиг.1) сострит в следующем.

До начала анализа подачей обнуляющего импульса на в:ходР5Т(фиг.2а) устройство устанавливают в исходное состояние. Опережающий X(t) i и задержанный на время т X(t- т) сигналы поступают на соответствующие входы устройства, в котором непрерывно тактируются регистр 1 сдвига и группа регистров 9 сдвига. При этом мультиплек- сер 10 коммутирует на вход регистра 1 сигнал X(t) непосредственно с входа устройства, что сопровождается появлением на разрядных выходах регистра 1 задержанных копий X(t). Причем, мультиплексор 11 исходном состоянии подает на тактовый вход регистра 1 последовательность импульсов CLK1 с периодом следования , где Т2 - период следования импульсов в последовательности CLK2.

С приходом на управляющий вход СО (фиг.26) устройство запускающего импульса начинается первый этап цикла вычислений - этап предварительной грубой оценки положения центрального взаимокорреляционного пика (ЦВКП) с разрешением по времени в TL В ответ на запускающий импульс синхронизатор 7 выдает строб-сигнал разрешения записи результатов побитных совпадений с выходом элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы 4 в счетчики группы 2, что обеспечивается подачей тактовых импульсов на объединенные входы элементов И группы 3 (фиг.2г). При переполнении одного из счетчиков группы 2 блок 6 формирует сигнал окончания этапа (фиг.2в), который (сигнал) поступает на соответствующий вход синхронизатора 7 (с выхода 3 блока 6 на вход 3 синхронизатора 7). в связи с чем прерывается поступление тактовых импульсов на объединенные входы элементов И группы 3 и устанавливается в единичное состояние триггер 8 (фиг.2д). Кроме того. блок б, выполняющий помимо прочих функцию шифратора номера канала переполнения, определяет номер канала переполнившегося счетчика и выставляет на адресном входе мультиплексора 10 соответствующий код ni-1 (фиг.2ж). Одновременно на выходе 2 окончания работы блока 6 устанавливается высокий логический-уро- вень, обнуляющий счетчики группы 2. На этом этап грубой оценки заканчивается, результатом которого служит код задержки n i. полученный при разрешении по времени в TL Далее установившийся в единичное состояние триггер 8 переводит коммутатор 11 в положение, разрешающее прохождение на тактовых вход регистра 1 импульсов CLK2 с периодом Т2. Т.О. регистр 1 переводится в режим работы многообводной линии задержки уже с дискретом задержки в Т2.

Следующий этап - оценка положения ЦВКП с более высоким разрешением, т.е. с декретом в Т2. При этом сигнал X(t) задерживается в цепочке регистров группы 9. с

одного из разрядных выходов которых он коммутируется на информационный вход регистра 1. Причем, съем сигнала осуществляется с выхода регистра 9-i. если на этапе

грубой оценки переполнился счетчик 2-(М 1). Указанное позволяет на настоящем этапе использовать регистр 1, элементы группы 3. 4 и счетчики группы 2 для корреляционного анализа, уже ни во всем диапазоне допусти0 мых задержек, а только в окружности ранее грубо вычисленного положения ЦЕЗКП. При переполнении одного и счетчиков группы 2 прерывается ведущийся счетчиками счет, а также устанавливается в нулевое состояние

5 триггер 8 (фиг.2д). Последнее приводит к появлению с задержкой во времени отпирающего высокого логического уровня (фиг.2е) на разрешающем входе ключа 15. который передает на выход устройства компоненту

0 П2-1 кода задержки.

На этапе грубой оценки вычисляется положение ЦВКП в диапазоне от 0 до (N-1) Ti. На следующем этапе с более высоким разрешением, анализ проводят в диапазоне от

5 ((m-1)Ti -Т1/2)до((гм-1)Т1 + Ti/2), причем щ 2.N. Несложно видеть, что ширина диапазона составляет Ti, т.е. дискрет грубой оценки равный Т1 разбивается на ряд интервалов шириной в Т2. В свою очередь, синте0 зированная из регистров группы 9 линия задержки должна обеспечить задержку сигTi

5

0

5

0

5

нала.Х(г) на время ((rn-1)Ti - поставленного условия Ti

Т-Д Для

i

обеспечения поставленного условия регистр 9-1 должен содержать ку- 41 разрядов, а каждый из регистров 9-2-9-(N-1) по Ti/T2 разрядов. Число разрядов регистра 1. необходимое для перекрытия диапазона

шириной в Ti доставляет N - +1. Кроме

того необходимым требованием является подключение к информационным входам мультиплексора 10 обязательно предпоследних (по направлению сдвига) разрядов регистров группы 9, последние разрядные выходы которых подключаются к информационным входам следующих в цепочке регистров.

Искомое время задержки г вычисляют по формуле

г (m-1)Ti-b. +(п2-1)Т2

где П2 - номер переполнившегося канала на этапе точной оценки. Код величины устанавливается на многоразрядном выходе устройства (фиг.2ж) по окончании второго этапа анализа. Что же касается кода величины щ-1, то он формируется блоком б по

окончании первого этапа анализа и в течение всего второго этапа хранится в его памяти с выводом на адресную шину мультиплексора 10. Для запоминания указанных кодов - составляющих кода г - могут быть использованы буферные регистры, подключенные к адресной и выходной шинам устройства. Запись информации может осуществляться, например, по строб-импульсу с выхода элемента И 13 в регистр, подключенный к адресной шине и с выхода 2 блока 6 в регистр, подключенный к выход- ной шине устройства.

Элемент 14 задержки необходим для сдвига момента отпирания ключа 15 на время, в течение которого блок 6 осуществляет поиск переполнившегося канала. Следовательно, вносимая элементом 14 задержка зависит от быстродействия блока 6 и может быть задана как т,з S N г (Т - период следования тактовых импульсов внутреннего тактового генератора блока 6), ,

В качестве многоразрядного ключа 15 могут быть использованы либо многоканальные коммутаторы типа 176 КТ1 и 561 КТЗ, либо группа элементов 2И, одни входы которых объединены и составляют вход разрешения ключа, а другие входы служат информационными входами.

Технико-экономическая эффективность устройства по сравнению с прототипом состоит в снижении аппаратурного объема за счет исключения из его состава одного из двух многоканальных блоков корреляции, являющихся наиболее емкими узлами устройства (в устройстве-прототипе, исключенный блок показан как блок 10).

Формула изобретения Корреляционное устройство, содержащее регистр сдвига, группу счетчиков, группу элементов И, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ, группу регистров сдвига, элемент ИЛИ, синхронизатор, элемент И и блок формирования кода задержки, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены с выходом элемента НЕ, вход которого является первым информационным входом устройства, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены с соответствующими разрядными выходами регистра сдвига, первый вход элемента ИЛИ соединен с обнуляющим входом блока формирования кода задержки и является обнуляющим входом устройства, выходы

элементов И группы соединены со счетными входами соответствующих счетчиков группы, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены с первыми входами

элементов И группы, вторые входы которых соединены с выходом синхронизатора, вход запуска которого является выходом запуска устройства, тактовые входы регистров сдвига группы объединены и подключены к первому тактовому входу устройства, отличающееся тем, что, с целью упрощения, в него введены мультиплексор, коммутатор, триггер, элемент задержки и ключ, выход которого является информационным выходом устройства, вторым информационным входом которого является информационный вход первого регистра сдвига группы, (N-1)- й разрядный выход j-ro регистра сдвига группы соединен с одноименным информационным входом мультиплексора (i 1.N-1: N - число каналов мультиплексора), выход j-ro регистра сдвига группы (j 1.N-2) соединен с информационным входом (j+1)-ro регистра сдвига группы, нулевой

информационный вход мультиплексора соединен с входом опорного сигнала устройства, выход мультиплексора соединен с информационным входом регистра сдвига, тактовый вход которого соединен с выходом

коммутатора, первый и второй информационные входы которого являются соответственно первым и вторым тактовыми входами устройства, управляющий вход коммутатора объединен с первым входом элемента И

и подключен к прямому выходу триггера, тактовый вход которого объединен с входом останова синхронизатора и подключен к выходу начала работы блока формирования кода задержки, выход окончания работы

которого соединен с вторым входом элемента И, выход которого соединен с вторым входом элемента И, выход которого соединен с вторым входом элемента ИЛИ, инверсный выход триггера через элемент

задержки соединен с управляющим входом ключа, информационный вход которого объединен с адресным входом мультиплексора и подключен к информационному выходу блока формирования кода задержки, информационные входы которого соединен с выходами переполнения соответствующих счетчиков, группы, обнуляющие входы регистра сдвига и триггера подключены к обнуляющему входу устройства, выход элемента

ИЛИ соединен с обнуляющими входами счетчиков группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОДНОКАНАЛЬНЫЙ КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ЧАСТОТНЫХ ИСКАЖЕНИЙ | 2009 |

|

RU2393491C2 |

| Корреляционное устройство для измерения времени задержки | 1990 |

|

SU1795474A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| Устройство приема шумоподобных сигналов | 1987 |

|

SU1663772A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для формирования порядковых статистик | 1984 |

|

SU1196897A1 |

| Устройство для индикации | 1985 |

|

SU1261005A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

Изобретение относится к специализированным устройствам извлечения информации и служит для определения времени задержки между случайными сигналами. Цель изобретения - упрощение устройства. Устройство содержит регистр 1 сдвига, группу счетчиков 2, группу элементов И 3, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4, элемент НЕ 5, блок 6 формирования кода задержки, синхронизатор 7, триггер 8, группу регистров 9 сдвига, N-канальный мультиплексор 10, коммутатор 11, элемент ИЛИ 12, элемент И 13, элемент 14 задержки и ключ 15. 2 ил.

| Корреляционное устройство для определения задержки | 1982 |

|

SU1051545A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Авторское свидетельство СССР № 1546995, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-05-15—Публикация

1991-01-02—Подача