ции содержит первый и второй элементы сравнения, первый, второй и третий элементы НЕ, первый и второй элементы И, входы которых являются соответственно первыми вторьм выходами блока, первые входы первого и второго элементов И объединены и являются первым управляющим входом блока, вторые входы первого и второго элементов И объединены и подключены к выходу первого элемента НЕ, вход которого является вторым управляющим входом блока, третьи входы первого и второго, элементов И объединены с входами

второго и третьего элементов НЕ соответственно и подключены соответственно к выходам второго и третьего элементов НЕ, выходы которых соединены соответственно с четвертыми входами первого и второго элементов И, первые входы первого и второго элементов сравнения объединены и являются первым информационным входом блока, а вторые входы первого и второго элементов сравнения являются соответственно вторым и третьим информационн1л ми входами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Корреляционное устройство дляОпРЕдЕлЕНия зАдЕРжКи | 1979 |

|

SU849226A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Корреляционное устройство для определения времени задержки | 1980 |

|

SU883914A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Устройство для тактовой синхронизации | 1989 |

|

SU1642591A1 |

| Функциональный генератор напряжения | 1976 |

|

SU610129A1 |

| Устройство для коррекции шкалы времени | 1990 |

|

SU1709268A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

1. КОРРЕЛЯЦИОННОЕ УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗАДЕРЖКИ, содержащее генератор тактовых импульсов, выход которого соединен с информационным входом управляемого делителя частоты, управляющие входы которого соединены с соответствующими выходами группы старших разрядов реверсивного счетчика, первый и второй регистры сдвига, информационный вход первого регистра сдвига является первым входом устройства, отличающееся тем, что, с целью повышения точночти, в устройст.во введены счетчик тактов, два дешифратора, блок сравнения, третий регистр сдвига, компаратор, два элемента И, элемент ИЛИ, три блока вычитания, три сумматора и блок коррекции , причем выход управляемого делителя частоты соединен с первым входом первого элемента И и счетным входом счетчика тактов, выходы разрядов которого подключены к соответствукадим входам первого и второго дешифраторов и первой группе входов блока сравнения, выход которого соединен с установочным входом счетчика тактов, входы второй группы входов блока сравнения соединены с соответствующими выходами группы младших разрядов реверсивного счетчика, вход суглмирования которого подключен к выходу элемента ИЛИ, а вход вычитания реверсивного счетчика подключен к первому выходу блока коррекции, первый управляющий вход которого объединен с первым входом второго элемента И и подключен к выходу первого дешифратора, второй выход блока коррекции соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, второй вход которого объединен с вторым управляющим входом блока коррекции и подключен к выходу компаратора, вход которого объединен с первым информационным входом блока коррекции и подключен к выходу первого сумматора, второй и третий информаi ционные вход блока коррекции подключены соответственно к выходам (П С второго и третьего сумматоров, управляющие входы первого, второго и третьего сумматоров объединены и подключены к выходу первого дешифратора, а информационные входы сумматоров подключены соответственно к выходам первого, второго и третьего блоков вычитания, первые входы которых объединены и являются вторым входом устройства, вторые входы сд первого, второго и третьего блоков вычитания подключены соответственно к выходам второго, первого и третьесл го регистров сдвига, тактовые входы 4 которых объединены и подключены к выходу первого элемента И, второй сд вход которого подключен к выходу второго дешифратора, выход первого регистра сдвига соединен с информацион HbS4 входом второго регистра сдвига, выход которого соединен с информационным входом третьего регистра сдвига, выходы группы младших разрядов i реверсивного счетчика и выход управляемого делителя частоты являются выходом устройства. 2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок коррек

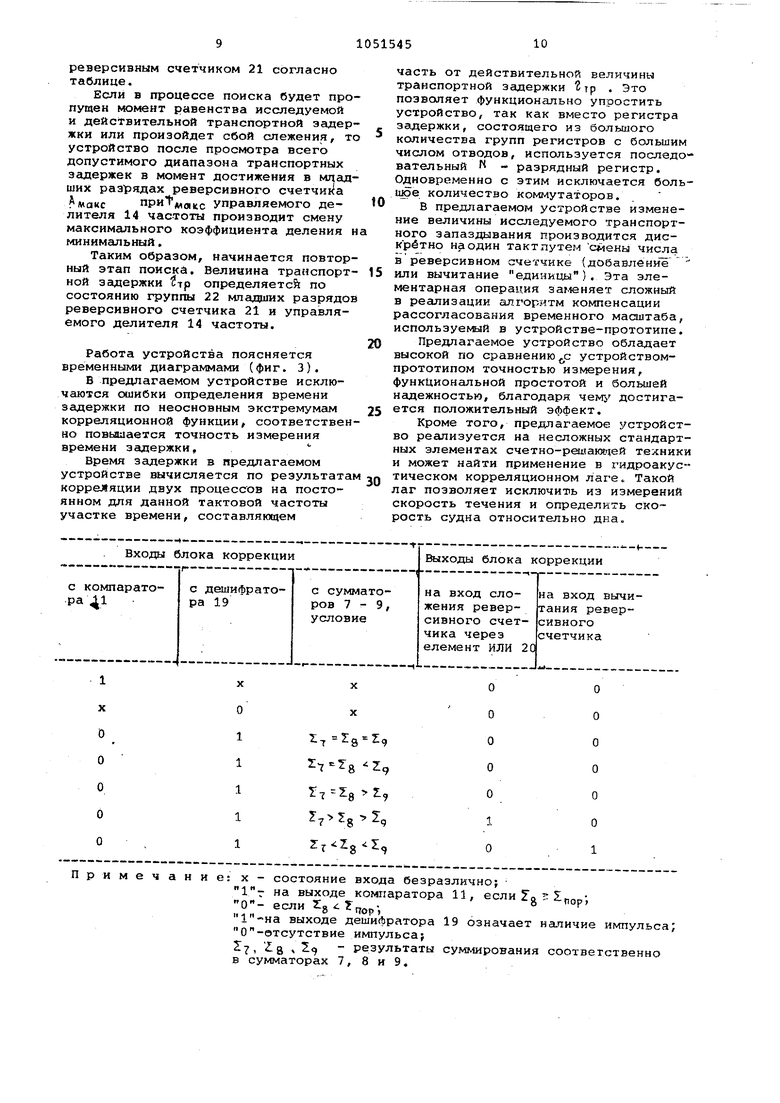

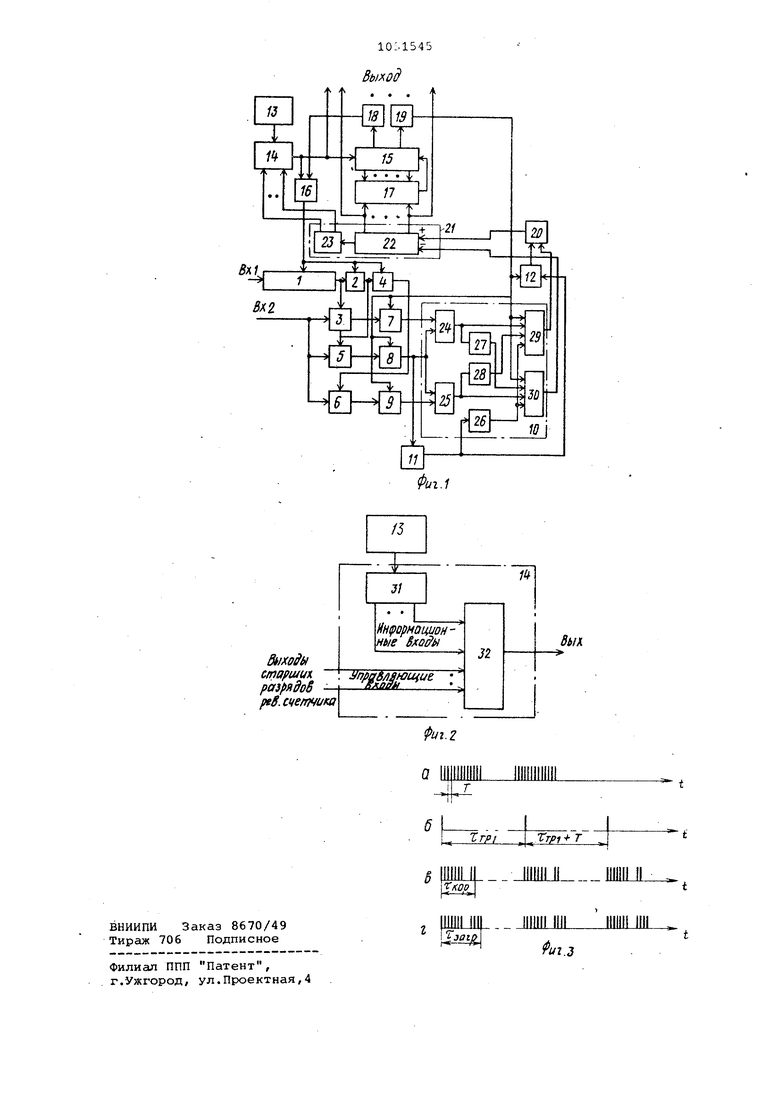

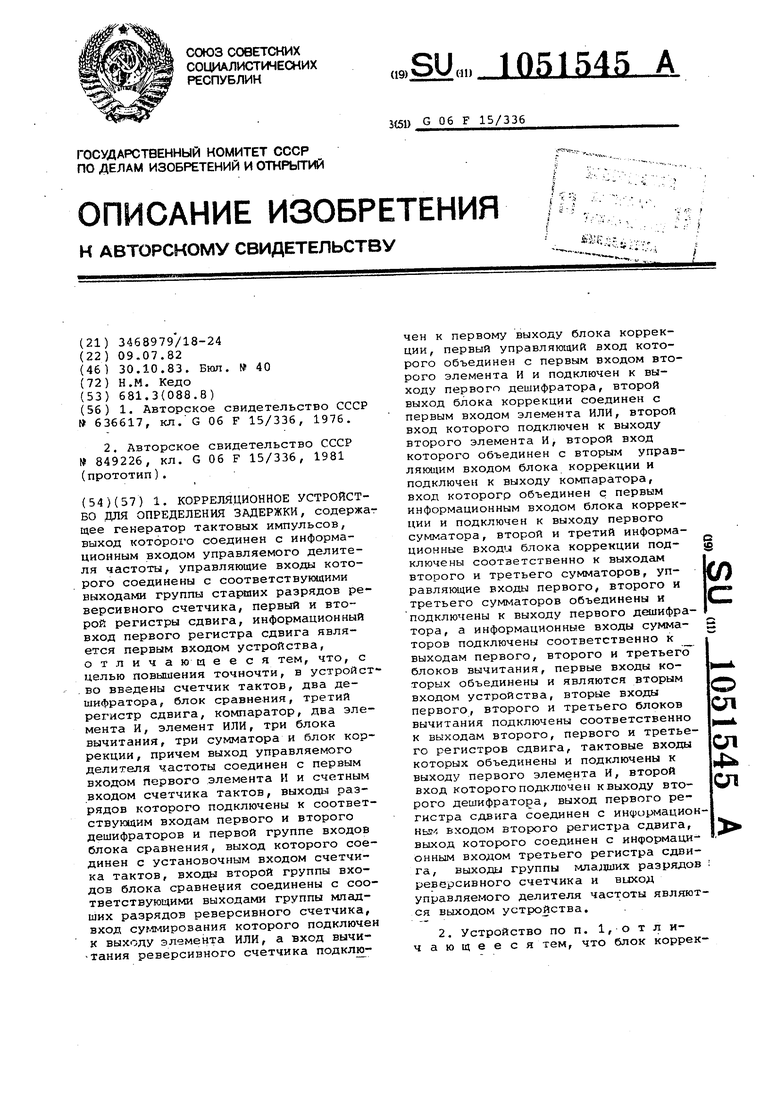

Изобретение относится к специалязированным средствам вычислительной .техники и может быть использова но для определения задержки между исходным и опорным сигналами в корр ляционных измерителях скорости .и дальномерах. Известно устройство, состоя1.цее из двух регистров сдвига, мультиплексора, преобразователя сигналчастота, реверсивного счетчика, дву делителей частоты, тактового генератора и блока индикации l . Недостатком данного устройства является невысокая точность определения задержки при сравнительно высоком быстродействии, либо низкое быстродействие при высокой точности Наиболее близким по технической сущности к предлагаемому является устройство, содержащее регистр сдви га, информационный вход которого является первым входом устройства, тактовый генератор, выход которого подключен к счетному входу делителя частоты, выход которого соединен с управляющими входами первого и второго регистров сдвига, преобразователь сигнал-частота, первый вход которого является вторым входом устройства, второй вход объединен с входом второго регистра и подключен к выходу мультиплексора, третий вход преббразователя сигнал-частота подключен к выходу второго регистра сдвига, реверсивный счетчик, выходы младших разрядов которого подключены к соответствующим установочным входам делителя частоты, а выходы старших разрядов соединены с управляющими входами мультиплексо ра, арифметический блок, коммутатор по числу ячеек первого регистра, вх ды ка удого комглутатора соединены с соответствующими разрядными выходами соответствующих ячеек первого регистра сдвига, выходы коммутаторов подключены .к соответствующим входам мультиплексора, блок управления, входы которого подключены соответственно к первому и второму выходам преобразователя сигналчастота и выходу делителя частоты, а первый и второй выходы блока управления, подключены к соответствующим входам реверсивного счетчика, третий выход соединен с управляющими входами коммутаторов и входом арифметического блока, другие входы которого подключены соответственно к выходам младших и старших .разрядов реверсивного счетчика 2j , Данное устройство благодаря использованию коммутаторов для последовательного подключения коммутируемых разрядов в каждой из групп регистра задержки к входам мультиплексора позволяет компенсировать временное рассогласование, возникающее в момент смены тактовой частоты. Это дает возможность совместить в устройстве быстродействие и точность измерения в широком интервале временных задержек. Однако, эта точность снижается Б случае, если форма корреляционной кривой имеет колебательный характер, т. е, имеет несколько экстремумов. Для определения времени задержки необходимо отыскание макси- . мального экстремума корреляционной функции. I Кроме того, данное устройство является сравнительно сложным, реализация его требует большого количества элементов. Наличие в каждой Из групп первого регистра коммутируемых разрядов влечет за собой ИспользоваНие регистров с большим количеством выводов. Так как разрядность выпускаемых промьшшенностью регистров, имеющих выводы с каждого азряда, невелика из-за ограниченного числа выводов, регшизация регистра задержки в устройстве-прототипе требует большого количества корпусо интегральных,микросхем. Подобная задача возникает и с коммутаторами, При большом количест ве коммутируемых разрядов необходимо использовать двухъярусное включение коммутаторов. В основном эти факторы определяю габариты, потребление, сложность проектирования и изготовления.данно го устройства. Еще более сложным становится устройство, когда его входные сигналы имеют многоуровнево квантование. В этом случае регистр и коммутаторы должны оперировать с многоразрядным кодом, соответственно, увеличивается объем и функциона льная сложность устройства. Большое количество узлов и элементов устройства приводит к снижению его надежности. Цель изобретения - повышение изм рения и надежности устройства, а также функциональное упрощение его схемы. Поставленная цель достигается тем, что в корреляционное устройст для определения задержки, содержаще генератор тактовых импульсов, выход которого соединен с информационным входом управляемого делителя частоты , управляющие входы которого соединены с соответствующими выходами группы старших разрядов реверсивног счетчика, первый и второй регистры сдвига, информационный вход первого регистра сдвига является первым вхо дом устройства, введены счетчик так тов, два дешифратора, блок сравнения, третий регистр сдвига, компара тор, два элемента И, элемент ИЛИ, три блока вычитания, три сумматора и блох коррекции, причем выход управляемого делителя частоты соединен с первым входом первого элемента И и счетным входом счетчика тактов, выходы разрядов которого подключены к соответствующим входам первого и второго дешифраторов и пе вой группе входов блока сравнения, выход которого соединен с установочным входом счетчика тактов, входы второй группы входов блока сравнения соединены с соответствующими выходами группы младших разрядов реверсивного счетчика, вход суммирования которого подключен к выходу элемента ИЛИ, а вход вычитания реверсивного счетчика подключен к первому выходу блока коррекции, первый управляющий вход которого объединен с первым входом второго элемента И и подключен к выходу первого дешифратора, второй выход блока коррекции соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, второй вход которого объединен с вторым управляющим входом блока коррекции и подключен к выходу компаратора, вход которого объединен с первым информационным входом блока коррекции и подключен к выходу первого сумматора, второй и третий информационные входы блока коррекции подключены соответственно к выходам второго и третьего сумматоров, управляющие входы первого, второго и. третьего сумматоров объединены и подключены к выходу первого дешифратора, а информационные входы сумматоров подключены соответственно к выходам первого, второго и третьего блоков вычитания, первые входы которых объединены и являются вторым входом устройства, вторые входы первого, второго и третьего блоков вычитания подключены соответственно к выходам второго, первого и третьего регистров сдвига, тактовые входы которых объединены и подключены к выходу первого элемента И, второй вход которого подключен к выходу второго дешифратора, выход первого регистра сдвига соединен с информационным входом второго регистра сдвига, выход которого соединен с информационным входом Третьего регистра сдвига, выходы группы младших разрядов реверсивного счетчика и выход управляемого делителя частоты являются выходом устройства. Кроме того, блок коррекции содержит первый и второй элементы срав- . нения, первый, второй и третий элементы НЕ, первый и второй элементы И, выходы которых являются соответственно первым и вторым выходами блока, первые входы первого и второго элементов И объединены и являются первым управляющим входом блока, вторые входы первого и второго элементов И объединены и подключены к выходу первого элемента НЕ, вход которого является вторым управляквдим входом блока, третьи входы первого и второго элементов И объединены с входами второго и третьего элементов НЕ соответственно и подключены соответственно к выходам второго и третьего элементов НЕ, выходы которых соединены соответственно с четвертыми входами первого и второго элементов И, nepi.вые входы первого и второго элементов сравнения объединены и являются первым информационным входом блока, а вторые входы первого и второго элементов сравнения являются соответственно вторым и третьим информационными входами блока. На фиг. 1 представлена блок-схема устройства на фиг. 2 - блок-схема управляемого делителя частоты; на фиг. 3 - диаграммы работы устройств Первый вход устройства (фиг. 1) соединен с информационным входом регистра 1 сдвига, выход регистра 1 Соединен с информационным входом регистра 2 и соответствугацим входом блока 3 вычитания, выход регистра 2 соединен с информационн(з1м входом регистра 4 и соответствующим входом блока 5 вычитания, выход регистра 4 соединен с соответствующим входом блока б вычитания; второй вход устройства соех1инен с другими входами блоков 3, 5 и 6 вычитания, выходы которых подключены к информационным входам соответствующих сумматоров 7-9, соответствующий управляющий вход блока 10 коррекгхии подключен к выходу компаратора 11,. вход которого соединен с выходом сумматора 8, пер вый вход элемента И 12 соединен с другим управляющим входом блока 10 и управляющими входами сумматоров 7 - 9, второй вход элемента И 12 подключен к выходу компаратора 11, Бь-лход генератора 13 тактовых импуль сов соединен с информационным входом управляемого делителя 14 частоты, выход которого подключен к счетному входу счетчика 15 тактов и первому входу элемента И 16, В:т1ходы разрядов счетчика 15 тактов соединены с первой группой входов блока сравнения, с входами дешифраторов 1 и 19, выход деп.тифратора 19 соединен с первым входом элемента И 12; выход элемента ИЛИ 20 соединен с входо сложения реверсивного счетчика 21, вход вычитания которого подключен к первому выходу блока 10 коррекции второй выход которого соединен с первым входом элемента ИЛИ 20, второй вход которого подключен к выходу элемента И 12, первый, второй и третий информационные входы блока 10 коррекции подключены соответственно к выходам сумматоров 8, 7 и 9, выход старшего разряда из группы 22 младишх разрядов реверсивного счетчика 21 соединен с счетным входом .группы 23 старших разрядов реверсивного счетчика 21 соединены с соответ ствующими входами второй группы входов блока 17 сравнения, выход которого сое&инен с установочным входом счетчика 15 тактов, выходы группы 2 старших разрядов реверсивного счетчика 21 подключены к соответствующим управляющим входам управляемого делителя 14 частоты, выход которого, а также выходы группы 22-младших раз рядов реверсивного счетчика 21 являются выходом устройства. Блок 10 коррекции содержит элементы 24 и 25 сравнения, элементы НЕ 26 - 28, элементы И 29 и 30. Управляемьтй делитель 14 частоты (фиг. 2) содержит делитель 31 частоты и мультиплексор 32. Устройство работает следующим образом. В момент включения производится начальная установка блоков: обнуляются счетчик 15 тактов, группа 23 старших разрядов реверсивного счетчика 21, задающих коэффициенты деления управляемого делителя (нулевое состояние старших разрядов реверсивного счетчика задает минимальный коэффициент деления управляег ого делителя, т„е. максимальную тактовую частоту на выходе делителя). В группе 22 младших разрядов реверсивного счетчика 21 устанавливается число / определяющее при минимальной длительности тактов (минимальном коэффициенте деления управляемого делителя 14 частоты) нижнюю границу измеряемой транспортной задержки L-rp мин Так, например, если в младшие разряды реверсивного счетчика записано число 300, а период тактовой частоты на выходе управляемого делителя 14 частотыТ 2 мкс ( F 500 кГц), то измеряемая транспортная задержка равна 600 мкс, что соответствует в реализованном макете корреляционногоустройства скорости объекта порядка 50 узлов, С минимального значения транспортной задержки . начинается поиск действительной величины транспортного запаздывания. Последовательность импульсов с генератора 13 тактовых импульсов, поделенная в управляемом делителе 14 частоты, поступает на счетчик 15 тактов н через элемент И 16 - на регистры 1,, 2 и 4 сдвига. На входы устройства поступают значения квантованных по уровню сигналов, сдвинутых между собой по времени на величину транспортного запаздывания. По каж,цому такту блоки 3, 5 и 6 вычитания производят вычисление; абсолютных значений разности величин, поступающих с выходов регистров 1,, 2 и 4 и входа устройства. Абсолютные значения разностей на каждом такте суммируются в соответствующих сумматорах 7-9. Процесс суммирования в сум1иаторах производится в течение N тактов, где N - число разрядов регистра 1 сдвига. Одновременно с этим производится заполнение регистров 1, 2 и 4 сдвига новой информацией, которая используется, в операциях следующего цикла вычислений, Интервал в N тактов является интервалом корреляции, моменту в N тактов соответствует выходной импульс дешиф ратора 19. Если в конце интервала корреляции число в cyNiMaTope 8 превышает заданный пороговый уровень, то выходной сигнал компаратора 11 разрешает прохождение импульса с дешифратора 19 через элемент И 12, элемент ИЛИ 20 на вход сложения реверсивного счетчика 21. В компарато 11 число с выхода сумматора 8 сравн вается с порогом. Абсолютные величи ны разности, определяемые блоками 3, 5 и б вычитания, характеризуют степень корреляции процессов на их входах. Чем меньше абсолютная велич на разности, тем ближе по величине сравниваемые значения. Следовательн чем меньше результаты суммирования сумматорах, тем сильнее коррелирова исследуемые процессы. Таким образом, превышение порога результатом суммирования в сумматор ;8 означает недостаточную степень коррелированности процессов, т. е. несоответствие значения исследуемой задержки действительному времени транспортного запаздывания. Импульс, поступивший на вход сложения реверсивного счетчика 21, увеличивает его содержимое на единицу, или исследуемое значение тран спортной задержки ир на один такт По заднему фронту сигнала с дешифра тора 19 производится обнуление сумм торов 7 - 9. В течение времени корр ляции Н тактов) новой информацией заполняется только регистр 1 сдвига Для смены информации во всех трех регистрах сдвига требуется время загрузки - , равное N +2 тактам. Регистры 2 и 4 сдвига - одноразрядные. Это обеспечивает измерен с точностью до одного такта. Дешифратор 18 фиксирует момент, рав ный времени зaгDvзки оегистоов (N +2VT и закрывает прохож дение тактовой последовательности через элемент И 16 на регистры 1, 2 и 4сдвига Т - период следования тактовых импульсов) . Таким образом, записанная в регистры информация запоминается до момента нового поступления тактов через элемент И 16. Такты с управля емого делителя 14 частоты продолжают отсчитываться в счетчике 15 тактов. В момент достижения в нем числ равного хранящемуся в группе 22 младших разрядов реверсивного счетчика 21, блок 17 сравнения вырабаты вает импульс сброса счетчика 15 так тов, вновь открывается для прохождения тактов элемент И 16 и вышеописанный процесс продолжается для исследования нового значения стр, увеличенного на один такт частоты следования тактовых импульсов с управляеМого делителя 14 частоты. Если время транспортной задержки лежит в области довольно больших величин, то в процессе добавления в группе 22 младших разрядов реверсив ного счетчика 21 происходит переполнение АЛЛИНГ импульс переполнения с группы 22 младших разрядов реверсивного счетчина меняет состояние группы 23 старших разрядов реверсивного счетчика, определяющее коэффициент деления управляемого делителя. Благодаря этому увеличивается вдвое иерио7а.следования тактовь,1Х импульсов с управляемого делителя Т4, при этом в группе 22 младших разрядов реверсивного счетчика вновь устанавливается число АМИН как Л wavic -2 А у,н иТ, 2 , то мо.с ;-- мин м , т, е. время tip при смене коэффициента деления в Управляемом делителе 14 частоты и замене числа А макс на Амин в младших разрядах реверсивного счетчика 21 не изменяется. Это обеспечивает непрерывность исследования времени транспортной задержки. В области, где значение исследуемого времени задержки приближается к действительному времени транспортной задержки, абсолютные значения разностей па выходах блоков 3, 5 и 6 вычитания уменьшаются, соответственно, уменьшаются значения сумм в сумматорах 7-9 к(моменту сравнения моменту окончания интервала корреляции). В процессе исследования наступает момент, когда значение суммы в сумматоре 8 за интервал корреляции не достигает заданного порога порогового уровня (признак хорошей коррелируемости процессов). В этом случае устройство переходит из режима поиска в режим слежения. Значение порогового уровня (в частном случае для реализованного стройства)определяется величиной боковых выбросов корреляционной функции. Таким образом, назначение порогового уровня отрезать боковые выбросы корреляционной функции, чтобы исключить возможность Определения транспортной задержк Ctp по неосновному экстремуму, следовательно, порог определяет лишь нижнюю границу области значений корреляционной функции, в которой отыскивается ее максимум. Сигнал с компаратора 11 закрывает элемент И 12 и включает в работу блок 10 корреляции, который по сигналам окончания интервала корреляции с дешифратора 19 вырабатывает сигнал сложения или вычитания в реверсивный счетчик,21, приближая тем самым значение исследуемого времени задержки к действительноьту траЕ:спорТ ному запаздыванию тр Блок 10 коррекции вырабатывает на своем выходе в режиме слежения (при наличии соответствующего сигнала с компаратора) сигналы управ1 ния

реверсивным счетчиком 21 согласно таблице.

Если в процессе поиска будет пропущен момент равенства исследуемой и действительной транспортной задержки или произойдет сбой слежения, то устройство после просмотра всего допустимого диапазона транспортных задержек в момент достижения в мдадших разрядах реверсивного счетчи а Л макс npHljMffluc управляемого делителя 14 частоты производит смену максимального коэффициента деления н минимальный.

Таким образом, начинается повторный этап поиска. Велинина транспортной задержки тр определяете по состоянию атруппы 22 младших разрядов реверсивного счетчика 21 и управляемого делителя 14 частоты.

Работа устройства поясняется временными диаграммами (фиг. 3).

В предлагаемом устройстве исключаются ошибки определения времени задержки по неосновным экстремумам корреляционной функции, соответственно повышается точность измерения времени задержки.

Время задержки в предлагаемом устройстве вычисляется по результата корреляции двух процессов на постоянном для данной тактовой частоты участке времени, составляющем Примечани

часть от действительной величины транспортной задержки тр . Это позволяет функционально упростить устройство, так как вместо регистра задержки, состоящего из бoльцJOГo количества групп регистров с большим числом отводов, используется последовательный - разрядный регистр. Одновременно с этим исключается больцюе количество коммутаторов.

В предлагаемом устройстве изменение величины исследуемого транспортного запаздывания производится дискретно на один тактлутем смены числа

вреверсивном счетчике (добайлениё или вычитание единицы). Эта элементарная операция заменяет сложный в реализации алгоритм компенсации рассогласования временного масштаба, используе1Фгй в устройстве-прототипе.

Предлагаемое устройство облгщает высокой по сравнению j,c устройствомпрототипом точностью измерения, функциональной простотой и большей надежностью, благодаря 4eNry достигается положительный эффект,

Кроме того, предлагаемое устройство реализуется на несложных стандартных элементах счетно-релшюгцей техники и может найти применение в гидроакустическом корреляционном лаге. Такой лаг позволяет исключить из измерений скорость течения и определить скорость судна относительно дна. е: х- состояние входа безразлично; на выходе компаратора 11, если о г 1г,„п, если °Р выходе дешифратора 19 означает наличие импульса; О -отсутствие импульса; 7, 8 9 результаты суммирования соответственно в сумматорах 7, 8 и 9.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Корреляционное устройство для определения задержки | 1976 |

|

SU636617A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Корреляционное устройство дляОпРЕдЕлЕНия зАдЕРжКи | 1979 |

|

SU849226A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-10-30—Публикация

1982-07-09—Подача