Перезапись

ю

о

О5

сд

Изобретение относится к приборостроению, а именно к технике магнитной записи.

Цель изобретения - сокращение времени контроля с поканальным анализом ошибок.

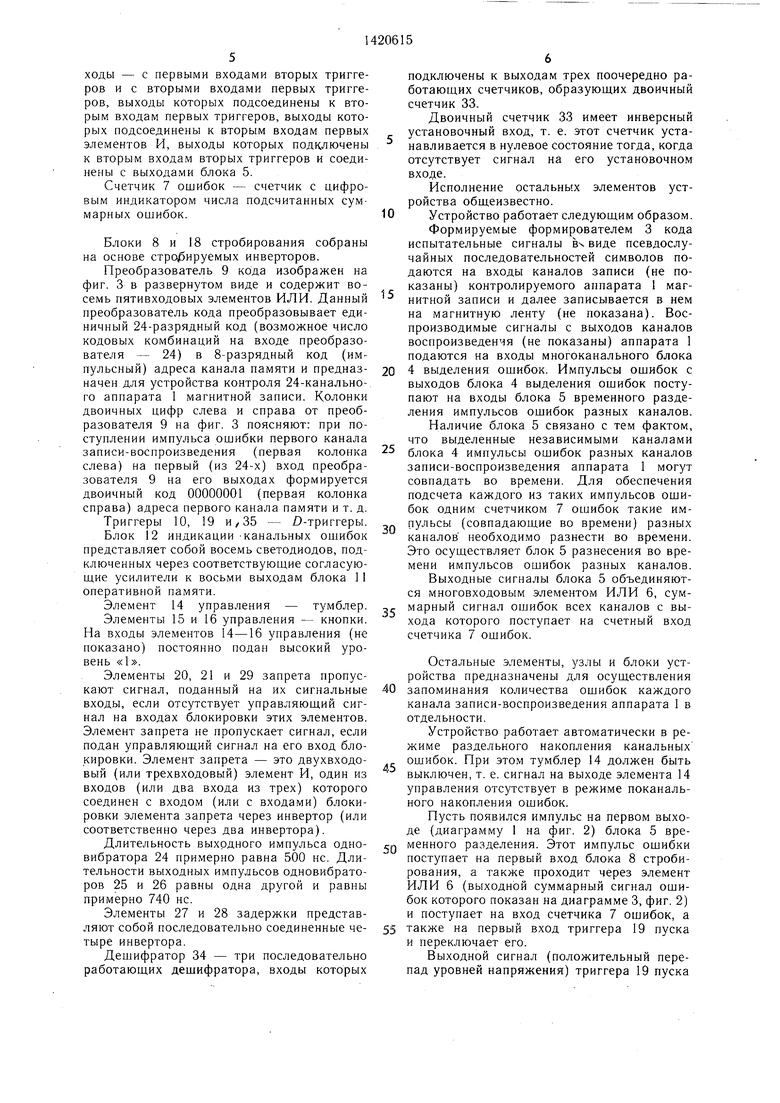

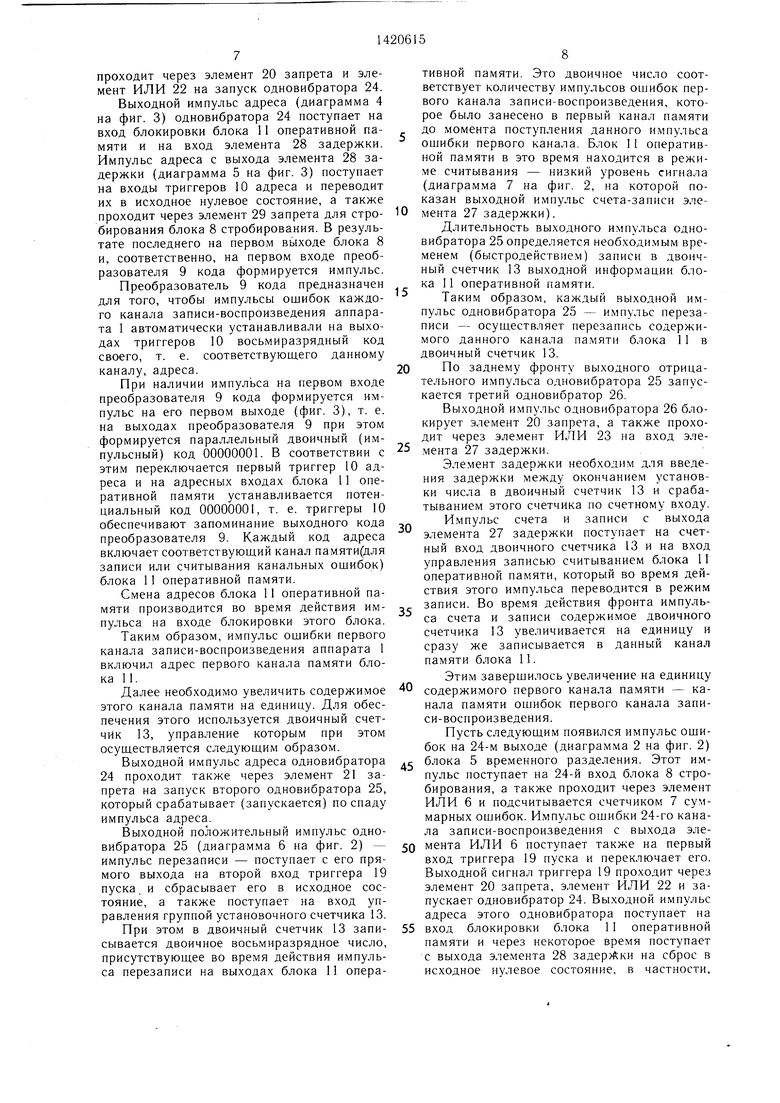

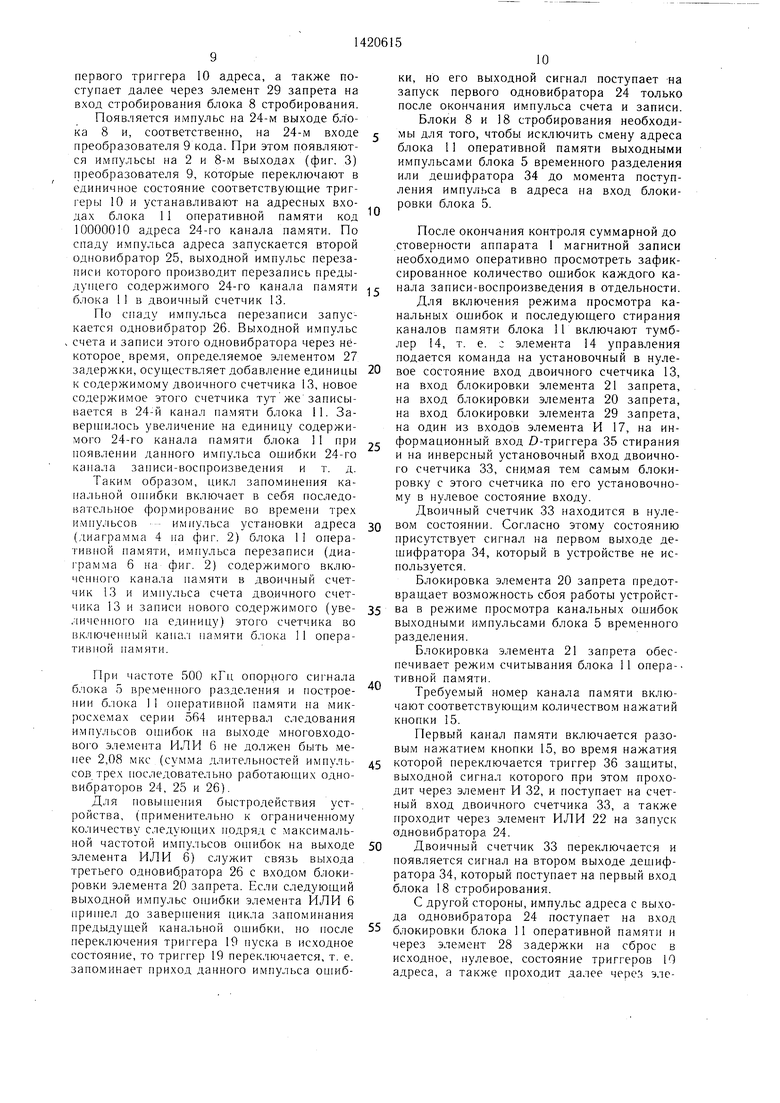

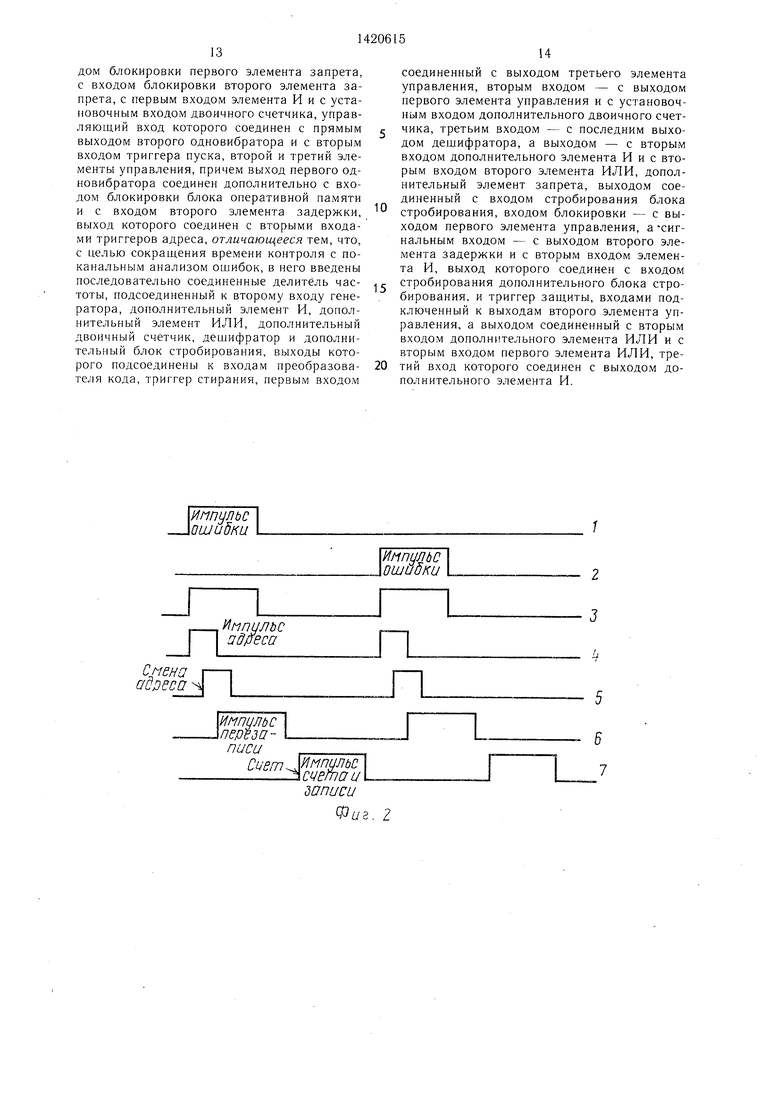

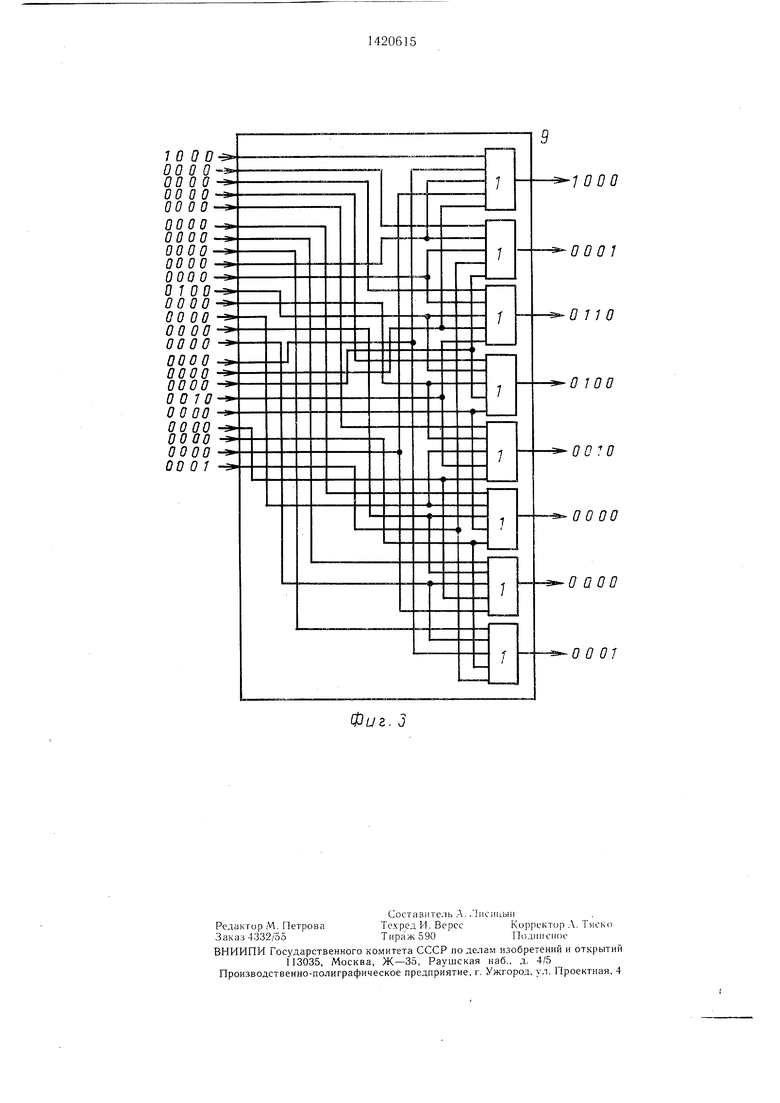

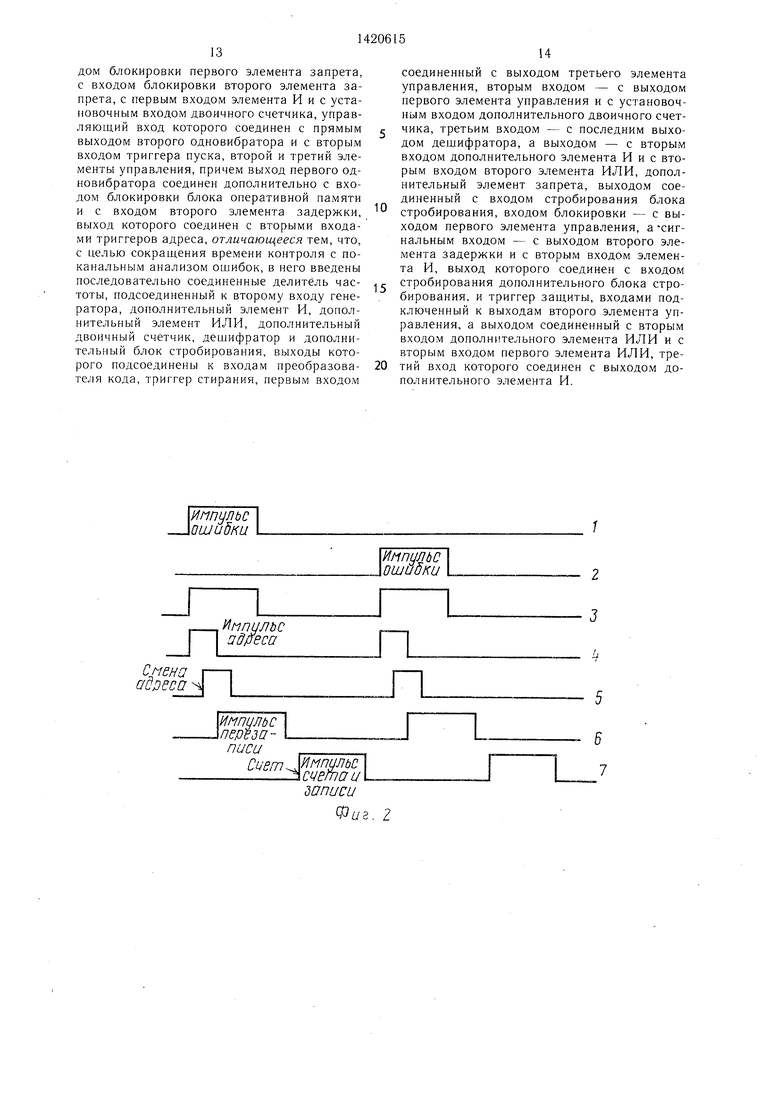

На фиг. 1 изображена функциональ- ная схема устройства; на фиг. 2 - временные диаграммы, иллюстрирующие принцип его работы; на фиг. 3 - преобразователь кода устройства в развернутом виде, вариант исполнения.

Устройство для контроля ошибок много- канального аппарата 1 магнитной записи содержит генератор 2, формирователь 3 кода, многоканальный блок 4 выделения ошибок, блок 5 временного разде.тения (ошибок разных каналов), многовходовый эле- мент ИЛИ 6, счетчик 7 ошибок, первый блок 8 стробирования, преобразователь 9 кода, триггеры 10 адреса, блок 11 оперативной па.мяти, блок 2 индикации (канальных ), первый двоичный счетчик 13, первый 14, второй 15 и третий 16 эле- менты управления, первый элемент И 17, второй (дополнительный) блок 18 стробирования, триггер 19 пуска, первый 20 и вто - рой 21 элементы запрета, первый 22 и второй 23 элементы ИЛИ, первый 24, второй 25, третий 26 одновибраторы, первый 27 и второй 28 элементы задержки, третий (дополнительный) элемент 29 запрета, делитель 30 частоты, второй (дополнительный) элемент И 31, третий (дополнительный) элемент И 32, второй (дополнительный) двоичный счетчик 33, дешифратор 34, триггер 35 стирания и триггер 36 зап1иты.

На фиг. 1 штриховой линией показан блок 27 индикации номера канала памяти, который может быть подключен к выходам депшфратора 34, но который не является пеобходиг«1ым элементом для устройства.

Первый выход (низкочастотный) генератора 2 соединен с входом тактового сигнала формирователя 3 кода, выходы которого подключены к входам каналов записи аппарата 1 магнитной записи, к выходам каналов воспроизведения которого подключены входы многоканального блока 4 выделения ошибок.

Выходы блока 4 выделения 01пибок соединены с входами блока 5 временного разделения, вход опорного сигнала которого соединен с вторым выходом (высокочастотным) генератора 2 и с входом делителя 30 частоты. Выходы блока 5 временного разделения соединены с входами многовходового элемента ИЛИ 6 и с сигнальными входами блока 8 стробировапия. Выход многовходового элемента ИЛИ 6 соединен со счетным входом счетчика 7 ошибок и с первым входом (тактирующим входом С) D-триггера 19 пуска. На информационный вход D этого три тера постоянно подан высокий уровень напряжения «1,(эта связь не показана). Выход триггера 19 пуска соединен с сигнальным входом элемента 20 запрета, выход

5

0 0

0

5

0

5

5

0

которого соединен с первым входом элемента ИЛИ 22,, выход которого соединен с входом одновибратора 24, выход которого соединен с входом блокировки блока 11 оперативной памяти, с входом элемента 28 задержки с сигнальным входом элемента 21 запрета, инверсный выход которого соединен с входом одновибратора 25, инверсный выход которого соединен с входом одновибратора 26, выход которого соединен с вторым входом блокировки элемента 20 запрета и с первым входом элемента ИЛИ 23, выход которого соединен с входом элемента 27 задержки, выход которого соединен со счетным входом двоичного счетчика 13 и с входом управления записью-считыванием блока 11 оперативной памяти. Нрямой выход одновибратора 25 соединен с вторым (установочным в нулевое состояние) входом триггера 19 пуска и с входом управления группой установочных входов двоичного счетчика 13. Выходы блока 8 стробирования соединены соответственно с выходами блока 18 стробирования и с входами преобразователя 9 кода, выходы которого соединены с первыми (установочными в единичное состояние) входами D-триггеров 10 адреса, единичные выходы которых соединены с адресными входами блока 11 оперативной памяти. Выход элемента 28 задержки соедиь ен с входом блокировки элемента 29 запрета, с вторым входом элемента И 17 и с вторыми (тактирующими) входами С триггеров 10 адреса. На информационные входы D-триггеров 10 адреса постоянно подан низкий уровень напряжения «О (эта связь не показана). Выход делителя 30 частоты соединен с первым входом элемента И 31, выход которого соединен с третьим входом элемента ИЛИ 22 и с первым входом элемента И 32, выход которого соединен со счетным входом двоичного счетчика 33, выходы разрядов которого соединены с входами дешифратора 34, выходы которого от второго и до предпоследнего соединены с сигнальными входами блока 18 стробирования. Первый выход дешифратора 34 в устройстве не используется. Выход элемента 16 управления соединен с первым (тактирующим) входом С D-триггера 35 стирания, выход которого соединен с вторым входом элемента ИЛИ 23 и с вторым входом элемента И 31. Выход элемента 14 управления соединен с вторым входом блокировки элемента 20 запрета, с входом блокировки элемента 21 запрета, с входом установки в нулевое состояние двоичного счетчика 13, с вторым (информационным) входом D-триггера 35 стирания, с инверсны.м установочны.м в нулевое состояние входом двоичного счетчика 33, с входом блокировки элемента 29 запрета, выход которого соединен с входом стробирования блока 8 стробирования, и с первым входом элеглента И 17, выход которого соединен с входом стробирования блока 18 стробирования. Выходы элемента 15 управления соединены с установочными входами триггера 36 зашиты, выход которого соединен с вторым входом элемента ИЛИ 22 и с вторым входом элемента И 32. Выходы блока 11 оперативной памяти соединены с входами блока 12 индикации канальных О пибок и с группой установочных входов двоичного счетчика 13, выходы которого соединены с информационными входами блока 1 1 оперативной памяти.

Последний выход дешифратора 34 соединен с установочным в нулевое состояние входом триггера 35 стирания. К выходам дешифратора 34 может быть подключен блок 37 индикации но.мера канальной памяти.

Конкретное исполнение отдельных узлов и блоков предлагаемого устройства следующее.

Генератор 2 содержит собственной типовой автогенератор непрерывной последовательности импульсов с частотой 500 кГц и включенный на его выходе управляемый по скоростям (в соответствии с рабочей скоростью движения магнитного носителя контролируемого аппарата 1 .магнитной записи) делитель частоты. Сигнал с выхода управляемого делителя частоты (первый выход генератора 2) в качестве тактового сигнала записи с соответствующей частотой поступает на вход формирователя 3 кода. Сигнал высокой частоты (500 кГц) непосредственно с выхода автогенератора (второй выход 1 енератора 2) поступает на вход опорного сигнала блока 5 временного разделения и па вход делителя 30 частоты.

Формирователь 3 кода формирует пока- нально испытательный сигнал в виде псевдослучайной последовательности символов известным путем на основе регистра сдвига, охваченного логической обратной связью через сумматор по модулю два. Псевдослучайный сигнал с выхода регистра сдвига в форме БВН (без возвращения к нулю) сиг- пала (в сигнале БВН «О соответствует низкий уровень, а «1 - высокий уровень напряжения) совместно с тактовым сигналом записи подается (при необходимости - через согласующие устройства) на вход каждого капала записи-воспроизведения контролируемого аппарата 1.

Каждый канал записи аппарата 1 содержит преобразователь сигнала БВН в сигнал с относительной фазовой манипуляцией прямоугольной несундей (сигнал ОФМ) и формирователь тока записи сигнала БВН способом «без возврашения к нулю. Запись сигналов производится многодоро- жечны.м блоко.м магнитных головок записи на магнитную ;1енту. Запись классифицируется как последовательная или асипхронная, поскольку каналы записи между собой (и каналы воспроизведения между собой) в аппарате 1 не связаны. Каждый капал воспроизведения аппарата I содержит магнитную головку воспропзведения (объединены в

многодоро;- ;ечио.м б.юке ма1 нитн1 1х го.юнок воспроизведения, ам11. 1иту.1но-часто1ч;ы1 | п фазочастотный корректоры, формнровате. и. прямоугольного ОФ.М сигнала воспронзведе- с ния, синхронизатор и демодулятор сигнала ОФМ, осуп1ествляю1ций преобразование сигнала ОФМ в БВН. С выхода каждого канала воспроизведения аппарата 1 воспроизведенный испытательный сигнал п

0

форме БВН и тактовый синхросигнал это|-о

же канала подаются в многокана.чьныи о. юк 4 на вход отдельного кана.па ,тения ошибок.

Многоканальный блок 4 выделения оп1и- бок содержит капал1а1 выделения ошибок н

5 количестве, равном чиелу каналов записи- воспроизведения контролируемого аппарата 1. Каждый канал выделения опшбок содержит на входе регистр сдвига с соответ- ствуюп1ими кодообразуюшему регистру сдвига фор.мировате,тя 3 кода отводами, которые

0 через первый сумматор по модулю два связаны с первым входом второго сумматора по модулю два, второй вход которого соединеп с информационным входо.м регистра сдвига и с информационным выходом канала вое5 произведения. Синхросигнал воспроизведения подается на тактовый вход регистра сдвига. Описаппая схема представляет co6oii известпый детектор ошибок, работающий но принципу проверки воспроизводимой псевдослучайной пос, 1едовательности на правн.() ее

0 кодообразования в регистре сдвига занисп. При воспроизведении оп;ибочного CH.MBO.KI на выходе второго с мматора по моду, 1К) два устанавливается высокий уровень ,iorn- ческой «1. Выходной сигнал оши.бок второго сумматора по модулю два ( в форме сиг5 на,та БВН) стробируется синхроимпу, |ьсами воспроизведения на элементе стробирования, включенном между выходом второго сумматора по модулю два и выходом данного канала выделения ошибок. С выхода каждо1-о канала выделен.ия 01иибок б.юка 4 нм11у.:и, - сы ошибок иоступают отде.льный вход блока 5 временного разделения импульсов О1пибок разных каиа. юв.

Блок 5 временного разделения содержит распределитель пмпульсов, вход котог рого соедипен с входом опорного сигнала блока 5, первые триггеры - Tpnn-epi) запоминания принятых ошибок, подк,1ючен- ные первыми входам к м 1огок; - наль;{ого блока 4 вь делен 1Я О иибок, первые -э, 1ементь И - первые э,1еме1 Т1 1 опро0 са, первые входы которых г Одсоед 11 е Ь к выходам распредел1 те. 1я мпу,, вто|1ые триггеры - выданных (для счета) , а вторые э, менты И - вторые э..1е)ть оироса. На- нример, первые входы вторых элементов И

5 соедипен з1 с выходами распределителя 1М- пульеов со сдвигом относ те, соответ- ствуюпи х первых элементов И, входы - с выхода. вторых триггеров, а вы

ходы - с первыми входами вторых триггеров и с вторыми входами первых триггеров, выходы которых подсоединены к вторым входам первых триггеров, выходы которых подсоединены к вторым входам первых элементов И, выходы которых подключены к вторым входам вторых триггеров и соединены с выходами блока 5.

Счетчик 7 ошибок - счетчик с цифровым индикатором числа подсчитанных суммарных ошибок.

Блоки 8 и 18 стробирования собраны на основе стро ируемых инверторов.

Преобразователь 9 кода изображен на фиг. 3 в развернутом виде и содержит восемь пятивходовых элементов ИЛИ. Данный преобразователь кода преобразовывает единичный 24-разрядный код (возможное число кодовых комбинаций на входе преобразователя - 24) в 8-разрядный код (импульсный) адреса канала памяти и предназ- начен для устройства контроля 24-канального аппарата 1 магнитной записи. Колонки двоичных цифр слева и справа от преобразователя 9 на фиг. 3 поясняют: при поступлении импульса ошибки первого канала записи-воспроизведения (первая колонка слева) на первый (из 24-х) вход преобразователя 9 на его выходах формируется двоичный код 00000001 (первая колонка справа) адреса первого канала памяти и т. д.

Триггеры 10, 19 и / 35 - /)-триггеры.

Блок 12 индикации-канальных ошибок представляет собой восемь светодиодов, подключенных через соответствующие согласую- шие усилители к восьми выходам блока 11 Оперативной памяти.

Элемент 14 управления - тумблер.

Элементы 15 и 16 управления - кнопки. На входы элементов 14-16 управления (не показано) постоянно подан высокий уровень «1.

Элементы 20, 21 и 29 запрета пропускают сигнал, поданный на их сигнальные входы, если отсутствует управляюш,ий сигнал на входах блокировки этих элементов. Элемент запрета не пропускает сигнал, если подан управляюш.ий сигнал на его вход блокировки. Элемент запрета - это двухвходо- вый (или трехвходовый) элемент И, один из входов (или два входа из трех) которого соединен с входом (или с входами) блокировки элемента запрета через инвертор (или соответственно через два инвертора).

Длительность выходного импульса одно- вибратора 24 примерно равна 500 не. Длительности выходных импульсов одновибрато- ров 25 и 26 равны одна другой и равны примерно 740 не.

Элементы 27 и 28 задержки представляют собой последовательно соединенные че- тыре инвертора.

Дешифратор 34 - три последовательно работающих дешифратора, входы которых

5

5

0

0

5

0

5

5

0

подключены к выходам трех поочередно работающих счетчиков, образующих двоичный счетчик 33.

Двоичный счетчик 33 имеет инверсный установочный вход, т. е. этот счетчик устанавливается в нулевое состояние тогда, когда отсутствует сигнал на его установочном входе.

Исполнение остальных элементов устройства общеизвестно.

Устройство работает следующим образом.

Формируемые формирователем 3 кода испытательные сигналы в виде псевдослучайных последовательностей символов подаются на входы каналов записи (не показаны) контролируемого аппарата 1 магнитной записи и далее записывается в нем на магнитную ленту (не показана). Воспроизводимые сигналы с выходов каналов воспроизведения (не показаны) аппарата 1 подаются на входы многоканального блока 4 выделения ошибок. Импульсы ошибок с выходов блока 4 выделения ошибок поступают на входы блока 5 временного разделения импульсов ошибок разных каналов.

Наличие блока 5 связано с тем фактом, что выделенные независимыми каналами блока 4 импульсы ошибок разных каналов записи-воспроизведения аппарата 1 могут совпадать во времени. Для обеспечения подсчета каждого из таких импульсов ошибок одним счетчиком 7 ошибок такие импульсы (совпадающие во времени) разных каналов необходимо разнести во времени. Это осуществляет блок 5 разнесения во времени импульсов ощибок разных каналов.

Выходные сигналы блока 5 объединяются многовходовым элементом ИЛИ 6, суммарный сигнал ошибок всех каналов с выхода которого поступает на счетный вход счетчика 7 ошибок.

Остальные элементы, узлы и блоки устройства предназначены для осуществления запоминания количества ошибок каждого канала записи-воспроизведения аппарата 1 в отдельности.

Устройство работает автоматически в режиме раздельного накопления канальных ошибок. При этом тумблер 14 должен быть выключен, т. е. сигнал на выходе элемента 14 управления отсутствует в режиме поканаль- ного накопления ошибок.

Пусть появился импульс на первом выходе (диаграмму 1 на фиг. 2) блока 5 временного разделения. Этот импульс ошибки поступает на первый вход блока 8 стробирования, а также проходит через элемент ИЛИ 6 (выходной суммарный сигнал ошибок которого показан на диаграмме 3, фиг. 2) и поступает на вход счетчика 7 ошибок, а также на первый вход триггера 19 пуска и переключает его.

Выходной сигнал (положительный перепад уровней напряжения) триггера 19 пуска

7

проходит через элемент 20 запрета и элемент ИЛИ 22 на запуск одновибратора 24.

Выходной импульс адреса (диаграмма 4 на фиг. 3) одновибратора 24 поступает на вход блокировки блока 11 оперативной памяти и на вход элемента 28 задержки. Импульс адреса с выхода элемента 28 задержки (диаграмма 5 на фиг. 3) поступает на входы триггеров 10 адреса и переводит их в исходное нулевое состояние, а также проходит через элемент 29 запрета для стро- бирования блока 8 стробирования. В результате последнего на первом вь1ходе блока 8 и, соответственно, на первом входе преобразователя 9 кода формируется импульс.

Преобразователь 9 кода предназначен для того, чтобы импульсы ошибок каждого канала записи-воспроизведения аппарата 1 автоматически устанавливали на выходах триггеров 10 восьмиразрядный код своего, т. е. соответствующего данному каналу, адреса.

При наличии импульса на первом входе преобразователя 9 кода формируется импульс на его первом выходе (фиг. 3), т. е. на выходах преобразователя 9 при этом формируется параллельный двоичный (импульсный) код 00000001. В соответствии с этим переключается первый триггер 10 адреса и на адресных входах блока 11 оперативной памяти устанавливается потенциальный код 00000001, т. е. триггеры 10 обеспечивают запоминание выходного кода преобразователя 9. Каждый код адреса включает соответствующий канал памяти(для записи или считывания канальных ошибок) блока 11 оперативной памяти.

Смена адресов блока 11 оперативной памяти производится во время действия импульса на входе блокировки этого блока.

Таким образом, импульс ошибки первого канала записи-воспроизведения аппарата 1 включил адрес первого канала памяти блока 11.

Далее необходимо увеличить содержимое этого канала памяти на единицу. Для обеспечения этого используется двоичный счет- чИк 13, управление которым при этом осуществляется следующим образом.

Выходной импульс адреса одновибратора 24 проходит также через элемент 21 запрета на запуск второго одновибратора 25, который срабатывает (запускается) поспаду импульса адреса.

Выходной положительный импульс одно- вибратора 25 (диаграмма 6 на фиг. 2) - импульс перезаписи - поступает с его прямого выхода на второй вход триггера 19 пуска, и сбрасывает его в исходное состояние, а также поступает на вход управления группой установочного счетчика 13.

При этом в двоичный счетчик 13 записывается двоичное восьмиразрядное число, присутствующее во время действия импульса перезаписи на выходах блока 11 опера8

0

5

0

5

0

5

0

5

0

5

тивной памяти. Это двоичное число соответствует количеству импульсов ошибок первого канала записи-воспроизведения, которое было занесено в первый канал памяти до момента поступления данного импульса ошибки первого канала. Блок 11 оперативной памяти в это время находится в режиме считывания - низкий уровень сигнала (диаграмма 7 на фиг. 2, на которой показан выходной импульс счета-записи элемента 27 задержки).

Длительность выходного импульса одно- вибратора 25 определяется необходимым временем (быстродействием) записи в двоичный счетчик 13 выходной информации блока II оперативной памяти.

Таким образом, каждый выходной импульс одновибратора 25 - импульс перезаписи - осуществляет перезапись содержимого данного канала памяти блока II в двоичный счетчик 13.

По заднему фронту выходного отрицательного импульса одновибратора 25 запускается третий одновибратор 26.

Выходной импульс одновибратора 26 блокирует элемент 20 запрета, а также проходит через элемент ИЛИ 23 на вход элемента 27 задержки.

Элемент задержки необходим для введения задержки между окончанием установки числа в двоичный счетчик 13 и срабатыванием этого счетчика по счетному входу.

Импульс счета и записи с выхода элемента 27 задержки поступает на счетный вход двоичного счетчика 13 и на вход управления записью считыванием блока 11 оперативной памяти, который во время действия этого импульса переводится в режим записи. Во время действия фронта импульса счета и записи содержимое двоичного счетчика 13 увеличивается на единицу и сразу же записывается в данный канал памяти блока 11.

Этим завершилось увеличение на единицу содержимого первого канала памяти - канала памяти ошибок первого канала записи-воспроизведения.

Пусть следующим появился импульс ошибок на 24-м выходе (диаграмма 2 на фиг. 2) блока 5 временного разделения. Этот импульс поступает на 24-й вход блока 8 стробирования, а также проходит через элемент ИЛИ 6 и подсчитывается счетчиком 7 суммарных ошибок. Импульс ошибки 24-го канала записи-воспроизведения с выхода элемента ИЛИ 6 поступает также на первый вход триггера 19 пуска и переключает его. Выходной сигнал триггера 19 проходит через элемент 20 запрета, элемент ИЛИ 22 и запускает одновибратор 24. Выходной импульс адреса этого одновибратора поступает на вход блокировки блока 1I оперативной памяти и через некоторое время поступает с выхода элемента 28 задер Лки на сброс в исходное нулевое состояние, в частности.

10

первого триггера 10 адреса, а также поступает далее через элемент 29 запрета на вход стробирования блока 8 стробирования.

Появляется импульс на 24-м выходе бл о- ка 8 и, соответственно, на 24-м входе преобразователя 9 кода. При этом появляются импульсы на 2 и 8-м выходах (фиг. 3) преобразователя 9, которые переключают в единичное состояние соответствующие триггеры 10 и устанавливают на адресных входах блока 11 оперативной памяти код 10000010 адреса 24-го канала памяти. По спаду импульса адреса запускается второй одновибратор 25, выходной импульс перезаписи которого производит перезапись предыдущего содержимого 24-го канала памяти блока И в двоичный счетчик 13.

По спаду импульса перезаписи запускается одновибратор 26. Выходной импульс счета и записи этого одновибратора через не- которое время, определяемое элементом 27 задержки, осуществляет добавление единицы 20 к содержимому двоичного счетчика 13, новое содержимое этого счетчика тут же записывается в 24-й канал памяти блока 11. За- вер1пилось увеличение на единицу содержимого 24-го канала памяти блока 1 1 при е появлении данного импульса ошибки 24-го капала записи-воспроизведения и т. д.

Таким образом, цикл запоминепия канальной ошибки включает в себя последовательное формирование во времени трех импульсов - импульса установки адреса зо (диаграмма 4 на фиг. 2) блока 11 оперативной памяти, импульса перезаписи (диаграмма 6 на фиг. 2) содержимого включенного кана.ла па.мяти в двоичный счетчик 13 и и. счета двоичного счетчика 13 и записи нового содержимого (уве- 35 . |иченпого па единицу) этого счетчика во включенный Kaiia. i памяти блока 11 опера- тинной памяти.

При частоте 500 кГц опорного сигнала блока 5 временного разделения и пестрое- НИН блока I 1 оперативной памяти на .микросхемах серии 564 интервал следования импульсов ошибок на выходе многовходо- вого элемента ИЛИ 6 не должен быть менее 2,08 МКС (сумма длительностей импуль- 5 сов трех последовательно работающих одно- вибраторов 24, 25 и 26).

Для повын ения быстродействия устройства, (применительно к ограниченному количеству следующих подряд с максимальной частотой и.мпульсов О1пибок на выходе 50 элемента ИЛИ 6) служит связь выхода третьего одновибратора 26 с входом блокировки элемента 20 запрета. Если следующий выходной импульс оп,ибки элемента ИЛИ 6 пришел до заверп1епия цикла запоминания предыдущей канальной 01пибки, но после 55 переключения триггера 19 пуска в исходное состояние, то триггер 19 перек.чючается, т. е. запоминает приход данного импульса ошиб0

0 е

о 5

5

0 5

ки, но его выходной сигнал поступает на запуск первого одновибратора 24 только после окончания импульса счета и записи. Блоки 8 и 18 стробирования необходимы для того, чтобы исключить смену адреса блока 11 оперативной памяти выходными импульсами блока 5 временного разделения или дешифратора 34 до момента поступления импульса в адреса на вход блокировки блока 5.

После окончания контроля суммарной до стоверности аппарата 1 магнитной записи необходимо оперативно просмотреть зафиксированное количество ошибок каждого канала записи-воспроизведения в отдельности.

Для включения режима просмотра канальных ошибок и последующего стирания каналов памяти блока 11 включают тумблер 14, т. е. с элемента 14 управления подается команда на установочный в нулевое состояние вход двоичного счетчика 13, на вход блокировки элемента 21 запрета, на вход блокировки элемента 20 запрета, на вход блокировки элемента 29 запрета, на один из входов элемента И 17, на информационный вход -триггера 35 стирания и на инверсный установочный вход двоичного счетчика 33, снимая тем самым блокировку с этого счетчика по его установочному в нулевое состояние входу.

Двоичный счетчик 33 находится в нулевом состоянии. Согласно этому состоянию присутствует сигнал на первом выходе дешифратора 34, который в устройстве не используется.

Блокировка элемента 20 запрета предотвращает возможность сбоя работы устройства в режиме просмотра канальных ощибок выходными импульсами блока 5 временного разделения.

Блокировка элемента 21 запрета обеспечивает режи.м считывания блока 11 опера-- тивной памяти.

Требуе.мый номер канала памяти включают соответствующим количеством нажатий кнопки 15.

Первый канал памяти включается разовым нажатием кнопки 15, во время нажатия которой переключается триггер 36 защиты, выходной сигнал которого при этом проходит через элемент И 32, и поступает на счетный вход двоичного счетчика 33, а также проходит через элемент ИЛИ 22 на запуск одновибратора 24.

Двоичный счетчик 33 переключается и появляется сигнал на втором выходе дешифратора 34, который поступает на первый вход блока 18 стробирования.

С другой стороны, импульс адреса с выхода одновибратора 24 поступает на вход блокировки блока 11 оперативной памяти и через элемент 28 задержки на сброс в исходное, нулевое, состояние триггеров 10 адреса, а также проходит далее через эле11

12

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

| Устройство для проверки многоканального аппарата магнитной записи | 1981 |

|

SU997096A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля ошибок воспроизведения информации с носителя магнитной записи | 1989 |

|

SU1619339A1 |

| Устройство для контроля многоканального аппарата магнитной записи | 1985 |

|

SU1312644A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1987 |

|

SU1490691A1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| Многоканальное устройство для регистрации и индикации аварийных ситуаций | 1990 |

|

SU1796907A1 |

Изобретение относится к приборостроению. Цель изобретения - сокращение времени контроля с поканальным анализом ошибок. Для этого в устройство, содержащее аппарат 1 магн. записи, генератор 2, формирователь 3 кода, блок 4 выделения ошибок, блок 5 временного разделения, элемент ИЛИ 6, счетчик 7 ошибок, блок 8 стробиро- вания, преобразователь 9 кода, триггеры 10 адреса, блок 11 памяти, блок 12 индикации. счетчик 13, элементы 14-16 управления, элемент И 17, триггер 19 пуска, элементы 20, 21 запрета, элементы ИЛИ 22, 23, одновибраторы 25, 26, элементы 27, 28 задержки, элемент 29 запрета, введены блок 18 стробирования, делитель 30 частоты, элементы И 31 и 32, счетчик 33, дешифратор 34 и триггер 35. Устройство работает автоматически в режиме раздельного наполнения канальных ошибок, при этом цикл запоминания канальной ошибки включает последовательное формирование импульса установки адреса блока 11 оперативной памяти, импульса перезаписи в счетчике 13 и импульса счета последнего и записи нового содержимого этого счетчика во включенный канал памяти блока 11. На выходах триггеров 10 перебираются адреса всех каналов памяти блока 11, а обнуление каждого канала производится по нулевому содержанию счетчика 13 от действия сигнала элемента 14 управления. 3 ил. & (Л

10

15

мент И 17 на вход стробирования блока 18 стробирования. После этого проявляется импульс на первом входе преобразователя 9 кода и на выходах триггеров 10 устанавливается адресный код первого канала памяти. При этом содержимое первого канала памяти выводится на выходы блока 11 оперативной памяти и индицируется блоком 12 индикации.

После вторичного нажатия кнопки 15 опять переключается двоичный счетчик 33 (т. е. счетчик 33 подсчитывает нажатия кнопки 15), в результате чего устанавливается сигнал на третьем выходе дешифратора 34 и, следовательно, на втором сигнальном входе блока 18 стробирования. При этом запускается также одновибратор 24, выходной импульс адреса которого блокирует блок 11 оперативной памяти, сбрасывает первый триггер 10 адреса в нулевое состояние и поступает на вход стробирования блока 18 стробирования. Формируется импульс на вто- 20 ром входе преобразователя 9 кода, вызывающий установку на выходах триггеров 10 адреса второго канала памяти, содержимое которого после этого выводится на блок 12 индикации.

Третий канал памяти включается нажа- тием кнопки 15 в третий раз и т. д.

Триггер 36 предназначен для защиты управляемых цепей от «дребезга контактов элемента 15 управления.

Для большего удобства работы с устройством путем индицирования, а не запоминания оператором номера канала памяти при считывании его содержимого можно подключить, например, к выходам дешифратора 34 дополнительный блок индикации.

30

От выходного сигнала делителя 30 частоты начинает автоматически переключаться двоичный счетчик 33 и, соответственно, формироваться сигнал поочередно на всех выходах дешифратора 34.

Выходной сигнал делителя 30 частоты проходит через элемент И 31 и поступает также через элемент ИЛИ 22 на запуск одновибратора 24, который при этом периодически формирует импульс адреса в момент каждого переключения дешифратора 34.

В результате на выходах триггеров 10 перебираются адреса всех каналов памяти блока 11. Обнуление каждого канала памяти происходит при этом потому, что блок 11 оперативной памяти находится в режиме записи и на его информационных входах в это время находятся одни нули, поскОоТьку двоичный счетчик 13 находится в нулевом состоянии от действия сигнала элемента 14 управления.

Т. е. стирание происходит путем записи в каждый канал памяти нулевого содержимого двоичного счетчика 13.

При появлении сигнала на последнем выходе дешифратора 34 триггер 35 стирания устанавливается в ис.ходное состояние.

Формула изобретения

Устройство для контроля многоканального аппарата магнитной записи, содержащее генератор, один выход которого соединен с входом формирователя кода, выходами подключенного к входам многоканального аппарата магнитной записи, выходы которого подсоединены к входам многоканального, блока выделения ошибок, выхосодержаший при этом, в частности, свето- -35 соединенного с входами блока времендиоды в количестве, равном числу каналов памяти.

После просмотра содержимого всех каналов памяти блока 11 оперативной памяти каналы памяти блока 11 необходимо обнулить. Эта операция в предлагаемом устройстве в отличие от известного выполняется автоматически после разовой подачи сигнала от элемента 16 управления.

Каждый раз перед включением режима обнуления каналов памяти блока 11, а также перед повторным включением просмотра канальных ошибок необходимо выключить, а затем опять включить элемент 14 управления. Этим достигается устаноки в исходное, нулевое, состояние двоичного счетчика 33.

Выходной сигнал элемента 16 управления переключает триггер 35 стирания, выходной сигнал которого открывает элемент И 31 для прохождения выходного низкочастотного (8 Гц) сигнала делителя 30 частоты на

40

ного разделения, вход опорного сигнала которого подключен к второму выходу генератора, а выходы соединены с входами блока стробирования и с входами многовходового элемента ИЛИ, выход которого соединен с счетчиком ошибок и с nepBt iM входом триггера пуска, выход которого соединен через последовательно включенные первый элемент запр-ета, первый элемент ИЛИ, первый одновибратор, второй элемент запрета, вто-с рой одновибратор, третий одновибратор, выход которого соединен также с первым входом блокировки первого элемента запрета, второй элемент ИЛИ и первый элемент задержки с управляющим входом блока оперативной памяти и со счетным входом двоич50 ного счетчика, соединенного выходами и с информационными входами блока оперативной памяти, выходы которого подключены к группе установочных входов двоичного счетчика и к входам блока индикации, а адресные входы соединены через группу тригсчетный вход двоичного счетчика 33, а так- 55 герое адреса с выходами преобразователя

же проходит через элемент ИЛИ 23, элемент 27 задержки и переводит блок 11 оперативной памяти в режим записи.

кода, входы которого подключены к выходам блока стробирования, первый элемент управления, выходом соединенный с вторым вхо0

5

0

0

От выходного сигнала делителя 30 частоты начинает автоматически переключаться двоичный счетчик 33 и, соответственно, формироваться сигнал поочередно на всех выходах дешифратора 34.

Выходной сигнал делителя 30 частоты проходит через элемент И 31 и поступает также через элемент ИЛИ 22 на запуск одновибратора 24, который при этом периодически формирует импульс адреса в момент каждого переключения дешифратора 34.

В результате на выходах триггеров 10 перебираются адреса всех каналов памяти блока 11. Обнуление каждого канала памяти происходит при этом потому, что блок 11 оперативной памяти находится в режиме записи и на его информационных входах в это время находятся одни нули, поскОоТьку двоичный счетчик 13 находится в нулевом состоянии от действия сигнала элемента 14 управления.

Т. е. стирание происходит путем записи в каждый канал памяти нулевого содержимого двоичного счетчика 13.

При появлении сигнала на последнем выходе дешифратора 34 триггер 35 стирания устанавливается в ис.ходное состояние.

Формула изобретения

Устройство для контроля многоканального аппарата магнитной записи, содержащее генератор, один выход которого соединен с входом формирователя кода, выходами подключенного к входам многоканального аппарата магнитной записи, выходы которого подсоединены к входам многоканального, блока выделения ошибок, выхоД ми соединенного с входами блока времен

ного разделения, вход опорного сигнала которого подключен к второму выходу генератора, а выходы соединены с входами блока стробирования и с входами многовходового элемента ИЛИ, выход которого соединен с счетчиком ошибок и с nepBt iM входом триггера пуска, выход которого соединен через последовательно включенные первый элемент запр-ета, первый элемент ИЛИ, первый одновибратор, второй элемент запрета, второй одновибратор, третий одновибратор, выход которого соединен также с первым входом блокировки первого элемента запрета, второй элемент ИЛИ и первый элемент задержки с управляющим входом блока оперативной памяти и со счетным входом двоичного счетчика, соединенного выходами и с информационными входами блока оперативной памяти, выходы которого подключены к группе установочных входов двоичного счетчика и к входам блока индикации, а адресные входы соединены через группу тригкода, входы которого подключены к выходам блока стробирования, первый элемент управления, выходом соединенный с вторым вхо13

дом блокировки первого элемента запрета, с входом блокировки второго элемента запрета, с первым входом элемента И и с уста- FJOBOMHbiM входом двоичного счетчика, управляющий вход которого соединен с прямым выходом второго одновибратора и с вторым входом триггера пуска, второй и третий элементы управления, причем выход первого одновибратора соединен дополнительно с входом блокировки блока оперативной памяти и с входом второго элемента задержки, выход которого соединен с вторыми входами триггеров адреса, отличающееся тем, что, с целью сокращения времени контроля с по- канальным анализом ощибок, в него введены последовательно соединенные делитель частоты, подсоединенный к второму входу генератора, дополнительный элемент И, дополнительный элемент ИЛИ, дополнительный двоичный счетчик, дешифратор и дополнительный блок стробирования, выходы которого подсоединены к входам преобразователя кода, триггер стирания, первым входом

ппильс адреса

Фиг. 2

14

5

0

соединенный с выходом третьего элемента управления, вторым входом - с выходом первого элемента управления и с установочным входом дополнительного двоичного счетчика, третьим входом - с последним выходом дещифратора, а выходом - с вторым входом дополнительного элемента И и с вторым входом второго элемента ИЛИ, дополнительный элемент запрета, выходом соединенный с входом стробирования блока стробирования, входом блокировки - с выходом первого элемента управления, а сигнальным входом - с выходом второго элемента задержки и с вторым входом элемента И, выход которого соединен с входом стробирования дополнительного блока стробирования, и триггер защиты, входами подключенный к выходам второго элемента управления, а выходом соединенный с вторым входом дополнительного элемента ИЛИ и с вторым входом первого элемента ИЛИ, третий вход которого соединен с выходом дополнительного элемента И.

70 Q

000 00 О 0000 0000

0000

0000

0000

0000

0000

о ТОО

0000

00 00

0000

0000

0000 0000 0000 0070 о о 00 00 00 0000 0000 00 о 1

Фиг. 3

| Авторское свидетельство СССР № 1945271, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР № 1171845, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| . | |||

Авторы

Даты

1988-08-30—Публикация

1986-12-08—Подача