3130

32 J4 $

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗМЕРЕНИЯ РАСХОДА ЭЛЕКТРОМАГНИТНЫМ РАСХОДОМЕРОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2004 |

|

RU2285243C2 |

| Аналого-цифровой преобразователь двухтактного интегрирования | 1988 |

|

SU1515367A2 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1411974A1 |

| Анализатор формы импульсных сигналов | 1985 |

|

SU1254395A1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| Способ определения усредненного значения сдвига фаз и устройство для его осуществления | 1987 |

|

SU1499266A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1674373A2 |

| Функциональный генератор | 1983 |

|

SU1120364A1 |

| ИЗМЕРИТЕЛЬ ХАРАКТЕРИСТИК ФАЗОВЫХ ФЛУКТУАЦИЙ | 1992 |

|

RU2041469C1 |

| Устройство для измерения относительной разности скоростей вращения | 1986 |

|

SU1455322A1 |

Изобретение относится к радиотехническим измерениям. Сущность изобретения: устройство для анализа сигнала включает блок 1 выделения моментов достижения анализируемым сигналом заранее обусловленных характерных значений, блоки 2, 3, 4 запоминания последовательных значений анализируемого сигнала, блок 5 измерения временных интервалов и накопительные запоминающие устройства 6, 7, 8. 2 ил.

(Л

С

00

VI о со ел

Изобретение относится к радиотехниеским измерениям, в частности к способам устройствам для анализа сигналов сложой формы, особенно колебаний с переменым периодом повторения импульсов еременной длительности.

Цель изобретения - расширение диапаона анализируемых сигналов,

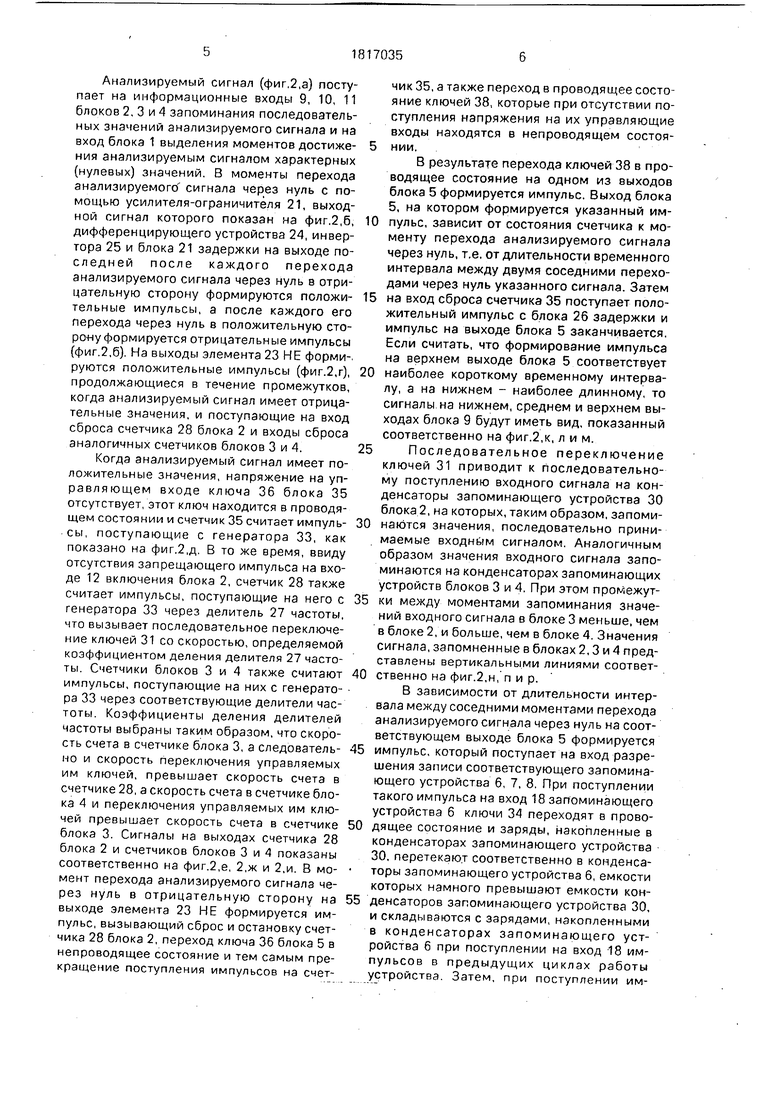

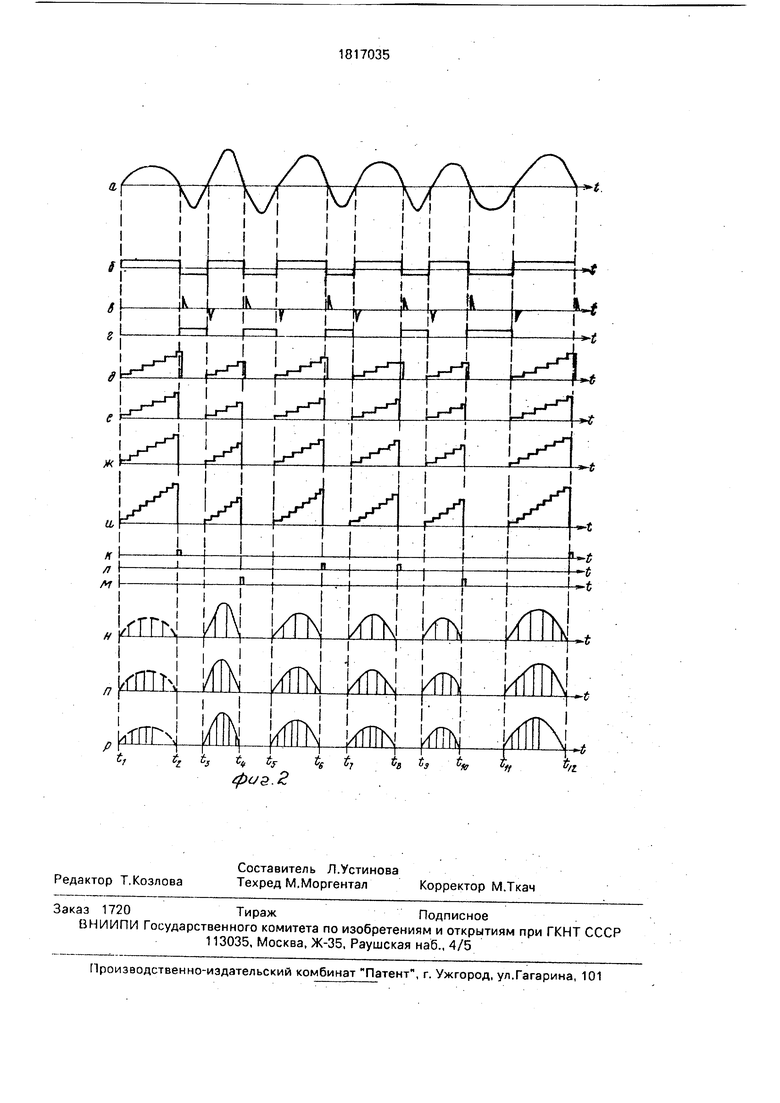

На фиг.1 изображена блок-схема устройства; на фиг,2 - эпюры сигналов, поясня- ющие работу устройства.

Устройство (фиг.1) содержит блок 1 выделения моментов достижения анализируемым сигналом заранее обусловленных характерных значений (в данном случае моменты перехода через нуль), блоки 2, 3 и 4 запоминания последовательных значений анализируемого сигнала, блок 5 измерения временных интервалов и накопительные запоминающие устройства 6, 7, 8. Блоки 2, 3, 4 запоминания значений сигнала имеют информационные входы 9,10,11, образующие вместе со входом блока 1 выделения моментов информационный вход устройства анализа сигнала, входы 12, 13, 1.4 включения и входы 15, 16, 17 сброса. Входы 9, 10, 11 включения и 12, 13, 14 сброса соединены с выходами блока 1. Каждое из накопительных запоминающих устройств 6, 7, 8 имеет информационные входы, информационные выходы, образующие выходы устройства анализа сигнала, и вход сброса. Информационные входы запоминающего устройства 6 соответственно соединены с выходами блока 2 запоминания значений сигнала, информационные входы запоминающего устройства 7 соответственно соединены с выходами блока 3 запоминания значений сигнала, а информационные входы запоминания устройства 8 соответственно соединены с выходами блока 4 запоминания значений сигнала. Входы 18, 19, 20 разрешения записи соответственно запоминающих устройств 6, 7 и 8 соединены соответственно с выходами блока 5 измере- ния интервалов, входы которого соединены с выходами блока 1.

Блок 1 выделения моментов содержит усилитель-ограничитель 21, вход которого является входом блока 1, однополупериод- ный выпрямитель 22 и элемент 23 НЕ, последовательно подключенные к выходу усилителя-ограничителя 21, и дифференцирующее устройство 24, инвертор и блок 26 задержки, также последовательно подключенные к выходам усилителя-ограничителя 21. Выходы элемента 23 НЕ и блока 26 задержки образуют выходы блока 1.

Блок 2 запоминания значений сигнала содержит делитель 27 частоты, счетчик 28,

счетный вход которого соединен с выходом делителя 27 частоты, а вход сброса образует вход включения блока 2, дешифратор 29, подключенный к выходам счетчика 28, запоминающее устройство 30 на конденсаторах и электронные ключи 31, входы которых образуют информационный вход блока 2. Выходы соответственно соединены с информационными входами запоминающего

0 устройства 30, а входы управления соответственно соединены с выходами дешифратора 29. Запоминающее устройство 30 содержит группу конденсаторов, одни выводы которых соответственно образуют информационные

5 входы запоминающего устройства 30, а также выходные выводы блока 2, а другие заземлены, и группу электронных ключей 32, которые включены соответственно параллельно конденсаторам и управляющие входы которых

0 соединены между собой и образуют вход 15 сброса блока 2.

Блоки 3 и 4 запоминания значений сигнала выполнены аналогично блоку 2. Входы делителя 27 частоты блока 2 и делителей

5 частоты блоков 3, и 4 подключены к выходу генератора 33.

. Накопительное запоминающее устройство 6 содержит группу конденсаторов, группу электронных ключей 34, входы кото0 ,рых образуют информационные входы запоминающего устройства 6, а управляющие входы соединены между собой и образуют входы 18 разрешения записи запоминающего устройства 6. Одни выводы конденса5 торов запоминающего устройства 6 через выпрямительные циоды соединены соответственно с выходами ключей 34, и образуют также выходные выводы запоминающего устройства 6, а другие заземлены. Накопи-/

0 тельные запоминающие устройства 7 и 8 выполнены аналогично запоминающему устройству 6. .

Блок 5 измерения интервалов содержит счетчик 35, счетный вход которого через

5 электронный ключ 36 соединен с выходом генератора 33, а вход сброса образует вход блока 5, соединенный с выходом блока 26 задержки блока 1, дешифратор 37, подключенный к выходным линиям счетчика 35 и

0 группу электронных ключей 38, входы которых подключены к дешифратору 37, а выходы соответственно образуют выходы блока 5, соединенные с входами 18, 19, 20 и 24 разрешения записи запоминающих устрой5 ство 6, 7 и 8. Входы управления ключей 36 и 38 соединены между собой и образуют вход блока 5, соединенный с выходом элемента 24 НЕ блока 1.

Устройство работает следующим образом.

Анализируемый сигнал (фиг,2,а) поступает на информационные входы 9, 10, 11 блоков 2, 3 и 4 запоминания последовательных значений анализируемого сигнала и на вход блока 1 выделения моментов достижения анализируемым сигналом характерных (нулевых) значений. В моменты перехода анализируемого сигнала через нуль с помощью усилителя-ограничителя 21, выходной сигнал которого показан на фиг.2,б, дифференцирующего устройства 24, инвертора 25 и блока 21 задержки на выходе последней после каждого перехода анализируемого сигнала через нуль в отрицательную сторону формируются положительные импульсы, а после каждого его перехода через нуль в положительную сто- ро-ну формируется отрицательные импульсы (фиг.2,6). На выходы элемента 23 НЕ формируются положительные импульсы (фиг.2,г), продолжающиеся в течение промежутков, когда анализируемый сигнал имеет отрицательные значения, и поступающие на вход сброса счетчика 28 блока 2 и входы сброса аналогичных счетчиков блоков 3 и 4.

Когда анализируемый сигнал имеет положительные значения, напряжение на управляющем входе ключа 36 блока 35 отсутствует, этот ключ находится в проводящем состоянии и счетчик 35 считает импульсы, поступающие с генератора 33, как показано на фиг.2,д. В то же время, ввиду отсутствия запрещающего импульса на входе 12 включения блока 2, счетчик 28 также считает импульсы, поступающие на него с генератора 33 через делитель 27 частоты, что вызывает последовательное переключение ключей 31 со скоростью, определяемой коэффициентом деления делителя 27 частоты. Счетчики блоков 3 и 4 также считают импульсы, поступающие на них с генератора 33 через соответствующие делители частоты. Коэффициенты деления делителей частоты выбраны таким образом, что скорость счета в счетчике блока 3, а следовательно и скорость переключения управляемых им ключей, превышает скорость счета в счетчике 28, а скорость счета в счетчике блока 4 и переключения управляемых им ключей превышает скорость счета в счетчике блока 3. Сигналы на выходах счетчика 28 блока 2 и счетчиков блоков 3 и 4 показаны соответственно на фиг.2,е, 2,ж и 2,и. В момент перехода анализируемого сигнала через нуль в отрицательную сторону на выходе элемента 23 НЕ формируется импульс, вызывающий сброс и остановку счетчика 28 блока 2, переход ключа 36 блока 5 в непроводящее состояние и тем самым прекращение поступления импульсов на счетчик 35, а также переход в проводящее состояние ключей 38, которые при отсутствии поступления напряжения на их управляющие входы находятся в непроводящем состоя- 5 нии.

В результате перехода ключей 38 в проводящее состояние на одном из выходов блока 5 формируется импульс. Выход блока 5, на котором формируется указанный им0 пульс, зависит от состояния счетчика к моменту перехода анализируемого сигнала через нуль, т.е. от длительности временного интервала между двумя соседними переходами через нуль указанного сигнала. Затем

5 на вход сброса счетчика 35 поступает положительный импульс с блока 26 задержки и импульс на выходе блока 5 заканчивается. Если считать, что формирование импульса на верхнем выходе блока 5 соответствует

0 наиболее короткому временному интервалу, а на нижнем - наиболее длинному, то сигналы на нижнем, среднем и верхнем выходах блока 9 будут иметь вид, показанный соответственно на фиг.2,к, л и м.

5 Последовательное переключение ключей 31 приводит к последовательному поступлению входного сигнала на конденсаторы запоминающего устройства 30 блока 2, на которых, таким образом, запоми0 наются значения, последовательно принимаемые входным сигналом. Аналогичным образом значения входного сигнала запоминаются на конденсаторах запоминающих устройств блоков 3 и 4. При этом промежут5 ки между моментами запоминания значений входного сигнала в блоке 3 меньше, чем в блоке 2, и больше, чем в блоке 4. Значения сигнала, запомненные в блоках 2,3 и 4 представлены вертикальными линиями соответ0 ственно на фиг.2,н, п и р.

В зависимости от длительности интервала между соседними моментами перехода анализируемого сигнала через нуль на соответствующем выходе блока 5 формируется

5 импульс, который поступает на вход разрешения записи соответствующего запоминающего устройства 6, 7, 8. При поступлении такого импульса на вход 18 запоминающего устройства 6 ключи 34 переходят в прово0 дящее состояние и заряды, накопленные в конденсаторах запоминающего устройства 30, перетекают соответственно в конденсаторы запоминающего устройства 6, емкости которых намного превышают емкости кон5 денсаторов запоминающего устройства 30, и складываются с зарядами, накопленными в конденсаторах запоминающего устройства б при поступлении на вход 18 импульсов в предыдущих циклах работы устройства. Затем, при поступлении импульса с блока 26 задержки, ключи 32 переходят в проводящее состояние, разряжая конденсаторы запоминающего устройства 30, после чего возвращаются в исходное непроводящее состояние, а импульс на входе 18 разрешения записи исчезает, в результате чего ключи 34 возвращаются в исходное непроводящее состояние. Заряды на конденсаторах запоминающего устройства 6 при этом сохраняются, т.к. их разряду препятствуют диоды, включенные между ними и ключами 34.

Аналогичным образом работают запоминающие устройства 7 и 8 при поступлении импульсов на их входы 19 и 20.

Таким образом, в процессе работы устройства на конденсаторах каждого из запоминающих устройств 6, 7 и 8 обеспечивается суммирование значений сигналов, занимающих одинаковые положения между соседними моментами перехода анализируемого сигнала через нуль, интервалы между которыми равны с заданной точностью соответствующему из заданных значений интервалов, как это предусматривается предложенным способом, В рассматриваемом примере запоминающее устройство 6 будет суммировать значения сигнала, соответствующих наиболее длинным интервалам, а запоминающее устройство 8 наиболее коротким интервалом.

Формула изобретения

Устройство для анализа сигналов сложной формы, содержащее блок выделения моментов достижения анализируемым сигналом заданных значений и последовательно соединенные генератор и блок измерения временных интервалов, второй вход которого подключен к выходу блока выделения моментов, отличающееся

тем, что, с целью расширения диапазона анализируемых сигналов, в него дополнительно введены п блоков запоминания последовательных значений анализируемого сигнала, входы включения и сброса которых

соединены с выходом блока выделения моментов, и п накопительных запоминающих устройств, информационные входы которых соединены с выходами соответствующего блока запоминания последовательных

значений анализируемого сигнала, а вход разрешения записи соединен с соответствующим выходом блока измерения временных интервалов.

| СПОСОБ ОЧИСТКИ ГАЗОКОНДЕНСАТА, НЕФТИ И НЕФТЕПРОДУКТОВ ОТ СЕРОВОДОРОДА | 1997 |

|

RU2119526C1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-05-23—Публикация

1991-01-09—Подача