Изобретение относится к вычислительной технике и может быть использовано для решения задачи нелинейного программирования.

Целью изобретения является повышение быстродействия устройства,

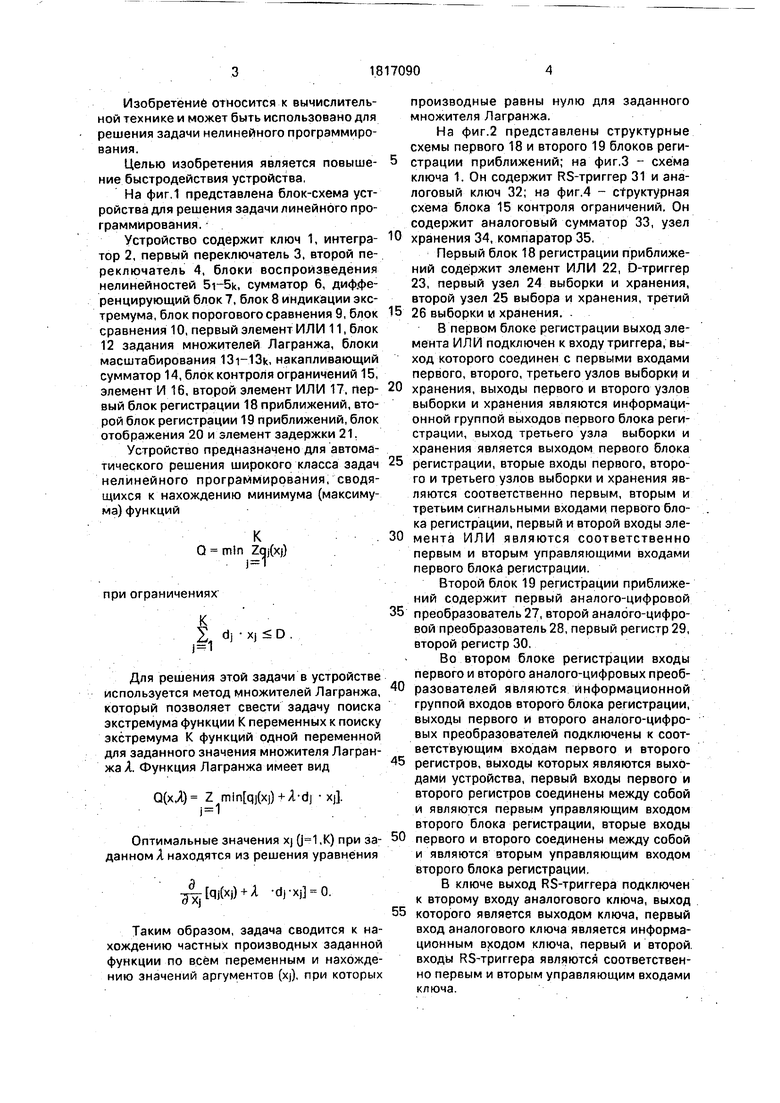

На фиг.1 представлена блок-схема устройства для решения задачи линейного программирования.

Устройство содержит ключ 1, интегратор 2, первый переключатель 3, второй переключатель 4, блоки воспроизведения нелинейностей 5i-5k, сумматор 6, дифференцирующий блок 7, блок 8 индикации экстремума, блок порогового сравнения 9, блок сравнения 10, первый элемент ИЛ И 11, блок 12 задания множителей Лагранжа, блоки масштабирования , накапливающий сумматор 14, блок контроля ограничений 15, элемент И 16, второй элемент ИЛИ 17. первый блок регистрации 18 приближений, второй блок регистрации 19 приближений, блок отображения 20 и элемент задержки 21.

Устройство предназначено для автоматического решения широкого класса задач нелинейного программирования, сводящихся к нахождению минимума (максимума) функций

К. Q mln ZQJ(XJ)

при ограничениях

dj xj D .

Для решения этой задачи в устройстве используется метод множителей Лагранжа, который позволяет свести задачу поиска экстремума функции К переменных к поиску экстремума К функций одной переменной для заданного значения множителя Лагранжа А. Функция Лагранжа имеет вид

0(хД) Z (xj) + A dj xj.

Оптимальные значения xj (,K) при заданном А находятся из решения уравнения

Тх

qj(xj) + A -dj-xfl-0.

Таким образом, задача сводится к нахождению частных производных заданной функции по всём переменным и нахождению значений аргументов (xj), при которых

производные равны нулю для заданного множителя Лагранжа.

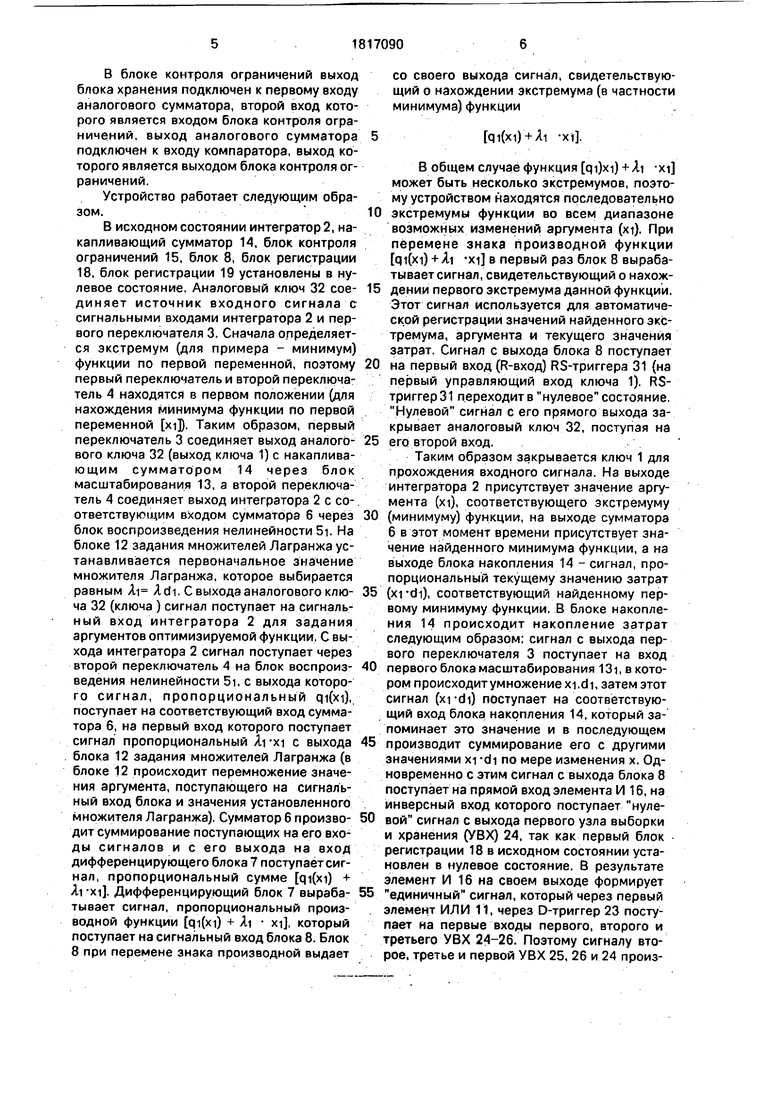

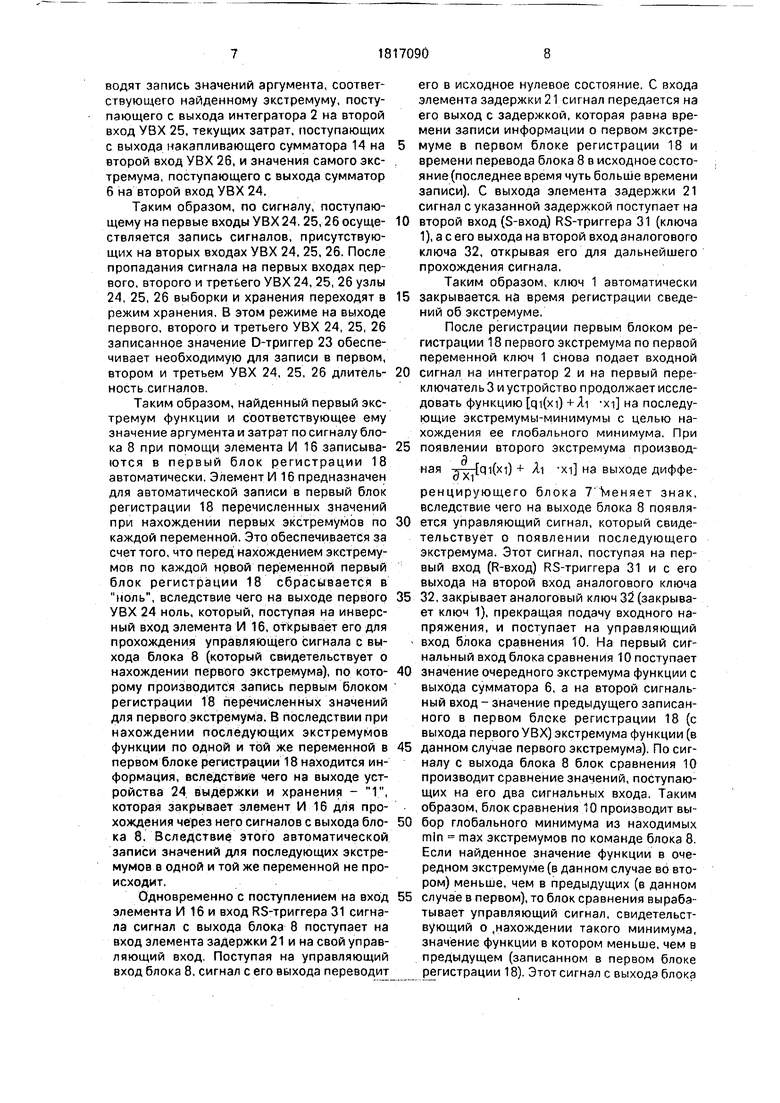

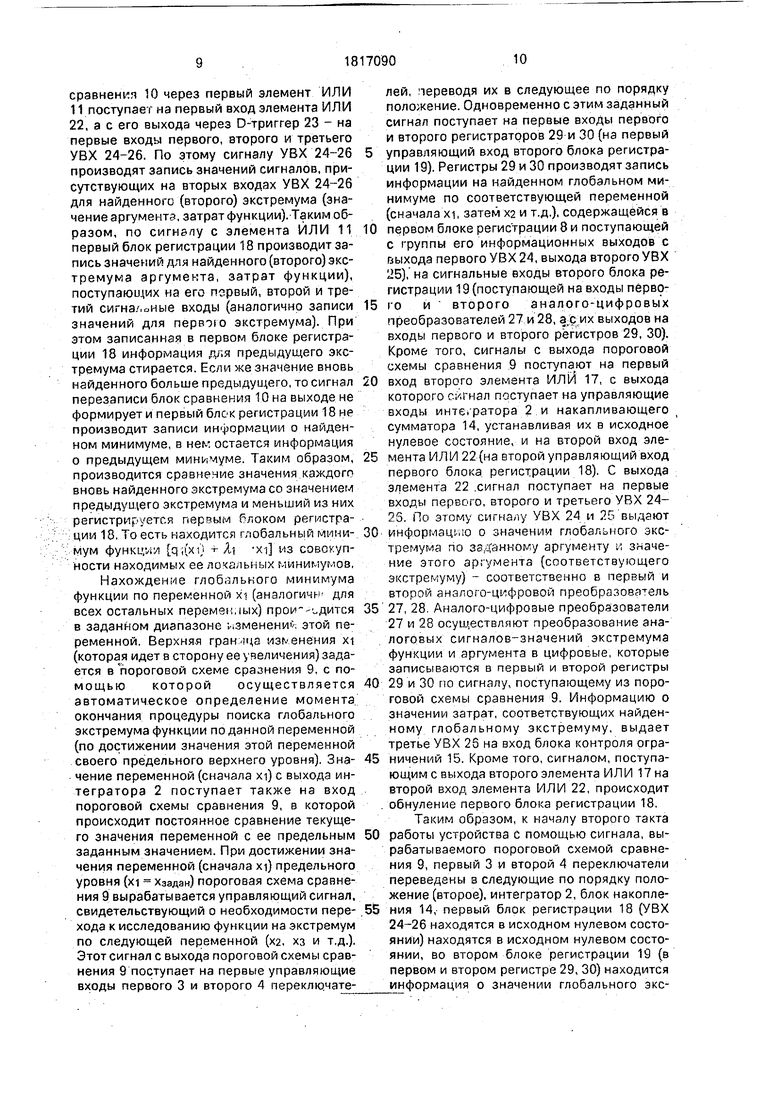

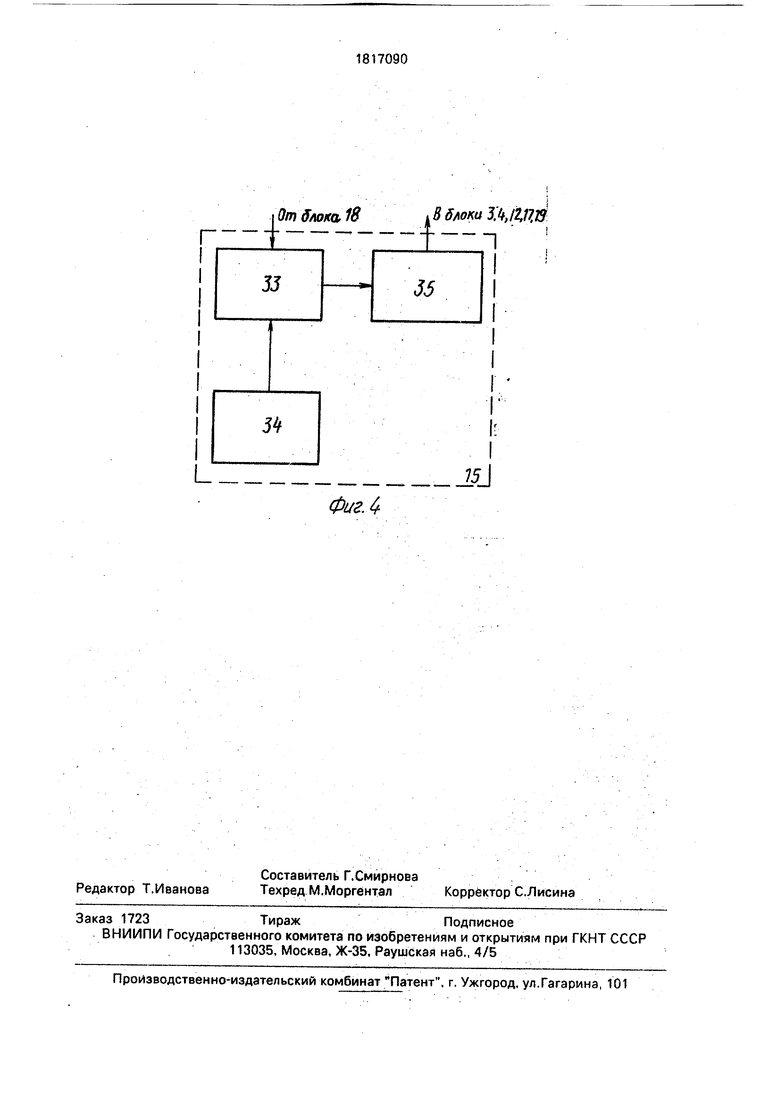

На фиг.2 представлены структурные схемы первого 18 и второго 19 блоков регистрации приближений; на фиг.3 - схема ключа 1. Он содержит RS-триггер 31 и аналоговый ключ 32; на фиг.4 - структурная схема блока 15 контроля ограничений. Он содержит аналоговый сумматор 33, узел

0 хранения 34, компаратор 35.

Первый блок 18 регистрации приближений содержит элемент ИЛИ 22, 6-триггер 23, первый узел 24 выборки и хранения, второй узел 25 выбора и хранения, третий

5 26 выборки и хранения. В первом блоке регистрации выход элемента ИЛИ подключен к входу триггера, выход которого соединен с первыми входами первого, второго, третьего узлов выборки и

0 хранения, выходы первого и второго узлов выборки и хранения являются информационной группой выходов первого блока регистрации, выход третьего узла выборки и хранения является выходом первого блока

5 регистрации, вторые входы первого, второго и третьего узлов выборки и хранения являются соответственно первым, вторым и третьим сигнальными входами первого блока регистрации, первый и второй входы эле0 мента ИЛИ являются соответственно первым и вторым управляющими входами первого блока регистрации.

Второй блок 19 регистрации приближений содержит первый аналого-цифровой

5 преобразователь 27, второй аналого-цифровой преобразователь 28, первый регистр 29, второй регистр 30,

Во втором блоке регистрации входы первого и второго аналого-цифровых преоб0 разователей являются информационной группой входов второго блока регистрации, выходы первого и второго аналого-цифровых преобразователей подключены к соответствующим входам первого и второго

5 регистров, выходы которых являются выходами устройства, первый входы первого и второго регистров соединены между собой и являются первым управляющим входом второго блока регистрации, вторые входы

0 первого и второго соединены между собой и являются вторым управляющим входом второго блока регистрации.

В ключе выход RS-триггера подключен к второму входу аналогового ключа, выход

5 которого является выходом ключа, первый вход аналогового ключа является информационным входом ключа, первый и второй, входы RS-триггера являются соответственно первым и вторым управляющим входами ключа.

В блоке контроля ограничений выход блока хранения подключен к первому входу аналогового сумматора, второй вход которого является входом блока контроля ограничений, выход аналогового сумматора подключен к входу компаратора, выход которого является выходом блока контроля ограничений.

Устройство работает следующим образом.

В исходном состоянии интегратор 2, накапливающий сумматор 14, блок контроля ограничений 15, блок 8, блок регистрации 18, блок регистрации 19 установлены в нулевое состояние. Аналоговый ключ 32 соединяет источник входного сигнала с сигнальными входами интегратора 2 и первого переключателя 3. Сначала определяется экстремум (для примера - минимум) функции по первой переменной, поэтому первый переключатель и второй переключатель 4 находятся в первом положении (для нахождения минимума функции по первой переменной xij. Таким образом, первый переключатель 3 соединяет выход аналогового ключа 32 (выход ключа 1) с накаплива- ющим сумматором 14 через блок масштабирования 13, а второй переключатель 4 соединяет выход интегратора 2 с со-. ответствую щи м входом сумматора б через блок воспроизведения нелинейности 5t. На блоке 12 задания множителей Лагранжа устанавливается первоначальное значение множителя Лагранжа, которое выбирается равным At Я di. С выхода аналогового ключа 32 (ключа ) сигнал поступает на сигналь- ный вход интегратора 2 для задания аргументов оптимизируемой функции, С выхода интегратора 2 сигнал поступает через второй переключатель 4 на блок воспроизведения нелинейности 5ь с выхода которого сигнал, пропорциональный qi(xi), поступает на соответствующий вход сумматора 6, на первый вход которого поступает сигнал пропорциональный Ai -xi с выхода блока 12 задания множителей Лагранжа (в блоке 12 происходит перемножение значения аргумента, поступающего на сигнальный вход блока и значения установленного множителя Лагранжа). Сумматор 6 производит суммирование поступающих на его входы сигналов и с его выхода на вход дифференцирующего блока 7 поступает сигнал, пропорциональный сумме qi(xi) + Ai -xij. Дифференцирующий блок 7 вырабатывает сигнал, пропорциональный производной функции qi(xi) + Ai xi, который поступает на сигнальный вход блока 8. Блок 8 при перемене знака производной выдает

со своего выхода сигнал, свидетельствующий о нахождении экстремума (в частности минимума) функции

(xi) + Ai -xi.

В общем случае функция qi)xi)+Ai -xi может быть несколько экстремумов, поэтому устройством находятся последовательно 0 экстремумы функции во всем диапазоне возможных изменений аргумента (xi). При перемене знака производной функции qt(xi) + Ai -xi в первый раз блок 8 вырабатывает сигнал, свидетельствующий о нахож5 дении первого экстремума данной функции. Этот сигнал используется для автоматической регистрации значений найденного экстремума, аргумента и текущего значения затрат. Сигнал с выхода блока 8 поступает

0 на первый вход (R-вход) RS-триггера 31 (на первый управляющий вход ключа 1). RS- триггер 31 переходит в нулевое состояние. Нулевой сигнал с его прямого выхода закрывает аналоговый ключ 32, поступая на

5 его второй вход.

Таким образом закрывается ключ 1 для прохождения входного сигнала. На выходе интегратора 2 присутствует значение аргумента (xi), соответствующего экстремуму

0 (минимуму) функции, на выходе сумматора 6 в этот момент времени присутствует значение найденного минимума функции, а на выходе блока накопления 14 - сигнал, пропорциональный текущему значению затрат

5 (), соответствующий найденному первому минимуму функции. В блоке накопления 14 происходит накопление затрат следующим образом: сигнал с выхода первого переключателя 3 поступает на вход

0 первого блока масштабирования 13i, в котором происходитумножениехт.сН, затем этот сигнал (хгсН) поступает на соответствующий вход блока накопления 14, который запоминает это значение и в последующем

5 производит суммирование его с другими значениями xi сН по мере изменения х. Одновременно с этим сигнал с выхода блока 8 поступает на прямой вход элемента И 16, на инверсный вход которого поступает нуле0 вой сигнал с выхода первого узла выборки и хранения (УВХ) 24, так как первый блок регистрации 18 в исходном состоянии установлен в нулевое состояние. В результате элемент И 16 на своем выходе формирует

5 единичный сигнал, который через первый . элемент ИЛИ 11, через D-триггер 23 поступает на первые входы первого, второго и третьего УВХ 24-26. Поэтому сигналу второе, третье и первой УВХ 25, 26 и 24 производят запись значений аргумента, соответствующего найденному экстремуму, поступающего с выхода интегратора 2 на второй вход УВХ 25, текущих затрат, поступающих с выхода накапливающего сумматора 14 на второй вход УВХ 26, и значения самого экстремума, поступающего с выхода сумматор 6 на второй вход УВХ 24.

Таким образом, по сигналу, поступающему на первые входы УВХ 24. 25,26 осуществляется запись сигналов, присутствующих на вторых входах УВХ 24, 25, 26. После пропадания сигнала на первых входах первого, второго и третьего УВХ 24, 25, 26 узлы 24, 25, 26 выборки и хранения переходят в режим хранения, В этом режиме на выходе первого, второго и третьего УВХ 24, 25, 26 записанное значение D-триггер 23 обеспечивает необходимую для записи в первом, втором и третьем УВХ 24, 25, 26 длительность сигналов.

Таким образом, найденный первый экстремум функции и соответствующее ему значение аргумента и затрат по сигналу блока 8 при помощи элемента И 16 записываются в первый блок регистрации 18 автоматически. Элемент И 16 предназначен для автоматической записи в первый блок регистрации 18 перечисленных значений при нахождении первых экстремумов по каждой переменной. Это обеспечивается за счет того, что перед нахождением экстремумов по каждой новой переменной первый блок регистрации 18 сбрасывается в ноль, вследствие чего на выходе первого УВХ 24 ноль, который, поступая на инверсный вход элемента И 16, открывает его для прохождения управляющего сигнала с выхода блока 8 (который свидетельствует о нахождении первого экстремума), по которому производится запись первым блоком регистрации 18 перечисленных значений для первого экстремума, В последствии при нахождении последующих экстремумов функции по одной и той же переменной в первом блоке регистрации 18 находится информация, вследствие чего на выходе устройства 24 выдержки и хранения - 1, которая закрывает элемент И 16 для прохождения через него сигналов с выхода блока 8,Вследствие этого автоматической записи значений для последующих экстремумов в одной и той же переменной не происходит,

Одновременно с поступлением на вход элемента И 16 и вход RS-триггера 31 сигнала сигнал с выхода блока 8 поступает на вход элемента задержки 21 и на свой управляющий вход. Поступая на управляющий вход блока 8, сигнал сего выхода переводит

его в исходное нулевое состояние. С входа элемента задержки 21 сигнал передается на его выход с задержкой, которая равна времени записи информации о первом экстремуме в первом блоке регистрации 18 и времени перевода блока 8 в исходное состояние (последнее время чуть больше времени записи), С выхода элемента задержки 21 сигнал с указанной задержкой поступает на

второй вход (S-вход) RS-триггера 31 (ключа 1), а с его выхода на второй вход аналогового ключа 32, открывая его для дальнейшего прохождения сигнала.

Таким образом, ключ 1 автоматически

закрывается на время регистрации сведений об экстремуме.

После регистрации первым блоком регистрации 18 первого экстремума по первой переменной ключ 1 снова подает входной

сигнал на интегратор 2 и на первый переключатель 3 и устройство продолжает исследовать функцию qi(xi) +Ai -xi на последующие экстремумы-минимумы с целью нахождения ее глобального минимума. При

появлении второго экстремума производная -jry-tcnOn) + Ai xi на выходе дифференцирующего блока У Ьеняет знак, вследствие чего на выходе блока 8 появляется управляющий сигнал, который свидетельствует о появлении последующего экстремума. Этот сигнал, поступая на первый вход (R-вход) RS-триггера 31 и с его выхода на второй вход аналогового ключа

32, закрывает аналоговый ключ 32 (закрывает ключ 1), прекращая подачу входного напряжения, и поступает на управляющий

- вход блока сравнения 10. На первый сигнальный вход блока сравнения 10 поступает

значение очередного экстремума функции с выхода сумматора 6, а на второй сигнальный вход - значение предыдущего записанного в первом блоке регистрации 18 (с выхода первого УВХ) экстремума функции (в

данном случае первого экстремума). По сигналу с выхода блока 8 блок сравнения 10 производит сравнение значений, поступающих на его два сигнальных входа. Таким

образом, блок сравнения 10 производит вы- бор глобального минимума из находимых min max экстремумов по команде блока 8. Если найденное значение функции в очередном экстремуме (в данном случае во втором) меньше, чем в предыдущих (в данном 5 случае в первом), то блок сравнения вырабатывает управляющий сигнал, свидетельствующий о .нахождении такого минимума, значение функции в котором меньше, чем в предыдущем (записанном в первом блоке регистрации 18). Этот сигнал с выхода блока

сравнения 10 через первый элемент ИЛИ 11 поступает на первый вход элемента ИЛИ 22, а с его выхода через D-триггер 23 - на первые входы первого, второго и третьего УВХ 24-26. По этому сигналу УВХ 24-26 производят запись значений сигналов, присутствующих на вторых входах УВХ 24-26 для найденного (второго) экстремума (значение аргумента, затрат функции). Таким образом, по сигналу с элемента ИЛИ 11 первый блок регистрации 18 производит запись значений для найденного (второго) экс- тремума аргумента, затрат функции), поступающих на его порвый, второй и третий сигна/.оные входы (аналогично записи значений для первого экстремума). При этом записанная в первом блоке регистрации 18 информация для предыдущего экстремума стирается. Если же значение вновь найденного больше предыдущего, то сигнал перезаписи блок сравнения 10 на выходе не формирует и первый блок регистрации 18 не производит записи информации о найденном минимуме, в нем остается информация о предыдущем минимуме. Таким образом, производится сравнение значения каждого вновь найденного экстремума со значением предыдущего экстремума и меньший из них регистрируется первым блоком регистра- :ции 18. То есть находится глобальный минимум функции q;(xi) + Яч -xi из совокупности находимых ее локальных минимумов, Нахождение глобального минимума функции по переменной x i (аналогична для всех остальных переменных) прои--идится в заданном диапазоне - зменени этой переменной. Верхняя граница изменения xi (которая идет в сторону ее увеличения) задается в пороговой схеме сразнения 9, с помощью которой осуществляется автоматическое определение момента. окончания процедуры поиска глобального экстремума функции по данной переменной (по достижении значения этой переменной своего предельного верхнего уровня). Зна- чение переменной (сначала xi) с выхода интегратора 2 поступает также на вход пороговой схемы сравнения 9, в которой происходит постоянное сравнение текущего значения переменной с ее предельным заданным значением. При достижении значения переменной (сначала xi) предельного уровня (xi Хзадан) пороговая схема сравнения 9 вырабатывается управляющий сигнал, свидетельствующий о необходимости пере- хода к исследованию функции на экстремум по следующей переменной (ха, хз и т.д.). Этот сигнал с выхода пороговой схемы сравнения 9 поступает на первые управляющие входы первого 3 и второго 4 переключателей, переводя их в следующее по порядку положение. Одновременно с этим заданный сигнал поступает на первые входы первого и второго регистраторов 29 и 30 (на первый управляющий вход второго блока регистрации 19). Регистры 29 и 30 производят запись информации на найденном глобальном минимуме по соответствующей переменной (сначала xi, затем Х2 и т.д.), содержащейся в первом блоке регистрации 8 и поступающей с группы его информационных выходов с выхода первого УВХ 24, выхода второго УВХ 25), на сигнальные входы второго блока регистрации 19 (поступающей на входы первого и второго аналого-цифровых преобразователей 27 и 28, а;С;их выходов на входы первого и второго регистров 29, 30). Кроме того, сигналы с выхода пороговой схемы сравнения 9 поступают на первый вход второго элемента ИЛИ 17, с выхода которого сигнал поступает на управляющие входы инте/ратора 2 и накапливающего сумматора 14, устанавливая их в исходное нулевое состояние, и на второй вход элемента ИЛИ 22 (на второй управляющий вход первого блока регистрации 18). С выхода элемента 22 .сигнал поступает на первые входы первого, второго и третьего УВХ 24- 25. По этому сигналу УВХ 24 и 25 выдают информацию о значении глобального экстремума по заданному аргументу и значение этого аргумента (соответствующего экстремуму) - соответственно в первый и второй аналого-цифровой преобразователь 27, 28. Аналого-цифровые преобразователи 27 и 28 осуществляют преобразование аналоговых сигналов-значений экстремума функции и аргумента в цифровые, которые записываются в первый и второй регистры 29 и 30 по сигналу, поступающему из пороговой схемы сравнения 9. Информацию о значении затрат, соответствующих найденному глобальному экстремуму, выдает третье УВХ 26 на вход блока контроля ограничений 15. Кроме того, сигналом, поступающим с выхода второго элемента ИЛИ 17 на второй вход элемента ИЛИ 22, происходит обнуление первого блока регистрации 18.

Таким образом, к началу второго такта работы устройства С помощью сигнала, вырабатываемого пороговой схемой сравнения 9, первый 3 и второй 4 переключатели переведены в следующие по порядку положение (второе), интегратор 2, блок накопления 14, первый блок регистрации 18 (УВХ 24-26 находятся в исходном нулевом состоянии) находятся в исходном нулевом состоянии, во втором блоке регистрации 19 (в первом и втором регистре 29, 30) находится информация о значении глобального экстремума по переменной xi и значении этой переменной, в блоке контроля ограничений 15 находится информация (на аналоговом сумматоре 33) о значении затрат, соответствующем найденному глобальному экстремуму функции qi(xi) + Ai xi аргументу xi.

Во втором такте работы определяется глобальный экстремум функции по переменной Х2 по алгоритму выше описанному для xi.

Таким образом, находятся глобальные экстремумы (минимумы) функции по остальным переменным. Информация о значениях функции, о найденных экстремумах и о значениях аргументов, соответствующих им. регистрируется во втором блоке регистрации (первом и втором регистрах 29, 30) и отображается в блоке отображения 20.

Информация о текущих значениях затрат, соответствующих найденным экстремумам, поступает в блок контроля ограничений 15. На вход блока контроля ограничений 15 (на второй вход аналогового сумматора 32) поступает сигнал, соответствующий текущему значению затрат (при найденном экстремуме). В аналоговом сумматоре 33 все поступающие значения Затрат складываются и постоянно сравниваются с заданным предельным значением затрат D, которые хранятся в узле 34. Выход блока хранения подключен к первому входу аналогового сумматора 33. Таким образом, на каждом шаге происходит сравнение полученного значения затрат

Л djXj Dn заданным D. Если после нахож- 1 1

дения очередного глобального экстремума, предположим по переменной хп, окажется,

что Dn У. djxi D, разностный сигнал с

J-1

выхода аналогового сумматора 33 поступает на вход компаратора 35. Напряжение порога компаратора 35 равно нулю. При на выходе компаратора 35 появляется сигнал, пропорциональный разности Dn-D, который с выхода компаратора 35 поступает на управляющий вход блока 12 задания множителей Лагранжа. Этот сигнал осуществляет коррекцию исходного множителя Лагранжа AL т.е. в сущности выбирает новый множитель Лагранжа Яг в соответствии со значением разности Dn-D. Кроме того, сигнал с выхода компаратора 35 (с выхода блока контроля ограничений 15), поступая на вторые управляющие входы первого переключателя 3 и второго переключателя 4, устанавливает их в исходное положение, поступая на вторые входы первого и второго регистров 29, 30 (поступая на второй управу

ляющий вход второго блока регистрации 19), сбрасывает их в исходное нулевое состояние, и через второй элемент ИЛИ 17, поступая на управляющие входы интегратора 2, накапливающего сумматора 14 и второй вход элемента ИЛИ 22 (второй управляющий вход первого блока регистрации 18), устанавливает их в нулевое состояние.

Таким образом,.сигнал с выхода блока контроля ограничений 15 фактически производит коррекцию, т.е. устанавливает новый множитель Лагранжа и автоматически устанавливает устройство в исходное состояние, происходит возобновление процесса нахождения глобальных экстремумов функции всем переменным, но уже с установленным новым множителем Лагранжа.

Схемно процесс установки нового значения А может реализоваться следующим образом; блок 12 задания множителей Лагранжа реализуется в виде усилителя с изменяющимся коэффициентом усиления. В данном случае коэффициент усиления будет

играть роль А, а управляющие сигналы с выхода блока контроля ограничений будут в соответствии с разностью Dn-D менять этот коэффициент усиления, т.е. устанавливать новые изменения. Процесс установки новых

значений А будет длиться до тех пор, пока не выполнится равенство Dn-D. Но этот процесс будет в отличие от прототи па достаточно коротким, так как новое значениеА может выбираться пропорционально Dn-D, если

эту пропорцию выбрать достаточно точно (при наладке устройства), то процесс нахождения необходимого А можно свести к двум шагам.

Аналогично работает устройство, если

по окончании определения всех оптимальных значений xj (соответствующих глобальным экстремумам) окажется, что Dn-D, в этом случае разность будет меньше нуля, т.е. А будет пропорционально этой разности уменьшаться.

Так как перед каждой установкой нового значения А второй блок регистрации (и первый блок регистрации 18) 19 обнуляется, то в итоге он регистрирует только конечные

оптимальные результаты.

Таким образом, в устройстве достигнута полная автоматизация решаемой задачи нахождения экстремума функции нескольких переменных при заданных ограничениях

путем автоматического переключения первого 3 и второго 4 переключателей, автоматического закрытия и открытия ключа 1, автоматического выбора из множества ло-, кальных экстремумов глобальных режимов

по всем переменным, автоматического выбора множителей Лагранжа, автоматической установки устройства в необходимые исходные состояния (перед началом каждого такта работы и при установке нового зна- чения множителя Лагранжа) и автоматической регистрации и отображения полученных результатов.

Формула, изобретения Устройство для решения задачи Лагранжа, содержащее ключ, интегратор, первый и второй переключатели, К блоков воспроизведения нелинейности, где k - число переменных функции, блок задания множителей Лагранжа, сумматор, дифференцирующий блок, k блоков масштабирования, накапливающий сумматор и блок контроля ограничений, отличающееся тем,ч.то.сцелью увеличения быстродействия, оно содержит блок индикации экстремума, блок порогового сравнения, первый и второй элементы ИЛИ, блок сравнения, первый и второй блоки регистрации приближений, элемент И и элемент задержки, причем информационный вход устройства подключен к информационному входу ключа, выход которого подключен к информационному входу интегратора и к информационному входу первого переключателя, выходы которого подключены соответственно к входам блоков масштабирования, выходы которых под- ключенысоответственно к информационным входам накапливающего сумматора, выход которого подключен к первому информационному входу первого блока регистрации приближений, выходы группы которого подключены соответственно к информационным входам второго блока регистрации приближений, выходы которого подключены соответственно к выходам результата решения устройства, выход интегратора подключен к информационному входу блока порогового сравнения, к информационному входу блока задания коэффициентов Лагранжа, к второму информационному входу первого блока регистрации приближений и к информационному входу второго переключателя,

выходы которого подключены соответственно к входам блоков воспроизведения нелинейности, выходы которых подключены соответственно к информационным рходам 5 группы сумматора, выход которого подключен к третьему информационному входу первого блока регистрации приближений, к первому информационному входу блока сравнения и к входу дифференцирующего

0 блока, выход которого подключен к информационному входу блока индикации экстремума, выход которого подключен к управляющему входу блока индикации экстремума, к входу признака разрешения блр5 ка сравнения, к первому управляющему входу ключа, к входу элемента задержки и к первому входу элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выход которого подключен к перво0 му управляющему входу первого блока регистрации приращений, первый выход которого подключен к первому управляющему входу первого переключателя, к первому управляющему входу второго блока регистра5 ции приращений, к управляющему входу блока задания множителей Лагранжа, к первому управляющему входу второго переключателя и к первому входу второго элемента ИЛИ, выход которого подключен к

0 управляющему входу накапливающего сумматора, к второму управляющему входу первого блока регистрации приращения и к управляющему входу интегратора, выход блока порогового сравнения подключен к

5 второму входу второго элемента ИЛИ, к вторым управляющим входам первого и второго переключателей и к второму управляющему входу второго блока регистрации приращений, выходы элемента за0 держки и блока задания множителей Лагранжа подключены соответственно к второму управляющему входу ключа и к информационному входу сумматора, второй выход первого блока регистрации прираще5 ний подключен к второму входу элемента И и к второму информационному входу блока сравнения, выход которого подключен к второму входу первого элемента ИЛИ.

i On блока 18kB ffwu М,йЛ&

---- f ------- f----

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения задачи оптимального распределения ресурсов | 1986 |

|

SU1341654A1 |

| Устройство для определения экстремумов функций | 1986 |

|

SU1322328A1 |

| Устройство для решения задачи оптимального распределения ресурсов | 1977 |

|

SU674049A1 |

| Устройство для воспроизведения функций | 1982 |

|

SU1126975A1 |

| АДАПТИВНАЯ АНТЕННАЯ РЕШЕТКА | 2000 |

|

RU2207680C2 |

| АНАЛОГОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ НАХОЖДЕНИЯ ЭКСТРЕМУМА ФУНКЦИЙ МНОГИХПЕРЕМЕННЫХ | 1972 |

|

SU326590A1 |

| Устройство для моделирования процесса воспроизводства продукта в экономических системах | 1985 |

|

SU1293740A1 |

| Моментный вентильный электродвигатель с устройством для его настройки | 1987 |

|

SU1661926A1 |

| Устройство для нахождения экстремума аддитивной функции многих переменных | 1990 |

|

SU1765830A1 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

Изобретение относится к вычислительной технике и может быть использовано для решения задачи нелинейного программирования. Целью изобретения является увеличение быстродействия. Устройство содержит ключ 1, интегратор 2, первый переключатель 3, второй переключатель 4, блоки 5i-5k воспроизведения нелинейнд- стеи, сумматор о , дифференцирующий блок 7, блок 8 индикации экстремума, схему сравнения 9, блок сравнения 10, первый элемент ИЛИ 11, блок 12 задания множителей Лагран- жа, блоки масштабирования 13, блок памяти 14, блок 15 контроля ограничений, элемент И 16, второй элемент ИЛИ 17, первый 18 и второй 19 блоки регистрации, блок отображения 20 и элемент задержки 21.4 ил.

I

JJ

L

Фиг.4

55

J5j

| Устройство для решения задачи оптимального распределения ресурсов | 1977 |

|

SU674049A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для определения экстремумов функций | 1986 |

|

SU1322328A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-05-23—Публикация

1990-01-08—Подача