Изобретение относится к вычислительной технике и может быть использовано для исправления ошибок фибоначчиевых 2-ко- дов.

Цель ивобретения - повышение быстродействия.;

Поставленная цель достигается тем, что для случая и , устройство, содержащее с первого по восьмой элементы И, первый и второй элементы ИЛИ, причем выходы второго и третьего элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ, выходы пятого и шестого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ дополнительно содержит с первого по четвертый элементы ИСКЛЮЧАЮЩЕЕ ИЛИ. причем первый вход группы устройства соединен с первыми входами с первого по третий элементы И и является первым выходом группы устройства, второй вход группы которого соединен со вторым входом первого элемента И, с первыми входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с четвертого по шестой элементов И, третий вход группы устройства соединен со вторыми входами со второго по четвертый элементов И, с первыми входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, седьмого и восьмого элементов И, четвертый вход группы устройства соединен с третьими входами первого и второго элементов И, со вторыми входами с пятого по седьмой элементов И, с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, пятый вход группы устройства соединен с третьими входами с третьего по пятый элементов И, со вторым входом восьмого элемента И и с первым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы, с первого по четвертый, элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются соответственно со второго по пятый выходами группы устройства, шестой вход группы которого соединен с третьими входами с шестого по восьмой элементов И и является шестым выходом группы устройства, выходы четвертого и седьмого элементов И соединены со(Л

00 4

g

00

ответственно с третьими входами первого и второго элементов ИЛИ, выходы первого элемента И, первого и второго элементов ИЛИ, восьмого элемента И соединены соответственно со вторыми входами с первого по четвертый элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

Любое натуральное число в п-разряд- нрм фибоначчиевом р-коде представляется в виде многочлена

A-i aspo(S)(1)

гдеа5Ј{0,1}

pp(S}-p - число Фибоначчи (р 0,1,...)

{О при п О 1 при п 0 #V(S-1) + p|j(S-p-1) Метод исправления ошибок в S-м разряде описывается булевой функцией:

(2)

ri(s) a(S-p+i)a(S)a(S+J)

где a(S) двоичный коэффициент S-ro разряда;

) единичный сигнал исправления ошибки типа переход О в Г

i 0,...p-1;J i+1,...p

Сущность изобретения заключается в реализации формулы (2) для р 2 и п 8. Следует отметить, что так как р-младших разряда кода не обрабатываются устройством, то два младших разряда кода из устройства исключены.

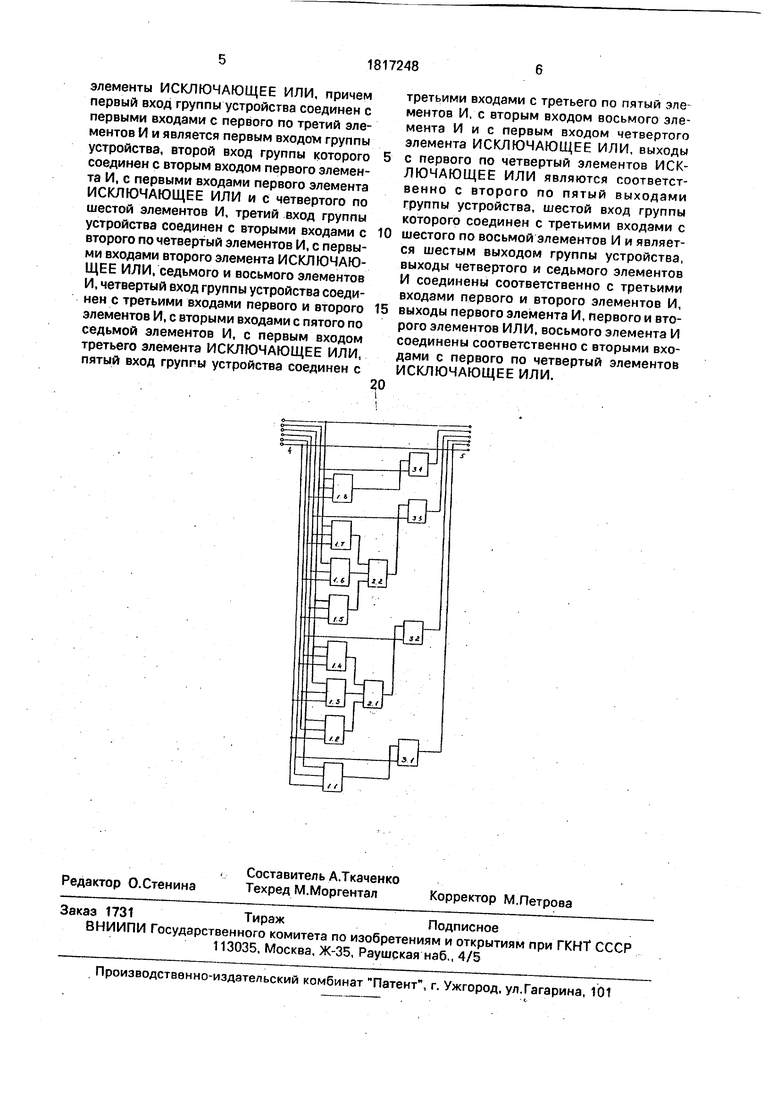

На чертеже изображена схема предлагаемого устройства.

Предлагаемое устройство содержит трехвходовые элементы И 1.1-1.8, элементы ИЛИ 2.1, 2.2, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 3.1-3.4, информационные входы И и информационные выходы 5. Трехвходовые элементы И 1.1-1.8 предназначены для формирования сигналов исправления ошибок, а элементы ИЛ И 2.1,2.2 предназначены для объединения этих сигналов. Элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 3,1-3.4 предназначены для исправления возникших ошибок на входах 4 и формирования верной кодовой комбинации на выходах 5 устройства. Введенные элементы удовлетворяют критерию существенные отличия.

Устройство работает следующим образом. Предположим, что на вход устройства подано представление числа 5 в 2 - коде Фибоначчи-00100100. Эта комбинация, поступая на соответствующие входы элементов И 1.1-1.8 ни в одном случае не дает на выходе элементов И единичного потенциала, т.е. О через элементы ИЛИ 2.1, 2.2 и непосредственно с выходов элементов И 1.1, 1.8 поступает на первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6.1-6.4, на вторые входы которых подаются потенциалы контролируемого кода, которые в этом случае проходят на выход устройства без изменений. Предположим, что в четвертом разряде произошел сбой типа переход О в 1 и кодовая комбинация приняла вид 00110100. В этом случае сработает элемент И 1.1., т.к. на все его входы поданы единич0 ные потенциалы соответственно третьего, шестого и четвертого разрядов. Единичный потенциал с выхода элемента И 1.1 поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3.1, на второй вход которого

5 поступает 1 искаженного четвертого разряда. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3.1 появится нулевой потенциал, который и пройдет на выход устройства, исправив таким образом возникшую ошибку.

0 Аналогично исправляется и сбой в пятом разряде. В этом случае срабатывает элемент И 1.2 и 1 через элемент ИЛИ 2.1 поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3.2, где и исправляет

5 возникшую ошибку пятого разряда. Если же контролируемая кодовая комбинация имела вид 00100010, то сбой пятого разряда вызовет срабатывание элемента И 1.3 и далее аналогично через элемент ИЛИ 2.1 срабаты0 вание элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3.2. Точно также будет исправлен сбой пятого разряда в случае кодовой комбинации 00010010, только в этот раз срабатывает элемент И 1.4.

5 Таким образом, предложенное устройство полностью сохраняет способность известного устройства исправлять часть однократных ошибок типа переход О в 1. Повышение быстродействия достигается за

0 счет уменьшения количества промежуточных элементов.

Предложенное устройство может быть использовано для построения высоконадежных электронных устройств хранения и

5 обработки информации в системах с высокими требованиями по достоверности, а также может быть использовано в системах с высоким уровнем помех.

Формула изобретения

0 Устройство для исправления ошибок 2- кодов Фибоначчи, содержащее с первого по восьмой элементы И, первый и второй элементы ИЛИ, причем выходы второго и третьего элементов И соединены соответственно с

5 первым и вторым входами первого элемента ИЛИ, выходы пятого и шестого элементов И - соответственно с первым и вторым входами второго элемента ИЛИ, отличающееся тем, что, с целью повышения быстродействия, оно содержит с первого по четвертый

элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый вход группы устройства соединен с первыми входами с первого по третий элементов И и является первым входом группы устройства, второй вход группы которого соединен с вторым входом первого элемента И, с первыми входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с четвертого по шестой элементов И, третий вход группы устройства соединен с вторыми входами с второго по четвертый элементов И, с первыми входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, седьмого и восьмого элементов И, четвертый вход группы устройства соединен с третьими входами первого и второго элементов И, с вторыми входами с пятого по седьмой элементов И, с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, пятый вход группы устройства соединен с

третьими входами с третьего по пятый элементов И, с вторым входом восьмого элемента И и с первым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. выходы

с первого по четвертый элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются соответственно с второго по пятый выходами группы устройства, шестой вход группы которого соединен с третьими входами с

шестого по восьмой элементов И и является шестым выходом группы устройства, выходы четвертого и седьмого элементов И соединены соответственно с третьими входами первого и второго элементов И,

выходы первого элемента И, первого и второго элементов ИЛИ, восьмого элемента И соединены соответственно с вторыми входами с первого по четвертый элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК I-КОДОВ ФИБОНАЧЧИ | 1992 |

|

RU2045130C1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОРРЕКТИРУЮЩЕЙ СИСТЕМЕ СЧИСЛЕНИЯ | 1990 |

|

RU2022341C1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК P-КОДОВ ФИБОНАЧЧИ | 1992 |

|

RU2045131C1 |

| Устройство для обнаружения и исправления ошибок | 1987 |

|

SU1578811A1 |

| Устройство для контроля 3-кода Фибоначчи | 1987 |

|

SU1478217A1 |

| УСТРОЙСТВО ДЛЯ ДЕШИФРАЦИИ ФИБОНАЧЧИЕВЫХ P-КОДОВ | 1992 |

|

RU2050691C1 |

| Устройство для контроля 2-кода Фибоначчи | 1988 |

|

SU1662009A1 |

| Синхронный десятичный счетчик | 1989 |

|

SU1661994A1 |

| Устройство для контроля оптимальных Р-кодов Фибоначчи | 1987 |

|

SU1471193A1 |

| Устройство для контроля оптимальных @ -кодов Фибоначчи | 1983 |

|

SU1149261A1 |

Изобретение относится к вычислительной технике и может быть использовано для исправления ошибок. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что устройство дополнительно содержит с первого по четвертый элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и соответствующие связи. Предложен ное устройство может быть использовано для построения высоконадежных электронных устройств хранения и обработки информации в системах с высокими требованиями по достоверности, а также может быть использовано в системах с высоким уровнем помех. 1 ил.

| Стахов А.П | |||

| Введение в алгоритмическую теорию измерения | |||

| - М.: Сов | |||

| радио, 1977, с | |||

| Раздвижной паровозный золотник с подвижными по его скалке поршнями между упорными шайбами | 1922 |

|

SU148A1 |

| Способ сужения чугунных изделий | 1922 |

|

SU38A1 |

| Устройство для исправления однократных ошибок р-кодов Фибоначчи | 1985 |

|

SU1361554A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-05-23—Публикация

1990-05-30—Подача