Изобретение относится к автоматике и вычислительной технике и может быть ис- пользовано в устройствах ввода информации о различных дискретных датчиках в устройство обработки данных или в управляющую вычислительную машину.

Целью изобретения является расширение функциональных возможностей при одновременном повышении достоверности обслуживания.

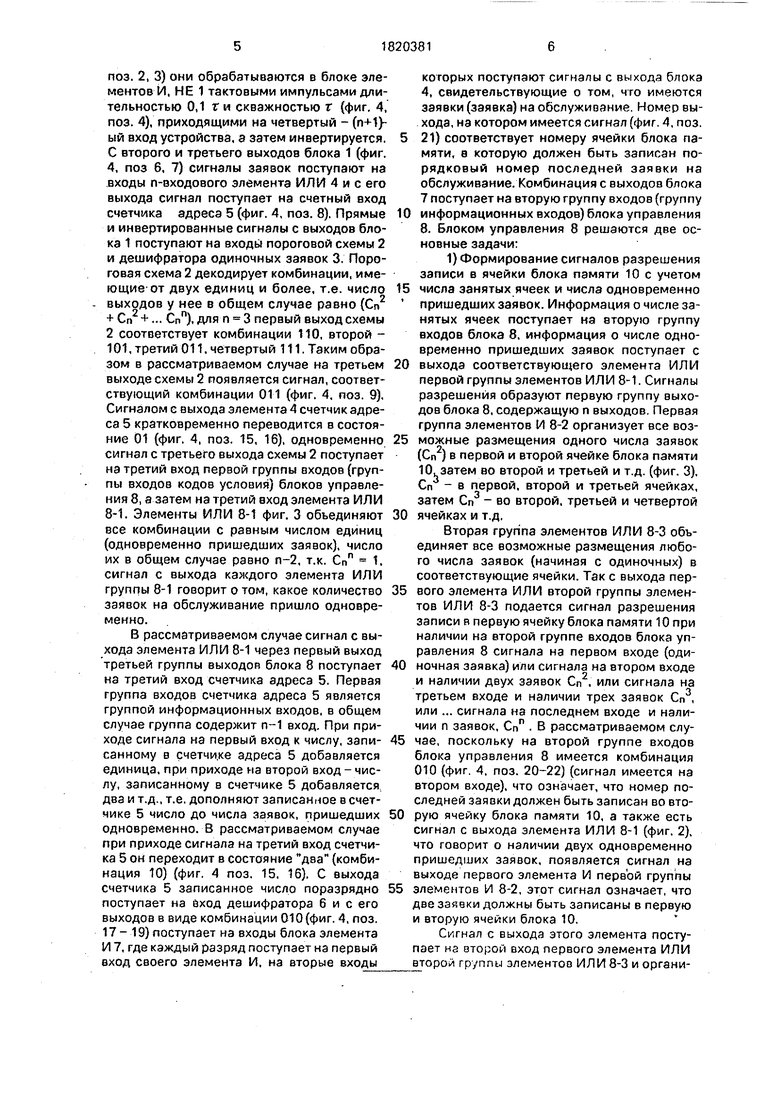

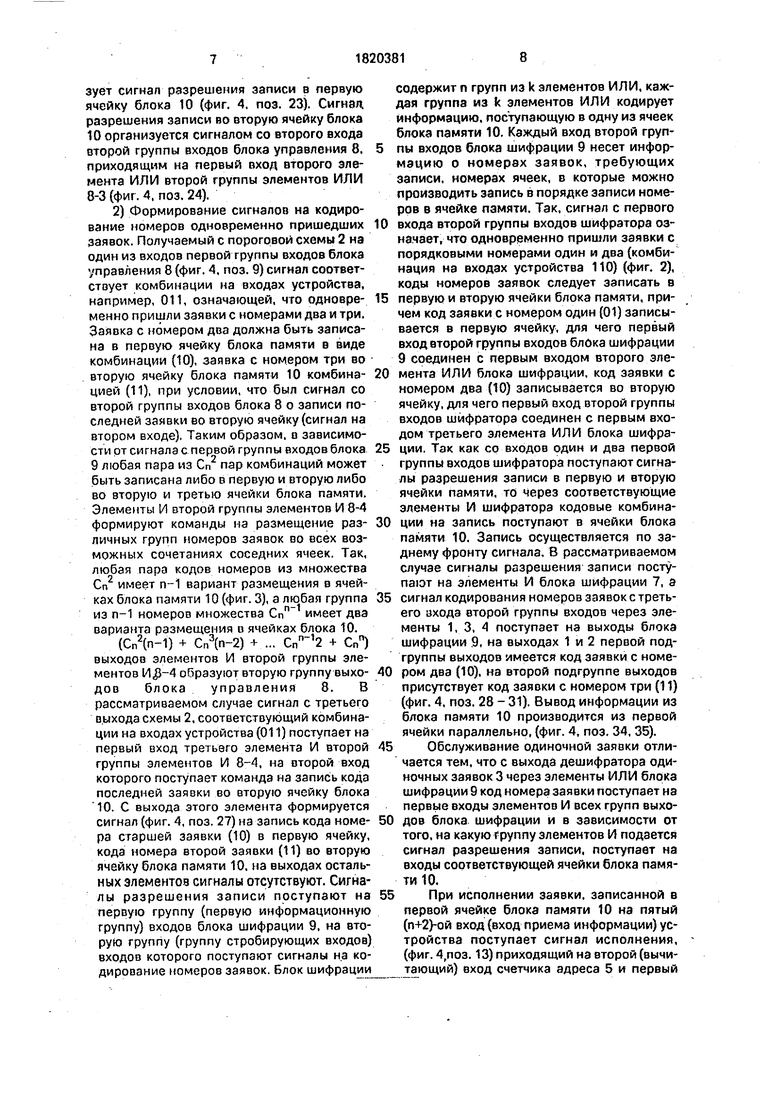

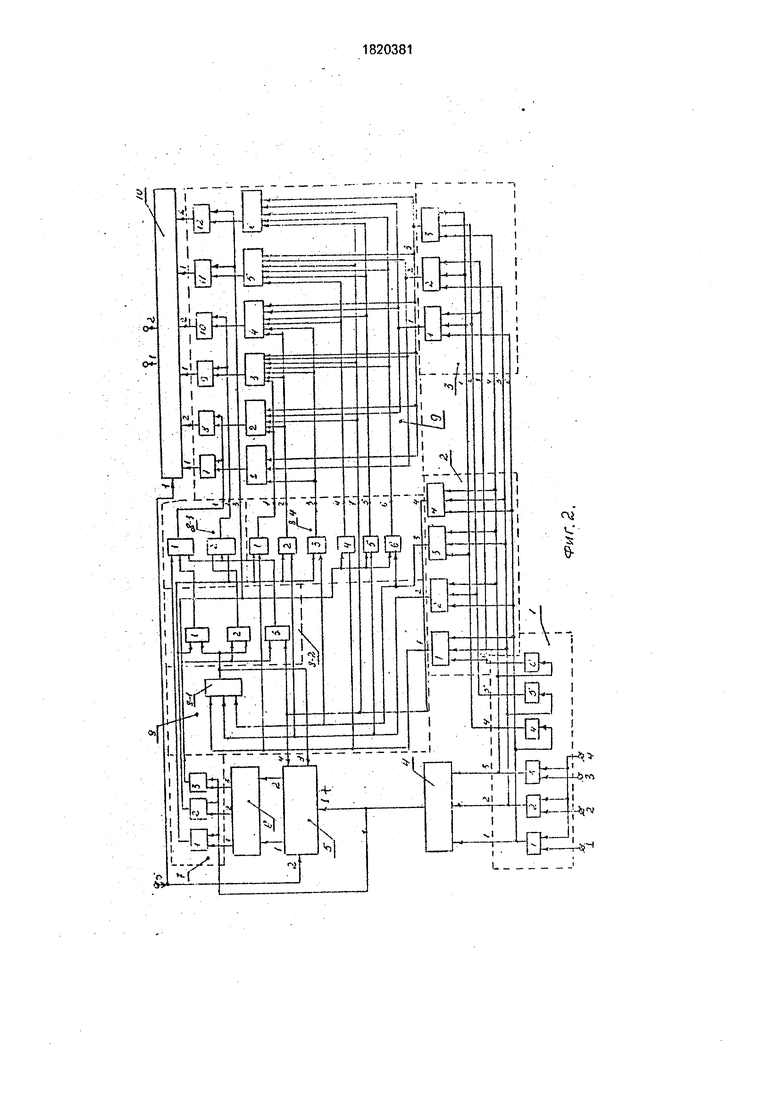

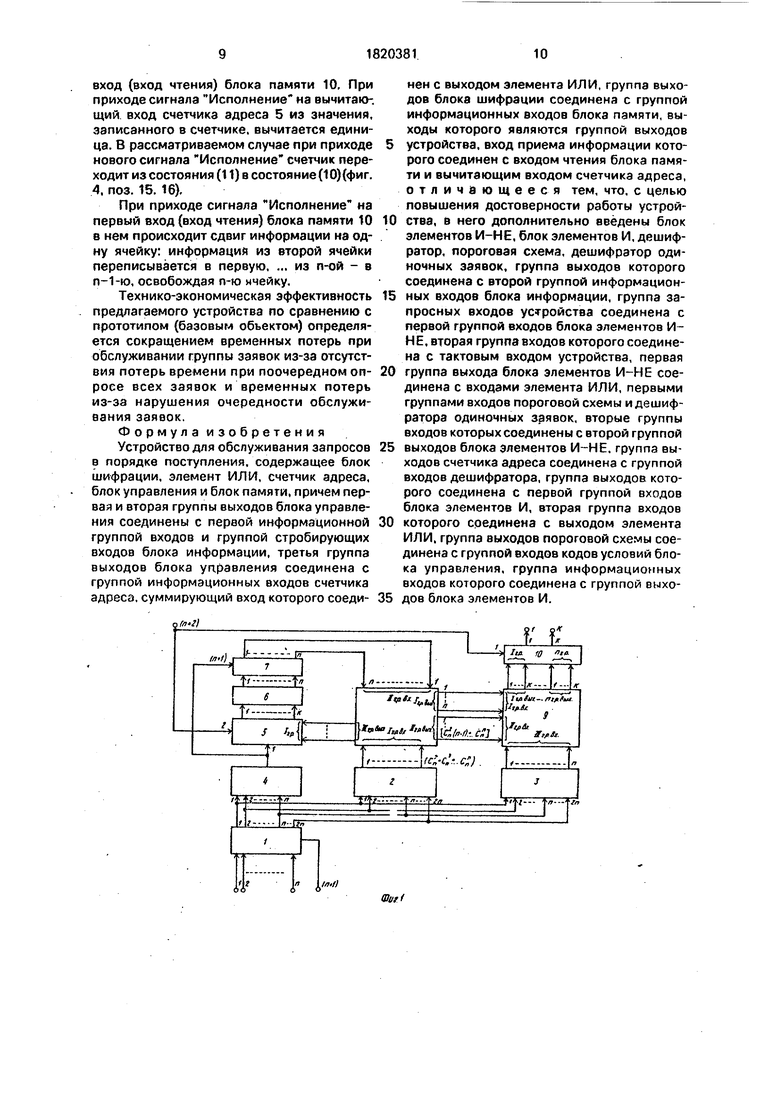

На фиг. 1 приведена структурная схема устройства; на фиг. 2 -функциональная схема устройства для п 3 (число информационных входов) и k 2 (п2 ).

Устройство для обслуживания запросов содержит блок элементов И, НЕ 1, п входов (первая группа входов) которого соединены с соответствующими входами (группой запросных входов) устройства, п выходов(пер- вая группа выходов) блока 1 соединение соответствующими входами элемента ИЛИ 4, все выходы блока 1 (первая и вторая группы выходов) соединены с соответствующими входами (первой и второй группами входов) пороговой схемы 2 и дешифратора одиночных заявок 3, Выходы пороговой схемы 2 соединены с первой группой входов (группой входов кодов условий) блока управления 8, вторая группа входов (группа информационных входов) которого соединена с выходами блока элементов И 7, третья группа выходов соединена с первой группой входов (группой информационных входов) счетчика адреса 5, первая и вторая группы выходов соединены соответственно с первой группой (первой информационной группой) и второй группой (группой строби- рующих входов) входов блока шифрэции 9, третья группа (вторая информационная группа) входов которого соединена с выходами дешифратора одиночных заявок 3, а п групп выходов (группа выходов) соединены с информационными входами блока памяти 10, выходы которого соединены с группой выходов устройства, а первый вход (вход чтения) соединен с n+2-ым входом (входом

(Л

С

м о о

00

«&

приема информации) устройства и со вторым (вычитающим) входом счетчика адреса 5. первый (суммирующий) вход которого соединен с выходом элемента ИЛИ 4 и с п+1- ым входом (второй группой входов) блока элементов И 7, а группа выходов -с группой входов дешифратора 6, выходы которого соединены с первой группой входов блока элементов И 7.

Блок элементов И, НЕ Т (фиг. 2) содержит п элементов И (1,.... п) и п элементов НЕ (n-Н,..., 2п), причем первые входы соответствующих элементов И соединены с группой запросных входов устройства, а вторые входы элементов И соединены с тактовым входом устройства, выходы элементов И соединены с первой группой входов блока и входами соответствующих элементов НЕ, выходы которых соединены со второй группой выходов блока.

Блок элементов И 7 (фиг. 2) содержит п элементов И, первые входы соответствующих элементов соединены с соответствующими входами первой группой входов блока, а вторые входы элементов И соединены с n+1-ым. входом блока (второй группой входов).

Пороговая схема 2 (фиг. 2 содержит (Cn2+Cn3+...Cnn) n-входовых элементов И. Дешифратор одиночных заявок 3 (фиг. 2) содержит п n-входовых Элементов И.

Выходы элементов И являются выходами пороговой схемы И дешифратора, а входы элементов - входами блоков.

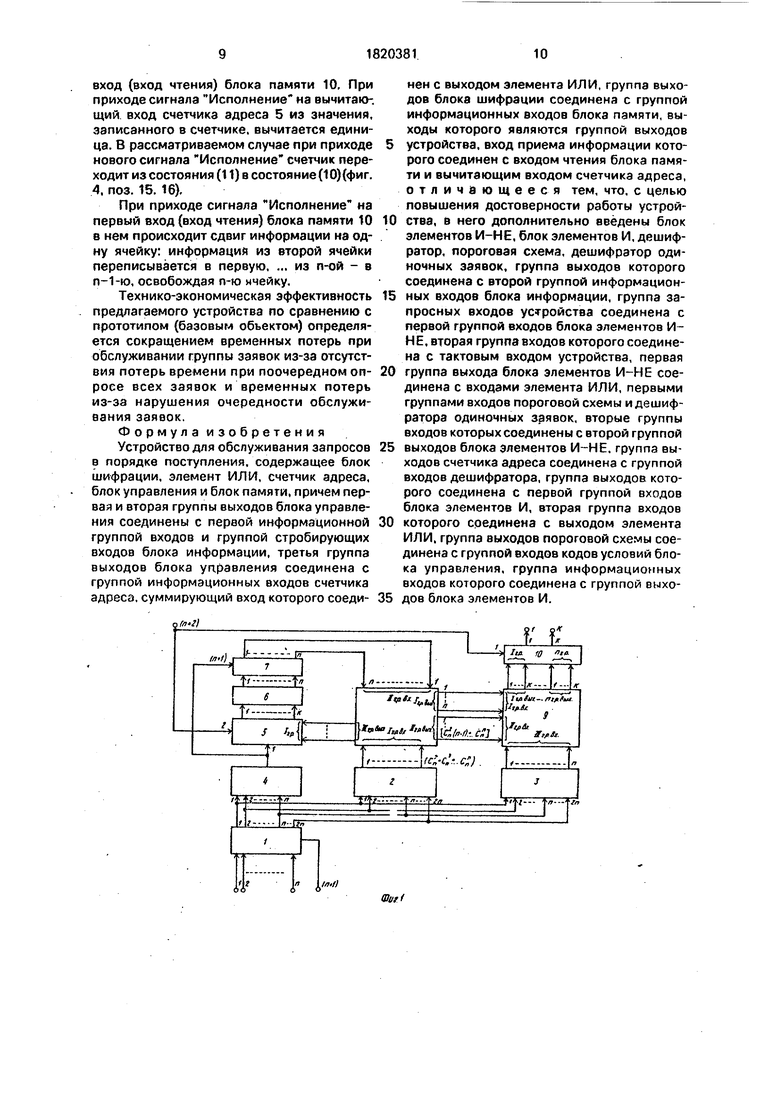

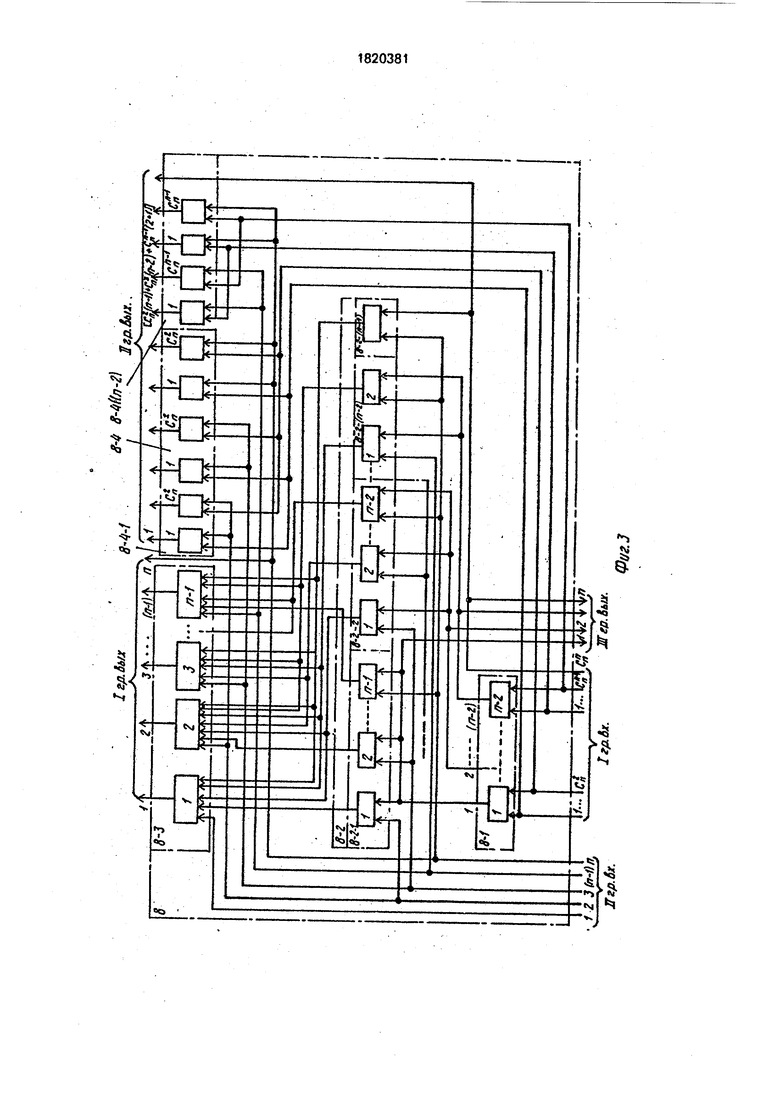

Блок управления 8 (фиг. 3) содержит первую группу многовходовых элементов ИЛИ 8-1, причем входы первого Элемента ИЛИ соединены с соответствующими входами (1,...,Сп2) первой подгруппы первой группы входа (группы входов кодов условий) блока, входы второго элемента ИЛИ соединены с соответствующими входами (1,..., Сп3) второй подгруппы первой группы входов блока и т.д., входы последнего ;(п-2) элемента ИЛИ соединены с соответствующими входами n-2-й подгруппы первой группы входов блока, а выходы первой группы многовходовых элементов ИЛИ соединены с входами первой группы элементов И8-2, со-, держащей {(п-1)+(п-2) + (п-3) + ...1 злемен-- тов И, причем вторые входы первых п-1 элементов И соединены с первым входом 8-1, вторые входы последующих (п-2) элементов И соединены с вторым выходом 8-1 и т.д., а второй выход последнего элемента И соединен с последним входом первой группы входов блока, причем выходы соединены с соответствующими выходами третьей группы выходов блока, последний выход которой соединен с последним входом первой группы входов блока первые входы первых п-1 элементов И 8-2 соединены с 2,3,.. п-ым входами второй группы входов (группы информационных входов) блока

и т.д., первый вход последнего элемента И соединен с n-ым входом второй группы входов блока, вторая группа многовходовых элементов ИЛИ 8-3 содержит п-1 элементов ИЛИ, первые входы элементов ИЛИ

0 (1,...,(п-1)) соединены с соответствующими входами (1,..., (п-1)) второй группы входов, (группы информационных входов) блока, вторые входы 1,2,..., n-Т-гО элементов ИЛИ соединены соответственно с выходами 1,...,

5 (п-1) 8-2, третьи входы элементов ИЛИ 1 и 2 соединены с n-ым выходом 8-2, n+1-ый выход которого соединен с четвертым входом элемента ИЛИ 2 и третьим входом элемента ИЛИ 3 8-3 и т.д., последний выход 8-2 сое0 динен с последними входами элементов ИЛИ (1,..., п-1) 8-3, выходы которого составляют первую группу выходов блока, вторая группа элементов И 8-4 содержит п-1 подгрупп из Сп2 элементов И, п-2 подгрупп из

5 On элементов Иtf т.д., причем в группе8-4-1

первые входы элементов И в каждой подгруппе соединены с соответствующими входами первого элемента ИЛИ 8-t, а вторые входы элементов И 1,2.„(п-1) подгрупп сое0 динены соответственное2,3,..., n-ым входами второй группы входов блока и т.д., второй вход последнего элемента И 8-4 соединен с n-ым входом второй группы входов блока, а первый вход с предпоследним вхо5 дом первой группы входов блока, последний вход первой группы входов блока является последним выходом 8-4, выходы 8-4 организуют вторую группу выходов блока.

Блок шифрации 9 (фиг. 2) содержит kxn

0 многовходовых элементов ИЛИ и kxn элементов И, причем первые группы входов многовходовых элементов ИЛИ соединены

- с входами второй группы входов (группой Стробирующих входов) двоичного шифрато5 ра, а последние группы входов многовходовых элементов соединены с входами третьей группы входов (второй группы информационных входов) блока шифрации, выходы многовходовых элементов ИЛИ соединены

0 с первыми входами соответствующих элементов И. вторые входы которых соединены со входами первой группы (первой информационной группы) входов блока шифрации, а выходы соединены с группой выходов

5 блока шифрации.

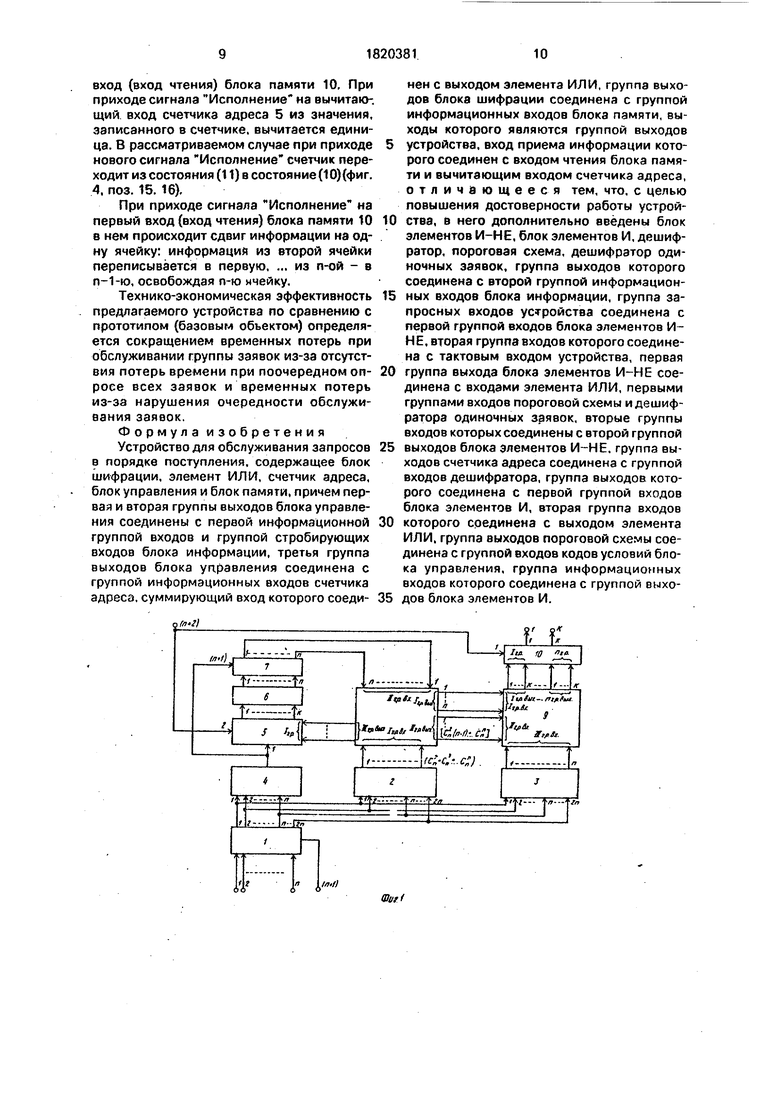

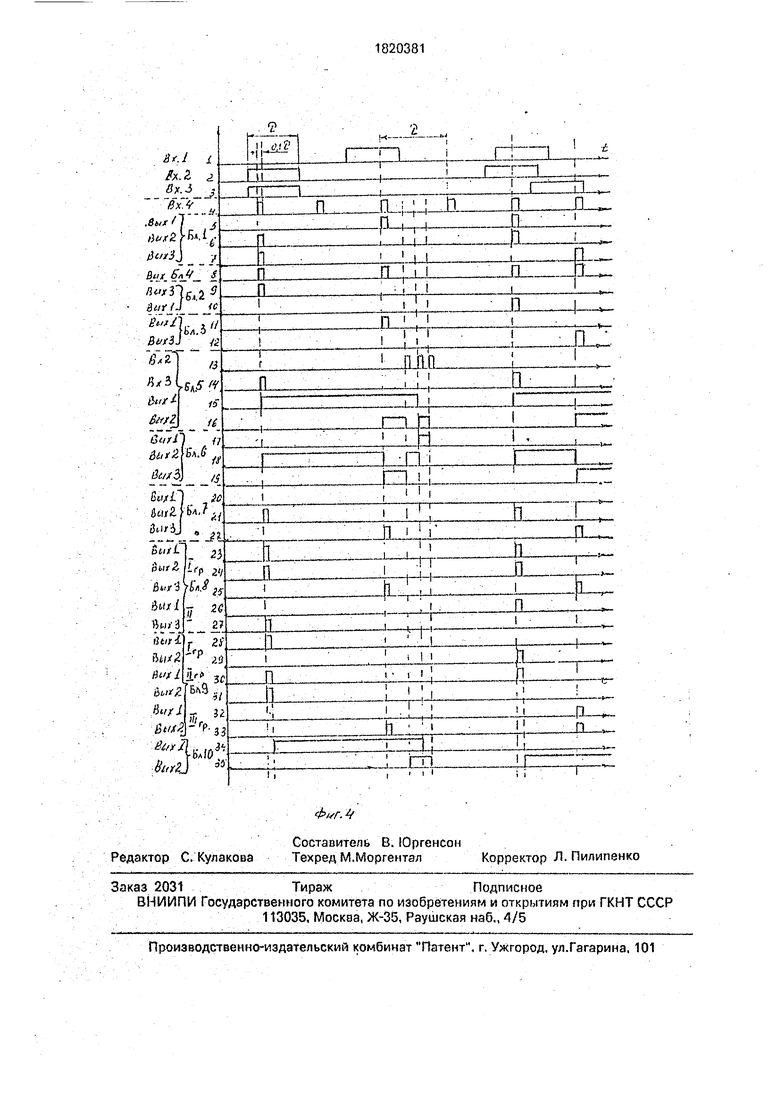

Работа устройства описывается для случая, когда число входов , , (п 2 ) (фиг. 2, фиг. 1, фиг. 3). В случае одновременного прихода заявок на второй и третий входы устройства (комбинация 011) (фиг. 4,

поз. 2, 3) они обрабатываются в блоке элементов И, НЕ 1 тактовыми импульсами длительностью 0,1 г и скважностью г (фиг. 4, поз. 4), приходящими на четвертый - (п+1)- ый вход устройства, а затем инвертируется. С второго и третьего выходов блока 1 (фиг. 4, поз 6, 7) сигналы заявок поступают на .входы n-входового элемента ИЛИ 4 и с его выхода сигнал поступает на счетный вход счетчика адреса 5 (фиг. 4, поз. 8). Прямые и инвертированные сигналы с выходов блока 1 поступают на входы пороговой схемы 2 и дешифратора одиночных заявок 3. Пороговая схема 2 декодирует комбинации, имеющие от двух единиц и более, т.е. число выходов у нее в общем случае равно (Сп2 + Сп2 + ... Сп), для п 3 первый выход схемы 2 соответствует комбинации 110, второй - 101, третий 011, четвертый 111. Таким образом в рассматриваемом случае на третьем выходе схемы 2 появляется сигнал, соответствующий комбинации 011 (фиг. 4, поз. 9), Сигналом е выхода элемента 4 счетчик адреса 5 кратковременно переводится в состояние 01 (фиг. 4, поз. 15, 16), одновременно сигнал с третьего выхода схемы 2 поступает на третий вход первой группы входов (группы входов кодов условия) блоков управления 8, а затем на третий вход элемента ИЛИ 8-1. Элементы ИЛИ 8-1 фиг. 3 объединяют все комбинации с равным числом единиц (одновременно пришедших заявок), число их в общем случае равно п-2, т.к. Спп 1. сигнал с выхода каждого элемента ИЛИ группы 8-1 говорит о том, какое количество заявок на обслуживание пришло одновременно.

В рассматриваемом случае сигнал с выхода элемента ИЛИ 8-1 через первый выход третьей группы выходов блока 8 поступает на третий вход счетчика адреса 5. Первая группа входов счетчика адреса 5 является группой информационных входов, в общем случае группа содержит п-1 вход. При приходе сигнала на первый вход к числу, записанному в счетчике адреса 5 добавляется единица, при приходе на второй вход-числу, записанному в счетчике 5 добавляется, два и т.д., т.е. дополняют записанное в счетчике 5 число до числа заявок, пришедших одновременно. В рассматриваемом случае при приходе сигнала на третий вход счетчика 5 он переходит в состояние два (комбинация 10) (фиг. 4 поз. 15, 16). С выхода счетчика 5 записанное число поразрядно поступает на вход дешифратора бис его выходов в виде комбинации 010 (фиг. 4, поз. 17-19} поступает на входы блока элемента И 7, где каждый разряд поступает на первый вход своего элемента И, на вторые входы

которых поступают сигналы с выхода блока 4, свидетельствующие о том, что имеются заявки (заявка) на обслуживание. Номер выхода, на котором имеется сигнал (фиг. 4, поз. 5 21) соответствует номеру ячейки блока памяти, в которую должен быть записан порядковый номер последней заявки на обслуживание. Комбинация с выходов блока 7 поступает на вторую группу входов (группу 0 информационных входов) блока управления 8. Блоком управления 8 решаются две основные задачи:

1) Формирование сигналов разрешения записи в ячейки блока памяти 10 с учетом 5 числа занятых ячеек и числа одновременно пришедших заявок. Информация о числе занятых ячеек поступает на вторую группу входов блока 8, информация о числе одновременно пришедших заявок поступает с 0 выхода соответствующего элемента ИЛИ первой группы элементов ИЛИ 8-1. Сигналы разрешения образуют первую группу выходов блока 8, содержащую п выходов. Первая группа элементов И 8-2 организует все воз- 5 можные размещения одного числа заявок (Сп2) в первой и второй ячейке блока памяти 10, затем во второй и третьей и т.д. (фиг. 3), Сп - в первой, второй и третьей ячейках, затем Сп3 - во второй, третьей и четвертой 0 ячейках и т.д.

Вторая группа элементов ИЛИ 8-3 объединяет все возможные размещения любого числа заявок (начиная с одиночных) в соответствующие ячейки. Так с выхода пер- 5 вого элемента ИЛИ второй группы элементов ИЛИ 8-3 подается сигнал разрешения записи в первую ячейку блока памяти 10 при наличии на второй группе входов блока управления 8 сигнала на первом входе (оди- 0 ночная заявка) или сигнала на втором входе и наличии двух заявок Сп2, или сигнала на третьем входе и наличии трех заявок Сп3, или ... сигнала на последнем входе и наличии п заявок, Сп11. В рассматриваемом слу- 5 чае, поскольку на второй группе входов блока управления 8 имеется комбинация 010 (фиг. 4, поз. 20-22) (сигнал имеется на втором входе), что означает, что номер последней заявки должен быть записан во вто- 0 рую ячейку блока памяти 10, а также есть сигнал с выхода элемента ИЛИ 8-1 (фиг. 2), что говорит о наличии двух одновременно пришедших заявок, появляется сигнал на выходе первого элемента И первой группы 5 элементов И 8-2, этот сигнал означает, что две заявки должны быть записаны в первую и вторую ячейки блока 10.

Сигнал с выхода этого элемента поступает на второй вход первого элемента ИЛИ второй группы элементов ИЛ И 8-3 и организует сигнал разрешения записи в первую ячейку блока 10 (фиг. 4, поз. 23). Сигнад разрешения записи во вторую ячейку блока 10 организуется сигналом со второго входа второй группы входов блока управления 8. приходящим на первый вход второго элемента ИЛИ второй группы элементов ИЛИ 8-3 (фиг. 4, поз. 24).

2) Формирование сигналов на кодирование номеров одновременно пришедших заявок. Получаемый с пороговой схемы 2 на один из входов первой группы входов блока управления 8 (фиг. 4, поз. 9) сигнал соответствует комбинации на входах устройства, например, 011, означающей, что одновременно пришли заявки с номерами два и три. Заявка с номером два должна быть записана в первую ячейку блока памяти в виде комбинации (10), заявка с номером три во вторую ячейку блока памяти 10 комбинацией (11), при условии, что был сигнал со второй группы входов блока 8 о записи последней заявки во вторую ячейку (сигнал на втором входе). Таким образом, в зависимости от сигнала с первой группы входов блока 9 любая пара из Сп2 пар комбинаций может быть записана либо в первую и вторую либо во вторую и третью ячейки блока памяти. Элементы И второй группы элементов И 8-4 формируют команды на размещение различных групп номеров заявок во всех возможных сочетаниях соседних ячеек. Так, любая пара кодов номеров из множества Сп имеет п-1 вариант размещения в ячейках блока памяти 10 (фиг. 3), а любая группа из п-1 номеров множества имеет два варианта размещения о ячейках блока 10.

(Сп2(п-1) + Сп3(п-2) + ... + Сп°) выходов элементов И второй группы элементов И.8-4 образуют вторую группу выходов блока управления 8. В рассматриваемом случае сигнал с третьего выхода схемы 2, соответствующий комбинации на входах устройства (011) поступает на первый вход третьего элемента И второй группы элементов И 8-4, на второй вход которого поступает команда на запись кода последней заявки во вторую ячейку блока 10. С выхода этого элемента формируется сигнал (фиг. 4, поз. 27) на запись кода номера старшей заявки (10) в первую ячейку, кода номера второй заявки (11) во вторую ячейку блока памяти 10, на выходах остальных элементов сигналы отсутствуют. Сигна- лы разрешения записи поступают на первую группу (первую информационную группу) входов блока шифрации 9, на вторую группу (группу стробирующих входов) входов которого поступают сигналы на кодирование номеров заявок. Блок шифрации

содержит п групп из к элементов ИЛИ, каждая группа из k элементов ИЛИ кодирует информацию, поступающую в одну из ячеек блока памяти 10. Каждый вход второй группы входов блока шифрации 9 несет информацию о номерах заявок, требующих записи, номерах ячеек, в которые можно производить запись в порядке записи номеров в ячейке памяти. Так, сигнал с первого

0 входа второй группы входов шифратора означает, что одновременно пришли заявки с порядковыми номерами один и два (комбинация на входах устройства 110) (фиг. 2), коды номеров заявок следует записать в

5 первую и вторую ячейки блока памяти, причем код заявки с номером один (01) записывается в первую ячейку, для чего первый вход второй группы входов блока шифрации 9 соединен с первым входом второго эле0 мента ИЛИ блока шифрэции, код заявки с номером два (10) записывается во вторую ячейку, для чего первый вход второй группы входов шифратора соединен с первым входом третьего элемента ИЛИ блока шифра5 ции. Так как со входов один и два первой группы входов шифратора поступают сигналы разрешения записи в первую и вторую ячейки памяти, то через соответствующие элементы И шифратора кодовые комбина0 ции на запись поступают в ячейки блока памяти 10. Запись осуществляется по заднему фронту сигнала. В рассматриваемом случае сигналы разрешения записи поступают на элементы И блока шифрации 7, э

5 сигнал кодирования номеров заявок с третьего зхода второй группы входов через элементы 1, 3, 4 поступает на выходы блока шифрации .9, на выходах 1 и 2 первой подгруппы выходов имеется код заявки с номе0 ром два (10), на второй подгруппе выходов присутствует код заявки с номером три (11) (фиг. 4, поз. 28 - 31). Вывод информации из блока памяти 10 производится из первой ячейки параллельно, (фиг. 4, поз. 34, 35).

5 Обслуживание одиночной заявки отличается тем, что с выхода дешифратора одиночных заявок 3 через элементы ИЛИ блока шифрэции 9 код номера заявки поступает на первые входы элементов И всех групп выхо0 дов блока шифрации и в зависимости от того, на какую группу элементов И подается сигнал разрешения записи, поступает на входы соответствующей ячейки блока памяти 10.

5 При исполнении заявки, записанной в первой ячейке блока памяти 10 на пятый (п+2)-ой вход (вход приема информации) устройства поступает сигнал исполнения, (фиг. 4,поз. 13) приходящий на второй (вычитающий) вход счетчика адреса 5 и первый

вход (вход чтения) блока памяти 10. При приходе сигнала Исполнение на вычитаю-, щий вход счетчика адреса 5 из значения, записанного в счетчике, вычитается единица. В рассматриваемом случае при приходе нового сигнала Исполнение счетчик переходит из состояния (11) в состояние (10){фиг. 4. поз. 15. 16),

При приходе сигнала Исполнение на первый вход (вход чтения) блока памяти 10 в нем происходит сдвиг информации на одну ячейку: информации из второй ячейки переписывается в первую, ... из п-ой - в n-1-ю, освобождая n-ю ячейку.

Технико-экономическая эффективность предлагаемого устройства по сравнению с прототипом (базовым объектом) определяется сокращением временных потерь при обслуживании группы заявок из-за отсутствия потерь времени при поочередном опросе всех заявок и временных потерь из-за нарушения очередности обслуживания заявок.

Формул а изо бретени я

Устройство для обслуживания запросов в порядке поступления, содержащее блок тифрации, элемент ИЛИ, счетчик адреса, блок управления и блок памяти, причем первая и вторая группы выходов блока управления соединены с первой информационной группой входов и группой стробирующих входов блока информации, третья группа выходов блока управления соединена с группой информационных входов счетчика адреса, суммирующий вход которого соединен с выходом элемента ИЛИ, группа выходов блока шифрации соединена с группой информационных входов блока памяти, выходы которого являются группой выходов

устройства, вход приема информации которого соединен с входом чтения блока памяти и вычитающим входом счетчика адреса, отличающееся тем, что. с целью повышения достоверности работы устройства, в него дополнительно введены блок элементов И-НЕ, блок элементов И, дешифратор, пороговая схема, дешифратор одиночных заявок, группа выходов которого соединена с второй группой информационных входов блока информации, группа запросных входов устройства соединена с первой группой входов блока элементов И-НЕ, вторая группа входов которого соединена с тактовым входом устройства, первая

группа выхода блока элементов И-НБ соединена с входами элемента ИЛИ, первыми группами входов пороговой схемы и дешифратора одиночных заявок, вторые группы входов которых соединены с второй группой

выходов блока элементов И-НЕ. группа выходов счетчика адреса соединена с группой входов дешифратора, группа выходов которого соединена с первой группой входов блока элементов И, вторая группа входов

которого соединена с выходом элемента ИЛИ. группа выходов пороговой схемы соединена с группой входов кодов условий блока управления, группа информационных входов которого соединена с группой выходов блока элементов И.

Oi

С

5:

О

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Устройство для сопряжения процессоров через общую память в многопроцессорной системе | 1984 |

|

SU1231508A1 |

| Микропроцессорное устройство для моделирования систем массового обслуживания | 1984 |

|

SU1196886A1 |

| Устройство для моделирования систем массового обслуживания | 1990 |

|

SU1709336A1 |

| Многопроцессорная вычислительная система | 1990 |

|

SU1798799A1 |

| СИСТЕМА ЗАЩИТЫ КОНКУРСНЫХ ПРЕДЛОЖЕНИЙ В ГОСУДАРСТВЕННЫХ ЗАКУПКАХ | 2004 |

|

RU2265883C1 |

| Устройство для организации мультиветвления процессов в электронной вычислительной машине | 1980 |

|

SU922743A1 |

| СИСТЕМА УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ДОКУМЕНТООБОРОТОМ ИНФОРМАЦИОННО-МАРКЕТИНГОВОГО ЦЕНТРА | 2004 |

|

RU2260843C1 |

| Устройство для контроля и учета времени работы транспортных средств | 1986 |

|

SU1441430A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах ввода информации о различных дискретных датчиков в устройство обработки данных или в управляющую вычислительную машину. Цель изобретения - повышение достоверности работы устройства. Устройство для обслуживания запросов в порядке поступления содержит блок элементов И-НЁ, блок элементов И, дешифратор, пороговую схему, дешифратор одиночных заявок, блок инф- ракции, элемент ИЛИ, счетчик адреса, блок управления и блок памяти. 4 ил.

t I

rt- I

| Устройство для загрузки данных | 1983 |

|

SU1103236A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обслуживания запросов | 1985 |

|

SU1264174A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-06-07—Публикация

1990-12-13—Подача