О) 4

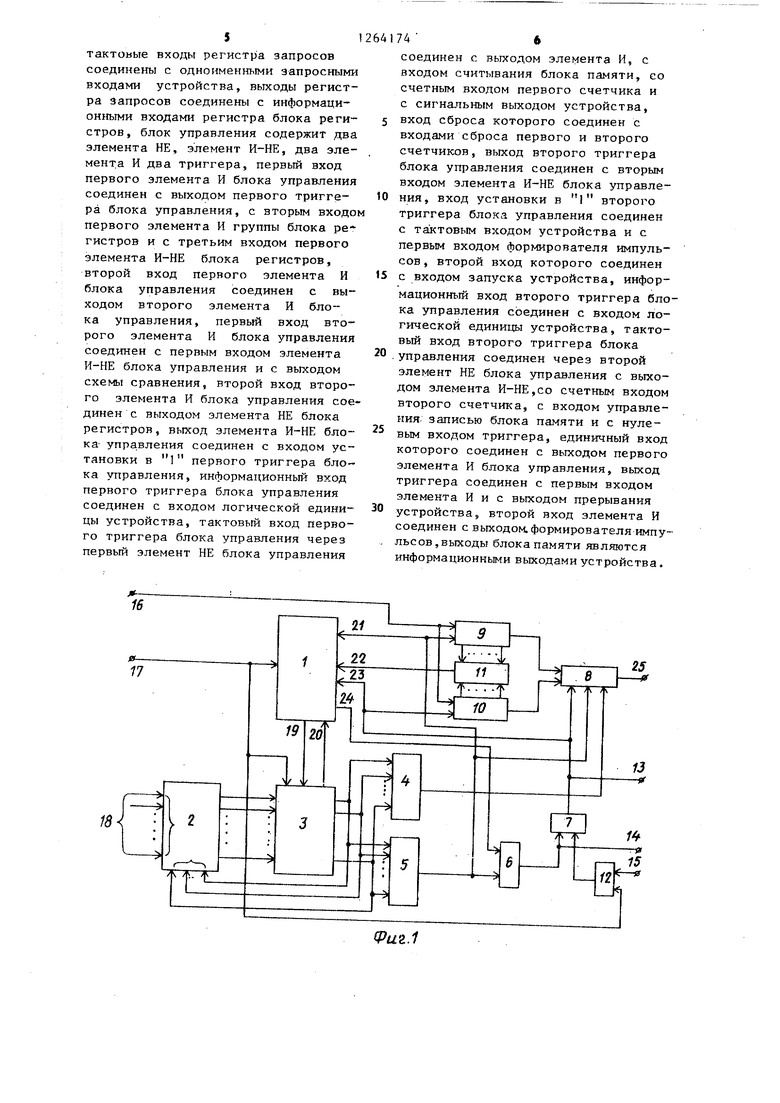

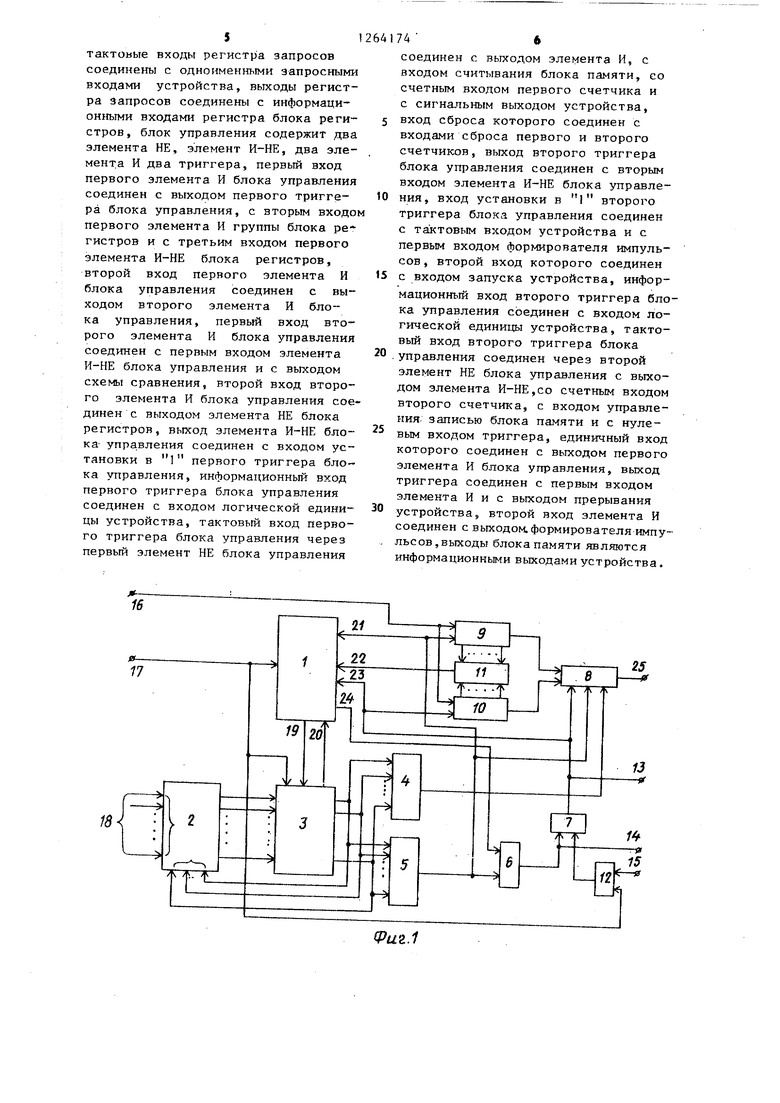

. Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах ввода информации от различных дискретных датчиков в устройство обрабо ки данных или в управляющую вычислительную маишну. Цель изобретения - увеличение достоверности обслуживания заявок за счет уменьшения вероятности i-rx потерь. На фиг.1 приведена структурная схема устройства; на фиг.2 - структурная схема блока управления; на фиг.З - структурная схема блока регистра. Устройство (ф1Т. ) содержит блок 1 управления, регистр 2 запросов с триггерами 2-1...2-h, блок 3 регистров, шифратор 4, элемент И-НЕ 5, триггер 6, элемент И 7, блок 8 памя ти, счетчик 9, счетчик 10 адреса, схему 11 сравнения, формирователь 12 импульсов, сигнальный выход .13 устройства, выход 14 прерывания устройства, вход 5 запуска, вход 16Ьбросаустройства, тактовьм вход 17устройства, группу запросных вхо дов 18 устройства, входы и выход 19-24 блока 1, группу информационны выходов 15 устройства. Блок 1 управления (,2) содержит элементы НЕ 26 и 27, элемент ИНЕ 28, триггеры 29 и 30, элемент 1 И 31 и 32. Блок 3 (фиг.З) содержит триггеры 33 регистра, элементы И 34, элементы И-НЕ 35 группы, элемент НЕ 36„ Устройство работает следующим об разом В случае одновременного поступле ния сигналов Запрос прерываний от внешних устройств. на входы 18 вхо ные триггеры 2- и прерываний регистра 2 переходят в состояние О Уровень О поступает на соответствующие триггеры 33. Ближайшим так том, поступающим с входа 17 устройс ва, триггеры 33 переходят в состояHjfe О. Ближайшим тактом с выхода элемента НЕ 36 формируется импульс отрицательной полярности. Этим импульсом входной триггер прерываний 2-1 переводится в состояние 1 С выхода элемента И-НЕ 35-2 в этот мо мент импульс не формируется, так ка на его третий вход с прямого выхода триггера 33-1 через элемент И 34-1 поступает сигнал зйпрета, который через элемент И-34-2 присутствует на всех последующих элементах И-НЕ 35. Кмпульс с выхода элемента И-НЕ 35-1 поступает на вход дешифратора 4,в котором осуществляется кодиро-: вание первого вектора прерываний в виде двоичного кода, поступающего на информационные входы блока 28. Через элемент М-НЕ 5 импульс с выхода элемента И-НЕ 35-1 осуществляет запись в блок В по адресу, формируемому счетчиком 9, информации кода вектора прерываний с выходов шифратора 4. В исходное состояние счетчики 9 и 10 устанавливаются сигналом, поступающим с входа 16. Поэтому первый вектор запроса прерываний записывается по ну.тгевому адресу в блок 8. При последующих опросах этот вектор может быть записан по любому адресу. Текущий адрес записи с выхода счетчика 9 поступает на входы блока 8. Задним фронтом импульса сигнала, поступакэщего с выхода элемента И-НЕ 5,триггер 6 устанавливается В состояние 1 и подготавливает элемент И 7 к прохождению сигнала. Одновременно осугчествляется суммирование в счетчике 10 адреса (запись . Следующим тактом триггер 33-1 привязки переводится в исходное состояние, чем снимается запрет входа элемента И 34-1, и он формирует на третьем входе элемента И-НЕ 35-2 сигнал разрешения, позволяющий сформировать отрицательный импульс, поступающий на вторые входы шифратора 4 и элемента И-НЕ 5 для формирования кода второго вектора прерываний и второго сигнала записи. По сигналу Запись в очередную ячейку блока 8 по адресу, сформированному счетчиком 9, записывается новый вектор прерываний. Так как в данном примере сигналы Разрешение прерываний следуют за первым и вторым сигналами Запись, то поступая на второй вход элемента И 7, на первый вход которого поступает сигнал ращрешения от триггера 6, они формируют на выходе элемента И 7 сигналы Считывание. .При этом с выходов счетчика 10 адрес ячейки, по которому будет считываться вектор прерываний, поступает в блок 8. На-выходах блока 8,

3

т.е. на выходах 25 устройства, появляется вектор прерываний, по которому будет осуществляться очередное прерывание. Задн11М фронтом импульса Считывание осуществляется суммирование в счетчике 10. Указанный режим является нормалъньм режимом функционирования устройства.

Если после очередного сигнала считывания числа, записанные в счет чик 9 Ив счетчик 10 адреса, (из блока 8 считан последний вектор прерывания), то на выходе схемы 11 появляется сигнал равенства, поступающий на первый вход элемента И 31 блока. 1 и разрешающий прохождение на первый вход элемента И 32 импульсов. Элемент И 32, имея на своем входе разрешающий сигнал с выход триггера 30, пропускает тактовые импульсы на вход сброса триггера 6,переводя его в положение О.Таким об.разом,с выхода триггера 6 на первый вход элемента И 7 поступает сигнал, запрещающий формирование сигнала Счтьгеание до прихода первого сигнала Запись. Если после очередного сигнала Запись числа, записанные в счетчики 9 и 10, равны, то блок 1 формирует со своего выхода 19 сигнал, запрещающий прохождение сигналов Запись.

Формирование сигнала Запрет

производится следующим образом. Триггер 29 сдвигает последний сигнал Запись, синхронизируя его. Сдвиг производится для исключения срабатывания триггера 30 в режиме нормального функционирования устройства. Сдвинутый сигнал Запись инвертируется и проходит через элемент И-НЕ 28, на первый вход которо го поступает разрещающий сигнал с входа 22 блока 1 на единичный вход триггера 30 и, так как на С-входе триггера 30 сигнал Считывание отсутствует , то триггер переключается и с его инверсного выхода в блок 3 поступает сигнал запрета формирования импульса записи. При приходе очередного сигнала Считывание задний фронт сигнала возвращает тригге 30 в исходное состояние и разрешает формирование сигнала Запись .

744

Формула изобретения

Устройство для обслуживания запросов, содержащее шифратор, элемент И-НЕ, два счетчика, схему сравнения и блок памяти, причем первая и вторая группы входов схемы сравнения соединены с первыми группами выходов первого и второго счетчиков, вторые группы выходов первого и второго счетчиков соединены соответственно с группой входов записи и группой входов адреса считывания блока памяти, группа выходов шифратора соединена с группой информационных входов блока памяти, отличающееся тем, что, с целью увеличения достоверности обслуживания заявок за счет уменьшения вероятности их потерь, устройство содержит регистр запросов, блок управления, блок регистров, элемент И-НЕ, триггер, элемент И и формирователь импульсов, причем блок регистров содержит регистр, группу элементов И, группу элементов И-НЕ и элемент НЕ, причем в блоке регистров прямые выходы регистра соединены с первыми вхрдами одноименных элементов И группы, выход каждого i-ro (,...,п-1,где - число запросов) элемента И группы соединен с вторым входом 1+1-го элемента И группы с первым входом i+l-ro элемента И группы и с первым входом i+1-го элемента И-НЕ группы, инверсные выходы разрядов регистра, начиная с второго, соединены с вторыми входами одноименных элементов И-НЕ группы, инверсный выход первого ра.зряда регистра соединен с первым входом первого элемента И-НЕ группы, второй вход последнего элемента И-НЕ группы соединен с выхоом последнего элемента И группы, тактовый вход устройства через элемент НЕ соединен с вторым входом первого элемента И-НЕ группы и с третьими входами остальных элементов И-НЕ группы, тактовые входы разрядов регистра блока регистров соединены с тактовым входом устройтва, выходы элементов И-НЕ группы оединены с входами установки в 1 дноименных разрядов регистра эапроов, с входами шифратора и с входаи элемента И-НЕ, информационные ходы регистра запросов соединены с ходом логического нуля устройства,; 51 тактовые входы регистра запросов соединены с одноименными запросными входами устройства, выходы регистра запросов соединены с информационными входами регистра блока регистров, блок управления содержит два элемента НЕ, элемент И-НЕ, два элемент.а И два триггера, первый вход первого элемента И блока управления соединен с выходом первого триггера блока управления, с вторым входо первого элемента И группы блока ре- гистров и с третьим входом первого элемента И-НЕ блока регистров, второй вход первого элемента И блока управления соединен с выходом второго элемента И блока управления, первый вход второго элемента И блока управления соединен с первым входом элемента И-НЕ блока управления и с выходом схемы сравнения, второй вход второго элемента И блока управления сое динен с выходом элемента НЕ блока регистров, выход элемента И-НЕ блока- упра.вления соединен с входом установки в 1 первого триггера блока управления, информационный вход первого триггера блока управления соединен с входом логической единицы устройства, тактовый вход перво го триггера блока управления через первый элемент НЕ блока управления 4 соединен с выходом элемента И, с входом считывания блока памяти, со счетным входом первого счетчика и с сигнальным выходом устройства, вход сброса которого соединен с входами сброса первого и второго счетчиков, выход второго триггера блока управления соединен с вторым входом элемента И-НЕ блока управления, вход установки в I второго триггера блока управления соединен с тактовым входом устройства и с первым входом формирователя импульсов , второй вход которого соединен с входом запуска устройства, информационный вход второго триггера блока управления соединен с входом логической единицы устройства, тактовый вход второго триггера блока .управления соединен через второй элемент НЕ блока управления с выходом элемента И-НЕ,со счетным входом второго счетчика, с входом управления, записью блока памяти и с нулевым входом триггера, единичный вход которого соединен с выходом первого элемента И блока управления, выход триггера соединен с первым входом элемента И и с выходом прерывания устройства, второй вход элемента И соединен с выходом, формирователя импульсов, выходы блока памяти являются информационными выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обслуживания запросов | 1988 |

|

SU1550517A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для сопряжения ЭВМ с синхронными каналами передачи данных | 1986 |

|

SU1347083A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1376084A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

Изобретение относится к вычислительной технике и может быть ис полызовано в устройствах ввода информации от различных дискретных датчиков в устройство обработки данных. Цель изобретения - увеличение достоверности обслуживания заявок за счет уменьшения вероятности их потерь. Устройство для обслуживания запросов содержит блок управления, регистр запросов, блок регистров, шифратор, триггер,элементы И, И-НЕ, блок памяти, счетчик, счетчик адреса, схему сравнения, формирователь импульсов. В шифраторе осуществляется кодирование первого вектора прерывания в виде двоичного кода, который записывается в блок памяти по адресу, формируемому счетчиком. Считывание из блока памяти производится по адресу счетчика адреса. (Л 3 ил.

(Риг.1

| СПОСОБ ПРИГОТОВЛЕНИЯ СИНТЕТИЧЕСКОГО КАУЧУКА | 1916 |

|

SU1103A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для организации очереди | 1979 |

|

SU834701A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-15—Публикация

1985-01-02—Подача