обеспечения селекции информации на входах устройства отдельно для каждого приемника информации. Устройство содержит накопители 1, - 1„(где п - число приемников информантки) , каждый из которых разделен на секции 2о-2, (где m - число параметров, упаковываемых в одну ячейку памяти накопителя 1)s счетчики 3„ адреса записи, счетчики 4,- 4, адреса чтения5 коммутатор 5, разделенный ни секции би-буп., 5 регистр 7 данных с .информационными входами 8j,-8rp,i уст ройства; группу коммутаторов 9, -9,, с информационными выходами 10,-10 устройстваJ коммутатор 11, блок управления выбором накопителя с выходами 12,-12 , элементы ИЛИ 14, 15, триггер со входом признака длины входного слова, две матрицы элементо И, группу коммутаторов,.две группы счетчиков параметров, суммирующие счетчики сдвигов, мультиплексоры.

1 .

Изобретение относится к вычисли- тельной технике и может быть использовано для построения буферных запог минающих устройств, применяемых в каналах ввода измерительных парамет ров в системы обработки данных.

Целью изобретения является расширение области применения устройства за счет обеспечения селекции информации на входах устройства отдельно для каждого приемника информации.

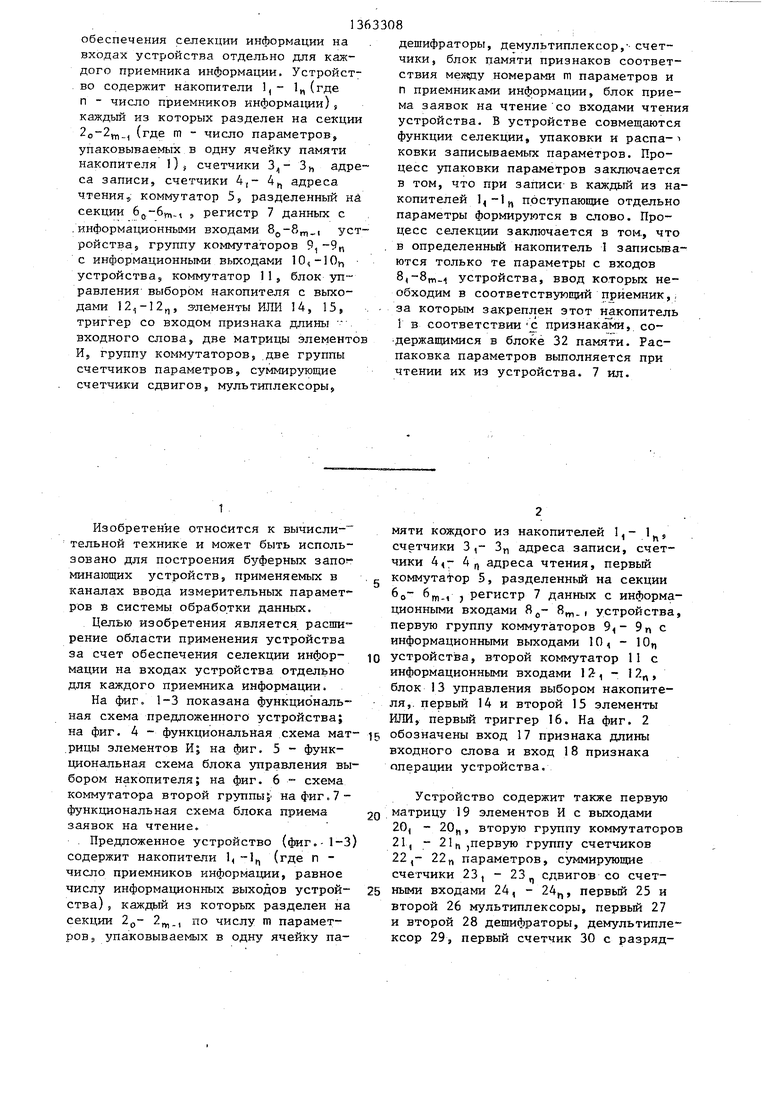

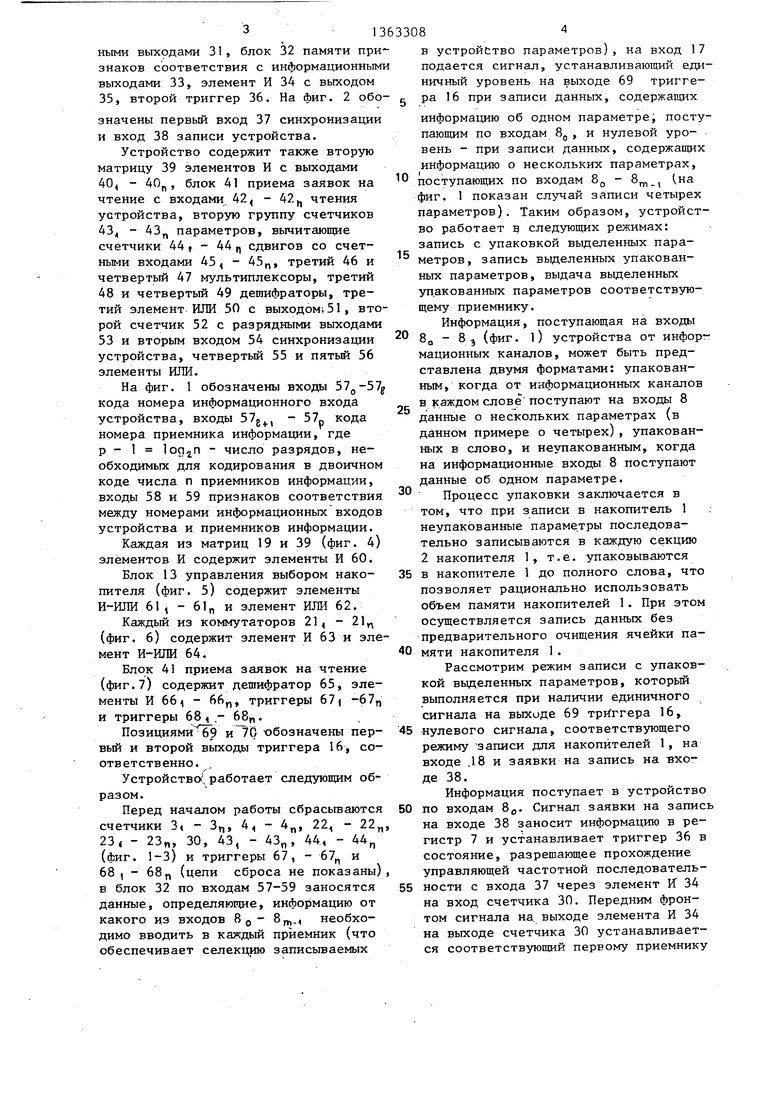

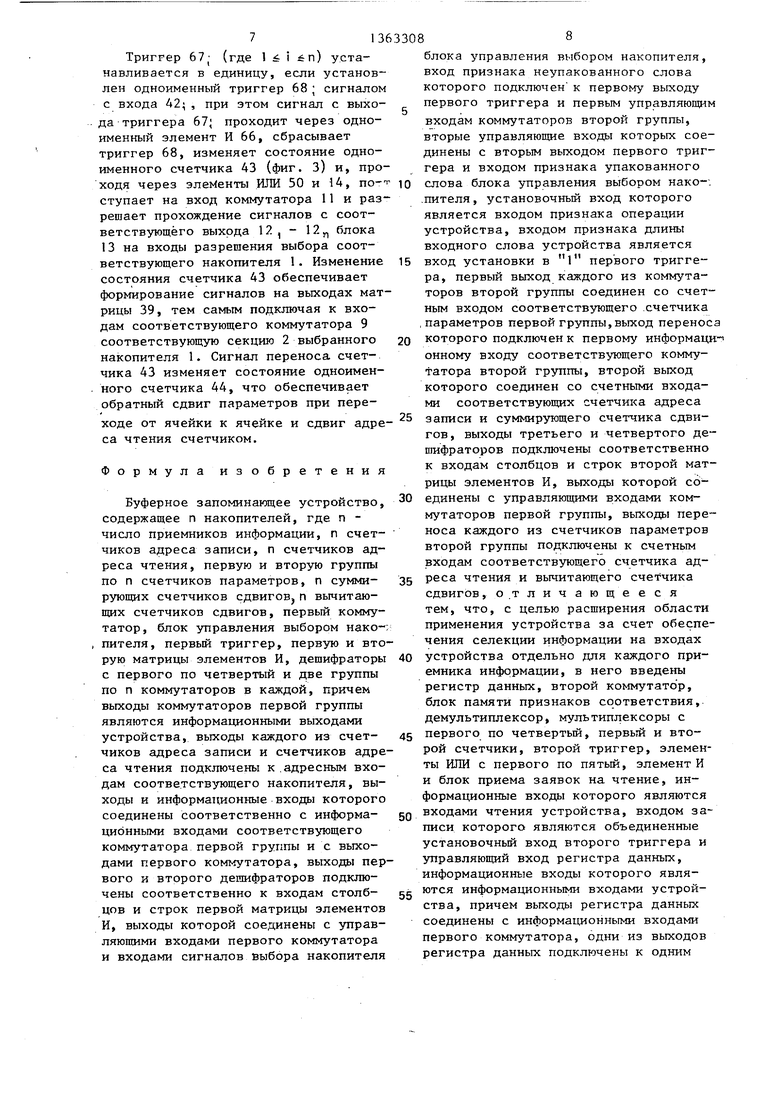

На фиг. 1-3 показана функциональная схема предложенного устройства; на фиг. 4 - функциональная схема матрицы элементов И| на фиг. 5 - функциональная схема блока управления выбором накопителя; на фиг. 6 - схема коммутатора второй группы на фиг. 7- функциональная схема блока приема заявок на чтение.

. Предложенное устройство (фиг.- 1-3 содержит накопители Ь -1 (где п - число приемников информации, равное числу информационных выходов устройства) S каждый из которых разделен на секции 2., по числу m параметров j упаковываемых в одну ячейку падешифраторы, демультиплексор,-- счетчики, блок памяти признаков соответствия между номерами m параметров и п приемниками информации, блок приема заявок на чтение со входами чтения устройства. В устройстве совмещаются функции селекции, упаковки и распа- ковки записываемых параметров. Процесс упаковки параметров заключается в том, что при записи в каждый из накопителей II-IH поступающие отдельно параметры формируются в слово. Процесс селекции заключается в том., что в определенный накопитель 1 записьша- ются только те параметры с входов 8,-8 устройства, ввод которых необходим в соответствующий приемник,, за которым закреплен этот накопитель 1 в соответствии С признаками, со- держащимнся в блоке 32 памяти. Распаковка параметров выполняется при чтении их из устройства. 7 ил.

мяти кождого из накопителей 1,- 1, счетчики 3,- 3„ адреса записи, счетчики 4„ адреса чтения, первый

коммутатор 5, разделенный на секции 6о 6, J регистр 7 данных с информационными входами Яд- 8.1 устройства, первую группу коммутаторов 9 п с информационными выходами 10, - 10

устройства, второй коммутатор II с информационными входами 12-, - 12„, блок 13 управления выбором накопителя,, первый 14 и второй 15 элементы ИЛИ, первый триггер 16. На фиг. 2

обозначены вход 17 признака длины входного слова и вход 18 признака операции устройства.

Устройство содержит также первую матрицу 19 элементов И с выходами

20,- 20„, вторую группу коммутаторов

21,- 2If, ,первую группу счетчиков 22,- 22п параметров, суммирующие счетчики 23, - 23 сдвигов со счетными входами 24, - 24,, первый 25 и второй 26 мультиплексоры, первый 27 и второй 28 дешифраторы, демультиплексор 29, первый счетчик 30 с разрядными выходами 31, блок 32 памяти признаков соответствия с информационным выходами 33, элемент И ЗА с выходом 35, второй триггер 36. На фиг. 2 обозначены первый вход 37 синхронизации и вход 38 записи устройства.

Устройство содержит также вторую матрицу 39 элементов И с выходами 40, - 40, блок 41 приема заявок на чтение с входами 42, - 42 j, чтения устройства, вторую группу счетчиков 43, - 43 параметров, вычитающие счетчики 44 - 44 | сдвигов со счетными входами 45, - 45„, третий 46 и четвертый 47 мультиплексоры, третий 48 и четвертый 49 дешифраторы, третий элементИПИ 50 с выходом; 51, второй счетчик 52 с разрядными выходами 53 и вторым входом 54 синхронизации устройства, четвертый 55 и пятый 56 элементы ИЛИ.

На фиг. 1 обозначены входы кода номера информационного входа устройства, входы 57g, р °ДЗ номера приемника информации, где р - 1 Ioci2.n - число разрядов, необходимых для кодирования в двоичном коде числа п приемников информации, входы 58 и 59 признаков соответствия между номерами информационных входов устройства и приемников информации.

Каждая из матриц 19 и 39 (фиг. 4) элементов И содержит элементы И 60.

Блок 13 управления выбором накопителя (фиг. 5) содержит элементы И-ИЛИ 61, - 61„ и элемент ИЛИ 62.

Каждый из коммутаторов 21, - 21 у, (фиг. 6) содержит элемент И 63 и элемент И-ИЛИ 64.

Блок 4 приема заявок на чтение (фиг.7) содержит дешифратор 65, элементы И 665 - 66„, триггеры 67( -67п и триггеры 68,.- 68р.

Позициями обозначены первый и второй выходы триггера 16, соответственно.

Устройство/, работает следующим образом.

Перед началом работы сбрасьгааются счетчики 3, - Зп, 4, - 4„, 22, - 22„ 23 - 23„, 30, 43, - 43„, 44, - 44 (фиг. 1-3) и триггеры 67, - 67 и 68 , - б8„ (цепи сброса не показаны) в блок 32 по входам 57-59 заносятся данные, определяющие, информацию от какого из входов 8., необходимо вводить в каждый приемник (что обеспечивает селекцию записываемых

0

5

0

в устройство параметров), на вход 17 подается сигнал, устанавливающий единичный уровень на выходе 69 триггера 16 при записи данных, содержащих

информацию об одном параметре, поступающим по входам 8д, и нулевой уровень - при записи данных, содержащих информацию о нескольких параметрах, поступающих по входам 8д - 8, .на фиг. 1 показан случай записи четырех параметров). Таким образом, устройство работает ч следующих режимах: запись с упаковкой вьщеленных параметров, запись вьщеленных упакованных параметров, выдача вьщеленных упакованных параметров соответствующему приемнику.

Информация, поступающая на входы

5

0

5

0

5

5

8 8 (фиг. О устройства от инфорг мационных каналов, может быть представлена двумя форматами: упакованным, когда от информационных каналов в каждом слове поступают на входы 8 данные о нескольких параметрах (в данном примере о четырех), упакованных в слово, и неупакованным, когда на информационные входы 8 поступают данные об одном параметре.

Процесс упаковки заключается в том, что при записи в накопитель 1 неупакованные параметры последовательно записываются в каждую секцию 2 накопителя 1, т.е. упаковываются в накопителе 1 до полного слова, что позволяет рационально использовать объем памяти накопителей 1. При этом осуществляется запись данных без предварительного очищения ячейки памяти накопителя 1.

Рассмотрим режим записи с упаковкой вьщеленных параметров, которьй выполняется при наличии единичного сигнала на выходе 69 триггера 16, нулевого сигнала, соответствующего режиму -записи для накопителей 1, на входе ,18 и заявки на запись на входе 38.

Информация поступает в устройство 0 по входам Qg, Сигнал заявки на запись на входе 38 заносит информацию в регистр 7 и устанавливает триггер 36 в состояние, разрешающее прохождение управляющей частотной последовательности с входа 37 через элемент И 34 на вход счетчика 30. Передним фронтом сигнала на. выходе элемента И 34 на выходе счетчика 30 устанавливается соответствуюший первому приемнику

информации код, который поступает на управляющие входы демультиплексо- ра 29 и мультиплексоров 25 и 26, а через элемент ИЛИ 15 - на вход 3,1 коммутатора 11 и на вход элемента ИЛИ 56, при этом на входе элемента ИЛИ 55 установлен код с выхода регистра 7, определяющий номер входа устройства 9 информация от которого записана в регистр 7. Задним фронтом сигнала на выходе элемента И 34 происходит считывание признаков из блока 32, Если информация на входе 8 подлежит вводу в данный приемник то на выходе 33 блока 32 устанавливается единичный уровень, который демуль типлексором 29 подключается к входу коммутатора 21,, передается на вход счетчика, 22, и изменяет его содержимое j что обеспечивает формирование сигнала на выходе матрицы 19 Сигнал с выхода 33 поступает также на входы записи накопителей 1 - 1,, а через элемент ИЛИ 14 - на вход коммутатора 11 и разрешает прохождение сигналов с выхода 12,блока 13 на входы разрешения выбора первого накопителя 1 . Формирование сигналов на выходах матрицы 19 позволяет осуществлять сдвиг входной информации из секции бд в секцию 6f., и одновременно подавать в нуАную секцию 2 сигнал Разрешение выбора, что обеспечивает упаковку входных параметров в ячейке накопителя 1.. При возникновении сигнала переноса на выходе счетчика 22i коммутатор 21 сигналом на входе 24, измейяет содержимое счетчика 23 и счетчика тем самым обеспечивается упаковка входных данных в следующие ячейки памяти накопителя 1 и сдвиг на длину одного параметра, относительно предыдущей ячейки Если информация на входе 8 не тре- бует ввода в первый приемник информации, то на выходе 33 блока 32 уста-. навливается нулевой уровень и записи в накопитель 1( не происходит.

Передним фронтом второго сигнала на выходе элемента И 34 на выходе счетчика 30 устанавливается код, соответствующий второму приемнику ин- формации, и далее устройство работает аналогично рассмотренному вьше случаю.

Когда счетчик 30 досчитывает до значения п выставляется признак переноса на его выходе, который сбра

15

4045

3308

сывает триггер 36 в исходное состояние.

Рассмотрим режим записи выделенных упакованных параметров,который осуществляется при наличии нулевого сигнала на выходе 69 триггера 16, заявки на запись на входе 38 и нулевого признака операции Запись на входе 18. Информа- 10 ция поступает на входы БД- .

Процесс селекции (выделения) параметров заключается в том, что в опре- деленньгй накопитель записывается информация только от тех информационных входов 8g - 8., , ввод которых необходим соответствующему приемнику, за которым закреплен этот накопитель 1 в соответствии с призна- Ками соответствия, содержащимися в

блоке 32.

Сигнал на входе 38 заносит информацию в регистр 7 и устанавливает триггер 36 в состояние, соответствующее записи. Далее устройство работает аналогично предыдущему режиму до момечта подключения демультиплек- сором 2$ единичного сигнала с выхода 33 блока 32 к входу соответствзпощего коммутатора 21, который изменяет содержимое одноименного счетчика 3, и одноименного счетчика 23, который обеспечивает каждый раз сдвиг входного слова в коммутаторе 5 на длину одного параметра. Блок 13 формирует 35 сигналы на всех выходах 12 - 12„ так как на входе 70 элемента 1ШИ 62 (фиг, 5) присутствует единичньш сиг- - нал.

20

25

30

Режим чтения выделенных упакованных параметров выполняется независимо от состояния триггера }6 при наличии единичного сигнала, соответствующего операции чтения для накопителей 1, на входе 1В и заявок на чтение на входах 42, - 42„, Сигнал на входе 18 обеспечивает формирова ние блоком 13 сигналов Разрешение выбора на всех выходах 2/j - 12, так как на одном из входов элемента ИЛИ 62 присутствует единичный сигнал с входа 18. Управляющая частотная последовательность с входа 54 (фиг.З поступает на вход счетчика 52, и код с его выхода поступает на управляющие входы мультиплексоров 46 и 47, а через элемент ИЛИ 15 на вход коммутатора 11, а также на вход дешифра тора 65 (фиг. 7).

Триггер 67; (где 1 i гп) устанавливается в единицу, если установлен одноименный триггер 68 ; сигналом с входа 42;, при этом сигнал с выхода триггера 67; проходит через одноименный элемент И 66, сбрасывает триггер 68, изменяет состояние одноименного счетчика 43 (фиг. З) и, проходя через элементы ИЛИ 50 и 14, поступает на вход коммутатора 11 и разрешает прохождение сигналов с соответствующего выхода 12, - 12 у, блока 13 на входы разрешения выбора соответствующего накопителя 1. Изменение состояния счетчика 43 обеспечивает формирование сигналов на выходах матрицы 39, тем самым подключая к входам соответствующего коммутатора 9 соответствующую секцию 2 выбранного накопителя 1. Сигнал переноса счетчика 43 изменяет состояние одноименного счетчика 44, что обеспечивает обратный сдвиг параметров при переходе от ячейки к ячейке и сдвиг адре са чтения счетчиком.

Формула изобретения

Буферное запоминающее устройство, содержащее п накопителей, где п - число приемников информации, п счетчиков адреса записи, п счетчиков адреса чтения, первую и вторую группы по п счетчиков параметров, п сумми- рующих счетчиков сдвигов, п вычитающих счетчиков сдвигов, первый коммутатор, блок управления выбором накопителя, первый триггер, первую и вторую матрицы элементов И, дешифраторы с первого по четвертый и две группы по п коммутаторов в каждой, причем выходы коммутаторов первой группы являются информационными выходами устройства, выходы каждого из счет- чиков адреса записи и счетчиков адреса чтения подключены к .адресным входам соответствующего накопителя, выходы и информационные входы которого соединены соответственно с информа- ционными входами соответствующего коммутатора первой группы и с выходами первого коммутатора, выходы первого и второго дешифраторов подключены соответственно к входам столб- цов и строк первой матрицы элементов И, выходы которой соединены с управляющими входами первого коммутатора и входами сигналов йыбора накопителя

блока управления выбором накопителя, вход признака неупакованного слова которого подключен к первому выходу первого триггера и первым управляюш м входам коммутаторов второй группы, вторые управляющие входы которых соединены с вторым выходом первого триггера и входом признака упакованного слова блока управления выбором нако-: .пителя, установочный вход которого является входом признака операции устройства, входом признака длины входного слова устройства является вход установки в 1 первого триггера, первый выход каждого из коммутаторов второй группы соединен со счетным входом соответствующего .счетчика , параметров первой группы,выход перенос которого подключен к первому информаци онному входу соответствующего коммутатора второй группы, второй выход которого соединен со счетными входами соответствующих счетчика адреса записи и суммирующего счетчика сдвигов, выходы третьего и четвертого дешифраторов подключены соответственно к входам столбцов и строк второй матрицы элементов И, выходы которой соединены с управляющими входами коммутаторов первой группы, выходы переноса каждого из счетчиков параметров второй группы подключены к счетным входам соответствующего счетчика адреса чтения и вычитающего счеТчика сдвигов, о.тличающееся тем, что, с целью расширения области применения устройства за счет обеспечения селекции информации на входах устройства отдельно для каждого приемника информации, в него введены регистр данных, второй коммутато р, блок памяти признаков соответствия, демультиплексор, мультиплексоры с первого по четвертый, первый и второй счетчики, второй триггер, элементы ШШ с первого по пятьй, элемент И и блок приема заявок на чтение, информационные входы которого являются входами чтения устройства, входом записи которого являются объединенные установочный вход второго триггера и управляющий вход регистра данных, информационные входы которого являются информационными входами устройства, причем выходы регистра данных соединены с информационными входами первого коммутатора, одни из выходов регистра данных подключены к одним

1363

из входов четвертого элемента ИЛИ, выход которого соединен с первым адресным входом блока памяти признаков соответствия, информационные выходы которого подключены к входам записи накопителей, информационным входам демультиплексора и одним из входов первого элемента ИЛИ, выход которого соединен с первым управляющим входом второго коммутатора, выходы которого подключены к входам разрешения записи и чтения накопителей, информационные входы и второй управляющий вход второго коммутатора соединены соответственно с выходами блока управления выбором накопителя и с выходом второго элемента ИЛИ, один из входов которого, один из входов пятого элемента ИЛИ, управляющие-входа демуль- типлексора, первого и второго мультиплексоров подключены к разрядным выходам первого счетчика, выход переноса и счетный вход которого соединены соответственно с входом сброса второ- го триггера, с выходом элемента И и входом чтения блока памяти признаков соответствия, второй адресный вход которого подключен к выходу пятого элемента И, другие входы четвер- того и пятого элементов ИЛИ являются соответственно входами кода номера информационного входа устройства и входами кода номера приемника информации, входы записи и входы данных блока памяти признаков соответствия

5

08

g 0 0 5 0 35

10

являются входами признаков соответствия между номерами инфор 1ационных входов устройства и приемников информации, выходы демультиплексора соединены с вторыми информационными входами коммутаторов второй группы, входы первого и второго дешифраторов подключены соответственно к выходам первого и второго мультиплексоров, информационные входы которых соединены соответственно с выходами счетчиков параметров первой группы и суммирующих счетчиков сдвигов, выходы второго счетчика подключены к другим входам второго элемента ИЛИ, управляющим входам третьего и четвертого мультиплексоров и блока приема заявок на чтение, выхода которого соединень с входами третьего элемента КЛИ и, счетными входами, счетчиков параметров второй группы, выходь которых подклю- чены к информационным входам третьего мультиплексора, выходы которого соединены с входами третьего де пифра- тора, информационные входы и выходы четвертого мультиплексора подключень соответственно к выходам вычитаю 1(их счетчиков сдвигов и к входам четвертого де пифратора, третьего элемента ИЛИ соединен с другим входом первого элемента ИЛИ, счетнь Й вход второго счетчика и второй вход элемента И являются входами синхронизации устройства.

17

фцг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1987 |

|

SU1439681A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1261012A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1119077A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1571679A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1381530A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1280457A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения буферных запоминающих устройств, применяемых в каналах ввода измерительных параметров в системы обработки данных. Целью изобретения является расширение области применения устройства за счет со 05 00 СО о 00

(Or)

фиг

QmZ7(8)

/f

KJ1

/2/7 t

61

IT

H

& if

Ltl

/77 75 - «

i7/77f

0m29

. 6

Шины 3ai40K HO чтение

Фае. 7

Составите/гь Т. Зайцева Редактор Л. Веселовская Техред Л.Олейни с Корректор А. Зимокосов

Заказ 6369/45

Тираж 588Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытийР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

62

73

if

Ltl

l l

63

IB

70

,K3u23

Щ

Om22

п22

| Буферное запоминающее устройство | 1982 |

|

SU1024984A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1265860A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1987-12-30—Публикация

1986-04-11—Подача