Изобретение относится к измерительной технике, конкретно к фазоизмеритель- ным устройствам и предназначено для использования в устройствах автоматики для измерения угла сдвига фаз.

Цель изобретения - расширение функциональных возможностей за счет цифровой компенсации амплитудно-фазовых погрешностей при измерении сдвига фаз.

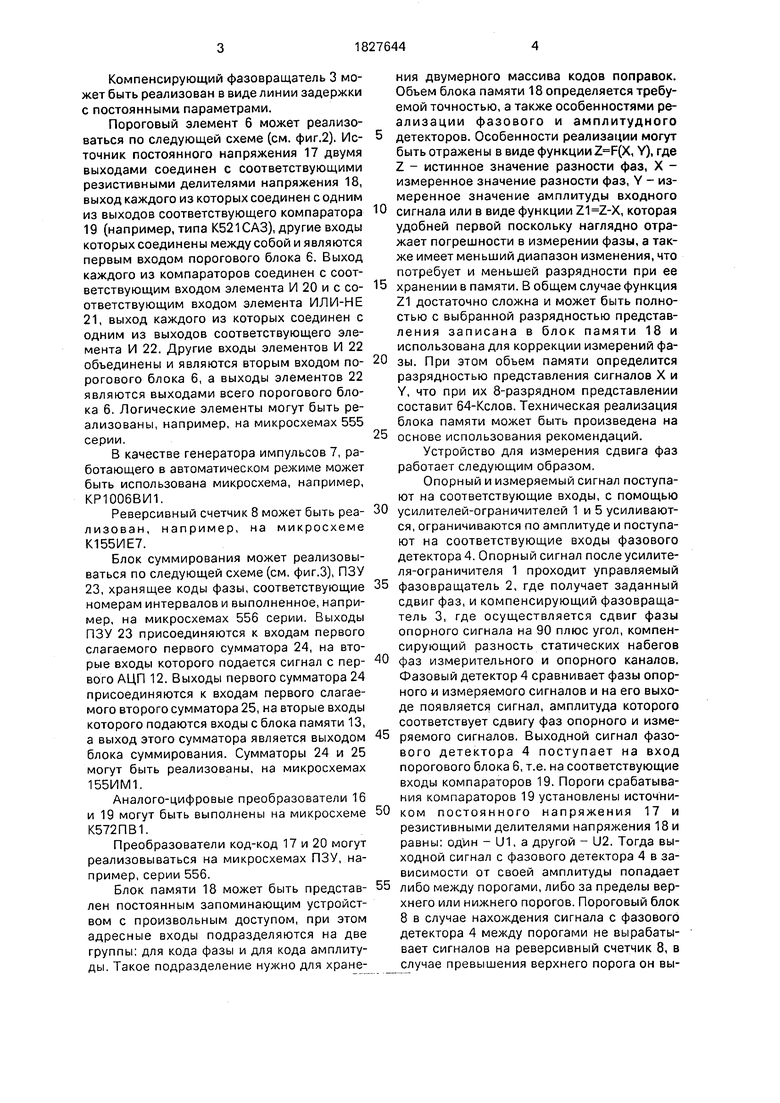

На фиг. 1 представлена блок-схема устройства.

Устройство для измерения сдвига фаз содержит последовательно соединенные усилитель-ограничитель 1, управляемый фазовращатель 2, компенсирующий фазовращатель 3, фазовый детектор 4. Второй вход фазового детектора 4 соединен с выходом усилителя-ограничителя 5, а выход фазового детектора 4 соединен с первым входом порогового блока 6, второй вход которого соединен с генератором импульсов 7. Выходы порогового блока соединены с соответствующими входами реверсивного счетчика 8, выходы которого соединены со входами управляемого фазовращателя 2 и первыми входами блока суммирования 9, последовательно соединенные логарифмический усилитель 10 и амплитудный детектор 11, вход которого соединен со входом усилителя ограничителя 5, второй вход блока суммирования 9 соединен через первый АЦП 12 с выходом фазового детектора 4, а третий вход блока суммирования 9 связан с выходом блока памяти 13, который первой группой входов через первый преобразователь код-код 14 присоединен к выходу АЦП 12 и второй группой входов через второй преобразователь код-код 15 соединен с выходом второго АЦП 16, вход которого соединен с амплитудным детектором. Выход блока суммирования является выходом всего устройства.

Усилители ограничители 1.5 и фазовый детектор 4 реализуются, например, на микросхемах К174УРЗ.

Управляемый фазовращатель 2 реализуется в виде дискретной управляемой линии задержки.

w

Ё

00

ю

ч1

0

N

Ьь

Компенсирующий фазовращатель 3 может быть реализован в виде линии задержки с постоянными параметрами.

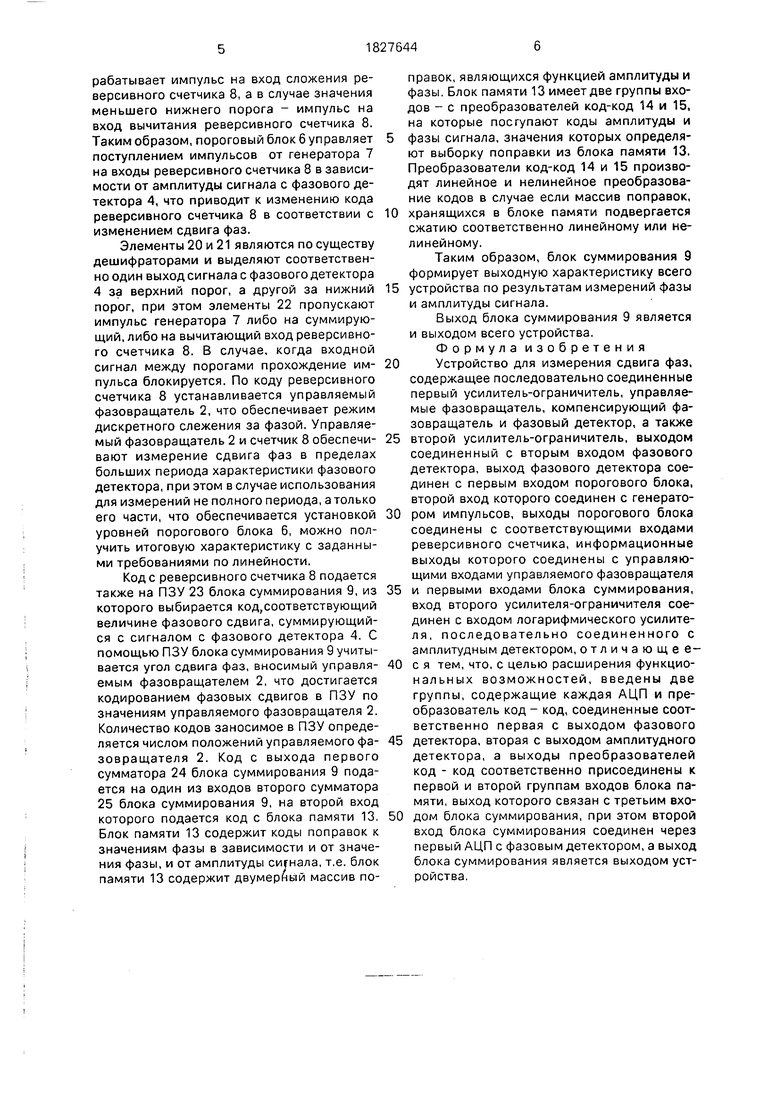

Пороговый элемент 6 может реализоваться по следующей схеме (см. фиг.2). Источник постоянного напряжения 17 двумя выходами соединен с соответствующими резистивными делителями напряжения 18, выход каждого из которых соединен с одним из выходов соответствующего компаратора 19 (например, типа К521САЗ), другие входы которых соединены между собой и являются первым входом порогового блока 6. Выход каждого из компараторов соединен с соответствующим входом элемента И 20 и с соответствующим входом элемента ИЛИ-НЕ 21, выход каждого из которых соединен с одним из выходов соответствующего элемента И 22. Другие входы элементов И 22 объединены и являются вторым входом порогового блока 6, а выходы элементов 22 являются выходами всего порогового блока 6. Логические элементы могут быть реализованы, например, на микросхемах 555 серии.

В качестве генератора импульсов 7, работающего в автоматическом режиме может быть использована микросхема, например, КР1006ВИ1.

Реверсивный счетчик 8 может быть реа- лизован, например, на микросхеме К155ИЕ7.

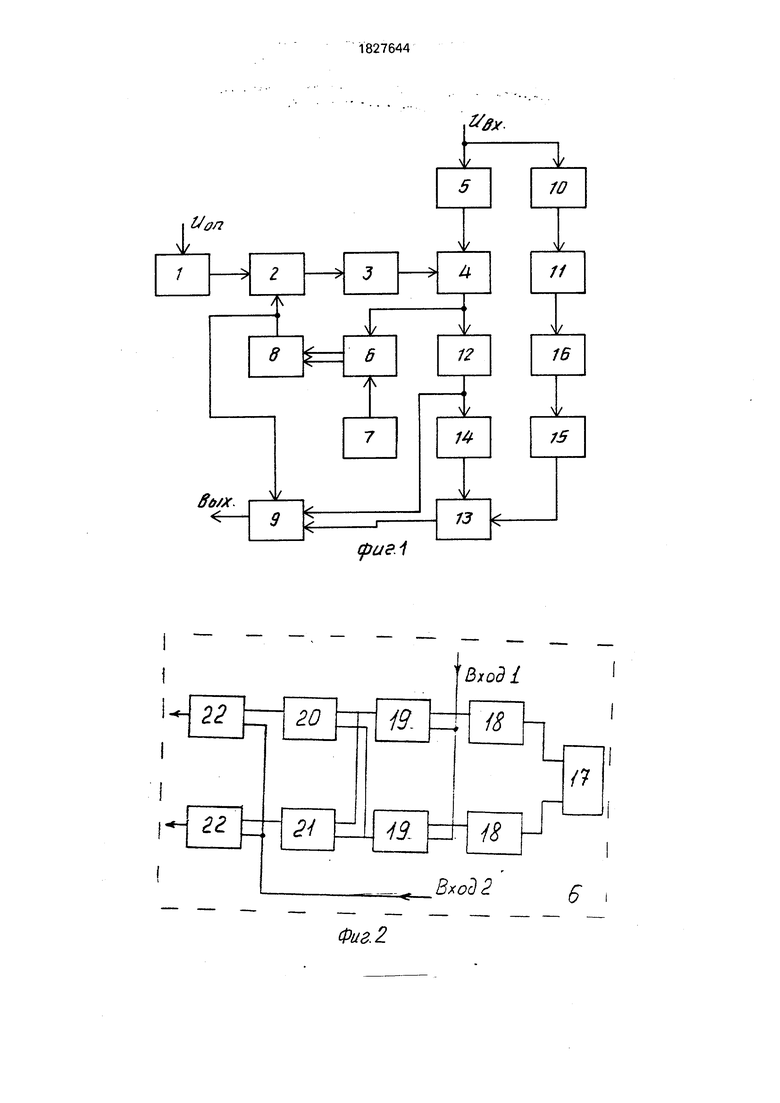

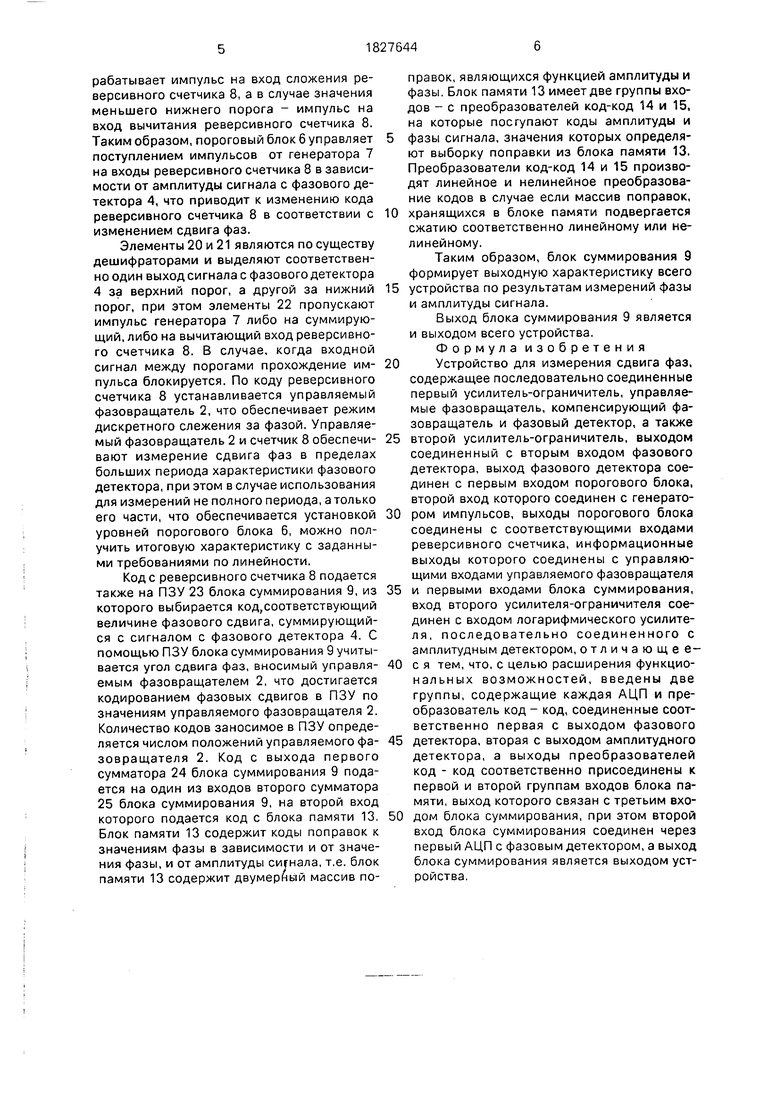

Блок суммирования может реализовываться по следующей схеме (см. фиг.З), ПЗУ 23, хранящее коды фазы, соответствующие номерам интервалов и выполненное, например, на микросхемах 556 серии. Выходы ПЗУ 23 присоединяются к входам первого слагаемого первого сумматора 24, на вторые входы которого подается сигнал с первого АЦП 12. Выходы первого сумматора 24 присоединяются к входам первого слагаемого второго сумматора 25, на вторые входы которого подаются входы с блока памяти 13, а выход этого сумматора является выходом блока суммирования. Сумматоры 24 и 25 могут быть реализованы, на микросхемах 155ИМ1.

Аналого-цифровые преобразователи 16 и 19 могут быть выполнены на микросхеме К572ПВ1.

Преобразователи код-код 17 и 20 могут реализовываться на микросхемах ПЗУ, например, серии 556.

Блок памяти 18 может быть представлен постоянным запоминающим устройством с произвольным доступом, при этом адресные входы подразделяются на две группы: для кода фазы и для кода амплитуды. Такое подразделение нужно для хранения двумерного массива кодов поправок. Объем блока памяти 18 определяется требуемой точностью, а также особенностями реализации фазового и амплитудного

детекторов. Особенности реализации могут быть отражены в виде функцииZ F(X, Y), где Z - истинное значение разности фаз, X - измеренное значение разности фаз, Y - измеренное значение амплитуды входного

0 сигнала или в виде функции , которая удобней первой поскольку наглядно отражает погрешности в измерении фазы, а также имеет меньший диапазон изменения, что потребует и меньшей разрядности при ее

5 хранении в памяти. В общем случае функция Z1 достаточно сложна и может быть полностью с выбранной разрядностью представления записана в блок памяти 18 и использована для коррекции измерений фа0 зы. При этом объем памяти определится разрядностью представления сигналов X и Y, что при их 8-разрядном представлении составит 64-Кслов. Техническая реализация блока памяти может быть произведена на

5 основе использования рекомендаций.

Устройство для измерения сдвига фаз работает следующим образом.

Опорный и измеряемый сигнал поступают на соответствующие входы, с помощью

0 усилителей-ограничителей 1 и 5 усиливаются, ограничиваются по амплитуде и поступают на соответствующие входы фазового детектора 4. Опорный сигнал после усилителя-ограничителя 1 проходит управляемый

5 фазовращатель 2, где получает заданный сдвиг фаз, и компенсирующий фазовращатель 3, где осуществляется сдвиг фазы опорного сигнала на 90 плюс угол, компенсирующий разность статических набегов

0 фаз измерительного и опорного каналов. Фазовый детектор 4 сравнивает фазы опорного и измеряемого сигналов и на его выходе появляется сигнал, амплитуда которого соответствует сдвигу фаз опорного и изме5 ряемого сигналов. Выходной сигнал фазового детектора 4 поступает на вход порогового блока 6, т.е. на соответствующие входы компараторов 19. Пороги срабатывания компараторов 19 установлены источни0 ком постоянного напряжения 17 и резистивными делителями напряжения 18 и равны: один - U1, а другой - LJ2. Тогда выходной сигнал с фазового детектора 4 в зависимости от своей амплитуды попадает

5 либо между порогами, либо за пределы верхнего или нижнего порогов. Пороговый блок 8 в случае нахождения сигнала с фазового детектора 4 между порогами не вырабатывает сигналов на реверсивный счетчик 8, в случае превышения верхнего порога он вырабатывает импульс на вход сложения реверсивного счетчика 8, а в случае значения меньшего нижнего порога - импульс на вход вычитания реверсивного счетчика 8. Таким образом, пороговый блок 6 управляет поступлением импульсов от генератора 7 на входы реверсивного счетчика 8 в зависимости от амплитуды сигнала с фазового детектора 4, что приводит к изменению кода реверсивного счетчика 8 в соответствии с изменением сдвига фаз.

Элементы 20 и 21 являются по существу дешифраторами и выделяют соответственно один выход сигнала с фазового детектора 4 за верхний порог, а другой за нижний порог, при этом элементы 22 пропускают импульс генератора 7 либо на суммирующий, либо на вычитающий вход реверсивного счетчика 8. В случае, когда входной сигнал между порогами прохождение им- пульса блокируется. По коду реверсивного счетчика 8 устанавливается управляемый фазовращатель 2, что обеспечивает режим дискретного слежения за фазой. Управляемый фазовращатель 2 и счетчик 8 обеспечи- вают измерение сдвига фаз в пределах больших периода характеристики фазового детектора, при этом в случае использования для измерений не полного периода, а только его части, что обеспечивается установкой уровней порогового блока 6, можно получить итоговую характеристику с заданными требованиями по линейности.

Код с реверсивного счетчика 8 подается также на ПЗУ 23 блока суммирования 9, из которого выбирается код,соответствующий величине фазового сдвига, суммирующийся с сигналом с фазового детектора 4. С помощью ПЗУ блока суммирования 9 учитывается угол сдвига фаз, вносимый управля- емым фазовращателем 2, что достигается кодированием фазовых сдвигов в ПЗУ по значениям управляемого фазовращателя 2. Количество кодов заносимое в ПЗУ определяется числом положений управляемого фа- зовращателя 2. Код с выхода первого сумматора 24 блока суммирования 9 подается на один из входов второго сумматора 25 блока суммирования 9, на второй вход которого подается код с блока памяти 13. Блок памяти 13 содержит коды поправок к значениям фазы в зависимости и от значения фазы, и от амплитуды сигнала, т.е. блок памяти 13 содержит двумерный массив поправок, являющихся функцией амплитуды и фазы. Блок памяти 13 имеет две группы входов - с преобразователей код-код 14 и 15, на которые поступают коды амплитуды и фазы сигнала, значения которых определяют выборку поправки из блока памяти 13. Преобразователи код-код 14 и 15 производят линейное и нелинейное преобразование кодов в случае если массив поправок, хранящихся в блоке памяти подвергается сжатию соответственно линейному или нелинейному.

Таким образом, блок суммирования 9 формирует выходную характеристику всего устройства по результатам измерений фазы и амплитуды сигнала.

Выход блока суммирования 9 является и выходом всего устройства.

Формула изобретения

Устройство для измерения сдвига фаз, содержащее последовательно соединенные первый усилитель-ограничитель, управляемые фазовращатель, компенсирующий фазовращатель и фазовый детектор, а также второй усилитель-ограничитель, выходом соединенный с вторым входом фазового детектора, выход фазового детектора соединен с первым входом порогового блока, второй вход которого соединен с генератором импульсов, выходы порогового блока соединены с соответствующими входами реверсивного счетчика, информационные выходы которого соединены с управляющими входами управляемого фазовращателя и первыми входами блока суммирования, вход второго усилителя-ограничителя соединен с входом логарифмического усилителя, последовательно соединенного с амплитудным детектором, отличающее- с я тем, что, с целью расширения функцио- нальных возможностей, введены две группы, содержащие каждая АЦП и преобразователь код - код, соединенные соответственно первая с выходом фазового детектора, вторая с выходом амплитудного детектора, а выходы преобразователей код - код соответственно присоединены к первой и второй группам входов блока памяти, выход которого связан с третьим входом блока суммирования, при этом второй вход блока суммирования соединен через первый АЦП с фазовым детектором, а выход блока суммирования является выходом устройства.

I

t/вл

фиаЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения сдвига фаз | 1985 |

|

SU1285396A1 |

| Устройство для измерения сдвига фаз | 1986 |

|

SU1370595A2 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU734776A1 |

| МОНОИМПУЛЬСНЫЙ РАДИОЛОКАТОР СО СКВОЗНЫМИ ФАЗОВЫМИ КАНАЛАМИ | 2002 |

|

RU2232404C1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU732955A1 |

| Двухканальный преобразователь перемещений | 1983 |

|

SU1135011A1 |

| Устройство для измерения флуктуационной составляющей частоты сигналов с линейно-частотной модуляцией | 1988 |

|

SU1631456A1 |

| Устройство для измерения амплитуды и фазы радиосигнала | 1989 |

|

SU1665811A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ФАЗЫ РАДИОСИГНАЛА | 1992 |

|

RU2050552C1 |

| ПРИЕМО-ПЕРЕДАЮЩЕЕ УСТРОЙСТВО РАДИОЛОКАТОРА | 1985 |

|

SU1841065A1 |

Использование: измерительная техника, измерение угла сдвига фаз. Сущность изобретения: устройство содержит 2 усилителя-ограничителя (1, 5), 1 управляемый фазовращатель (2), 1 компенсационный фазовращатель (3), 1 фазовый детектор (4), 1 пороговый блок (6), 1 генератор импульсов

Фиг. 2

ft«.3

| Устройство для измерения сдвига фаз | 1985 |

|

SU1285396A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения сдвига фаз | 1986 |

|

SU1370595A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-07-15—Публикация

1991-06-28—Подача