Изобретение относится к вычислительной технике (к устройствам приоритета) и может быть использовано при управлении очередностью обращения нескольких процессоров к коллективно используемому ресурсу вычислительной системы.

Целью изобретения является расширение области применения устройства за счет определения отказавших микропроцессоров и маскирования из после работы.

При использовании изобретения может быть получен положительный эффект за счет исключения холостых тактов работы устройства при передаче ресурсов микропроцессорной системы от одного микропроцессора к другому, а также за счет маскирования реакций отказавших микропроцессоров и их отключения от системной магистрали.

Расширение области применения достигается введением регистра запросов, схемы выделения крайней единицы, элемента 2 ИЛИ-НЕ, триггера, третьего блока элементов ИЛИ, третьего блока элементов И, порогового элемента, блока настойки, первого и второго одновибраторов, второго-пятого и второго И, второго элемента ИЛИ, позволяющих уменьшить время передачи управления ресурсами микропроцессорной системы от одного микропроцессора к другому, фиксировать отказы микропроцессоров и осуществлять маскирование отказавших микро- процессоров в течение работы микропроцессорной системы.

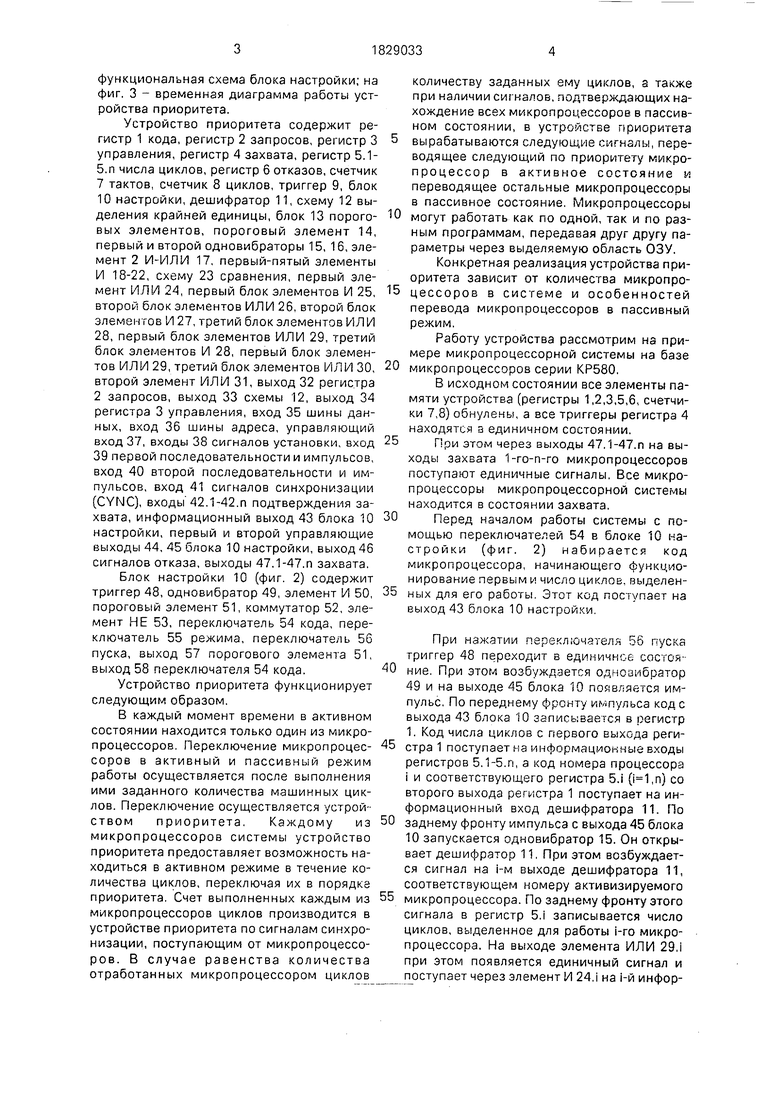

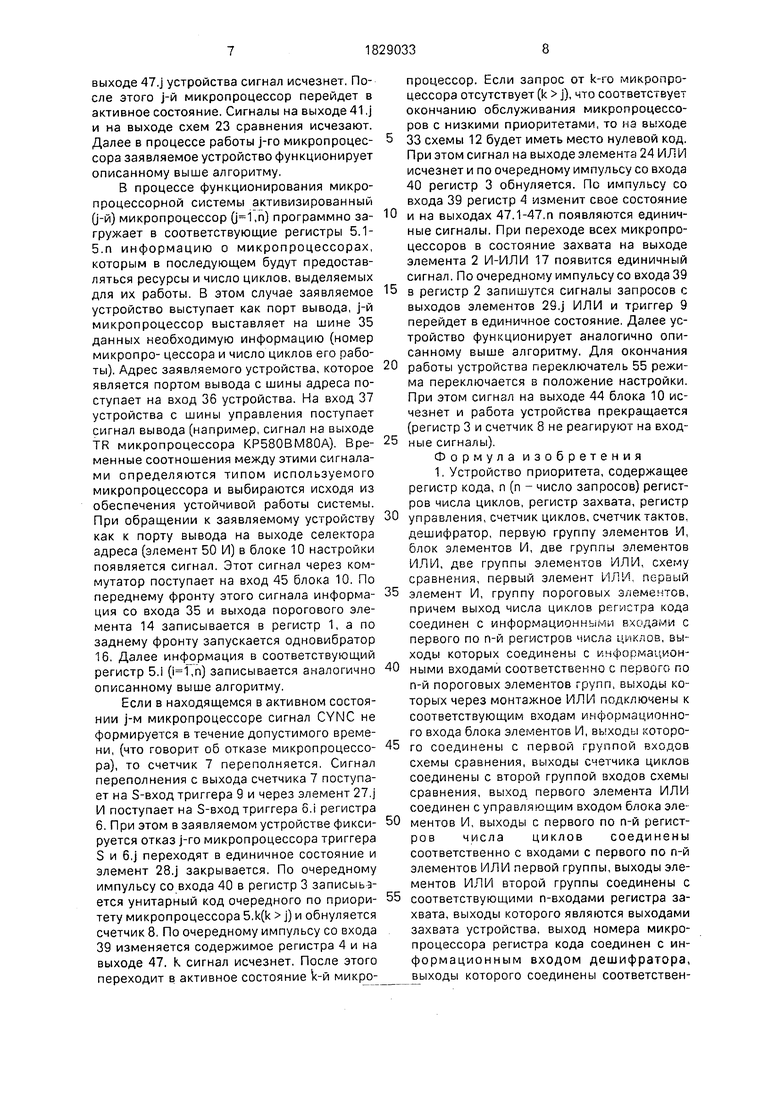

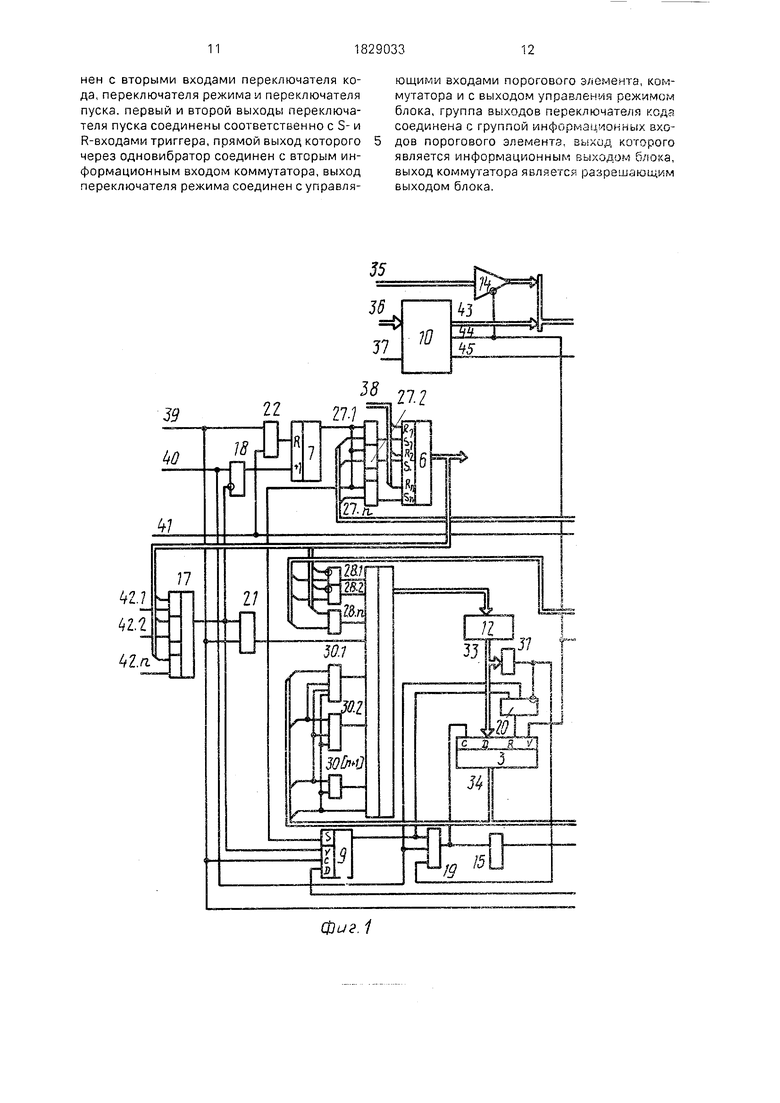

Фиг. 1-5 иллюстрируют предлагаемое изобретение.

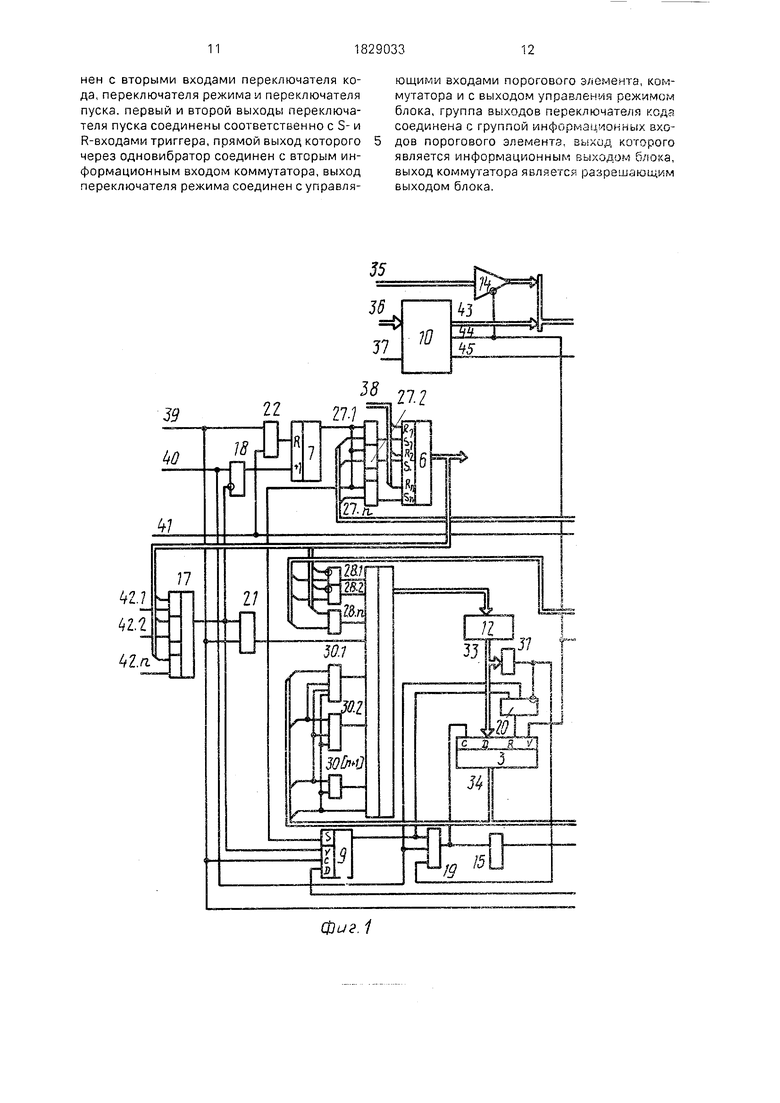

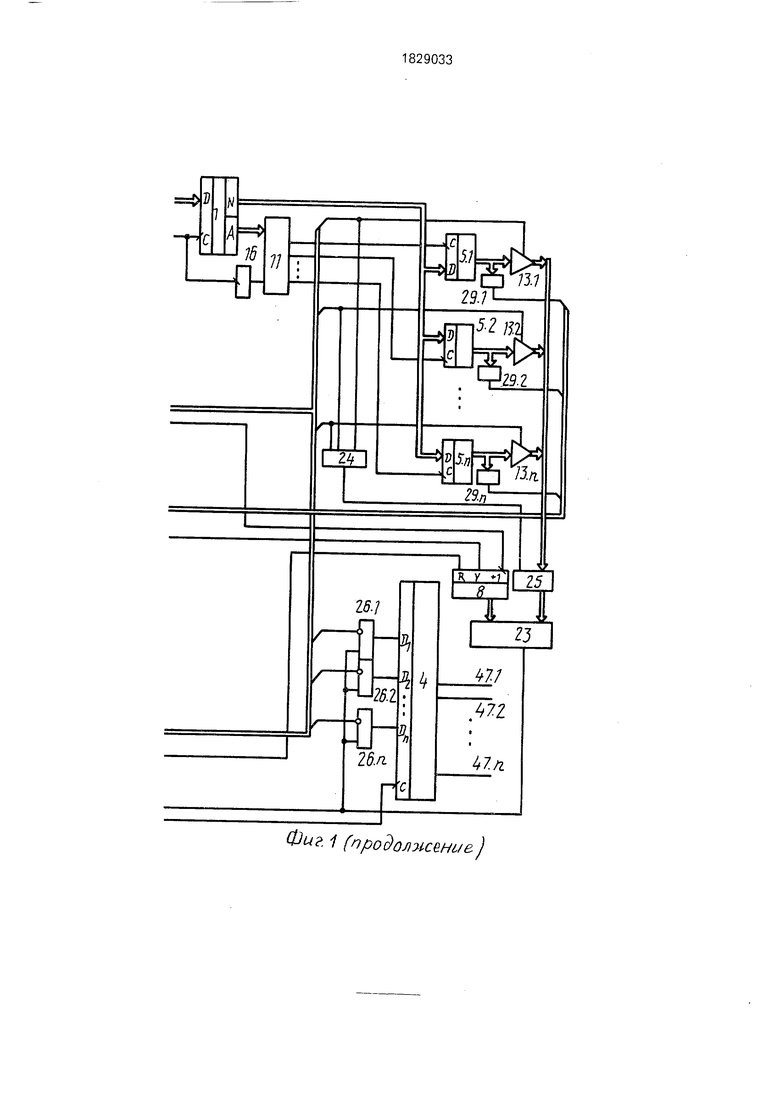

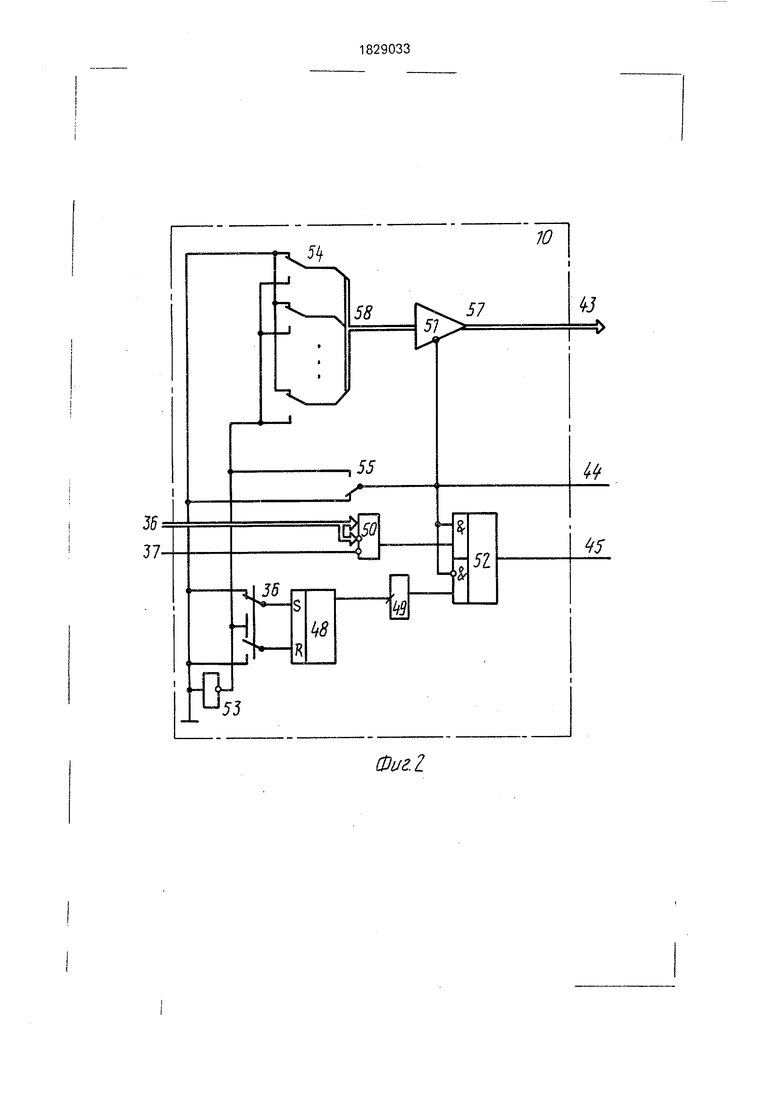

На фиг. 1 приведена функциональная схема устройства приоритета; на фиг. 2 00

hO 4D О GO 00

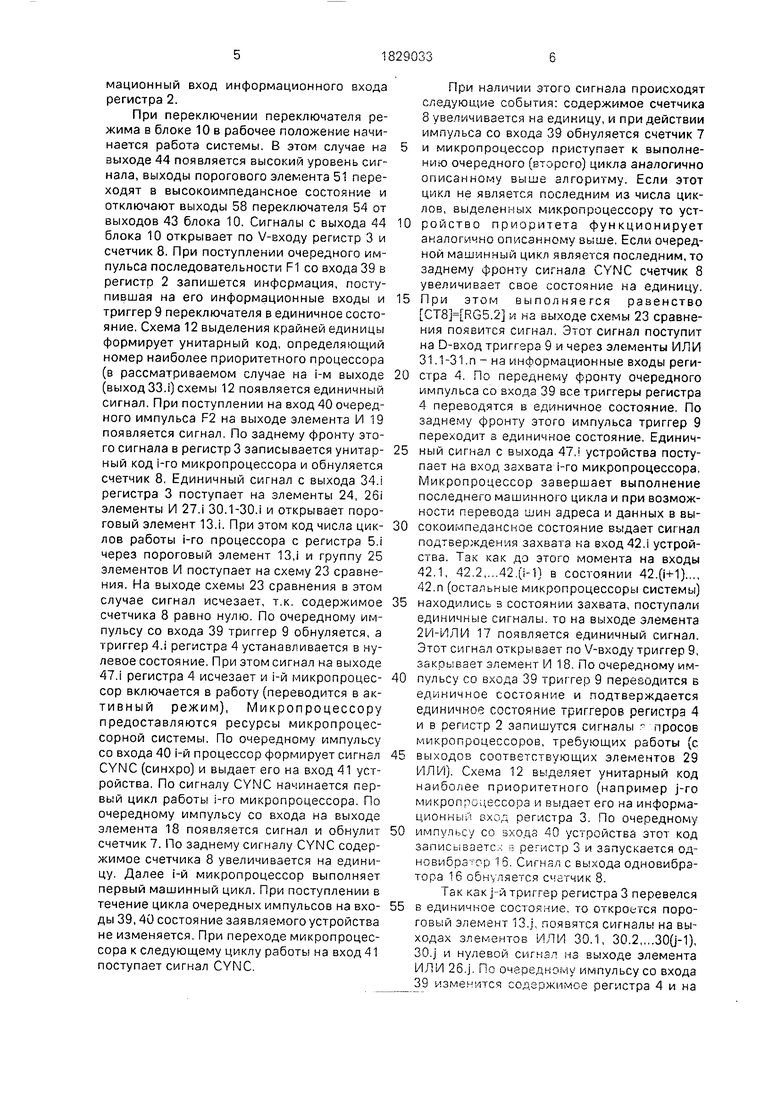

функциональная схема блока настройки; на фиг. 3 - временная диаграмма работы устройства приоритета.

Устройство приоритета содержит регистр 1 кода, регистр 2 запросов, регистр 3 управления, регистр 4 захвата, регистр 5.1- 5.п числа циклов, регистр 6 отказов, счетчик 7 тактов, счетчик 8 циклов, триггер 9, блок 10 настройки, дешифратор 11, схему 12 выделения крайней единицы, блок 13 пороге- вых элементов, пороговый элемент 14, первый и второй одновибраторы 15, 16, элемент 2 И-ИЛИ 17, первый-пятый элементы И 18-22, схему 23 сравнения, первый элемент ИЛИ 24, первый блок элементов И 25, второй блок элементов ИЛИ 26, второй блок элементов И 27, третий блок элементов ИЛ И 28, первый блок элементов ИЛИ 29, третий блок элементов И 28, первый блок элементов ИЛИ 29, третий блок элементов ИЛИ 30, второй элемент ИЛИ 31, выход 32 регистра 2 запросов, выход 33 схемы 12, выход 34 регистра 3 управления, вход 35 шины данных, вход 36 шины адреса, управляющий вход 37, входы 38 сигналов установки, вход 39 первой последовательности и импульсов, вход 40 второй последовательности и импульсов, вход 41 сигналов синхронизации (CYNC), входы 42.1-42.п подтверждения захвата, информационный выход 43 блока 10 настройки, первый и второй управляющие выходы 44, 45 блока 10 настройки, выход 46 сигналов отказа, выходы 47.1-47.п захвата.

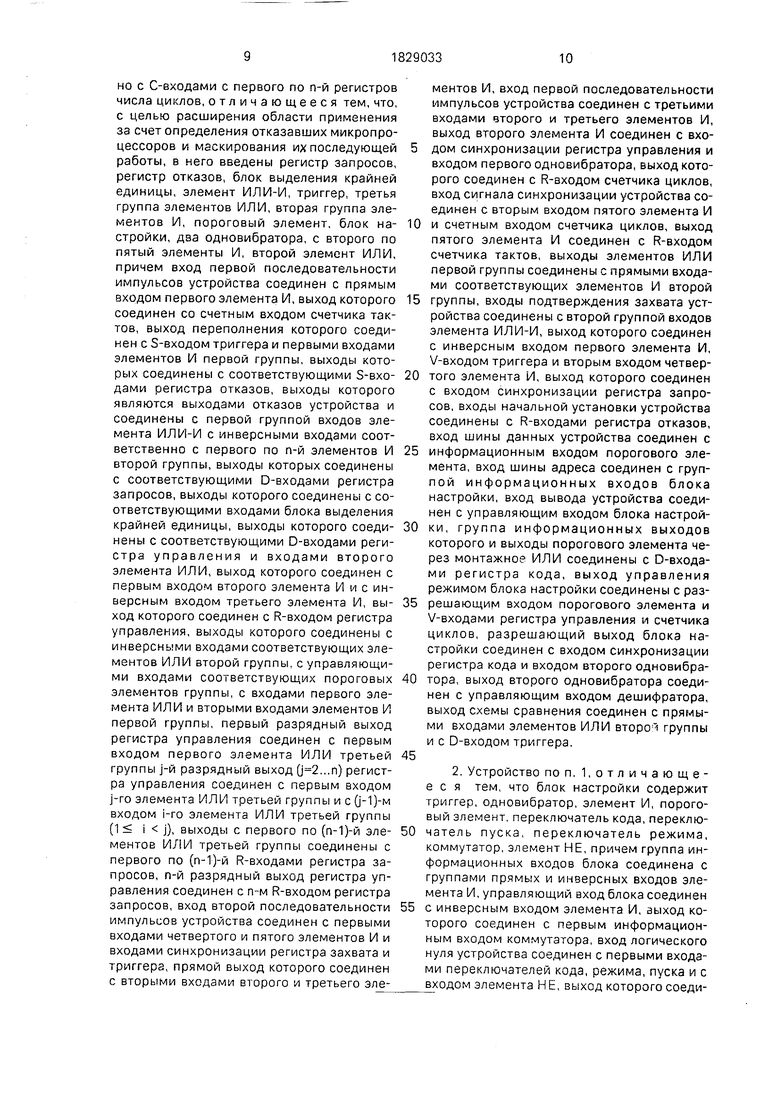

Блок настройки 10 (фиг. 2) содержит триггер 48, одновибратор 49, элемент И 50, пороговый элемент 51, коммутатор 52, элемент НЕ 53, переключатель 54 кода, переключатель 55 режима, переключатель 56 пуска, выход 57 порогового элемента 51, выход 58 переключателя 54 кода.

Устройство приоритета функционирует следующим образом.

В каждый момент времени в активном состоянии находится только один из микропроцессоров. Переключение микропроцес- соров в активный и пассивный режим работы осуществляется после выполнения ими заданного количества машинных циклов. Переключение осуществляется устройством приоритета. Каждому из микропроцессоров системы устройство приоритета предоставляет возможность находиться в активном режиме в течение количества циклов, переключая их в порядке приоритета. Счет выполненных каждым из микропроцессоров циклов производится в устройстве приоритета по сигналам синхронизации, поступающим от микропроцессоров. В случае равенства количества отработанных микропроцессором циклов

количеству заданных ему циклов, з также при наличии сигналов, подтверждающих нахождение всех микропроцессоров в пассивном состоянии, в устройстве приоритета вырабатываются следующие сигналы, переводящее следующий по приоритету микропроцессор в активное состояние и переводящее остальные микропроцессоры в пассивное состояние. Микропроцессоры могут работать как по одной, так и по разным программам, передавая друг другу параметры через выделяемую область ОЗУ.

Конкретная реализация устройства приоритета зависит от количества микропроцессоров в системе и особенностей перевода микропроцессоров в пассивный режим.

Работу устройства рассмотрим на примере микропроцессорной системы на базе микропроцессоров серии КР580.

В исходном состоянии все элементы памяти устройства (регистры 1,2,3,5,6, счетчики 7,8) обнулены, а все триггеры регистра 4 находятся з единичном состоянии.

При этом через выходы 47.1-47.П на выходы захвата 1-го-п-го микропроцессоров поступают единичные сигналы. Все микропроцессоры микропроцессорной системы находится в состоянии захвата.

Перед началом работы системы с помощью переключателей 54 в блоке 10 настройки (фиг. 2) набирается код микропроцессора, начинающего функционирование первым и число циклов, выделенных для его работы. Этот код поступает на выход 43 блока 10 настройки.

При нажатии переключателя 56 пуска триггер 48 переходит в единичное состояние. При этом возбуждается одноаибратор 49 и на выходе 45 блока 10 появляется импульс. По переднему фронту импульса код с выхода 43 блока 10 записывается в регистр 1. Код числа циклов с первого выхода регистра 1 поступает на информационные входы регистров 5.1-5.П, а код номера процессора i и соответствующего регистра 5.i (,n) со второго выхода регистра 1 поступает на информационный вход дешифратора 11. По заднему фронту импульса с выхода 45 блока 10 запускается одновибратор 15. Он открывает дешифратор 11, При этом возбуждается сигнал на i-м выходе дешифратора 11, соответствующем номеру активизируемого микропроцессора. По заднему фронту этого сигнала в регистр 5.i записывается число циклов, выделенное для работы i-ro микропроцессора. На выходе элемента ИЛИ 29,i при этом появляется единичный сигнал и поступает через элемент И 24.i на 1-й информационный вход информационного входа регистра 2.

При переключении переключателя режима в блоке 10 в рабочее положение начинается работа системы. В этом случае на выходе 44 появляется высокий уровень сигнала, выходы порогового элемента 51 переходят в высокоимпедансное состояние и отключают выходы 58 переключателя 54 от выходов 43 блока 10. Сигналы с выхода 44 блока 10 открывает по V-входу регистр 3 и счетчик 8. При поступлении очередного импульса последовательности F1 со входа 39 в регистр 2 запишется информация, поступившая на его информационные входы и триггер 9 переключателя в единичное состояние. Схема 12 выделения крайней единицы формирует унитарный код, определяющий номер наиболее приоритетного процессора (в рассматриваемом случае на i-м выходе (выход 33.i) схемы 12 появляется единичный сигнал. При поступлении на вход 40 очередного импульса F2 на выходе элемента И 19 появляется сигнал. По заднему фронту этого сигнала в регистр 3 записывается унитарный код i-ro микропроцессора и обнуляется счетчик 8. Единичный сигнал с выхода 34.i регистра 3 поступает на элементы 24, 26i элементы И 27.1 30.1-30.i и открывает пороговый элемент 13.1. При этом код числа циклов работы 1-го процессора с регистра 5.i через пороговый элемент 13,i и группу 25 элементов И поступает на схему 23 сравнения. На выходе схемы 23 сравнения в этом случае сигнал исчезает, т.к. содержимое счетчика 8 равно нулю. По очередному импульсу со входа 39 триггер 9 обнуляется, а триггер 4.i регистра 4 устанавливается в нулевое состояние. При этом сигнал на выходе 47.i регистра 4 исчезает и i-й микропроцессор включается в работу (переводится в активный режим), Микропроцессору предоставляются ресурсы микропроцессорной системы. По очередному импульсу со входа 40 i-й процессор формирует сигнал CYNC (синхро) и выдает его на вход 41 устройства. По сигналу CYNC начинается первый цикл работы i-ro микропроцессора. По очередному импульсу со входа на выходе элемента 18 появляется сигнал и обнулит счетчик 7. По заднему сигналу CYNC содержимое счетчика 8 увеличивается на единицу. Далее i-й микропроцессор выполняет первый машинный цикл. При поступлении в течение цикла очередных импульсов на входы 39,40 состояние заявляемого устройства не изменяется. При переходе микропроцессора к следующему циклу работы на вход 41 поступает сигнал CYNC.

При наличии этого сигнала происходят следующие события: содержимое счетчика 8 увеличивается на единицу, и при действии импульса со входа 39 обнуляется счетчик 7

и микропроцессор приступает к выполнению очередного (второго) цикла аналогично описанному выше алгоритму. Если этот цикл не является последним из числз циклов, выделенных микропроцессору то уст0 ройство приоритета функционирует аналогично описанному выше. Если очередной машинный цикл является последним, то заднему фронту сигнала CYNC счетчик 8 увеличивает свое состояние на единицу.

5 При этом выполняется равенство .2 и на выходе схемы 23 сравнения появится сигнал. Этот сигнал поступит на D-вход триггера 9 и через элементы ИЛИ 31.1-31 .п - на информационные входы реги0 стра 4. По переднему фронту очередного импульса со входа 39 все триггеры регистра 4 переводятся в единичное состояние. По заднему фронту этого импульса триггер 9 переходит а единичное состояние. Единич5 ный сигнал с выхода 47.i устройства поступает на вход захвата i-ro микропроцессора. Микропроцессор завершает выполнение последнего машинного цикла и при возможности перевода шин адреса и данных в вы0 сокоимпедансное состояние выдает сигнал подтверждения захвата на вход 42,i устройства. Так как до этого момента на входы 42.1, 42.2,...42.(1-1) в состоянии 42.(i+1)..., 42.п (остальные микропроцессоры системы)

5 находились з состоянии захвата, поступали единичные сигналы, то на выходе элемента 2И-ИЛИ 17 появляется единичный сигнал. Этот сигнал открывает по V-входу триггер 9, закрывает элемент И 18. По очередному им0 пульсу со входа 39 триггер 9 переводится Б единичное состояние и подтверждается единичное состояние триггеров регистра 4 и в регистр 2 запишутся сигналы ° просов микропроцессоров, требующих работы (с

5 выходов соответствующих элементов 29 ИЛИ). Схема 12 выделяет унитарный код наиболее приоритетного (например j-ro микропроцессора и выдает его на информационный вход регистра 3. По очередному

0 импульсу со входа 40 устройства этот код записываете:-: в регистр 3 и запускается од- новибрзтор 15. Сигнал с выхода одновибра- тора 16 обнуляется счатчик 8.

Так как j-й триггер регистра 3 перевелся

5 в единичное состояние, то откроется пороговый элемент 13.j, появятся сигналы на выходах элементов ИЛИ 30.1, 3Q.2,...30Q-1), 30.j и нулевой сигнал из выходе элемента ИЛИ 26.j. По очередному импульсу со входа 39 изменится содержимое регистра 4 и на

выходе 47.J устройства сигнал исчезнет. После этого j-й микропроцессор перейдет в активное состояние. Сигналы на выходе 41 ,j и на выходе схем 23 сравнения исчезают. Далее в процессе работы j-ro микропроцес- сора заявляемое устройство функционирует описанному выше алгоритму.

В процессе функционирования микропроцессорной системы активизированный (j-й) микропроцессор () программно за- гружает в соответствующие регистры 5.1- 5.п информацию о микропроцессорах, которым в последующем будут предоставляться ресурсы и число циклов, выделяемых для их работы. В этом случае заявляемое устройство выступает как порт вывода, j-й микропроцессор выставляет на шине 35 данных необходимую информацию (номер микропро- цессора и число циклов его работы). Адрес заявляемого устройства, которое является портом вывода с шины адреса поступает на вход 36 устройства. На вход 37 устройства с шины управления поступает сигнал вывода (например, сигнал на выходе TR микропроцессора КР580ВМ80А). Вре- менные соотношения между этими сигналами определяются типом используемого микропроцессора и выбираются исходя из обеспечения устойчивой работы системы. При обращении к заявляемому устройству как к порту вывода на выходе селектора адреса (элемент 50 И) в блоке 10 настройки появляется сигнал. Этот сигнал через коммутатор поступает на вход 45 блока 10. По переднему фронту этого сигнала информа- ция со входа 35 и выхода порогового элемента 14 записывается в регистр 1, а по заднему фронту запускается одновибратор 16. Далее информация в соответствующий регистр 5.i (,n) записывается аналогично описанному выше алгоритму.

Если в находящемся в активном состоянии j-м микропроцессоре сигнал CYNC не формируется в течение допустимого времени, (что говорит об отказе микропроцессо- ра), то счетчик 7 переполняется, Сигнал переполнения с выхода счетчика 7 поступает на S-вход триггера 9 и через элемент 27.j И поступает на S-вход триггера o.i регистра 6, При этом в заявляемом устройстве фикси- руется отказ j-ro микропроцессора триггера S и 6J переходят в единичное состояние и элемент 28J закрывается. По очередному импульсу со входа 40 в регистр 3 записыва-

ется унитарный код очередного по приори тету микропроцессора 5.k(k j) и обнуляется счетчик 8. По очередному импульсу со входа 39 изменяется содержимое регистра 4 и на выходе 47. К сигнал исчезнет. После этого переходит в активное состояние k-й микро-

5

10152025 30 3540

4550 55

процессор. Если запрос от k-ro микропроцессора отсутствует (k j), что соответствует окончанию обслуживания микропроцессоров с низкими приоритетами, то на выходе 33 схемы 12 будет иметь место нулевой код. При этом сигнал на выходе элемента 24 ИЛИ исчезнет и по очередному импульсу со входа 40 регистр 3 обнуляется. По импульсу со входа 39 регистр 4 изменит свое состояние и на выходах 47.1-47.п появляются единичные сигналы. При переходе всех микропроцессоров в состояние захвата на выходе элемента 2 И-ИЛИ 17 появится единичный сигнал. По очередному импульсу со входа 39 в регистр 2 запишутся сигналы запросов с выходов элементов 29J ИЛИ и триггер 9 перейдет в единичное состояние. Далее устройство функционирует аналогично описанному выше алгоритму. Для окончания работы устройства переключатель 55 режима переключается в положение настройки. При этом сигнал на выходе 44 блока 10 исчезнет и работа устройства прекращается (регистр 3 и счетчик 8 не реагируют на входные сигналы).

Формула изобретения 1. Устройство приоритета, содержащее регистр кода, л (п - число запросов) регистров числа циклов, регистр захвата, регистр управления, счетчик циклов, счетчик тактов, дешифратор, первую группу элементов И, блок элементов И, две группы элементов ИЛИ, две группы элементов ИЛИ, схему сравнения, первый элемент ИЛИ, первый элемент И, группу пороговых элементов, причем выход числа циклов регистра кода соединен с информационными входами с первого по n-й регистров числа циклов, выходы которых соединены с информационными входами соответственно с первого по n-й пороговых элементов групп, выходы которых через монтажное ИЛИ подключены к соответствующим входам информационного входа блока элементов И, выходы которого соединены с первой группой входов схемы сравнения, выходы счетчика циклов соединены с второй группой входов схемы сравнения, выход первого элемента ИЛИ соединен с управляющим входом блока элементов И, выходы с первого по n-й регистров числа циклов соединены соответственно с входами с первого по п-й элементов ИЛИ первой группы, выходы элементов ИЛИ второй группы соединены с соответствующими n-входами регистра захвата, выходы которого являются выходами захвата устройства, выход номера микропроцессора регистра кода соединен с информационным входом дешифратора, выходы которого соединены соответственно с С-входами с первого по n-й регистров числа циклов, отличающееся тем, что, с целью расширения области применения за счет определения отказавших микропроцессоров и маскирования их последующей работы, в него введены регистр запросов, регистр отказов, блок выделения крайней единицы, элемент ИЛИ-И, триггер, третья группа элементов ИЛИ, вторая группа элементов И, пороговый элемент, блок настройки, два одновибратора, с второго по пятый элементы И, второй элемент ИЛИ, причем вход первой последовательности импульсов устройства соединен с прямым входом первого элемента И, выход которого соединен со счетным входом счетчика тактов, выход переполнения которого соединен с S-входом триггера и первыми входами элементов И первой группы, выходы которых соединены с соответствующими S-вхо- дами регистра отказов, выходы которого являются выходами отказов устройства и соединены с первой группой входов элемента ИЛИ-И с инверсными входами соответственно с первого по n-й элементов И второй группы, выходы которых соединены с соответствующими D-входами регистра запросов, выходы которого соединены с соответствующими входами блока выделения крайней единицы, выходы которого соединены с соответствующими D-входами регистра управления и входами второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И и с инверсным входом третьего элемента И, выход которого соединен с R-входом регистра управления, выходы которого соединены с инверсными входами соответствующих элементов ИЛИ второй группы, с управляющими входами соответствующих пороговых элементов группы, с входами первого элемента ИЛИ и вторыми входами элементов И первой группы, первый разрядный выход регистра управления соединен с первым входом первого элемента ИЛИ третьей группы j-й разрядный выход ...п) регистра управления соединен с первым входом j-ro элемента ИЛИ третьей группы и с 0-1)-м входом i-ro элемента ИЛИ третьей группы (1 i j), выходы с первого по (п-1)-й элементов ИЛИ третьей группы соединены с первого по (п-1)-й R-входами регистра запросов, n-й разрядный выход регистра управления соединен с п-м R-входом регистра запросов, вход второй последовательности импульсов устройства соединен с первыми входами четвертого и пятого элементов И и входами синхронизации регистра захвата и триггера, прямой выход которого соединен с вторыми входами второго и третьего элементов И, вход первой последовательности импульсов устройства соединен с третьими входами второго и третьего элементов И, выход второго элемента И соединен с входом синхронизации регистра управления и входом первого одновибратора, выход которого соединен с R-входом счетчика циклов, вход сигнала синхронизации устройства соединен с вторым входом пятого элемента И

и счетным входом счетчика циклов, выход пятого элемента И соединен с R-входом счетчика тактов, выходы элементов ИЛИ первой группы соединены с прямыми входами соответствующих элементов И второй

группы, входы подтверждения захвата устройства соединены с второй группой входов элемента ИЛИ-И, выход которого соединен с инверсным входом первого элемента И, V-входом триггера и вторым входом четвертого элемента И, выход которого соединен с входом синхронизации регистра запросов, входы начальной установки устройства соединены с R-входами регистра отказов, вход шины данных устройства соединен с

информационным входом порогового элемента, вход шины адреса соединен с группой информационных входов блока настройки, вход вывода устройства соединен с управляющим входом блока настройки, группа информационных выходов которого и выходы порогового элемента через монтажное ИЛИ соединены с D-входами регистра кода, выход управления режимом блока настройки соединены с разрешающим входом порогового элемента и V-входами регистра управления и счетчика циклов, разрешающий выход блока настройки соединен с входом синхронизации регистра кода и входом второго одновибратора, выход второго одновибратора соединен с управляющим входом дешифратора, выход схемы сравнения соединен с прямыми входами элементов ИЛИ второй группы и с D-входом триггера.

2. Устройство по п. 1,отличающееся тем, что блок настройки содержит триггер, одновибратор, элемент И, пороговый элемент, переключатель кода, переключатель пуска, переключатель режима, коммутатор, элемент НЕ, причем группа информационных входов блока соединена с группами прямых и инверсных входов элемента И, управляющий вход блока соединен

с инверсным входом элемента И, аыход которого соединен с первым информационным входом коммутатора, вход логического нуля устройства соединен с первыми входами переключателей кода, режима, пуска и с

входом элемента НЕ, выход которого соединен с вторыми входами переключателя кода, переключателя режима и переключателя пуска, первый и второй выходы переключателя пуска соединены соответственно с S- и R-входами триггера, прямой выход которого через одновибратор соединен с вторым информационным входом коммутатора, выход переключателя режима соединен с управляющими входами порогового элемента, коммутатора и с выходом управления режимом блока, группа выходов переключателя кода соединена с группой информационных входов порогового элемента, выход которого является информационным выходом блока, выход коммутатора является разрешающим выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для обслуживания запросов | 1985 |

|

SU1290326A1 |

| Устройство для передачи информации | 1989 |

|

SU1700571A1 |

| Многопроцессорная система | 1989 |

|

SU1741144A1 |

| Многопроцессорная вычислительная система | 1991 |

|

SU1837309A1 |

| Устройство приоритета | 1990 |

|

SU1789984A1 |

| Многопроцессорная система | 1990 |

|

SU1783538A1 |

| Устройство приоритетного обслуживания каналов | 1989 |

|

SU1702369A1 |

| Мультимикропрограммное устройство для контроля и управления | 1984 |

|

SU1249513A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043653A1 |

| Устройство для обслуживания запросов | 1990 |

|

SU1805467A1 |

Изобретение относится к вычислительной технике и может быть использовано при управлении очередностью обращения нескольких процессоров к коллективно используемому ресурсу вычислительной системы. Целью изобретения является расширение области применения устройства за счет определения отказавших микропроцессоров и маскирования их последующей работы. В устройство введены регистры запросов и отказов, блок выделения крайней единицы, элемент ИЛИ-И, триггер, третья группа элементов ИЛИ, вторая группа элементов И, пороговый элемент, блок настройки, два однозибратора, с второго по пятый элементы И, второй элемент ИЛИ. 1 з.п, ф-лы, 3 ил.

фиг. 1

EC06S81

5Ь

36: 5735

н

W

HJ

U5J

;

58

51

57

4J

55

$

52

45

П

Л.

/

Фиг.З (пист 1)

| Устройство приоритета | 1982 |

|

SU1080144A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для мажоритарного резервирования | 1983 |

|

SU1140278A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1415950, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-07-23—Публикация

1990-10-29—Подача