Изобретение относится к вычислительной технике и может быть использовано в отказоустойчивых многопроцессорных системах для распределения задач между процессорами.

Цель изобретения - повышение быстродействия системы.

Сущность изобретения состоит в повы- иении быстродействия системы за счет обеспечения возможности решения менее приоритетных задач в промежутки времени, когда более приоритетные задачи находятся режиме ожидания, а также возможности проверки хода решения задачи посредством контрольных точек.

В системе, в зависимости от типа зада- и, поступают в один, два или три процессора и решается либо в одинарном, либо в дублированном, либо в мажоритарном ре- .

Задачи, предназначенные для решения мажоритарном режиме, при ожидании Свободных процессоров могут отдавать имеющиеся свободные процессоры задачам, решаемым в одинарном и дублированном режимах (низкоприоритетным задачам), а при освобождении необходимого количества процессов - прерывать решение низкоприоритетных задач и захватывать необходимые свободные процессоры. При этом те из низкоприоритетных задач, которые не успели решиться (были прерваны), остаются во входной очереди с правом на последующее их обслуживание.

Правильность хода решения задач в дублированном и мажоритарном режимах проверяется с помощью контрольных точек. При каждом несовпадении промежуточных результатов в процессорах, решение задачи прерывается и принимаются меры по обеспечению возможности дальнейшего решения данной задачи с целью получения верного результата.

После решения задачи в каналах и получения правильного результата данные каналы устанавливаются в исходное состо00 CJ

1

00

о о

яниё, после чего они готовы к приему очередной задачи.

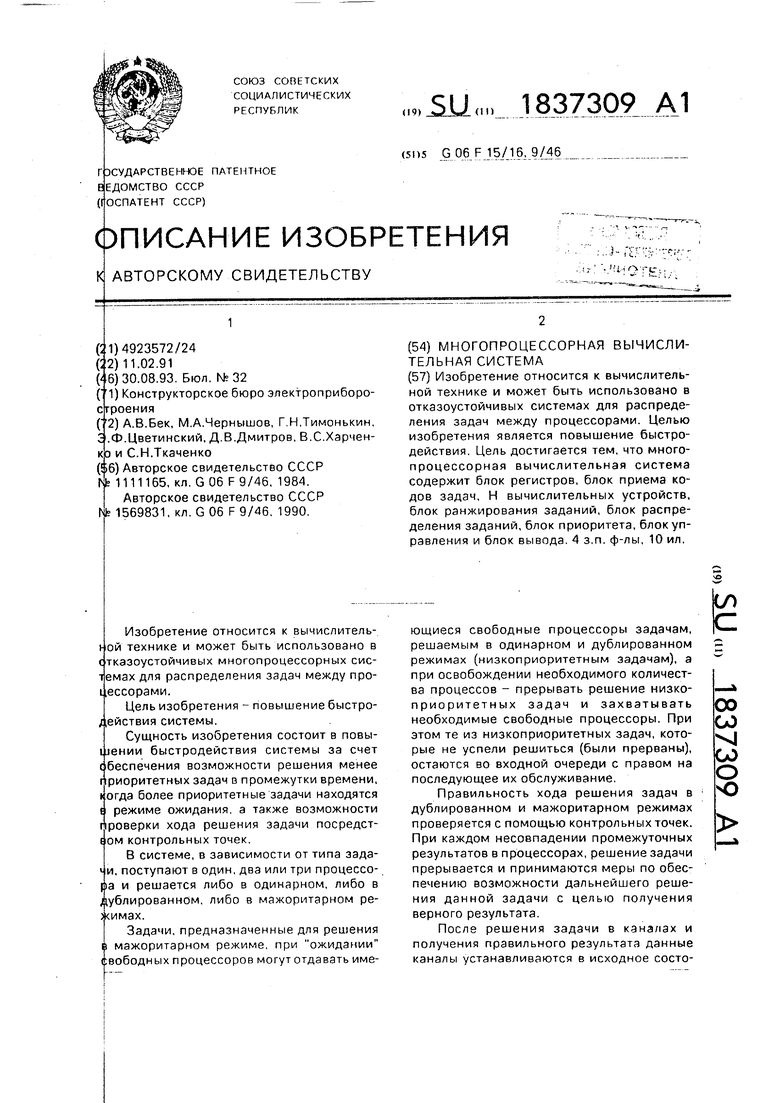

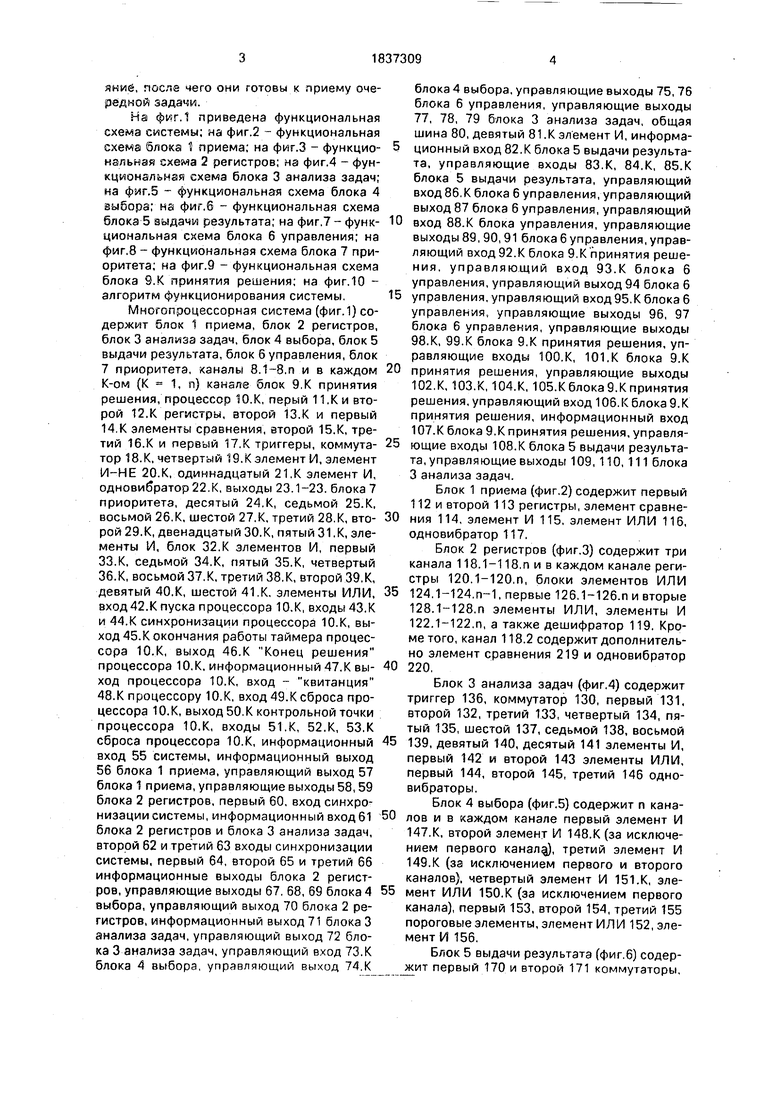

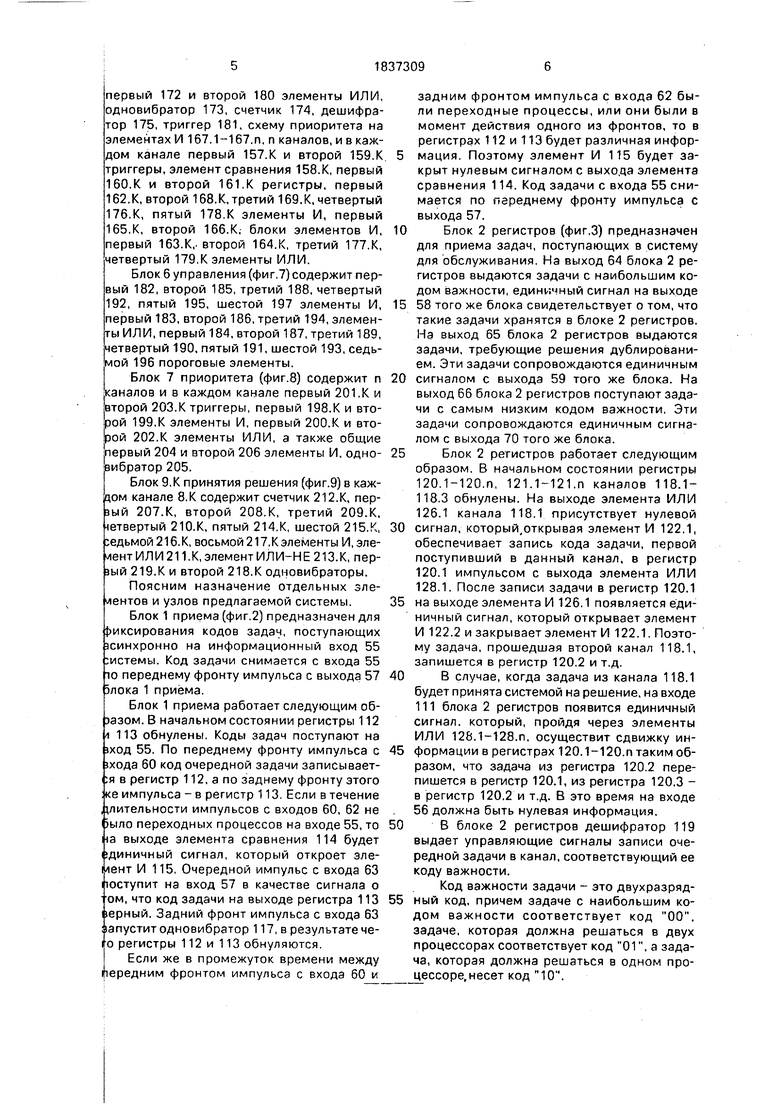

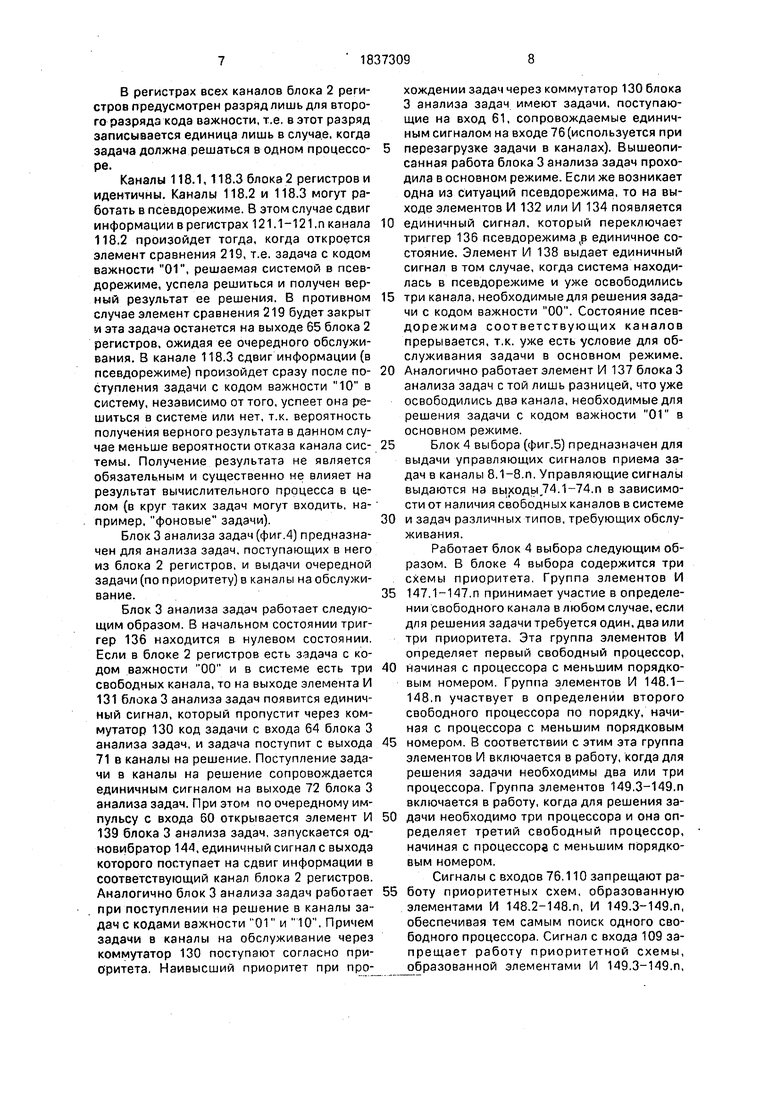

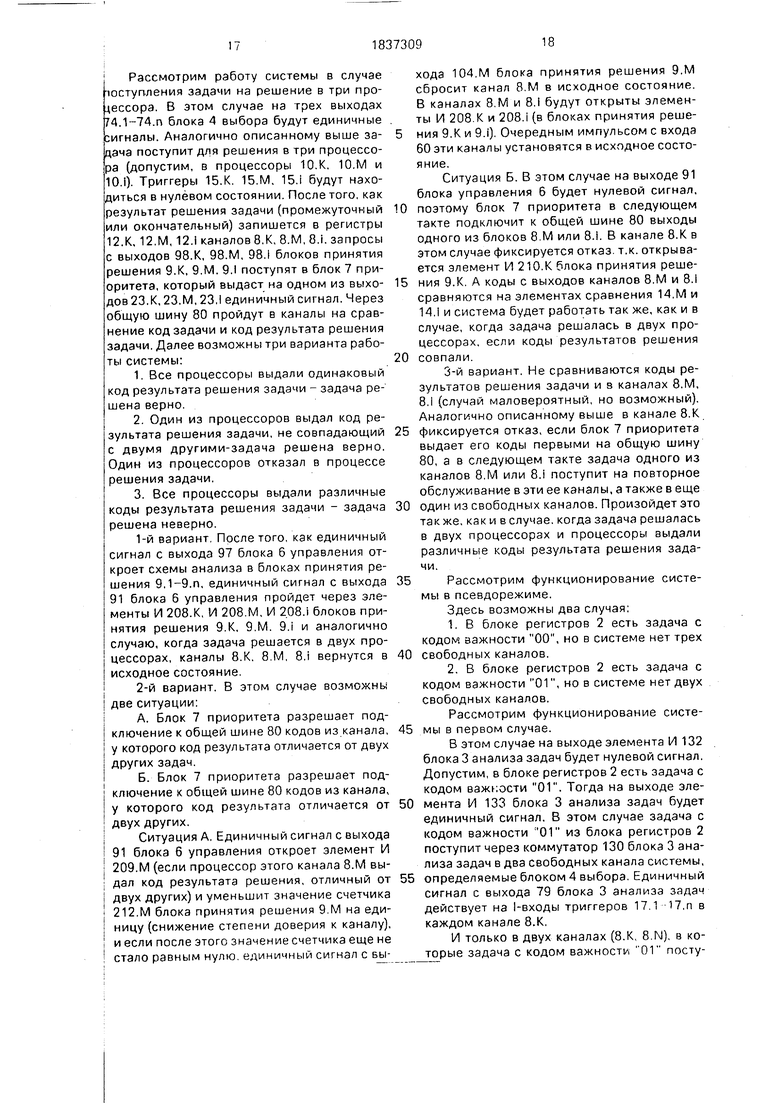

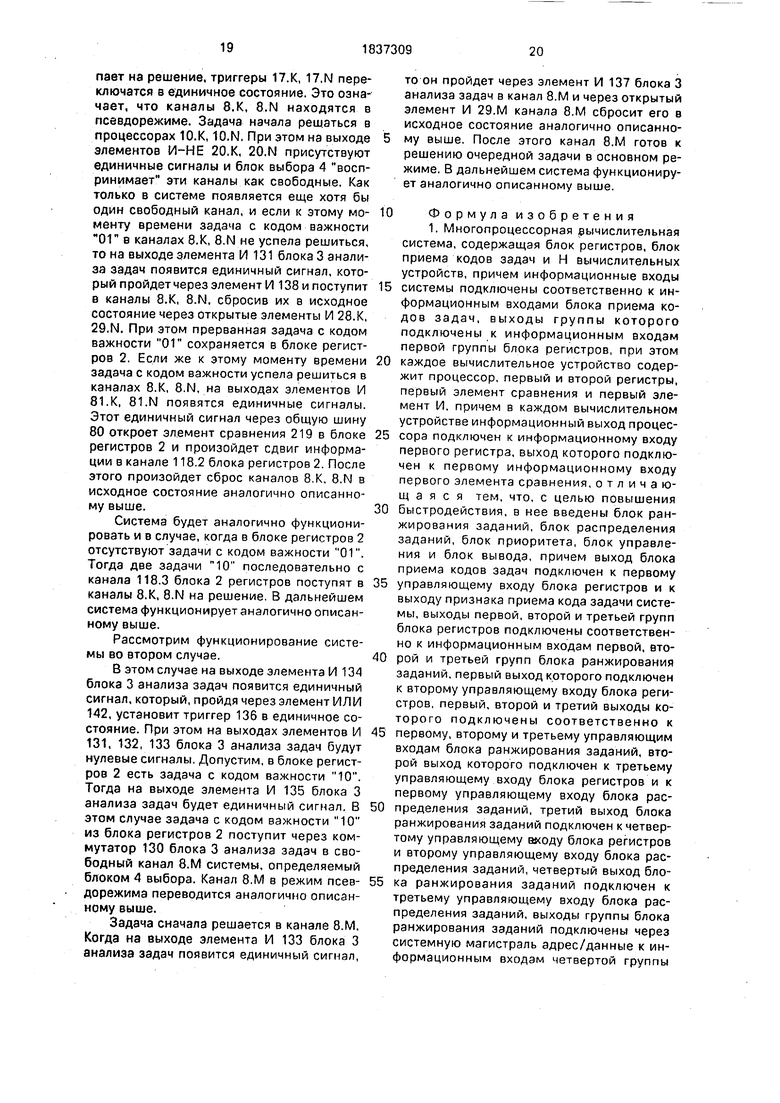

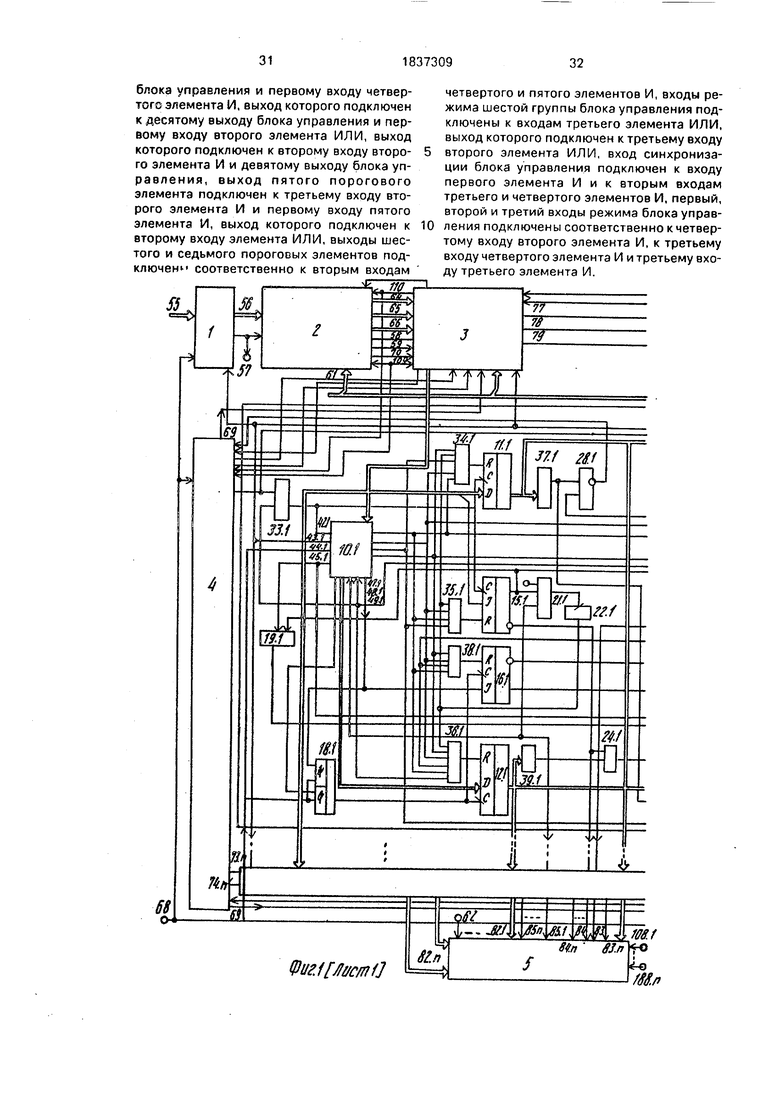

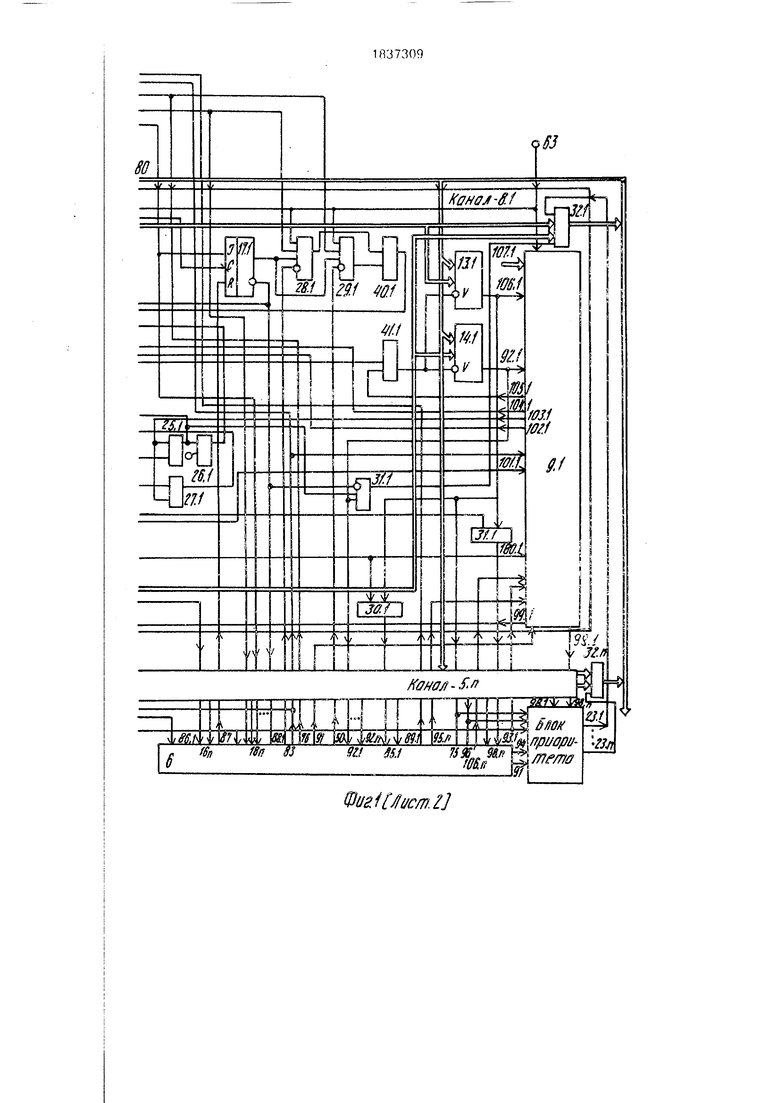

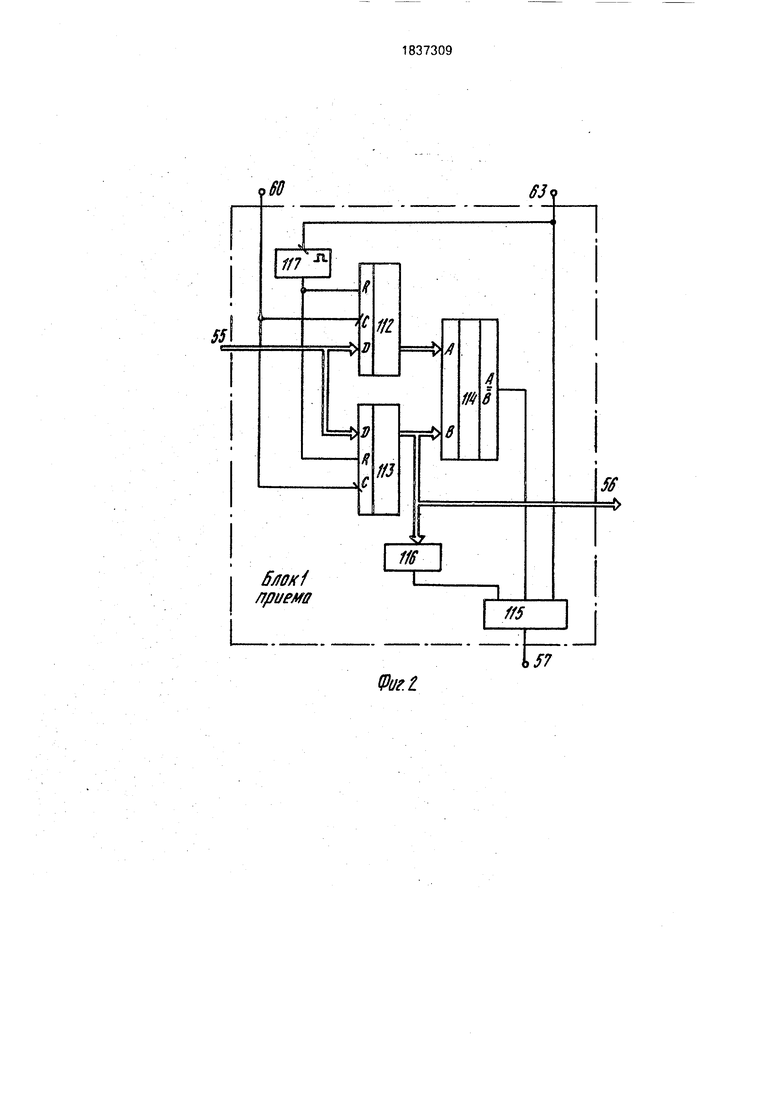

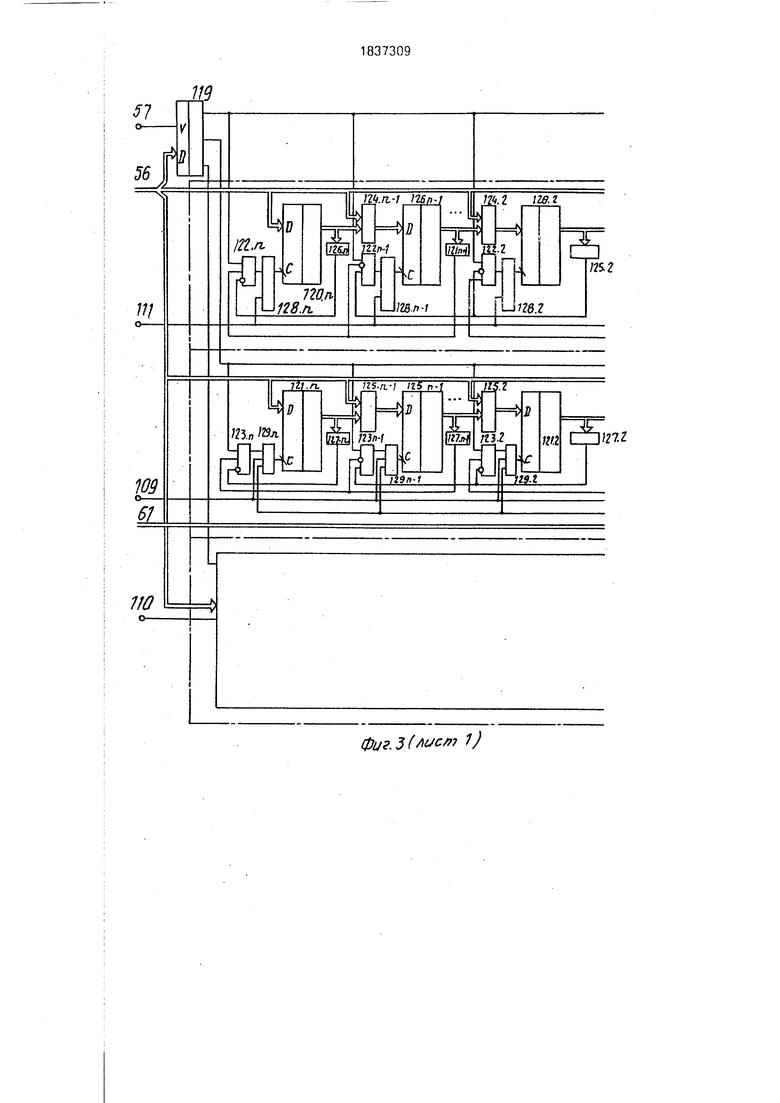

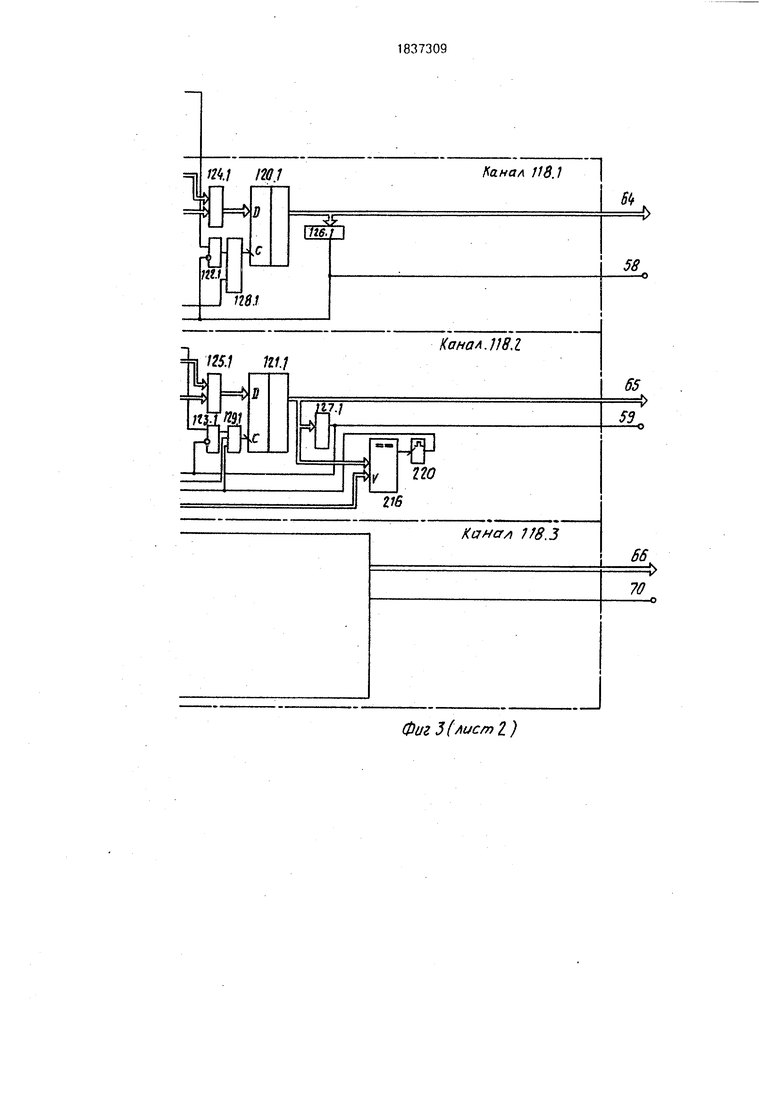

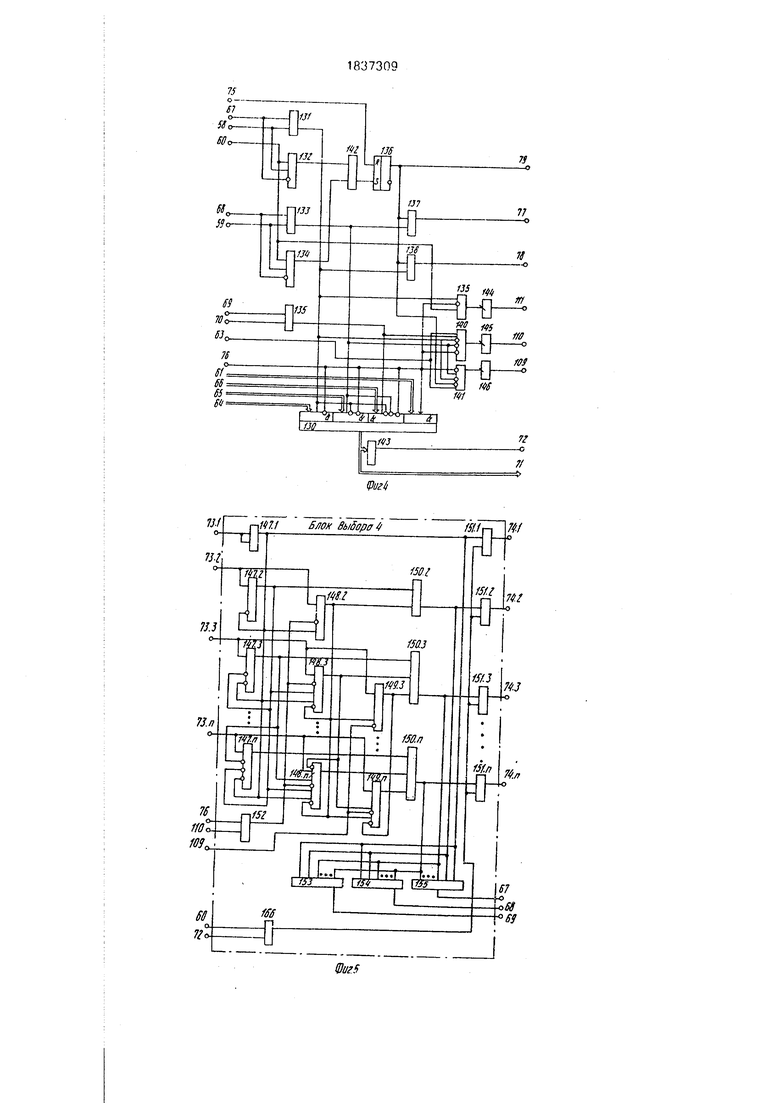

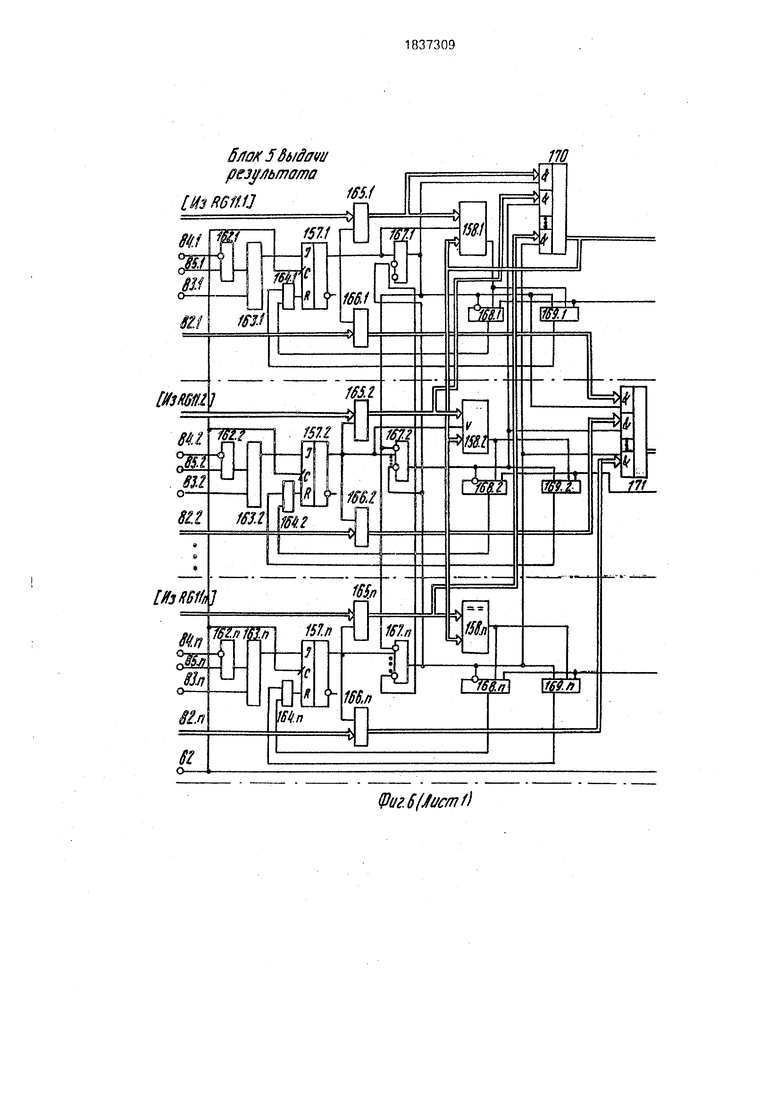

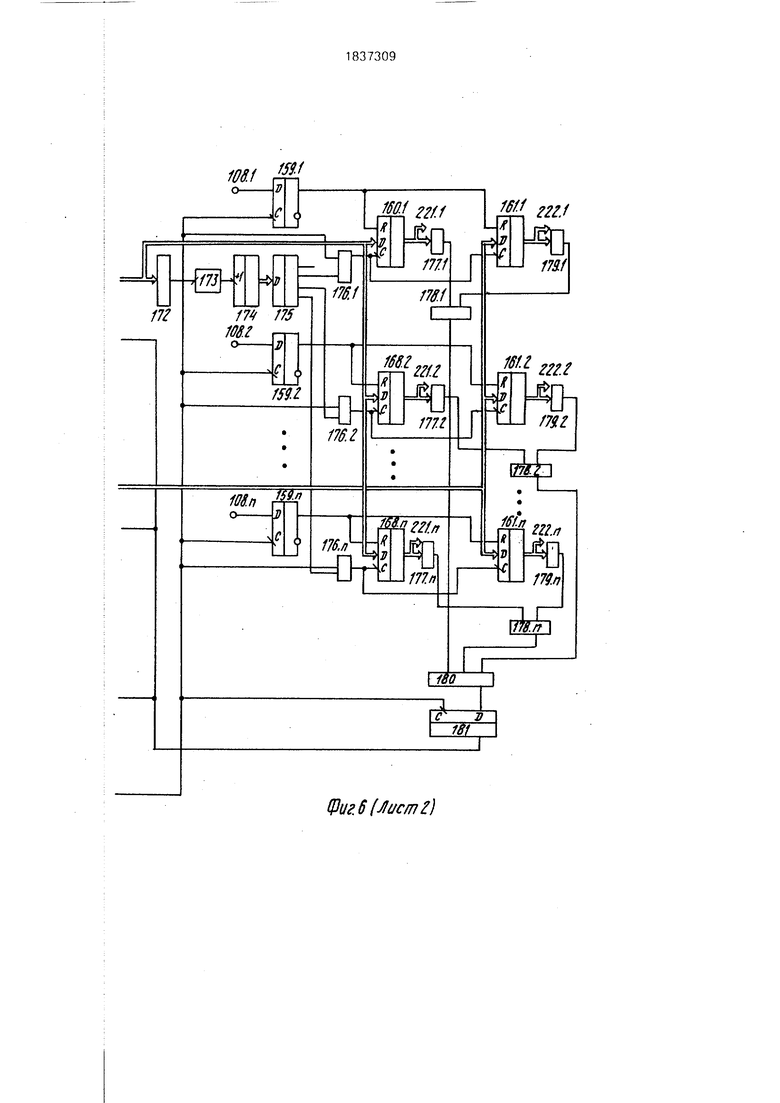

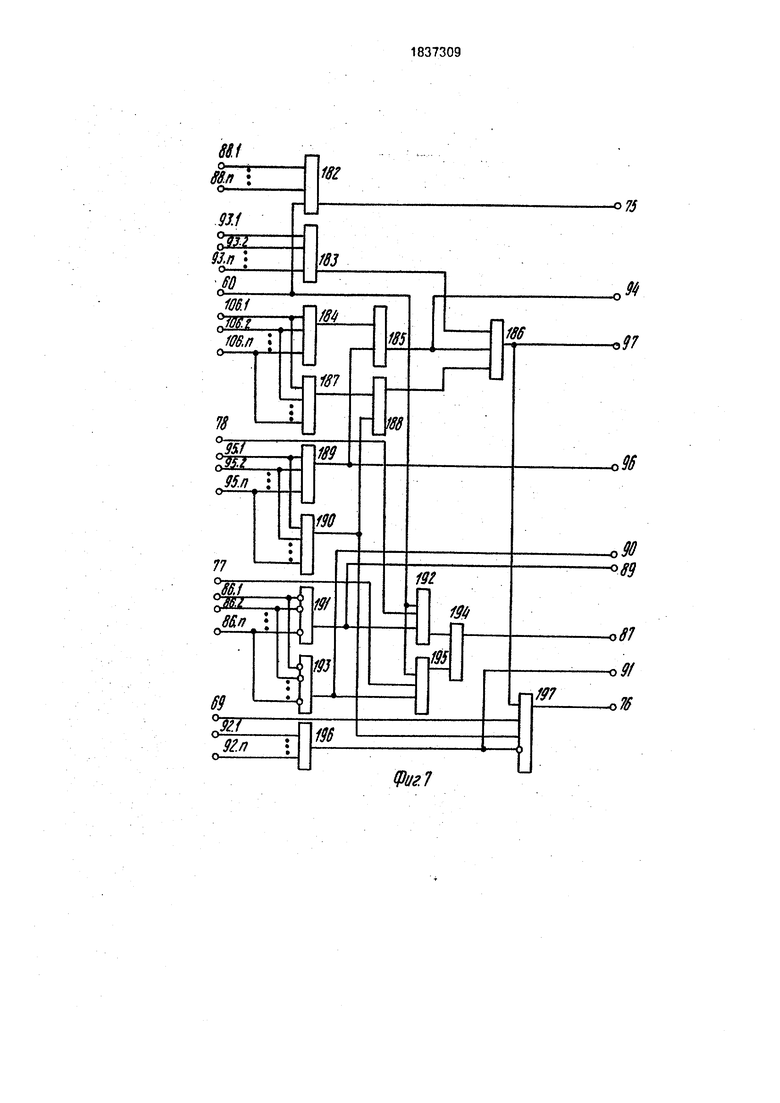

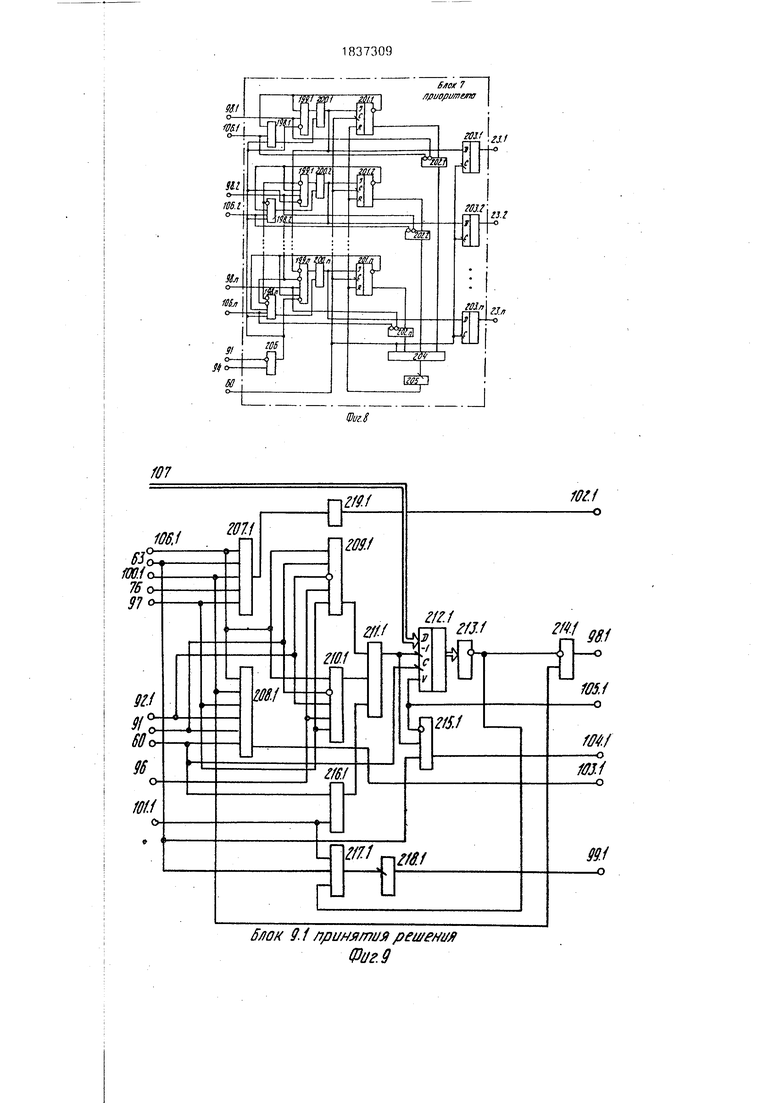

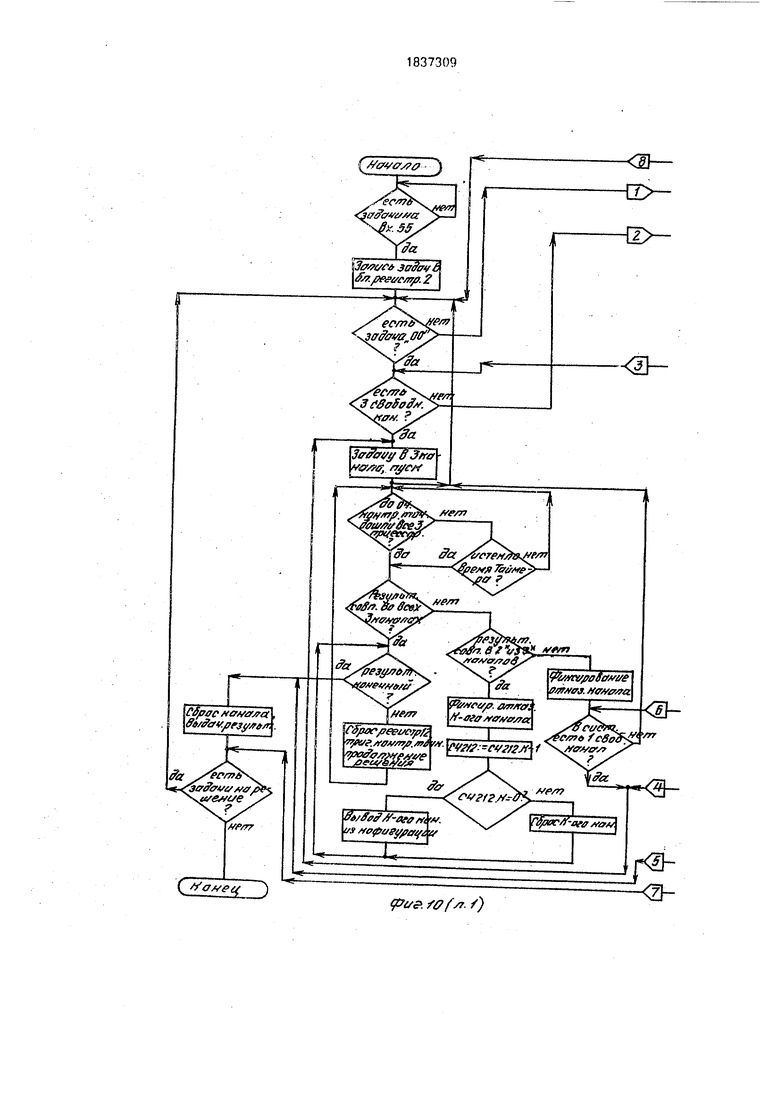

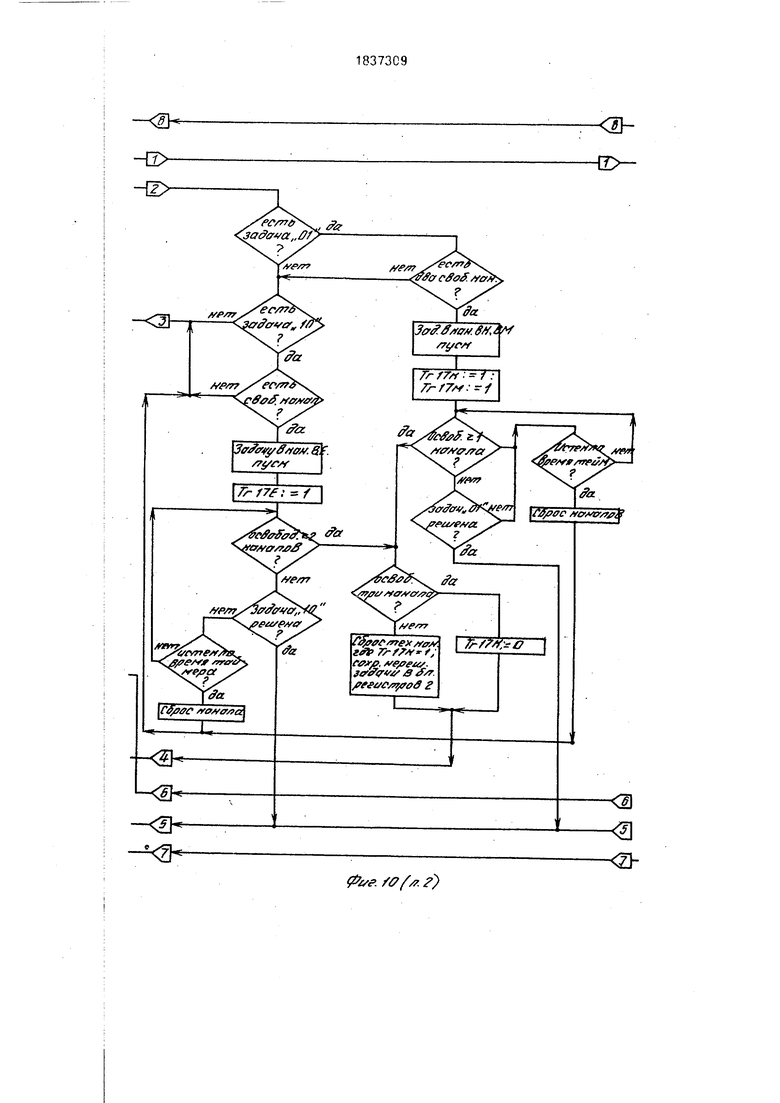

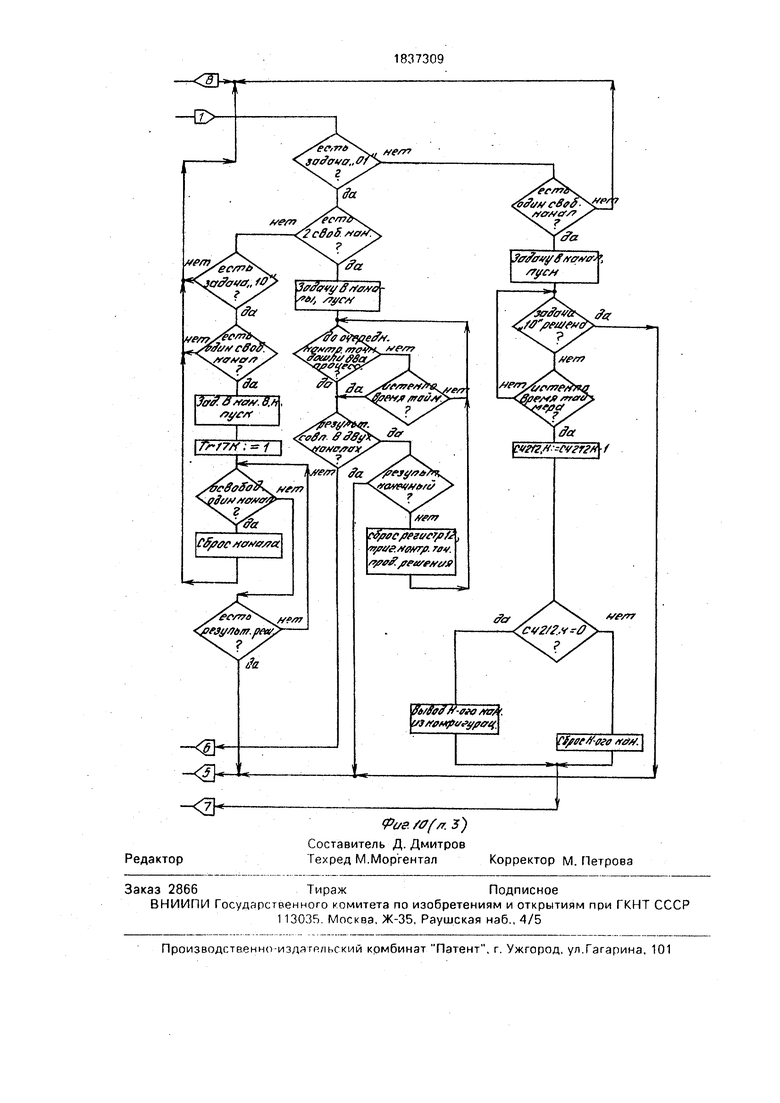

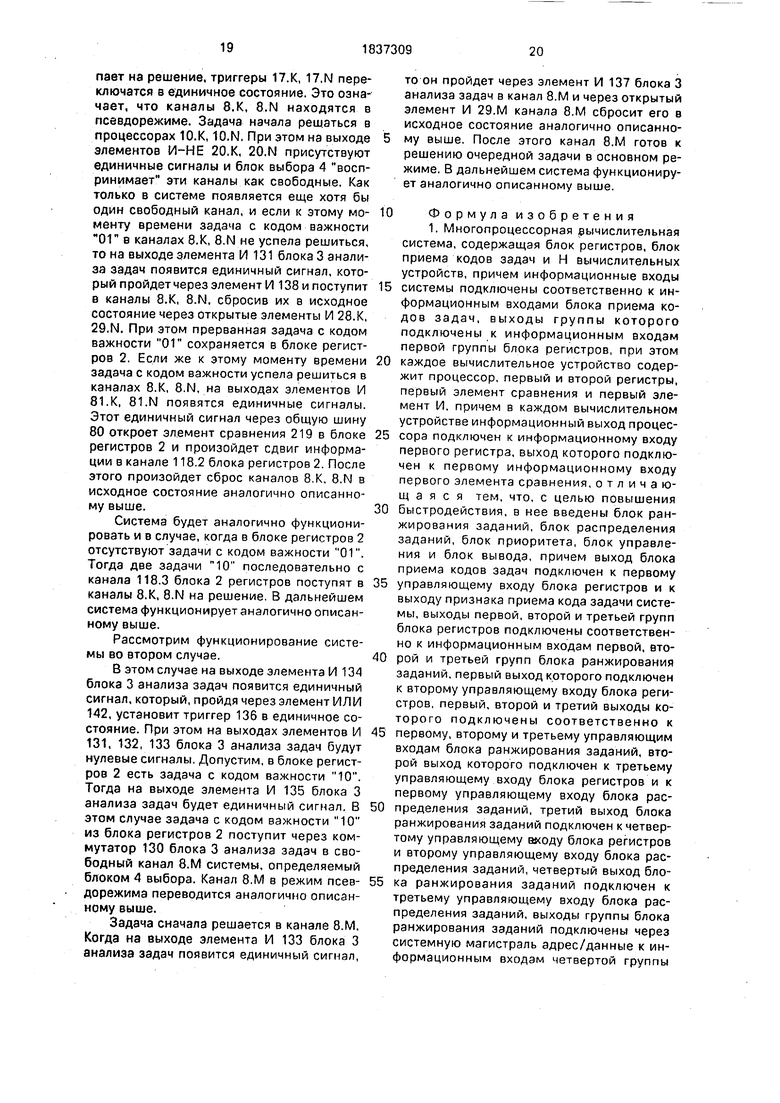

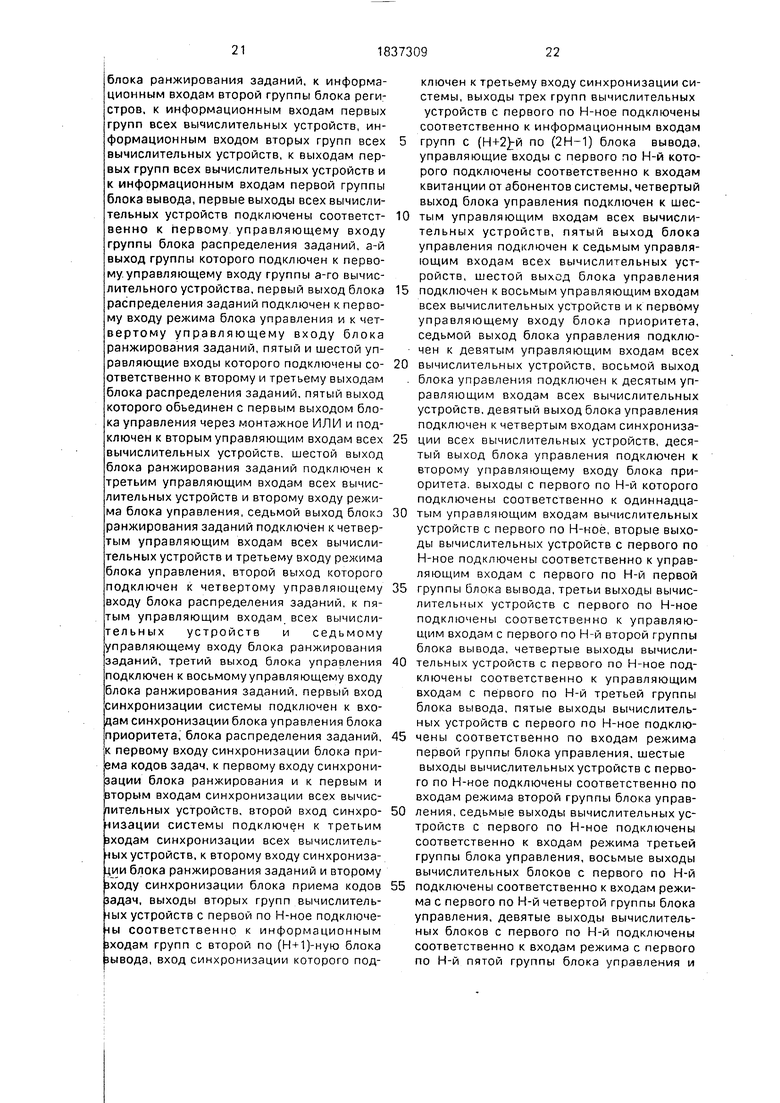

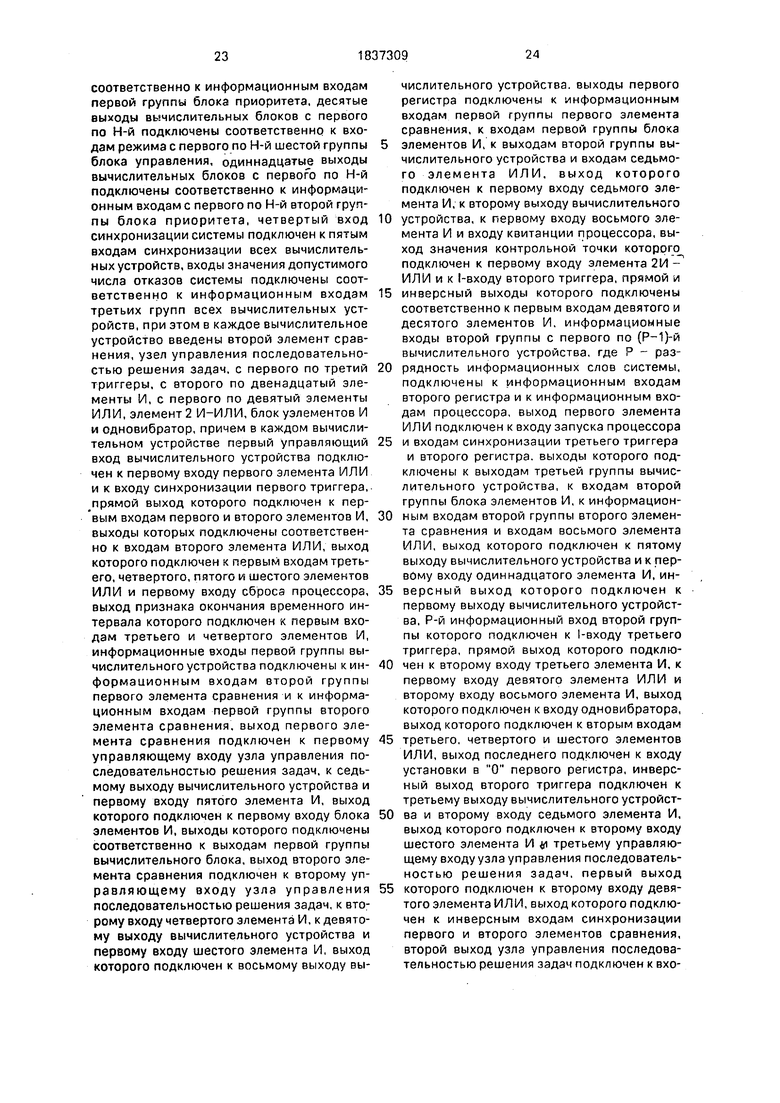

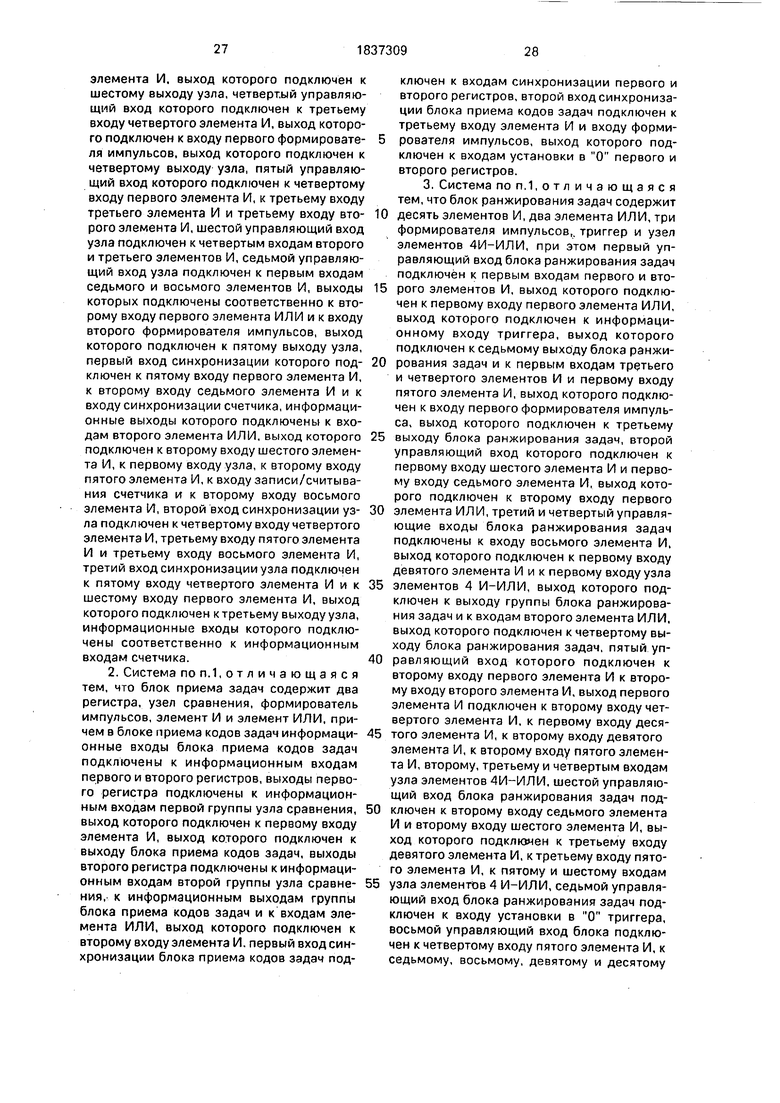

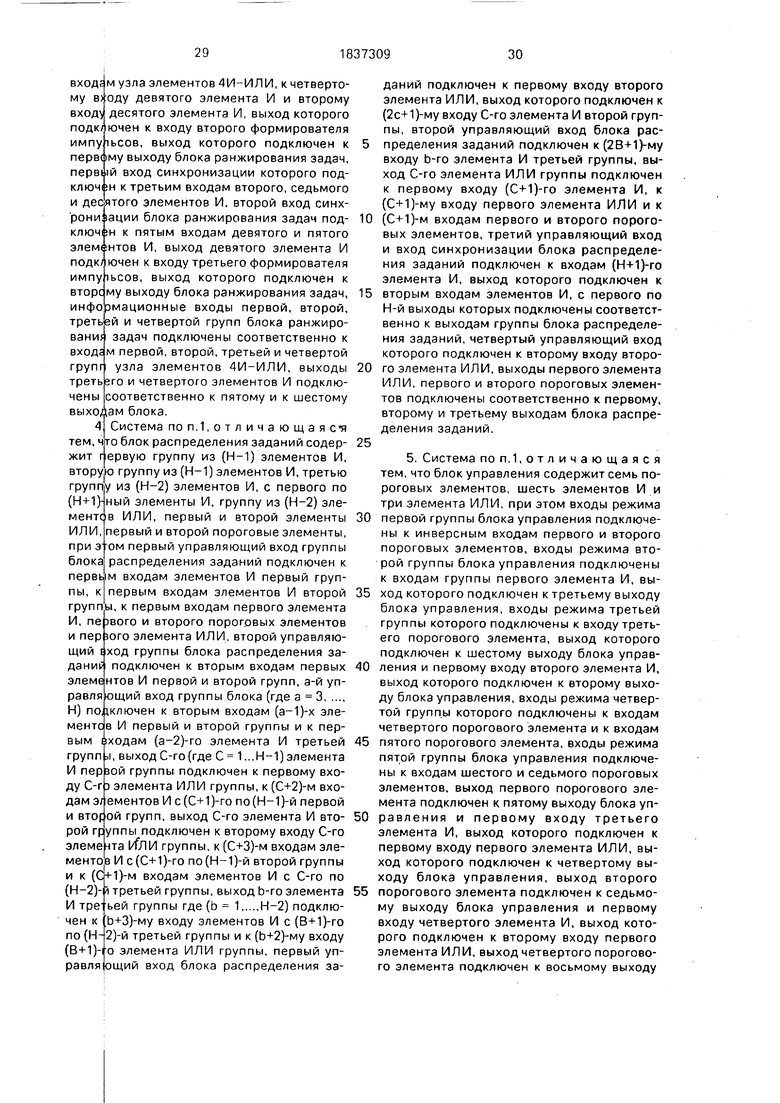

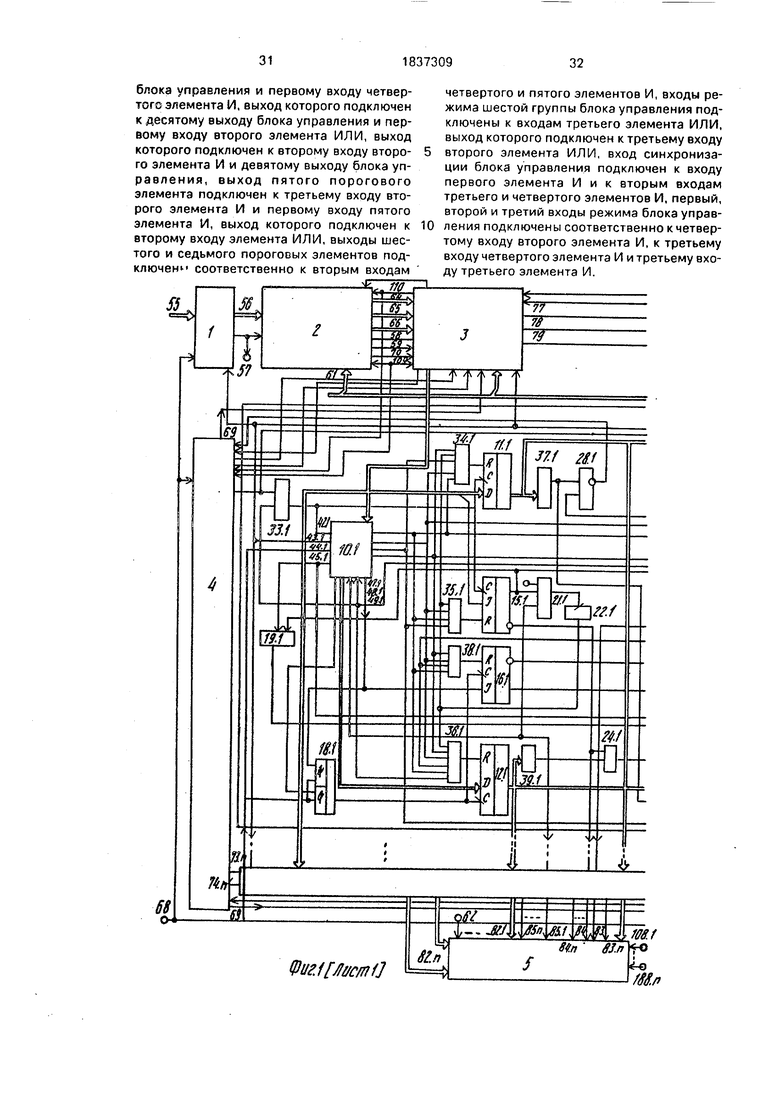

На .1 приведена функциональная схема системы; на фиг.2 - функциональная схема блока I приема; на фиг.З - функцио- нальная схема 2 регистров; на фиг.4 - функциональная схема блока 3 анализа задач; на фиг.5 - функциональная схема блока 4 выбора; на фиг.б - функциональная схема блока 5 выдачи результата; на фиг.7 - функ- циональная схема блока б управления; на фиг.8 - функциональная схема блока 7 приоритета; на фиг.9 - функциональная схема блока 9.К принятия решения; на фиг.10 - алгоритм функционирования системы.

Многопроцессорная система (фиг.1) содержит блок 1 приема, блок 2 регистров, блок 3 анализа задач, блок 4 выбора, блок 5 выдачи результата, блок 6 управления, блок 7 приоритета, каналы 8.1-8.П и в каждом К-ом (К 1, п) канале блок 9.К принятия решения, процессор 10.К, перый 11,К и второй 12.К регистры, второй 13.К и первый 14.К элементы сравнения, второй 15.К, третий 16.К и первый 17.К триггеры, коммута- тор 18. К, четвертый 19.К элемент И, элемент И-НЕ 20.К, одиннадцатый 21.К элемент И, одновибратор 22.К, выходы 23.1-23. блока 7 приоритета, десятый 24.К, седьмой 25.К, восьмой 26.К, шестой 27.К, третий 28.К, вто- рой 29.К, двенадцатый ЗО.К, пятый 31.К, элементы И, блок 32.К элементов И, первый 33.К, седьмой 34.К, пятый 35.К, четвертый 36.К, восьмой 37.К, третий 38.К, второй 39.К, девятый 40.К, шестой 41.К, элементы ИЛИ, вход 42.К пуска процессора 10.К, входы 43.К и 44.К синхронизации процессора 10.К, выход 45.К окончания работы таймера процессора 10.К, выход 46.К Конец решения процессора 10.К, информационный 47.К вы- ход процессора 10.К, вход - квитанция 48.К процессору 10.К, вход 49.К сброса процессора 10.К, выход 50.К контрольной точки процессора 10,К, входы 51.К, 52.К, 53.К сброса процессора 10.К, информационный вход 55 системы, информационный выход 56 блока 1 приема, управляющий выход 57 блока 1 приема, управляющие выходы 58,59 блока 2 регистров, первый 60, вход синхронизации системы, информационный вход 61 блока 2 регистров и блока 3 анализа задач, второй 62 и третий 63 входы синхронизации системы, первый 64, второй 65 и третий 66 информационные выходы блока 2 регистров, управляющие выходы 67. 68, 69 блока 4 выбора, управляющий выход 70 блока 2 регистров, информационный выход 71 блока 3 анализа задач, управляющий выход 72 блока 3 анализа задач, управляющий вход 73.К блока 4 выбора, управляющий выход 74.К

блока 4 выбора, управляющие выходы 75, 76 блока 6 управления, управляющие выходы 77, 78, 79 блока 3 анализа задач, общая шина 80, девятый 81.К элемент И, информационный вход 82.К блока 5 выдачи результата, управляющие входы 83.К, 84,К, 85.К блока 5 выдачи результата, управляющий вход 86.К блока 6 управления, управляющий выход 87 блока 6 управления, управляющий вход 88.К блока управления, управляющие выходы 89,90,91 блока 6 управления, управляющий вход 92.К блока 9.К принятия решения, управляющий вход 93.К блока 6 управления, управляющий выход 94 блока б управления, управляющий вход 95.К блока 6 управления, управляющие выходы 96, 97 блока 6 управления, управляющие выходы 98.К, 99.К блока 9.К принятия решения, управляющие входы 100.К, 101,К блока 9.К принятия решения, управляющие выходы 102.К, 103.К, 104.К, 105.К блока 9.К принятия решения, управляющий вход 106. К блока 9.К принятия решения, информационный вход 107.К блока 9.«принятия решения, управляющие входы 108.К блока 5 выдачи результата, управляющие выходы 109,110, 111 блока 3 анализа задач.

Блок 1 приема (фиг,2) содержит первый 112 и второй 113 регистры, элемент сравнения 114, элемент И 115, элемент ИЛИ 116, одновибратор 117.

Блок 2 регистров (фиг.З) содержит три канала 118.1-118.п и в каждом канале регистры 120.1-120,п, блоки элементов ИЛИ 124.1-124.п-1, первые 126.1-126.п и вторые 128.1-128.п элементы ИЛИ, элементы И 122.1-122.п, а также дешифратор 119. Кроме того, канал 118.2 содержит дополнительно элемент сравнения 219 и одновибратор 220.

Блок 3 анализа задач (фиг.4) содержит триггер 136, коммутатор 130, первый 131, второй 132, третий 133, четвертый 134, пятый 135, шестой 137, седьмой 138, восьмой 139, девятый 140, десятый 141 элементы И, первый 142 и второй 143 элементы ИЛИ, первый 144, второй 145, третий 146 одно- вибраторы.

Блок 4 выбора (фиг.5) содержит п каналов и в каждом канале первый элемент И 147.К, второй элемент И 148.К (за исключением первого канала,), третий элемент И 149.К (зз исключением первого и второго каналов), четвертый элемент И 151.К, элемент ИЛИ 150.К (за исключением первого канала), первый 153, второй 154, третий 155 пороговые элементы, элемент ИЛИ 152, элемент И 156.

Блок 5 выдачи результата (фиг.б) содержит первый 170 и второй 171 коммутаторы,

первый 172 и второй 180 элементы ИЛИ, одновибратор 173, счетчик 174, дешифратор 175, триггер 181, схему приоритета на элементах И 167.1-167.n, n каналов, и в каждом канале первый 157.К и второй 159.К триггеры, элемент сравнения 158.К, первый 160.К и второй 161.К регистры, первый 162.К, второй 168.К, третий 169.К, четвертый 176.К, пятый 178.К элементы И, первый 165.К, второй 166.К, блоки элементов И, первый 163.К,- второй 164.К, третий 177.К, четвертый 179.К элементы ИЛИ.

Блок 6 управления (фиг.7) содержит первый 182, второй 185, третий 188, четвертый 192, пятый 195, шестой 197 элементы И, первый 183, второй 186, третий 194, элементы ИЛИ, первый 184, второй 187, третий 189, четвертый 190, пятый 191, шестой 193, седь- ой 196 пороговые элементы.

Блок 7 приоритета (фиг.8) содержит n каналов и в каждом канале первый 201.К и второй 203.К триггеры, первый 198.К и вто- ой 199,К элементы И, первый 200.К и вто- ой 202.К элементы ИЛИ, а также общие ервый 204 и второй 206 элементы И, одно- ибратор 205.

Блок 9.К принятия решения (фиг.9) в каж- цом канале 8.К содержит счетчик 212.К, пер- зый 207.К, второй 208.К, третий 209.К, 1етвертый 210.К, пятый 214.К, шестой 215.К, ;едьмой216.К, восьмой 217,К элементы И, эле- иентИЛИ 211.К, элемент ИЛИ-НЕ 213.К, пер- зый 219.К и второй 218.К одновибраторы.

Поясним назначение отдельных зле- иентов и узлов предлагаемой системы.

Блок 1 приема (фиг.2) предназначен для фиксирования кодов задач, поступающих асинхронно на информационный вход 55 :истемы. Код задачи снимается с входа 55 ю переднему фронту импульса с выхода 57 элока 1 приёма.

Блок 1 приема работает следующим об- зазом. В начальном состоянии регистры 112 1 113 обнулены. Коды задач поступают на жод 55. По переднему фронту импульса с $хода 60 код очередной задачи записывает- :я в регистр 112, а по заднему фронту этого ке импульса -в регистр 113. Если в течение длительности импульсов с входов 60, 62 не шло переходных процессов на входе 55, то ta выходе элемента сравнения 114 будет | диничный сигнал, который откроет элемент И 115. Очередной импульс с входа 63 поступит на вход 57 в качестве сигнала о ом, что код задачи на выходе регистра 113 верный. Задний фронт импульса с входа 63 запустит одновибратор 117, в результате чего регистры 112 и 113 обнуляются.

Если же в промежуток времени между передним фронтом импульса с входа 60 и

задним фронтом импульса с входа 62 были переходные процессы, или они были в момент действия одного из фронтов, то в регистрах 112 и 113 будет различная инфор- мация. Поэтому элемент И 115 будет закрыт нулевым сигналом с выхода элемента сравнения 114. Код задачи с входа 55 снимается по переднему фронту импульса с выхода 57.

0Блок 2 регистров (фиг.З) предназначен

для приема задач, поступающих в систему для обслуживания. На выход 64 блока 2 регистров выдаются задачи с наибольшим кодом важности, единичный сигнал на выходе

5 58 того же блока свидетельствует о том, что такие задачи хранятся в блоке 2 регистров, На выход 65 блока 2 регистров выдаются задачи, требующие решения дублированием. Эти задачи сопровождаются единичным

0 сигналом с выхода 59 того же блока. На выход 66 блока 2 регистров поступают задачи с самым низким кодом важности, Эти задачи сопровождаются единичным сигналом с выхода 70 того же блока.

5Блок 2 регистров работает следующим

образом. В начальном состоянии регистры 120.1-120.п, 121.1-121.n каналов 118.1- 118.3 обнулены. На выходе элемента ИЛИ 126.1 канала 118.1 присутствует нулевой

0 сигнал, который,открывая элемент И 122,1, обеспечивает запись кода задачи, первой поступивший в данный канал, в регистр 120.1 импульсом с выхода элемента ИЛИ 128.1. После записи задачи в регистр 120.1

5 на выходе элемента И 126.1 появляется единичный сигнал, который открывает элемент И 122.2 и закрывает элемент И 122.1. Поэтому задача, прошедшая второй канал 118.1, запишется в регистр 120.2 и т.д.

0В случае, когда задача из канала 118.1

будет принята системой на решение, на входе 111 блока 2 регистров появится единичный сигнал, который, пройдя через элементы ИЛИ 128.1-128.п, осуществит сдвижку ин5 формации в регистрах 120.1-120.п таким образом, что задача из регистра 120.2 перепишется в регистр 120.1, из регистра 120,3 - в регистр 120.2 и т.д. В это время на входе 56 должна быть нулевая информация.

0В блоке 2 регистров дешифратор 119

выдает управляющие сигналы записи очередной задачи в канал, соответствующий ее коду важности.

Код важности задачи - это двухразряд5 ный код, причем задаче с наибольшим кодом важности соответствует код 00, задаче, которая должна решаться в двух процессорах соответствует код 01, а задача, которая должна решаться в одном процессоре, несет код 10.

В регистрах всех каналов блока 2 регистров предусмотрен разряд лишь для второго разряда кода важности, т.е. в этот разряд записывается единица лишь в случае, когда задача должна решаться в одном процессе- ре.

Каналы 118.1,118.3 блока 2 регистров и идентичны. Каналы 118.2 и 118.3 могут работать в псевдорежиме. В этом случае сдвиг информации в регистрах 121.1-121,п канала 118.2 произойдет тогда, когда откроется элемент сравнения 219, т.е. задача с кодом важности 01, решаемая системой в псевдорежиме, успела решиться и получен верный результат ее решения. В противном случае элемент сравнения 219 будет закрыт м эта задача останется на выходе 65 блока 2 регистров, ожидая ее очередного обслуживания. В канале 118.3 сдвиг информации (в псевдорежиме) произойдет сразу после по- ступления задачи с кодом важности 10 в систему, независимо от того, успеет она решиться в системе или нет, т.к. вероятность получения верного результата в данном случае меньше вероятности отказа канала сие- темы. Получение результата не является обязательным и существенно не влияет на результат вычислительного процесса в целом (в круг таких задач могут входить, на- пример, фоновые задачи).

Блок 3 анализа задач (фиг.4) предназначен для анализа задач, поступающих в него из блока 2 регистров, и выдачи очередной задачи (по приоритету) в каналы на обслуживание.

Блок 3 анализа задач работает следующим образом. В начальном состоянии триггер 136 находится в нулевом состоянии. Если в блоке 2 регистров есть задача с кодом важности 00 и в системе есть три свободных канала, то на выходе элемента И 131 блока 3 анализа задач появится единичный сигнал, который пропустит через коммутатор 130 код задачи с входа 64 блока 3 анализа задач, и задача поступит с выхода 71 в каналы на решение. Поступление задачи в каналы на решение сопровождается единичным сигналом на выходе 72 блока 3 анализа задач. При этом по очередному импульсу с входа 60 открывается элемент И 139 блока 3 анализа задач, запускается од- новибратор 144, единичный сигнал с выхода которого поступает на сдвиг информации в соответствующий канал блока 2 регистров. Аналогично блок 3 анализа задач работает при поступлении на решение в каналы задач с кодами важности 01 и 10. Причем задачи в каналы на обслуживание через коммутатор 130 поступают согласно приоритета. Наивысший приоритет при прохождении задач через коммутатор 130 блока 3 анализа задач имеют задачи, поступающие на вход 61, сопровождаемые единичным сигналом на входе 76 (используется при перезагрузке задачи в каналах). Вышеописанная работа блока 3 анализа задач проходила в основном режиме. Если же возникает одна из ситуаций псевдорежима, то на выходе элементов И 132 или И 134 появляется единичный сигнал, который переключает триггер 136 псевдорежима единичное состояние. Элемент И 138 выдает единичный сигнал в том случае, когда система находилась в псевдорежиме и уже освободились три канала, необходимые для решения задачи с кодом важности 00. Состояние псевдорежима соответствующих каналов прерывается, т.к. уже есть условие для обслуживания задачи в основном режиме. Аналогично работает элемент И 137 блока 3 анализа задач с той лишь разницей, что уже освободились два канала, необходимые для решения задачи с кодом важности 01 в основном режиме.

Блок 4 выбора (фиг.5) предназначен для выдачи управляющих сигналов приема задач в каналы 8.1-8.п. Управляющие сигналы выдаются на вцходы,74.1-74.п в зависимости от наличия свободных каналов в системе и задач различных типов, требующих обслуживания.

Работает блок 4 выбора следующим образом. В блоке 4 выбора содержится три схемы приоритета. Группа элементов И 147.1-147.п принимает участие в определении свободного канала в любом случае, если для решения задачи требуется один, два или три приоритета. Эта группа элементов И определяет первый свободный процессор, начиная с процессора с меньшим порядковым номером. Группа элементов И 148.1- 148,п участвует в определении второго свободного процессора по порядку, начиная с процессора с меньшим порядковым номером. В соответствии с этим эта группа элементов И включается в работу, когда для решения задачи необходимы два или три процессора. Группа элементов 149.3-149.п включается в работу, когда для решения задачи необходимо три процессора и она определяет третий свободный процессор, начиная с процессора с меньшим порядковым номером.

Сигналы с входов 76.110 запрещают работу приоритетных схем, образованную элементами И 148.2-148.П, И 149.3-149.п, обеспечивая тем самым поиск одного свободного процессора. Сигнал с входа 109 запрещает работу приоритетной схемы, образованной элементами И 149.3-149.п,

|беспечивая поиск двух свободных процес- оров. На выходе 67 блока 4 выбора будет 1ДИНИЧНЫЙ сигнал в случае, когда в системе сть хотя бы три свободных процессора, на исходе 68 - когда в системе есть хотя бы два ;вободных процессора, на выходе 69 - когда в системе есть хотя бы один свободный процессор.

Блок 5 выдачи результата (фиг.б) предназначен для приема кодов задач и кодов результатов решения задач, их хранения и зыдачи абоненту.

Блок 5 выдачи результата работает следующим образом.

В начальном состоянии триггеры 157.1- 57.п, 159.1-159.п. 181, регистры 160.1- 60.п, 161.1-161.п, счетчик 174 находятся в левом состоянии. Появление единичного :игнала на выходе элемента И 162.К блока i выдачи результатов говорит о том, что адача с кодов важности 10 решена, а еди- мчный сигнал на входе 83.К блока 5 выдачи езультата говорит о том. что завершилось зешение задачи либо с кодом важности 00, либо с кодом важности 01 и получен 1врный результат ее решения. Рассмотрим, ,ак код задачи и код результата решения адачи записываются в блок 5 выдачи ре- 1ультата. Допустим, появился единичный игнал на входах 83.1, 83.2 блока 5 выдачи езультата. К этому моменту времени на ыходах из регистров 11.1,11.2, каналов 8.1, .2 в блоке 5 выдачи результата находится од задачи, а на выходах 82.1, 82.2 - код 1ерного результата решения этой задачи. 1о переднему фронту импульса с входа 62 риггеры 157.1, 157.2 установятся в единич- юе состояние. Так как время срабатывания риггеров 157.1, 157.2 может быть различ- 1ым, то триггер, который первым переклю- ится в единичное состояние (допустим, риггер 157.1), выставит первым на выходе лемента И 167.1 единичный сигнал, который закроет все другие элементы И 167.2- ; 67.п. Код задачи с входа их регистра 11.1 ганала 8.1 блока 5 выдачи результата пройдет через открытый элемент И 1.65.1, через юммутатор 170 и поступит на входы элементов сравнения 158.1-158.п, элемента ИЛИ 172, а также на D-входы регистров 60.1-160.п. На выходах элементов сравнения 158.1, 158.2 появятся единичные сигналы. А код результата решения задачи с ЕХОДЭ 82.1 блока 5 выдачи результата пройдет через открытый элемент И 166.1, через юммутатор 171 и поступит на D-входы регистров 161,1-161.п. По переднему фронту сигнала с выхода элемента ИЛИ 172 сработает одновибратор 173, в счетчик 174 запи- иется единица, на первом выходе

дешифратора 175 появится единичный сигнал, который по переднему фронту импульса с входа 62 откроет элемент И 176.1, а по заднему фронту этого же импульса запишет информацию в регистры 160.1, 161.1. На выходах элементов ИЛИ 177.1, 179.1 появятся единичные сигналы, которые откроют элемент И 178.1, единичный сигнал с выхода которого пройдет через элемент ИЛИ 180 и установит триггер 181 в единичное состояние по заднему фронту импульса с входа 62 блока 5 выдачи результата. Единичный сигнал с выхода, триггера 181 откроет элемент И 169.1, И 168.2,и установит триггеры 157.1. 157,2 в нулевое состояние, после чего они готовы к приему новых запросов на обслуживание. Код задачи и код результата реше- ния задачи выставляются абоненту соответственно на выходы 221.1, 222.1 блока 5 выдачи результатов, после получения которых абонент выставляет единичный сигнал на соответствующем входе 108.1. Триггер 159.1 по заднему фронту импульса с входа 62 установится в единичное состояние и сбросит регистры 160.1, 161.1 в исходное состояние. Регистровая ячейка памяти станет свободной и готовой к записи очередной информации. Запросы от задач с кодами важности 00 и 10 обслуживаются аналогично описанному выше.

Блок 6 управления (фиг.7) предназначен для выдачи управляющих сигналов в каналы 8.1-8.Л,

Блок 6 управления работает следующим образом. Единичный сигнал на выходе 75 блока 6 управления выдает в случае, когда все каналы 8.1-8.П системы работают в основном режиме.

Единичный сигнал на выходе элемента ИЛИ 183 появляется в случае, когда закончилось время решения задачи по таймеру хотя бы в одном канале, который подключен в данный момент времени через общую шину 80. Единичный сигнал на выходе первого элемента 184 появляется в случае, когда задача, подключенная через общую шину 80, решалась в трех процессорах, а на выходе порогового элемента 187- когда задача решалась в двух процессорах. Единичный сигнал на выходе порогового элемента 189 появляется в случае, .когда задача, подключенная через общую шину 80, решалась в трех процессорах, а на выходе порогового элемента 190 - когда задача решалась в двух процессорах. Единичный сигнал на выходе порогового элемента 191 появляется в случае, когда в системе есть менее трех каналов, свободных от решения задач и не находящихся в псевдорежиме, а на выходе порогового элемента 193 - когда в системе

есть ме менее двух свободных каналов. Единичный сигнал на выходе порогового элемента 196 появляется в случае, когда в системе задача, подключенная через общую шину 80, решилась с одинаковым результатом не менее, чем в двух каналах системы. Единичный сигнал на выходе 87 блока 6 управления появляется в случае, когда при появлении сигнала на прерывание псевдорежима в соответствующих каналах, в системе есть другие свободные каналы и поэтому каналы, находящиеся в псевдорежиме, можно перевести в основной режим. Единичный сигнал на выходе элемента И 197 проявляется в случае, когда задача, решаемая в двух процессорах, решилась неправильно и в системе есть еще хотя бы один свободный канал.

Блок 7 приоритета (фиг.8) предназначен для приема сигналов запроса от каналов 8.1-8.п, их обслуживания и выдачи управляющих сигналов на выходы 23.1-23.п.

Блок 7 приоритета работает следующим образом. В канальном состоянии триггеры 201.1-201.п, 203.1-203.п обнулены, на запросных входах 98.1-98.п, 106.1-106.п присутствуют нулевые сигналы, на выходах 23.1-23.п будет также нулевая информация. Запросы от каналов поступают на входы 98.1-98,п. Если одновременно поступает несколько запросов, то приоритетная схема, образованная элементами И 199.1- 199.п, выбирает наиболее приоритетный. После выбора наиболее приоритетного запроса на выходе соответствующего элемента И 199.К (К 1-п) появляется единичный сигнал. По очередному импульсу с входа 60 триггера 201.К и 203.К устанавливаются в единичное состояние. На выходе 23.К появляется единичный сигнал, разрешающий подключение соответствующего канала 8.К к общей шине 80. Каждому каналу запрещается более одного такта подключаться к общей шине 80. Поэтому по следующему тактовому импульсу с входа 60 фиксируется запрос от другого канала на соответствующем триггере 201.М (М 1-n, M К). Если запрос не успел обслужиться за один такт, то повторное разрешение на подключение к общей шине 80 предоставляется после обслуживания всех запросов от других каналов. После одноразового обслуживания всех имеющихся запросов на всех элементах ИЛИ 202,1-202.п появляются единичные сигналы. Очередной импульс с входа 60 пройдет через открытый элемент И 204 и своим задним фронтом запустит одновиб- ратор 205. Импульс с его выхода установит триггеры 201.1-201.п в нулевое состояние. После этого возможно повторное обслуживание запросов. В случае, если на выходе элемента И 206 появляется единичный сигнал, то запрещается работа приоритетной схемы, образованной элементами И

199.1-199.п и разрешается работа приоритетной схемы, образованной элементами И 198.1-198.ri. В этом случае запросными входами являются входы 106.1-106.п. Выбор наиболее приоритетного запроса и его

0 подключение осуществляется аналогично описанному выше.

Блок 9.К принятия решения (фиг.9) в каждом канале 8.К предназначен для анализа результатов решения задач в каналах и

5 на основании его выработки соответствующего решения по дальнейшему функционированию системы.

Блок 9.К принятия решения работает следующим образом.

0В начальном состоянии счетчик 212.К

находится в нулевом состоянии. По заднему фронту импульса с входа 60 в счетчик 212.К записывается информация с входа 107, после чего синхровход счетчика 212.К закры5 вается нулевым сигналом на его разрешающем входе. Информация, записанная в счетчик 212.К, представляет собой код числа отказов, количество которых допустимо для данного канала, т.е. чем мень0 ше число, записанное в счетчик 212.К, тем меньше степень доверия к данному каналу. Когда содержимое счетчика 212.К становится равным нулю, данный канал 8.К выводится из конфигурации системы (на

5 выходе 105.К присутствует единичный сигнал),

Система работает следующим образом.

В начальном состоянии блок 2 регист0 ров. блок 5 выдачи результата не содержит никакой информации. На входы блока 7 приоритета поступают нулевые сигналы, на его выходах 23.1-23.п также нулевые сигналы.

5 На входах блока 4 выбора нулевые сигналы, на его выходах-нулевые сигналы. В каждом К-ом (К 1-п) канале 8.К регистры 11.К, 12.К, триггеры 15.К, 16.К, 17.К, а также счетчик в блоке принятия решения 9.К

0 обнулены,процессорное устройство 10.К находится в исходном состоянии и работоспособно. Задачи поступают на вход 55 системы, после чего они фиксируются в блоке 2 регистров.

5 В системе предусмотрено поступление задач трех типов. Тип задачи определяется кодом важности, который поступает в систему на вход 55 вместе с кодом задачи. Код важности ноль (1) определяет, что задача должна обслужиться в системе за минимально возможное время. Поэтому задача с кодом важности два считывается первой из блока регистров 2 через блок анализа задач 3 на выход 71 в три канала на решение. Это позволяет получить правильный результат решения задачи в случае, если даже один из процессоров во время решения задачи отказал. Код важности один О) определяет, что задача должна обслу- житься в системе с повышенной вероятностью получения верного результата. Каждая задача с кодом важности один поступает для обслуживания в два процессора. Если после решения процессоры выдают различные коды результатов решения задачи, то это означает, что один из процессоров во время решения задачи отказал или дал сбой. В этом случае к данной паре процессоров подключается еще один процессор1 системы из числа свободных и исправный, и задача обслуживается повторно уже в трех процессорах. По окончании ее повторного обслуживания определяется отказавший процессор и имеется верный результат решения задачи. Задачи с кодом важности один обслуживаются только после обслуживания всех задач с кодом важности . Задачи с нулевым кодом важности два (10) обслуживаются в одном процессоре и поступают на решение в последнюю очередь/

Блок 4 выбора выдает сигналы в блок анализа задач 3 о наличии свободных процессоров. Единичные сигналы на выходах 74.1-74.п блока 4 выбора свидетельствуют о том, что очередная задача должна постурить для решения в соответствующие процессоры. Эти сигналы могут быть одновременно не более чем на трех выходах 74.1-74.п.

В исходном состоянии счетчик в блоке тринятия решения 9.К каждого канала обну- 1ен. Поэтому в счетчик разрешена запись информации со входа 107.К в каждом канате, после чего D- и С-входы счетчика закры- заются нулевым сигналом на V-входе. После этого счетчик готов к работе. В дальнейшем функционирует только счетный вход счетчи- са, который работает на убывание. В. счет- пик может быть записан код любого целого числа, в зависимости от того, какой крите- )ий отказа выбран для каждого канала. С юмента времени, когда счетчик достиг нуля, данный канал 8.К выводится из конфигу- ации системы. В простейшем случае в ;четчик может быть записана единица и тог- , а, после перого же исправного функциони- ования данного канала (по различным причинам, например, сбой и др.). данный

канал 8.К выводится из конфигурации системы.

Система функционирует в следующих двух режимах:

1) - основной режим,

2) - псевдорежим.

Рассмотрим функционирование системы в основном режиме.

В основном режиме в систему могут по0 ступать задачи, требующие решения в одном, двух или трех процессорах.

Рассмотрим работу системы в случае поступления задачи на решение в один процессор с кодом важности (10).

5 Задача, находящаяся на выходе 66 блока регистров (с кодом важности (10), проходит в один из каналов системы, выбранный блоком выбора 4, через коммутатор блока анализа задач 3 (при условии, что в блоке

0 регистров 2 нет задач с кодами важности 01 и 00), после чего на выходе 72 блока анализа задач появится единичный сигнал, Только на одном выходе 74. К блока выбора 4 появится единичный сигнал, поэтому код зада5 чи запишется в регистр 11.К этого канала по заднему фронту импульса с входа 60.

Кроме того, единичный сигнал с выхода элемента ИЛИ 33.К поступит на вход 42.К процессора 10.К в качестве сигнала Пуск,

0 а также установит триггер 15.К в единичное состояние. Процессор 10.К запустился на решение задачи, программируемый таймер данного процессора начал отсчет времени выполнения задачи. На выходе элемента И

5 20.К появился нулевой сигнал, который информирует блок выбора 4 о том, что данный канал занят обслуживанием задачи. Заметим, что для задач с кодом важности 10 контрольных точек не предусмотрено. Если

0 решение данной задачи прошло успешно (по истечении времени таймера), то на выходе 47.К процессора 10.К появляется код результата решения данной задачи, сопровождающийся единичным сигналом

5 на выходе 46. К процессора 10.К. Этот сигнал пройдет через коммутатор 18.К, после чего результат решения задачи запишется в регистр 12.К по заднему фронту импульса с входа 60. На выходе элемента ИЛИ 39.К

0 появится единичный сигнал, который по переднему фронту импульса с входа 63 откроет элемент И 21.К и пройдет через одновибратор 22,К на сброс канала в исходное состояние, после чего данный канал го5 тов к приему очередной задачи.

Если же по каким-либо причинам результат решения задачи не появился на выходе 47.К процессора 10.К, то по истечении времени, отсчитываемого таймером, на выходе 45.К процессора 10.К появится единичный сигнал, который откроет элемент И 19.К и поступит на вход 101 блока принятия решения, который, уменьшив значение счетчиков отказов на единицу (уменьшение степени доверия к каналу), выдает единич- ный сигнал на выход 99, который установит данный канал в исходное состояние.

Рассмотрим работу системы в случае поступления задачи на решение в два процессора (допустим, в процессоры 10.К и 10.М). В этом случае триггер 15. К (15.М) будет находиться в нулевом состоянии. По до- стижении процессором 10.К (10.М) контрольной точки на выходе 47.К (47.М) процессора Ю.К(10.М)будет находиться ре- зультат промежуточных вычислений, который сопровождается единичным сигналом на выходе 50.К (50.М) процессора 10.К (10.М), Этот сигнал пройдет через коммутатор 18.К (18.М) и запишет в регистр 12.К (12.М) результат промежуточных вычислений, а триггер 16.К (16.М) переключит в единичное состояние по заднему фронту импульса с входа 60. Сигнал с выхода элемента ИЛИ 39.К (39.М) поступит через от- крытый элемент И 24.К (24.М) на вход 100 блока принятия решения в качестве сигнала запроса. Блок приоритета 7 анализирует все поступившие запросы и выдает единичный сигнал на одном из выходов 23.1-23.п. Если нет более высокоприоритетных запросов, то выдается единичный сигнал на выходе 23.К, разрешая подключение кода задачи и кода результата решения задачи через блок элементов И 32.К к общей шине 80. Код задачи через общую шину 80 подключается к входам всех элементов сравнения 13.1- 13.п, а код результат решения задачи - к входам всех элементов сравнения 14.1- 14.п. В каналах 8.К и 8.М происходит срав- нение кодов задач, следовательно, появляются единичные сигналы на выходах элементов сравнения 13.К и 13.М. Далее возможны два варианта работы системы:

1.Коды результатов решения задачи на элементах сравнения 14.К и 14.М совпали - результат решения правильный,

2.Коды результатов решения задачи на элементах сравнения 14.К и 14.М не совпали - результат решения не верный.

1-й вариант. В этом случае на выходе 97 блока управления 6 появится единичный сигнал, который откроет схемы анализа в блоках принятия решения 9.К и 9.М. В блоках принятия решения 9.К и 9.М на выходах элементов И 208.К, И 208.М появятся единичные сигналы, которые поступят на соответствующие выходы 103.К и 103.М. Если в регистрах 12.К и 12.М записан промежуточный результат (очередная контрольная точка), то сигнал с выхода 103.К, 103.М блоков принятия решений 9.К, 9.М откроет в каналах 8.К и 8.М соответствующие элементы И 27.К, 27.М, единичный сигнал с выходов которых сбросит триггеры 16.К, 16.Ми регистры 12.К, 12.М в нулевое состояние, тем самым подготовив их для фиксирования очередной контрольной точки.

Если же в регистрах 12.К, 12.М записан окончательный результат, то сигналы с выходов 103.К, 103.М блоков принятия решения 9,К, 9.М откроют в каналах 8.К, 8.М соответствующие элементы И 25.К, 25.М, единичный сигнал с выходов которых (после приема блоком выдачи результата исходного кода и кода результата решения задачи) по переднему фронту импульса с входа 63 пройдет через элементы И 26.К, 26.М на сброс каналов 8,К, 8,М в исходное состояние.

2-ой вариант. В этом случае на выходе 97 блока управления 6 будет единичный сигнал, который открывает схемы анализа в блоках принятия решения 9.К, 9.М. На выходе порогового элемента 196 блока управления 6 будет нулевой сигнал, который откроет элемент И 197 блока управления 6. На его выходе появится единичный сигнал при условии, что в схеме есть хотя бы один свободный процессор, о чем свидетельствует единичный сигнал на выходе 69 блока 4 выбора. Единичный сигнал с выхода 76 блока управления 6 поступит на входы элементов И 207.К, 207.М блоков принятия решения 9.К, 9.М, а также на вход 76 блока выбора 4 и разрешит ему сформировать единичный сигнал только на одном из выходов 74.1-74.п, т.к. в этом случае к решению задачи подключается только один процессор. Кроме того, этот сигнал разрешит проход через коммутатор 130 блока 1 анализа задач 3 кода задачи с общей шины 80. По очередному импульсу с входа 63 единичный сигнал с выходов 102.К, 102.М блоков принятия решения 9.К, 9.М поступит через элементы ИЛИ 33.К, 33.М каналов 8.К, 8.М и произведет повторный запуск задач для решения в соответствующих процессорах 10.К, 10.М. Кроме того, поочередному импульсу с входа 60 код задачи поступит в один из процессоров, выбранный блоком 4 выбора. Таким образом, задача с выхода регистра 11.К поступит на повторное решение в процессоры 10.К, 10.М, а также в еще один из свободных процессоров. В дальнейшем система при решении этой задачи будет реализовать алгоритм работы, соответствующий поступлению задачи одновременно в три процессора, который рассматривается ниже.

Рассмотрим работу системы в случае юступления задами на решение в три про- дессора. В этом случае на грех выходах 74.1-74.п блока 4 выбора будут единичные сигналы. Аналогично описанному выше за- дача поступит для решения в три процессора (допустим, в процессоры 10.К, 10.М и 10.1). Триггеры 15.К. 15.М, 15.1 будут находиться в нулевом состоянии. После того, как результат решения задачи (промежуточный или окончательный) запишется в регистры 12.К, 12.М, 12.(каналов 8.К, 8.М, 8.i. запросы с выходов 98.К, 98.М, 98.i блоков принятия решения 9.К, 9.М, 9.I поступят в блок 7 приоритета, который выдаст на одном из выхо- дов23.К,23.М, 23,1 единичный сигнал. Через общую шину 80 пройдут в каналы на сравнение код задачи и код результата решения задачи. Далее возможны три варианта работы системы:

1.Все процессоры выдали одинаковый код результата решения задачи - задача решена верно.

2.Один из процессоров выдал код результата решения задачи, не совпадающий с двумя другими-задача решена верно. Один из процессоров отказал в процессе решения задачи,

3.Все процессоры выдали различные коды результата решения задачи - задача решена неверно.

1-й вариант, После того, как единичный сигнал с выхода 97 блока 6 управления откроет схемы анализа в блоках принятия решения 9.1-9.П, единичный сигнал с выхода 91 блока 6 управления пройдет через элементы И 208.К, 1/1 208.М, И 2.08.1 блоков принятия решения 9.К, 9.М. 9.1 и аналогично случаю, когда задача решается в двух процессорах, каналы 8.К. 8.М, 8.1 вернутся в исходное состояние.

2-й вариант. В этом случае возможны две ситуации:

А. Блок 7 приоритета разрешает подключение к общей шине 80 кодов из канала, у которого код результата отличается от двух других задач.

Б. Блок 7 приоритета разрешает подключение х общей шине 80 кодов из канала, у которого код результата отличается от двух других.

Ситуация А, Единичный сигнал с выхода 91 блока 6 управления откроет элемент И 209.М (если процессор этого канала 8.М выдал код результата решения, отличный от двух других) и уменьшит значение счетчика 212.М блока принятия решения 9.М на единицу (снижение степени доверия к каналу), несли после этого значение счетчика еще не стало равным нулю, единичный сигнал с выхода 104.М блока принятия решения 9.М сбросит канал 8.М в исходное состояние. В каналах 8.М и 8.1 будут открыты элементы И 208.К и 208.1 (в блоках принятия решения 9.К и 9.i). Очередным импульсом с входа 60 эти каналы установятся в исходное состояние.

Ситуация Б. В этом случае на выходе 91 блока управления 6 будет нулевой сигнал, поэтому блок 7 приоритета в следующем такте подключит к общей шине 80 выходы одного из блоков 8.М или 8.I. В канале 8.К в этом случае фиксируется отказ, т.к. открывается элемент И 210.К блока принятия решения 9.К. А коды с выходов каналов 8.М и 8.I сравняются на элементах сравнения 14.М и 14.1 и система будет работать так же, как и в случае, когда задача решалась в двух процессорах, если коды результатов решения совпали.

3-й вариант. Не сравниваются коды результатов решения задачи и в каналах 8.М, 8.1 (случай маловероятный, но возможный). Аналогично описанному выше в канале 8.К. фиксируется отказ, если блок 7 приоритета выдает его коды первыми на общую шину 80, а в следующем такте задача одного из каналов 8.М или 8.1 поступит на повторное обслуживание в эти ее каналы, а также в еще один из свободных каналов. Произойдет это так же, какие случае, когда задача решалась в двух процессорах и процессоры выдали различные коды результата решения задачи.

Рассмотрим функционирование системы в псевдорежиме.

Здесь возможны два случая:

1.В блоке регистров 2 есть задача с кодом важности 00, но в системе нет трех свободных каналов.

2.В блоке регистров 2 есть задача с кодом важности 01, но в системе нет двух свободных каналов.

Рассмотрим функционирование системы в первом случае.

В этом случае на выходе элемента И 132 блока 3 анализа задач будет нулевой сигнал. Допустим, в блоке регистров 2 есть задача с кодом важности 01. Тогда на выходе элемента И 133 блока 3 анализа задач будет единичный сигнал. В этом случае задача с кодом важности 01 из блока регистров 2 поступит через коммутатор 130 блока 3 анализа задач в два свободных канала системы, определяемые блоком 4 выбора. Единичный сигнал с выхода 79 блока 3 анализа задач действует на l-входы триггеров 17.1--17.П в каждом канале 8.К.

И только в двух каналах (8.К, 8.N), в которые задача с кодом важности 01 постулает на решение, триггеры 17.К, 17.N переключатся в единичное состояние. Это означает, что каналы 8.К, 8.N находятся в псевдорежиме. Задача начала решаться в процессорах 10.К, 10.N, При этом на выходе элементов И-НЕ 20.К, 20.N присутствуют единичные сигналы и блок выбора 4 воспринимает эти каналы как свободные. Как только в системе появляется еще хотя бы один свободный канал, и если к этому моменту времени задача с кодом важности 01 в каналах 8.К, 8.N не успела решиться, то на выходе элемента И 131 блока 3 анализа задач появится единичный сигнал, который пройдет через элемент И 138 и поступит в каналы 8.К, 8.N. сбросив их в исходное состояние через открытые элементы И 28.К, 29.N. При этом прерванная задача с кодом важности 01 сохраняется в блоке регистров 2. Если же к этому моменту времени задача с кодом важности успела решиться в каналах 8.К, 8.N, на выходах элементов И 81.К, 81.N появятся единичные сигналы. Этот единичный сигнал через общую шину 80 откроет элемент сравнения 219 в блоке регистров 2 и произойдет сдвиг информации в канале 118.2 блока регистров 2. После этого произойдет сброс каналов 8.К, 8.N в исходное состояние аналогично описанному выше.

Система будет аналогично функционировать и в случае, когда в блоке регистров 2 отсутствуют задачи с кодом важности 01. Тогда две задачи 10 последовательно с канала 118.3 блока 2 регистров поступят в каналы 8.К, 8.N на решение. В дальнейшем система функционирует аналогично описанному выше.

Рассмотрим функционирование системы во втором случае.

В этом случае на выходе элемента И 134 блока 3 анализа задач появится единичный сигнал, который, пройдя через элемент ИЛИ 142, установит триггер 136 в единичное состояние. При этом на выходах элементов И 131, 132, 133 блока 3 анализа задач будут нулевые сигналы. Допустим, в блоке регистров 2 есть задача с кодом важности 10. Тогда на выходе элемента И 135 блока 3 анализа задач будет единичный сигнал. В этом случае задача с кодом важности 10 из блока регистров 2 поступит через коммутатор 130 блока 3 анализа задач в свободный канал 8.М системы, определяемый блоком 4 выбора. Канал 8.М в режим псевдорежима переводится аналогично описанному выше.

Задача сначала решается в канале 8.М. Когда на выходе элемента И 133 блока 3 анализа задач появится единичный сигнал,

то он пройдет через элемент И 137 блока 3 анализа задач в канал 8.М и через открытый элемент И 29.М канала 8.М сбросит его в исходное состояние аналогично описанно- му выше. После этого канал 8.М готов к решению очередной задачи в основном режиме. В дальнейшем система функционирует аналогично описанному выше.

Формула изобретения

1. Многопроцессорная .вычислительная система, содержащая блок регистров, блок приема кодов задач и Н вычислительных устройств, причем информационные входы

системы подключены соответственно к информационным входами блока приема кодов задач, выходы группы которого подключены к информационным входам первой группы блока регистров, при этом

каждое вычислительное устройство содержит процессор, первый и второй регистры, первый элемент сравнения и первый элемент И, причем в каждом вычислительном устройстве информационный выход процессора подключен к информационному входу первого регистра, выход которого подключен к первому информационному входу первого элемента сравнения, отличающаяся тем, что, с целью повышения

быстродействия, в нее введены блок ранжирования заданий, блок распределения заданий, блок приоритета, блок управления и блок вывода, причем выход блока приема кодов задач подключен к первому

управляющему входу блока регистров и к выходу признака приема кода задачи системы, выходы первой, второй и третьей групп блока регистров подключены соответственно к информационным входам первой, второй и третьей групп блока ранжирования заданий, первый выход которого подключен к второму управляющему входу блока регистров, первый, второй и третий выходы которого подключены соответственно к

первому, второму и третьему управляющим входам блока ранжирования заданий, второй выход которого подключен к третьему управляющему входу блока регистров и к первому управляющему входу блока распределения заданий, третий выход блока ранжирования заданий подключен к четвертому управляющему входу блока регистров и второму управляющему входу блока распределения заданий, четвертый выход блока ранжирования заданий подключен к третьему управляющему входу блока распределения заданий, выходы группы блока ранжирования заданий подключены через системную магистраль адрес/данные к информационным входам четвертой группы

элока ранжирования заданий, к информационным входам второй группы блока регистров, к информационным входам первых рупп всех вычислительных устройств, информационным входом вторых групп всех вычислительных устройств, к выходам первых групп всех вычислительных устройств и к информационным входам первой группы элока вывода, первые выходы всех вычислительных устройств подключены соответственно к первому управляющему входу группы блока распределения заданий, а-й выход группы которого подключен к первому управляющему входу группы а-го вычислительного устройства, первый выход блока распределения заданий подключен к первому входу режима блока управления и к четвертому управляющему входу блока ранжирования заданий, пятый и шестой управляющие входы которого подключены соответственно к второму и третьему выходам блока распределения заданий, пятый выход которого объединен с первым выходом блока управления через монтажное ИЛИ и подключен к вторым управляющим входам всех вычислительных устройств, шестой выход блока ранжирования заданий подключен к третьим управляющим входам всех вычислительных устройств и второму входу режима блока управления, седьмой выход блока ранжирования заданий подключен к четвертым управляющим входам всех вычислительных устройств и третьему входу режима блока управления, второй выход которого подключен к четвертому управляющему входу блока распределения заданий, к пятым управляющим входам всех вычислительных устройств и седьмому управляющему входу блока ранжирования заданий, третий выход блока управления подключен к восьмомууправляющему входу блока ранжирования заданий, первый вход синхронизации системы подключен к входам синхронизации блока управления блока приоритета, блока распределения заданий, к первому входу синхронизации блока приема кодов задач, к первому входу синхронизации блока ранжирования и к первым и вторым входам синхронизации всех вычис- пительных устройств, второй вход синхронизации системы подключен к третьим входам синхронизации всех вычислительных устройств, к второму входу синхронизации блока ранжирования заданий и второму зходу синхронизации блока приема кодов задач, выходы вторых групп вычислительных устройств с первой по Н-ное подключены соответственно к информационным зходам групп с второй по (Н+1)-ную блока зывода, вход синхронизации которого подключен к третьему входу синхронизации системы, выходы трех групп вычислительных устройств с первого по Н-ное подключены соответственно к информационным входам

групп с (Н+2):й по (2Н-1) блока вывода, управляющие входы с первого по Н-й которого подключены соответственно к входам квитанции от абонентов системы, четвертый выход блока управления подключен к шес0 тым управляющим входам всех вычислительных устройств, пятый выход блока управления подключен к седьмым управляющим входам всех вычислительных устройств, шестой выход блока управления

5 подключен к восьмым управляющим входам

всех вычислительных устройств и к первому

управляющему входу блока приоритета,

седьмой выход блока управления подклю чен к девятым управляющим входам всех

0 вычислительных устройств, восьмой выход . блока управления подключен к десятым управляющим входам всех вычислительных устройств, девятый выход блока управления подключен к четвертым входам синхрониза5 ции всех вычислительных устройств, десятый выход блока управления подключен к второму управляющему входу блока приоритета, выходы с первого по Н-й которого подключены соответственно к одиннадца0 тым управляющим входам вычислительных устройств с первого по Н-ноё, вторые выходы вычислительных устройств с первого по Н-ное подключены соответственно к управляющим входам с первого по Н-й первой

5 группы блока вывода, третьи выходы вычислительных устройств с первого по Н-ное подключены соответственно к управляющим входам с первого по Н-й второй группы блока вывода, четвертые выходы вычисли0 тельных устройств с первого по Н-ное подключены соответственно к управляющим входам с первого по Н-й третьей группы блока вывода, пятые выходы вычислительных устройств с первого по Н-ное подклю5 чены соответственно по входам режима первой группы блока управления, шестые выходы вычислительных устройств с первого по Н-ное подключены соответственно по входам режима второй группы блока управ0 ления, седьмые выходы вычислительных устройств с первого по Н-ное подключены соответственно к входам режима третьей группы блока управления, восьмые выходы вычислительных блоков с первого по Н-й

5 подключены соответственно к входам режима с первого по Н-й четвертой группы блока управления, девятые выходы вычислительных блоков с первого по Н-й подключены соответственно к входам режима с первого по Н-й пятой группы блока управления и

соответственно к информационным входам первой группы блока приоритета, десятые выходы вычислительных блоков с первого по Н-й подключены соответственно к входам режима с первого по Н-й шестой группы блока управления, одиннадцатые выходы вычислительных блоков с первого по Н-й подключены соответственно к информационным входам с первого по Н-й второй груп- пы блока приоритета, четвертый вход синхронизации системы подключен к пятым входам синхронизации всех вычислительных устройств, входы значения допустимого числа отказов системы подключены соответственно к информационным входам третьих групп всех вычислительных устройств, при этом в каждое вычислительное устройство введены второй элемент сравнения, узел управления последовательностью решения задач, с первого по третий триггеры, с второго по двенадцатый элементы И, с первого по девятый элементы ИЛИ, элемент 2 И-ИЛИ, блок уэлементов И и одновибратор, причем в каждом вычислительном устройстве первый управляющий вход вычислительного устройства подключен к первому входу первого элемента ИЛИ и к входу синхронизации первого триггера, прямой выход которого подключен к первым входам первого и второго элементов И, выходы которых подключены соответственно к входам второго элемента ИЛИ, выход которого подключен к первым входам третьего, четвертого, пятого и шестого элементов ИЛИ и первому входу сброса процессора, выход признака окончания временного интервала которого подключен к первым входам третьего и четвертого элементов И, информационные входы первой группы вычислительного устройства подключены к информационным входам второй группы первого элемента сравнения и к информационным входам первой группы второго элемента сравнения, выход первого элемента сравнения подключен к первому управляющему входу узла управления последовательностью решения задач, к седьмому выходу вычислительного устройства и первому входу пятого элемента И, выход которого подключен к первому входу блока элементов И, выходы которого подключены соответственно к выходам первой группы вычислительного блока, выход второго элемента сравнения подключен к второму управляющему входу узла управления последовательностью решения задач, к второму входу четвертого элемента И, к девятому выходу вычислительного устройства и первому входу шестого элемента И, выход которого подключен к восьмому выходу вычислительного устройства, выходы первого регистра подключены к информационным входам первой группы первого элемента сравнения, к входам первой группы блока элементов И, к выходам второй группы вычислительного устройства и входам седьмого элемента ИЛИ, выход которого подключен к первому входу седьмого элемента И, к второму выходу вычислительного

0 устройства, к первому входу восьмого элемента И и входу квитанции процессора, выход значения контрольной точки которого подключен к первому входу элемента 2И ИЛИ и к 1-входу второго триггера, прямой и

5 инверсный выходы которого подключены соответственно к первым входам девятого и десятого элементов И, информационные входы второй группы с первого по (Р-1)-й вычислительного устройства, где Р - раз0 рядность информационных слов системы, подключены к информационным входам второго регистра и к информационным входам процессора, выход первого элемента ИЛИ подключен к входу запуска процессора

5 и входам синхронизации третьего триггера и второго регистра, выходы которого подключены к выходам третьей группы вычислительного устройства, к входам второй группы блока элементов И, к информацион0 ным входам второй группы второго элемента сравнения и входам восьмого элемента ИЛИ, выход которого подключен к пятому выходу вычислительного устройства и к первому входу одиннадцатого элемента И, ин5 версный выход которого подключен к первому выходу вычислительного устройства, Р-й информационный вход второй группы которого подключен к l-входу третьего триггера, прямой выход которого подклю0 чен к второму входу третьего элемента И, к первому входу девятого элемента ИЛИ и второму входу восьмого элемента И, выход которого подкл ючен к входу одновибратора, выход которого подключен к вторым входам

5 третьего, четвертого и шестого элементов ИЛИ, выход последнего подключен к входу установки в О первого регистра, инверсный выход второго триггера подключен к третьему выходу вычислительного устройст0 ва и второму входу седьмого элемента И, выход которого подключен к второму входу шестого элемента И # третьему управляющему входу узла управления последовательностью решения задач, первый выход

5 которого подключен к второму входу девятого элемента ИЛИ, выход которого подключен к инверсным входам синхронизации первого и второго элементов сравнения, второй выход узла управления последовательностью решения задач подключен к входу кода решаемой задачи процессора, к третьему входу третьего элемента ИЛИ, к второму входу пятого элемента ИЛИ и третьему входу шестого элемента ИЛИ, выходы третьего, четвертого и пятого элемен- тов ИЛИ подключены соответственно к входам установки в О второго регистра, третьего триггера и второго триггера, третий выход узла управления последовательностью решения задач подключен к вторым входам девятого и десятого элементов И, выход девятого элемента И подключен к первому входу двенадцатого элемента И, к второму входу пятого элемента И и четвертому выходу вычислительного устройства, выход десятого элемента И подключен к третьему входу пятого элемента ИЛИ и к четвертому входу шестого элемента ИЛИ, выход двенадцатого элемента И подключен к четвертому входу третьего элемента ИЛИ, к второму входу сброса процессора, к третьему входу четвертого элемента ИЛИ, к четвертому входу пятого элемента ИЛИ и к пятому входу шестого элемента ИЛИ, четвертый выход узла управления последова- тельностью решения задач подключен к третьему входу сброса процессора, к второму входу первого элемента ИЛИ и шестому входу шестого элемента ИЛИ, второй управляющий вход вычислительного устройства подключен к второму входу второго элемента И, третий управляющий вход вычислительного устройства подключен к второму входу первого элемента И, четвертый управляющий вход вычислительного устройства подключен к l-входу первого триггера, инверсный выход которого подключен к третьему входу пятого элемента И, к шестому выходу вычислительного блока и второму входу одиннадцатого элемента И, пятый уп- равляющий вход вычислительного устройства подключен к четвертому управляющему входу узла управления последовательностью решения задач, шестой управляющий вход вычислительного устройства подключен к входу установки в О первого триггера, седьмой управляющий вход вычислительного устройства подключен к третьему входу первого элемента И, восьмой управляющий вход вычислительного устройства подключен к пя- тому управляющему входу узла управления последовательностью решения задач, девятый управляющий вход вычислительного устройства подключен к третьему входу второго элемента И. десятый и одиннадца- тый управляющие входы вычислительного устройства подключены к шестому управляющему входу узла управления последовательностью решения задач и к второму входу блока элементов И, первый вход синхронизации вычислительного устройства подключен к первому входу синхронизации узла управления последовательностью

решения задач, пятый выход которого подключен к четвертому входу четвертого элемента ИЛИ, к четвертому входу сброса процессора и пятому входу третьего элемента ИЛИ, второй вход синхронизации вычислительного устройства подключен к первому входу синхронизации процессора и второму и третьему входам элемента 2И- ИЛИ, выход которого подключен к входам синхронизации первого регистра и второго триггера, третий вход синхронизации узла управления последовательностью решения задач подключен к четвертым входам первого и второго элементов И, к второму входу синхронизации процессора и к второму входу синхронизации узла управления последовательностью решения задач, четвертый вход синхронизации вычислительного устройства подключен к третьему входу синхронизации узла управления последовательностью решения задач, пятый вход синхронизации подключен к третьему входу восьмого элемента И и второму входу двенадцатого элемента И, выход признака конца решения задачи процессора подключен к четвертому входу элемента 2И-ИЛИ, выход третьего элемента И подключен к седьмому управляющему входу узла управления последовательностью решения задач, шестой выход и информационные входы которого подключены соответственно к одиннадцатому выходу и к информационным входам вычислительного устройства, выход четвертого элемента И подключен к десятому выходу вычислительного устройства, причем узел управления последовательностью решения задач содержит восемь элементов И, два элемента ИЛИ, два формирователя импульсов и счетчик, при этом в узле управления последовательностью решения задач первый управляющий вход узла подключен к первым входам первого и второго элементов И и к первому входу третьего элемента И, второй управляющий вход

узла подключен к первому входу четвертого элемента И, к второму входу первого элемента И к вторым входам второго и третьего элементов И, выходы которых подключены соответственно к первому и второму входам первого элемента ИЛИ, выход которого подключен к входу декремента счетчика и первому входу пятого элемента И, выход которого подключен к второму выходу узла, третий управляющий вход которого подключен второму входу четвертого элемента И, к зторому входу первого элемента И и первому входу шестогоэлемента И, выход которого подключен к шестому выходу узла, четвертый управляющий вход которого подключен к третьему входу четвертого элемента И, выход которого подключен к входу первого формировате- ля импульсов, выход которого подключен к четвертому выходу узла, пятый управляющий вход которого подключен к четвертому входу первого элемента И, к третьему входу третьего элемента И и третьему входу вто- рого элемента И, шестой управляющий вход узла подключен к четвертым входам второго и третьего элементов И, седьмой управляющий вход узла подключен к первым входам седьмого и восьмого элементов И, выходы которых подключены соответственно к второму входу первого элемента ИЛИ и к входу второго формирователя импульсов, выход которого подключен к пятому выходу узла, первый вход синхронизации которого под- ключей к пятому входу первого элемента И, к второму входу седьмого элемента И и к входу синхронизации счетчика, информационные выходы которого подключены к входам второго элемента ИЛИ, выход которого подключен к второму входу шестого элемента И, к первому входу узла, к второму входу пятого элемента И, к входу записи/считывания счетчика и к второму входу восьмого элемента И, второй вход синхронизации уз- ла подключен к четвертому входу четвертого элемента И, третьему входу пятого элемента И и третьему входу восьмого элемента И, третий вход синхронизации узла подключен к пятому входу четвертого элемента И и к шестому входу первого элемента И, выход которого подключен к третьему выходу узла, информационные входы которого подключены соответственно к информационным входам счетчика.

2. Система по п. 1,отличающаяся тем, что блок приема задач содержит два регистра, узел сравнения, формирователь импульсов, элемент И и элемент ИЛИ, причем в блоке приема кодов задач информаци- онные входы блока приема кодов задач подключены к информационным входам первого и второго регистров, выходы первого регистра подключены к информационным входам первой группы узла сравнения, выход которого подключен к первому входу элемента И, выход которого подключен к выходу блока приема кодов задач, выходы второго регистра подключены к информационным входам второй группы узла сравне- ния, к информационным выходам группы блока приема кодов задач и к входам элемента ИЛИ, выход которого подключен к второму входу элемента И. первый вход синхронизации блока приема кодов задач подключен к входам синхронизации первого и второго регистров, второй вход синхронизации блока приема кодов задач подключен к третьему входу элемента И и входу формирователя импульсов, выход которого подключен к входам установки в О первого и второго регистров.

3. Система по п. 1,отличающаяся тем, что блок ранжирования задач содержит десять элементов И, два элемента ИЛИ, три формирователя импульсов,, триггер и узел элементов 4И-ИЛИ, при этом первый управляющий вход блока ранжирования задач подключён к первым входам первого и второго элементов И, выход которого подключен к первому входу первого элемента ИЛИ, выход которого подключен к информационному входу триггера, выход которого подключен к седьмому выходу блока ранжирования задач и к первым входам третьего и четвертого элементов И и первому входу пятого элемента И, выход которого подключен к входу первого формирователя импульса, выход которого подключен к третьему выходу блока ранжирования задач, второй управляющий вход которого подключен к первому входу шестого элемента И и первому входу седьмого элемента И, выход которого подключен к второму входу первого элемента ИЛИ, третий и четвертый управляющие входы блока ранжирования задач подключены к входу восьмого элемента И, выход которого подключен к первому входу девятого элемента И и к первому входу узла элементов 4 И-ИЛИ, выход которого подключен к выходу группы блока ранжирования задач и к входам второго элемента ИЛИ, выход которого подключен к четвертому выходу блока ранжирования задач, пятый управляющий вход которого подключен к второму входу первого элемента И к второму входу второго элемента И, выход первого элемента И подключен к второму входу четвертого элемента И, к первому входу десятого элемента И, к второму входу девятого элемента И, к второму входу пятого элемента И, второму, третьему и четвертым входам узла элементов 4И-ИЛИ, шестой управляющий вход блока ранжирования задач подключен к второму входу седьмого элемента И и второму входу шестого элемента И, выход которого подключен к третьему входу девятого элемента И, к третьему входу пятого элемента И, к пятому и шестому входам узла элементов 4 И-ИЛИ, седьмой управляющий вход блока ранжирования задач подключен к входу установки в О триггера, восьмой управляющий вход блока подключен к четвертому входу пятого элемента И, к седьмому, восьмому, девятому и десятому

ВХОДЕ м узла элементов 4И-ИЛ И, к четвертому входу девятого элемента И и второму вход десятого элемента И, выход которого подк/ ючен к входу второго формирователя импутьсов, выход которого подключен к первому выходу блока ранжирования задач, первый вход синхронизации которого подключен к третьим входам второго, седьмого и десятого элементов И. второй вход синх- рониаации блока ранжирования задач под- ключей к пятым входам девятого и пятого элементов И, выход девятого элемента И подключен к входу третьего формирователя импутьсов, выход которого подключен к вторе му выходу блока ранжирования задач, информационные входы первой, второй, третьей и четвертой групп блока ранжирования задач подключены соответственно к входам первой, второй, третьей и четвертой групп узла элементов 4И-ИЛИ, выходы третьэго и четвертого элементов И подключены соответственно к пятому и к шестому выходам блока.

4 Система по п.1, отличающая сч тем, что блок распределения заданий содер- жит первую группу из (Н-1) элементов И, вторую группу из (Н-1) элементов И, третью группу из (Н-2) элементов И, с первого по (Н+1Нный элементы И, группу из (Н-2) элементов ИЛИ, первый и второй элементы

ИЛИ, при э блока первь пы, к

первый и второй пороговые элементы, ом первый управляющий вход группы распределения заданий подключен к м входам элементов И первый труппервым входам элементов И второй группы, к первым входам первого элемента И, пе эвого и второго пороговых элементов и пер юго элемента ИЛИ, второй управляющий ход группы блока распределения заданий подключен к вторым входам первых элементов И первой и второй групп, а-й управляющий вход группы блока (где а 3

Н) подключен к вторым входам (а-1)-х элементов И первый и второй группы и к первым ходам (а-2)-го элемента И третьей групп э|, выход С-го (где С 1 ...Н-1) элемента И перзой группы подключен к первому входу С-гэ элемента ИЛИ группы, к (С+2)-м входам э; ементов И с (С+1)-го по(Н-1)-й первой и втог.ой групп, выход С-го элемента И второй группы подключен к второму входу С-го элемента группы, к(С+3)-м входам элементов И с(С+1)-го по(Н-1)-й второй группы и к (С+1)-м входам элементов И с С-го по (H-2)-ii третьей группы, выход b-го элемента И третьей группы где (Ь 1Н-2) подключен к Ъ+3)-му входу элементов И с (В+1)-го по (Н-2)-й третьей группы и к (Ь+2)-му входу (B+1)-i о элемента ИЛИ группы, первый управляющий вход блока распределения за0 5 0

5 0

5

0

5

0

5

даний подключен к первому входу второго элемента ИЛИ, выход которого подключен к (2с+1)-му входу С-го элемента И второй группы, второй управляющий вход блока распределения заданий подключен к(2В+1)-му входу b го элемента И третьей группы, выход С-го элемента ИЛИ группы подключен к первому входу (С-М)-го элемента И, к (С+1)-му входу первого элемента ИЛИ и к (С+1)-м входам первого и второго пороговых элементов, третий управляющий вход и вход синхронизации блока распределения заданий подключен к входам (Н-Н)-го элемента И, выход которого подключен к вторым входам элементов И, с первого по Н-й выходы которых подключены соответственно к выходам группы блока распределения заданий, четвертый управляющий вход которого подключен к второму входу второго элемента ИЛИ. выходы первого элемента ИЛИ, первого и второго пороговых элементов подключены соответственно к первому, второму и третьему выходам блока распределения заданий.

5. Система по п.1,отличающаяся тем, что блок управления содержит семь пороговых элементов, шесть элементов И и три элемента ИЛИ, при этом входы режима первой группы блока управления подключены к инверсным входам первого и второго пороговых элементов, входы режима второй группы блока управления подключены к входам группы первого элемента И, выход которого подключен к третьему выходу блока управления, входы режима третьей группы которого подключены к входу третьего порогового элемента, выход которого подключен к шестому выходу блока управления и первому входу второго элемента И, выход которого подключен к второму выходу блока управления, входы режима четвертой группы которого подключены к входам четвертого порогового элемента и к входам пятого порогового элемента, входы режима пятой группы блока управления подключены к входам шестого и седьмого пороговых элементов, выход первого порогового элемента подключен к пятому выходу блока уп- равления и первому входу третьего элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выход которого подключен к четвертому выходу блока управления, выход второго порогового элемента подключен к седьмому выходу блока управления и первому входу четвертого элемента И, выход которого подключен к второму входу первого элемента ИЛИ, выход четвертого порогового элемента подключен к восьмому выходу

блока управления и первому входу четвертого элемента И, выход которого подключен к десятому выходу блока управления и первому входу второго элемента ИЛИ, выход которого подключен к второму входу второго элемента И и девятому выходу блока управления, выход пятого порогового элемента подключен к третьему входу второго элемента И и первому входу пятого элемента И, выход которого подключен к второму входу элемента ИЛИ, выходы шестого и седьмого пороговых элементов подключен соответственно к вторым входам

четвертого и пятого элементов И, входы режима шестой группы блока управления подключены к входам третьего элемента ИЛИ, выход которого подключен к третьему входу второго элемента ИЛИ, вход синхронизации блока управления подключен к входу первого элемента И и к вторым входам третьего и четвертого элементов И, первый, второй и третий входы режима блока управления подключены соответственно к четвертому входу второго элемента И, к третьему входу четвертого элемента И и третьему входу третьего элемента И.

I

I

г

6ш1 приема

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная система | 1990 |

|

SU1783538A1 |

| Многопроцессорная система | 1989 |

|

SU1741144A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1636846A1 |

| Многопроцессорная система | 1989 |

|

SU1735866A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1524052A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1543404A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1569831A1 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

Изобретение относится к вычислительной технике и может быть использовано в отказоустойчивых системах для распределения задач между процессорами. Целью изобретения является повышение быстродействия. Цель достигается тем, что многопроцессорная вычислительная система содержит блок регистров, блок приема кодов задач, Н вычислительных устройств, блок ранжирования заданий, блок распределения заданий, блок приоритета, блок управления и блок вывода. 4 з.п. ф-лы, 10 ил.

Фиг. 3( лист 1)

/м.; iwj

Р

Ш.1.

flf

Канал 118.1

Л

Л

Кана л.Ц 8.1

65

55

RP

ИГг7//гг/ V8.3

,

J

00 3(лист 2

з §5

блох 5 дыдачц результата

Мз№1Ш

ИЗКШ1

ИзНБШ

Фиг.Б(Лист)

№1

v

{

n

172

174 175 108.Z

Ш fSU

r-i p)

I

10S.n

D

фиг.6(ЛистЈ}

ffu1 22UШ1 221.1

m jim

ГШ IK

ч

mi

1Ш

////

////

mj

%1

/7//

Шл

лд.п

н-u

блок 9.1 принятия решения Фиг. 9

(tfaveq }

ш-

30#Ј/Ы 3ffffirv6

t$j.pefft/c sry.2

pi/. S0fs /)

pe/e. /0f#. )

Рае. S0(/r. 3)

Составитель Д. Дмитров

Техред М.МоргенталКорректор М. Петрова

Редактор

Заказ 2866ТиражПодписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035. Москва, Ж-35, Раушская изб., 4/5

Авторы

Даты

1993-08-30—Публикация

1991-02-11—Подача